### ADVANCE PRODUCT BULLETIN September, 1989

### FEATURES

#### **Key Features:**

- · Four full-duplex multi-protocol channels

- Asynchronous, character synchronous and HDLC framing

- 32-bit double-buffered DMA controller for all channels

- Bit rates to 64K baud on transmit and receive

- Independent bit rate generators for transmit and receive

- · Digital PLL on each receiver

- NRZ, NRZI and Manchester data encoding supported

- · Two independent timers per channel

#### **Asynchronous Operation Features:**

- Improved interrupt schemes:

- Vectored interrupts to allow direct jump into proper service routines

- Good data interrupts<sup>™</sup> eliminate need for status checks

- · User-programmable and automatic flow control modes:

- In-Band (software) via XON, XOFF

- Out-of-Band (hardware) via RTS/CTS, DTR/DSR

- Line break detection and generation

- --- Special character recognition and transmission

# *CL*—*CD240*

### Intelligent Multi-Protocol Peripheral (IMP)

#### **Synchronous Operation Features:**

- Programmable sync, frame start/end and idle character

- Optional CRC generation and validation

- Chain/unchain of long frames into multiple buffers

#### **HDLC Features:**

- Four 8-bit or two 16-bit frame address matching

- FCS generation and validation

- Header only (small frame) transmission and reception without DMA overhead

#### **Bisync Features:**

- ASCII or EBCDIC encoding

- Special character recognition for block separation and CRC processing without host intervention

CL - CD240

## FEATURES (Continued)

#### **DMA Controller Features:**

- Full 32-bit address and 16-bit data transfers

- Duplicated configuration register set to reduce real-time constraints

- Trickle buffer and block buffer DMA capability on transmit

#### **Other Features:**

- Transmit and receive clock rates independently set using a divisor of system clock

- 16 byte receive and transmit FIFOs

- Local and remote maintenance loopback modes

- 5 clock/modem control signals per channel DTR, CD, DSR, RTS, CTS

- 5- to 8-bit character plus optional parity

- Programmable parity and number of stop bits

- Byte-endian orientation selection pin

- System clock of up to 20 MHz

- Packaged in an 84-pin PLCC

- Advanced low power CMOS process technology

#### **Application Areas:**

- ISDN Terminal Equipment

- Data Concentrators/MUX

- Cluster Controllers

- SDLC

- Local Area Networking

- Protocol Converter

- Terminal/Modem

- X.21, X.25 and SS7

## **OVERVIEW**

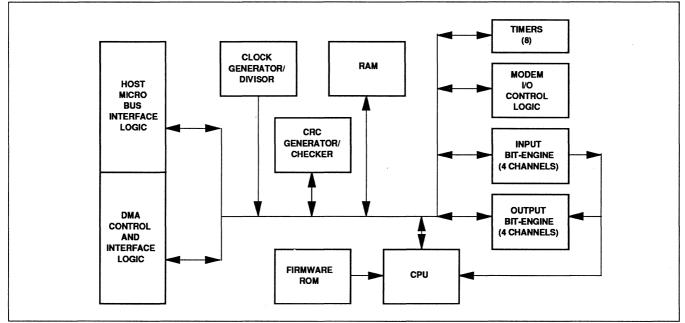

The CD240 is a sync/async communications controller featuring full on chip DMA for each channel in each direction. Combining the DMA and protocol controllers enables a more efficient Host interface by reducing Host intervention and bus occupancy for both synchronous and asynchronous modes of operation.

The throughput and performance of the CD240 are further improved by the following features:

- optimized firmware sequence for the on-chip protocol handling

- simultaneous usage of more than one buffer area and adding data space to existing buffers during DMA

- on-chip timers keeping track of real time events

- an efficient, fair share mechanism vectored interrupt scheme.

Refer to Figure 1 for the functional block diagram of the CD240.

# *CL*—*CD240*

## **ADVANTAGES**

| Unique Features                                                                                                          | Benefits                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 multi-protocol serial channels with on-chipDMA                                                                         | Reduce chip space, increase reliability of the system and cost reduction                                                                                                                                                                                                                                                                                  |

| On-chip FIFO (16 bytes per direction for each channel)                                                                   | Greatly reduces real-time response time by the CPU.<br>Cut down overrun/underrun possibilities. Increase DMA efficiency.                                                                                                                                                                                                                                  |

| On-chip DMA with advanced<br>buffer management schemes<br>(Chain Buffering, Trickle Buffering<br>and Header Segregation) | Efficient utilization of system memory space, reducing CPU overhead of re-<br>programming DMA address locations, byte counts, etc. The buffer management<br>also allows the implementation of Bank Switching or Dual Port memory which<br>increase system performance. The Header Separation eliminates DMA overhead on<br>"small" HDLC frames Rx and Tx. |

| Two independent timers per channel                                                                                       | Reduce CPU overhead of keeping track of time-out and unnecessary holding of system bus.                                                                                                                                                                                                                                                                   |

| Interrupt and DMA handshaking                                                                                            | This allows normal DMA activity to be interspersed with interrupts when special conditions or data errors occur. This is not possible when the DMA and data control functions are separated.                                                                                                                                                              |

# **REGISTER SUMMARY (Intel Mode)**

### **Global Registers**

| Description                            | Registers | A7 | <b>A6</b> | A5 | A4 | A3 | A2 | A1 | <b>A0</b> | R/W |

|----------------------------------------|-----------|----|-----------|----|----|----|----|----|-----------|-----|

| Global Interrupt Channel Register      | GICR      | 1  | 0         | 0  | 0  | 0  | 0  | 0  | 0         | R/W |

| Modem End of Interrupt Register        | MEOIR     | 1  | 0         | 0  | 0  | 0  | 1  | 0  | 1         | R/W |

| Transmit End of Interrupt Register     | TEOIR     | 1  | 0         | 0  | 0  | 0  | 1  | 1  | 0         | R/W |

| Receive End of Interrupt Register      | REOIR     | 1  | 0         | 0  | 0  | 0  | 1  | 1  | 1         | R/W |

| Timer Period Register                  | TPR       | 1  | 1         | 0  | 1  | 1  | 0  | 0  | 0         | R/W |

| Priority Interrupt Level Register 1    | PILR1     | 1  | 1         | 1  | 0  | 0  | 0  | 0  | 1         | R/W |

| Priority Interrupt Level Register 2    | PILR2     | 1  | 1         | 1  | 0  | 0  | 0  | 1  | 0         | R/W |

| Priority Interrupt Level Register 3    | PILR3     | 1  | 1         | 1  | 0  | 0  | 0  | 1  | 1         | R/W |

| Channel Access Register                | CAR       | 1  | 1         | 1  | 0  | 1  | 1  | 0  | 0         | R/W |

| Receive Data Register                  | RDR       | 1  | 1         | 1  | 1  | 1  | 0  | 0  | 0         | R   |

| Transmit Data Register                 | TDR       | 1  | 1         | 1  | 1  | 1  | 0  | 0  | 0         | W   |

| Global Firmware Revision Code Register | GFRCR     | 1  | 0         | 0  | 0  | 0  | 0  | 1  | 0         | R   |

| Transmit FIFO Transfer Count           | TFTC      | 1  | 0         | 0  | 0  | 0  | 0  | 1  | 1         | R   |

| Modem Interrupt Status Register        | MISR      | 1  | 0         | 0  | 0  | 1  | 0  | 0  | 0         | R   |

| Transmit Interrupt Status Register     | TISR      | 1  | 0         | 0  | 0  | 1  | 0  | 0  | 1         | R   |

| Receive Interrupt Status Register Low  | RISRL     | 1  | 0         | 0  | 0  | 1  | 0  | 1  | 0         | R   |

| Receive Interrupt Status Register High | RISRH     | 1  | 0         | 0  | 0  | 1  | 0  | 1  | 1         | R   |

| Channel Registers                      |           |    |           |    |    |    |    |    |           |     |

| Local Interrupt Vector Register        | LIVR      | 0  | 0         | 0  | 0  | 1  | 0  | 1  | 0         | R/W |

| Channel Command Register               | CCR       | 0  | 0         | 0  | 1  | 0  | 0  | 0  | 0         | R/W |

| Special Transmit Command Register      | STCR      | 0  | 0         | 0  | 1  | 0  | 0  | 0  | 1         | R/W |

*CL*—*CD240*

# **REGISTER SUMMARY** (Continued)

| Description                                       | Registers  | A7 | <b>A6</b> | A5 | A4 | A3 | A2 | A1 | A0 | R/W |

|---------------------------------------------------|------------|----|-----------|----|----|----|----|----|----|-----|

| Interrupt Enable Register                         | IER        | 0  | 0         | 0  | 1  | 0  | 0  | 1  | 0  | R/W |

| Channel Option Register 1                         | COR1       | 0  | 0         | 0  | 1  | 0  | 0  | 1  | 1  | R/W |

| Channel Option Register 2                         | COR2       | 0  | 0         | 0  | 1  | 0  | 1  | 0  | 0  | R/W |

| Channel Option Register 3                         | COR3       | 0  | 0         | 0  | 1  | 0  | 1  | 0  | 1  | R/W |

| Channel Option Register 4                         | COR4       | 0  | 0         | 0  | 1  | 0  | 1  | 1  | 0  | R/W |

| Channel Option Register 5                         | COR5       | 0  | 0         | 0  | 1  | 0  | 1  | 1  | 1  | R/W |

| Channel Mode Register                             | CMR        | 0  | 0         | 0  | 1  | 1  | 0  | 0  | 0  | R/W |

| Channel Status Register                           | CSR        | 0  | 0         | 0  | 1  | 1  | 0  | 0  | 1  | R   |

| Modem Change Register                             | MCR        | 0  | 0         | 0  | 1  | 1  | 0  | 1  | 1  | R/W |

| Special Character Register 1–4 (Async)            | SCHR1-4    | 0  | 0         | 0  | 1  | 1  | 1  | Х  | X  | R/W |

| Receive Frame Address Register 1–4 (Sync)         | RFAR1-4    |    |           |    |    |    |    |    |    |     |

| Special Character Range Low, High (Async)         | SCRL, SCRH | 0  | 0         | 1  | 0  | 0  | 0  | 0  | Х  | R/W |

| Transmit Header Address Low, High (Sync)          | THAL, THAH | -  | -         |    | -  | -  | -  | -  |    |     |

| Transmit Header Control Low                       | THCL       | 0  | 0         | 1  | 0  | 0  | 0  | 1  | 0  | R/W |

| Transmit Header Control High                      | THCH       | 0  | 0         | 1  | 0  | 0  | 0  | 1  | 1  | R/W |

| Receive Header Address Low                        | RHAL       | Ō  | 0         | 1  | 0  | 0  | 1  | 0  | 0  | R   |

| Receive Header Address High                       | RHAH       | Õ  | Ő         | 1  | Õ  | Õ  | 1  | Õ  | 1  | R   |

| Receive Timeout Period Register Low, High (Async) | RTPRL, H   | Õ  | Õ         | 1  | Õ  | Õ  | 1  | 1  | x  | R/W |

| Receive Header Control Low, High (Sync)           | RHCL, H    | Õ  | Ő         | 1  | Õ  | Õ  | 1  | 1  | X  | R   |

| Receive Timer Register Low, High (Async)          | RTRL, RTRH | Õ  | Ő         | 1  | Õ  | ĩ  | 0  | Ō  | x  | R   |

| General Timer 1 Low, High (Sync)                  | GT1L, GT1H | Õ  | Õ         | 1  | Õ  | 1  | Õ  | Õ  | X  | R/W |

| Transmit Timer Register (Async)                   | TTR        | Õ  | Ő         | 1  | Õ  | 1  | Õ  | 1  | 0  | R   |

| General Timer 2 (Sync)                            | GT2        | Õ  | Ő         | 1  | Õ  | 1  | Õ  | 1  | Ő  | R/W |

| A Receive Buffer Address 0–3                      | ARBADR0-3  | Ő  | 1         | 0  | Õ  | Ô  | Ŏ  | x  | x  | R/W |

| B Receive Buffer Address 0–3                      | BRBADR0-3  | Ő  | 1         | 0  | Õ  | Õ  | 1  | X  | X  | R/W |

| A Transmit Buffer Address 0–3                     | ATBADR0-3  | Ő  | 1         | Õ  | 1  | Ő  | 0  | X  | X  | R/W |

| B Transmit Buffer Address 0–3                     | BTBADR0-3  | Ő  | 1         | 0  | 1  | Ő  | 1  | X  | X  | R/W |

| A Buffer Transmit Byte Count Low                  | ATBCNTL    | 0  | 1         | 0  | 1  | 1  | 0  | 0  | 0  | R/W |

| A Buffer Transmit Byte Count High                 | ATBCNTH    | 0  | 1         | 0  | 1  | 1  | Õ  | 0  | 1  | R/W |

| B Buffer Transmit Byte Count Low                  | BTBCNTL    | 0  | 1         | 0  | 1  | 1  | Ő  | 1  | 0  | R/W |

| B Buffer Transmit Byte Count High                 | BTBCNTH    | Ő  | 1         | 0  | 1  | 1  | Ő  | 1  | 1  | R/W |

| A Transmit Buffer Status                          | ATBSTS     | 0  | 1         | 0  | 1  | 1  | 1  | 0  | 0  | R/W |

| B Transmit Buffer Status                          | BTBSTS     | 0  | 1         | 0  | 1  | 1  | 1  | 0  | 1  | R/W |

| Transmit Baud Rate Generator Register             | TBPR       | 1  | 1         | 0  | 0  | 0  | 0  | 0  | 1  | R/W |

| Transmit Clock Option Register                    | TCOR       | 1  | 1         | 0  | 0  | 0  | 0  | 1  | 0  | R/W |

|                                                   | RBPR       |    | 1         | 0  | 0  |    | 0  | 0  |    |     |

| Receive Baud Rate Period Register                 |            | 1  |           |    |    | 1  |    |    | 1  | R/W |

| Receive Clock Option Register                     | RCOR       | 1  | 1         | 0  | 0  | 1  | 0  | 1  | 0  | R/W |

| CRC Polynomial Select Register                    | CPSR       | 1  | 1         | 0  | 1  | 0  | 1  | 0  | 0  | R/W |

| Modem Signal Value Register — RTS                 | MSVR-RTS   | 1  | 1         | 0  | 1  | 1  | 1  | 0  | 0  | R/W |

| Modem Signal Value Register — DTR                 | MSVR-DTR   | 1  | 1         | 0  | 1  | 1  | 1  | 0  | 1  | R/W |

| Receive FIFO Output Count                         | RFOC       | 0  | 0         | 1  | 1  | 0  | 0  | 1  | 1  | R   |

| Receive Current Buffer Address 0–3                | RCBADR0-3  | 0  | 0         | 1  | 1  | 1  | 1  | X  | X  | R   |

| A Buffer Receive Byte Count Low                   | ARBCNTL    | 0  | 1         | 0  | 0  | 1  | 0  | 0  | 0  | R   |

| A Buffer Receive Byte Count High                  | ARBCNTH    | 0  | 1         | 0  | 0  | 1  | 0  | 0  | 1  | R   |

| B Buffer Receive Byte Count Low                   | BRBCNTL    | 0  | 1         | 0  | 0  | 1  | 0  | 1  | 0  | R   |

| B Buffer Receive Byte Count High                  | BRBCNTH    | 0  | 1         | 0  | 0  | 1  | 0  | 1  | 1  | R   |

| A Receive Buffer Status                           | ARBSTS     | 0  | 1         | 0  | 0  | 1  | 1  | 0  | 0  | R   |

| B Receive Buffer Status                           | BRBSTS     | 0  | 1         | 0  | 0  | 1  | 1  | 0  | 1  | R   |

*CL*—*CD240*

## **PIN DESCRIPTION**

| Symbol          | NUM         | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocesso   | r Interface |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>cc</sub> | 2           | I               | Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GND             | 4           | Ι               | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <del>CS</del>   | 1           | Ι               | Chip Select — when low the CD240 registers may be read or written by the Host.                                                                                                                                                                                                                                                                                                                                                                               |

| ĀS              | 1           | I/O, 3-state    | Address Strobe — input when CD240 is the slave. This signal is output when CD240 is the bus master indicating that $R\overline{W}$ , A(0-7) and A(8-31) <sup>@</sup> are valid.<br>@ see pin ADLD for explanation                                                                                                                                                                                                                                            |

| DS              | 1           | I/O, 3-state    | $\overline{\text{Data Strobe}}$ — when the CD240 is not a bus master, this is an input used to strobe data into registers during write cycles and enable data onto the bus during read cycles. When the CD240 is a bus master $\overline{\text{DS}}$ is an output used to control data transfer to and from system memory.                                                                                                                                   |

| R/W             | 1           | I/O, 3-state    | Read/Write — when the CD240 is not a bus master this pin is an input which determines if a read or write operation is required when the $\overline{CS}$ and $\overline{DS}$ are active. When the CD240 is a bus master $\overline{R/W}$ is an output and indicates a read or write to system memory.                                                                                                                                                         |

| DTACK           | 1           | I/O, open drain | Data Transfer Acknowledge — when the CD240 is not a bus master this is an output and indicates to the Host when a read or write to the CD240 is complete. When BR is driven low by the CD240, DTACK is an input which qualifies system bus is no longer in use. When the CD240 is a bus master, DTACK is an input which indicates when system memory read and write cycles are complete.                                                                     |

| SIZ(0-1)        | 2           | I/O, 3-state    | SIZE(0-1) — when not the active bus master these are an inputs which determine the size of the operand being read or written by the Host. When the CD240 is a bus master these are an outputs determining the size of the operand being transferred to or from system memory.                                                                                                                                                                                |

| IACKIN          | 1           | I               | Interrupt Acknowledge IN — this input qualified with $\overline{\text{DS}}$ and A(0–7), acknowledges CD240 interrupts.                                                                                                                                                                                                                                                                                                                                       |

| IACKOUT         | 1           | 0               | Interrupt Acknowledge OUT — this output is driven low during interrupt acknowledge cycles for which no internal interrupt is valid.                                                                                                                                                                                                                                                                                                                          |

| IREQ(1–3)       | 3           | I/O, open-drain | $\overline{\text{Interrupt Request (1-3)} - \text{these outputs signal that the CD240 has a valid interrupt for modem lead activity [IREQ(1)], transmit activity [IREQ(2)], or receive activity [IREQ(3)].}$                                                                                                                                                                                                                                                 |

| BR              | 1           | O, open-drain   | Bus Request — this output is used to signal to the Host processor or bus arbiter that bus mastership is required by the CD240.                                                                                                                                                                                                                                                                                                                               |

| BGIN            | 1           | I               | $\overline{\text{Bus Grant IN}}$ — this input indicates that the bus is available after the current bus master relinquishes the bus.                                                                                                                                                                                                                                                                                                                         |

| BGOUT           | 1           | 0               | $\overline{\text{Bus Grant OUT}}$ — this output is asserted when $\overline{\text{BGIN}}$ is low and no internal Bus Request<br>has been made. A daisy chain scheme of bus arbitration can be formed by connecting<br>BGOUT to $\overline{\text{BGIN}}$ of the next device in the chain. If a priority scheme is preferred Bus<br>Requests must be prioritized externally and Bus Grant routed to the $\overline{\text{BGIN}}$ of the<br>appropriate device. |

| BGACK           | 1           | I/O, open-drain | Bus Grant Acknowledge — as an input this signal is used to determine if another bus master<br>is in control of the bus. As an output it signals to other bus masters that this device is in control<br>of the bus.                                                                                                                                                                                                                                           |

| BERR            | 1           | I               | Bus Error — if this input becomes active while the CD240 is a bus master the current bus cycle will be terminated, the bus relinquished and an interrupt generated to indicate the error to the Host processor.                                                                                                                                                                                                                                              |

| A(0-7)          | 8           | I/O, 3-state    | Address $(0-7)$ — when the CD240 is not a bus master these pins are inputs, used to determine<br>which registers are being accessed, or which interrupt is being acknowledged. When ADLD<br>is low A $(0-7)$ output address bits 8 through 15 for external latching. When the CD240 is a<br>bus master A $(0-7)$ output the least significant byte of the transfer address.                                                                                  |

CL - CD240

### **PIN DESCRIPTION** (Continued)

| Symbol                               | NUM     | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------------------------------------|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Microprocessor Interface (Continued) |         |              |                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| A/D(0–15)                            | 16      | I/O, 3-state | Address/Data (0–15) — when the CD240 is not a bus master these pins provide the 16 data bus for reading and writing to the CD240 registers. When ADLD is low A/D(0-provide the upper address bits A(16–31) for external latching. When the CD240 is a master A/D (0–15) provide a data bus for reading and writing to system memory.                                                                                |  |  |  |  |

| ADLD                                 | 1       | O, 3-state   | Address Load — is a strobe used to externally latch the upper portion of the system address bus $A(8-31)$ . While $\overline{ADLD}$ is low address bits 16 through 31 are available on $A/D(0-15)$ and address bits 8 through 15 on $A(0-7)$ .                                                                                                                                                                      |  |  |  |  |

| AEN                                  | 1       | O, 3-state   | Address Enable — this output is used to output enable the external address bus drivers during CD240 DMA cycles.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| DATDIR                               | 1       | O, 3-state   | $\overline{\text{Data Direction}}$ — this output is active when either the CD240 is a bus master or the $\overline{\text{CS}}$ pin is low. It is used to control the external data buffers, when low the buffers should be enabled in the CD240 to system bus direction.                                                                                                                                            |  |  |  |  |

| DATEN                                | 1       | O, 3-state   | $\overline{\text{Data Enable}}$ — this output is active when either the CD240 is a bus master or the $\overline{\text{CS}}$ and $\overline{\text{AS}}$ pins are low. It is used to enable the external data bus buffers during Host register read/<br>write operations or during DMA operations. For operations on 32 bit buses this signal needs to be gated with A(1) to select the correct half of the data bus. |  |  |  |  |

| CLK                                  | 1       | I            | Clock — system clock.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| BUSCLK                               | 1       | 0            | Bus Clock — is the system clock divided by 2 which is used internally to control certain bus operations.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RESET                                | 1       | I            | Reset — asynchronously resets the CD240, should be active for a minimum of five clock periods. When RESET is removed the CD240 performs a software initialization of its registers.                                                                                                                                                                                                                                 |  |  |  |  |

| TEST                                 | 1       | I            | Test — this must be kept low at all times.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| INT/MOT                              | 1       | I            | This pin alters the byte ordering of data during 16-bit transfers to comply with that used<br>in Intel or Motorola processors, it does not alter the bus handshake signals. A different<br>register map is used depending on the state of this pin.                                                                                                                                                                 |  |  |  |  |

| <b>Communications Int</b>            | terface |              |                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| RTS(0-3)                             | 4       | 0            | Request to Send (0-3).                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| TXCOUT/DTR(0-3)                      | 4       | 0            | Transmit Clock OUT/Data Terminal Ready (0-3) — user selectable via the MSVR-DTR register.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CTS (0-3)                            | 4       | I            | Clear to Send (0-3).                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TXCIN/CD(0-3)                        | 4       | I            | Transmit Clock IN/Carrier Detect (0-3) — when used as transmit clock the state of the pin is still available in the MSVR register.                                                                                                                                                                                                                                                                                  |  |  |  |  |

| RXCIN/DSR(0-3)                       | 4       | I            | Receive Clock IN/Data Set Ready (0-3) — when used as receive clock the state of the pin is still available in the MSVR register.                                                                                                                                                                                                                                                                                    |  |  |  |  |

| TXD(0-3)                             | 4       | 0            | Transmit Data (0-3) — serial data output for each channel.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| RXD(0-3)                             | 4       | I            | Receive Data (0-3) — serial data input for each channel.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

Advance product information describes products which are in development, or are subject to developmental changes. CIRRUS LOGIC believes the information contained in this document is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by CIRRUS LOGIC for its use; nor for the infringements of patents or other rights of third parties. This document implies no license under patents or copyrights, other than those explicitly stated.

CIRRUS LOGIC, Inc., 1463 Centre Pointe Drive, Milpitas, CA 95035 PHONE 408.945.8300 FAX 408.263.5682 TLX 171918 CIRRUS LOGIC, and S/LA are trademarks of CIRRUS LOGIC, Inc. © Copyright, CIRRUS LOGIC, Inc. 1989