**CL-CD1190**

**Preliminary** Data Sheet

# FEATURES

- Centronics<sup>®</sup>- and Dataproducts<sup>®</sup>- compatible

- Up to 250 kbytes/second transfer rate

- 128-byte FIFO

- Improved interrupt schemes

- Vectored interrupt to allow jump into service routine

- Interrupt on FIFO threshold

- Interrupts on timer expiration and external status, e.g., PAPER EMPTY, ERROR, TIMEOUT, etc.

- Programmable FiFO threshold for receive and transmit

- Bi-directional operation

- Independent general-purpose timer

- Multiple CL-CD1190s can be cascaded using interrupt daisy chain scheme

- Programmable strobe and acknowledge widths from 0.8 μs to 50 μs

- Six general-purpose I/O pins

Three inputs and three outputs

#### **Other Features**

- Local loopback capability

- System clock up to 20 MHz

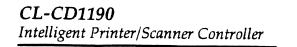

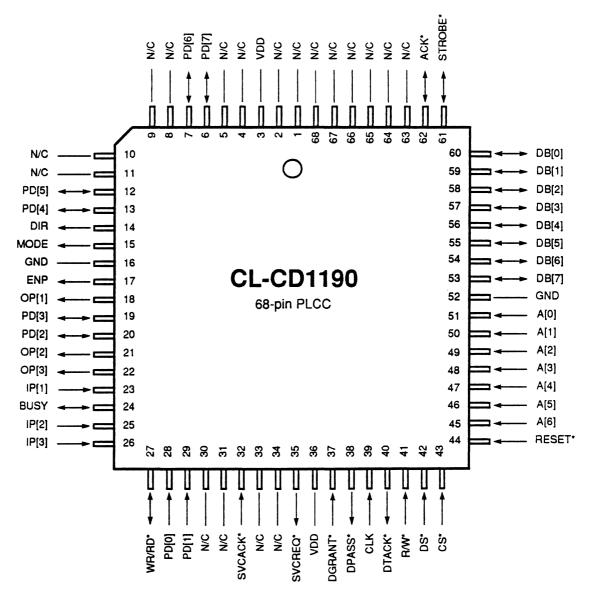

- Packaged in 68-pin PLCC

- Pin-compatible with CL-CD1400

- Advanced, low-power CMOS process technology

# Intelligent Printer/Scanner Interface Controller

# OVERVIEW

The CL-CD1190 is an intelligent, high-speed interface for bi-directional parallel transfers at rates up to 250 kbytes/second. It is a flexible, buffered interface controller for parallel data transfer to and from printers and scanners. A 128-byte FIFO greatly reduces host overhead, while providing the necessary logic for both the parallel interface and an interrupt or polled host interface. It also provides a flexible parallel interface compatible with industry-standard specifications like those used on Centronics and Dataproducts high-speed line printers.

The standard interface has been extended within the CL-CD1190 to include a bi-directional capability to accommodate devices such as optical page scanners. The device is flexible enough to be used on either the controller or peripheral side of the parallel interface, providing a high-speed solution for both controller and peripheral manufacturers.

(cont. next page)

DRAF

# OVERVIEW (cont.)

Two CL-CD1190s can be connected in tandem to provide a simple but fast bi-directional interface between two host systems.

The most important advantage of using the CL-CD1190 is the reduction in CPU overhead. It automatically handles the handshake signals, and the deep FIFO allows the host to transfer up to 128 bytes without further intervention. The CL-CD1190 can operate in either an interrupt-driven or polled environment, thus providing complete flexibility in system implementation.

To accommodate a variety of end applications, the CL-CD1190 provides programmable strobe and acknowledge pulse widths that can be varied from 800 ns to 50  $\mu$ s (based on a 20 MHz system clock) in 200 ns increments.

By automatically controlling all data transfers on the parallel channel, the CL-CD1190 will, for example, generate an interrupt when its FIFO is empty during send operations. The host can then transfer up to 128

bytes directly to the controller at full bus speed. The CL-CD1190 will place the first byte on the printer interface pins, assert STROBE\* and wait for ACK\*. When it receives ACK\*, it will place the next byte on the interface pins and repeat the process. It will continue this until the FIFO is empty, and then generate another interrupt to the host.

The CL-CD1190 does not need host support when data is being moved from the FIFO to the parallel pins, thus freeing the host to perform other functions.

Depending on the system clock frequency, the mode of operation (controller/peripheral), the direction (input/output), and the programmed duration of the handshake signals, the CL-CD1190 can sustain data transfer rates of up to 250 kbytes per second.

The CL-CD1190 is fabricated using an advanced low-power CMOS technology. The device operates on a 20 MHz system clock and is packaged in a 68pin PLCC.

#### Industry Standard Compatibility

| CL-CD1190                                                                    | Centronics<br>Peripheral                                              | Dataproducts<br>Peripheral                                             | Hewlett Packard<br>Controller                                                                            |  |  |  |  |  |  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Data Signals                                                                 |                                                                       |                                                                        |                                                                                                          |  |  |  |  |  |  |

| PD0-VO<br>PD1-VO<br>PD2-VO<br>PD3-VO<br>PD4-VO<br>PD5-VO<br>PD5-VO<br>PD7-VO | D1-I<br>D2-I<br>D3-I<br>D4-I<br>D5-I<br>D6-I<br>D7-I<br>D8-I-optional | D 1-1<br>D2-1<br>D3-1<br>D4-1<br>D5-1<br>D6-1<br>D7-1<br>D8-1-optional | DATA1-VO<br>DATA2-VO<br>DATA3-VO<br>DATA4-VO<br>DATA5-VO<br>DATA5-VO<br>DATA6-VO<br>DATA7-VO<br>DATA8-VO |  |  |  |  |  |  |

| Control Signals                                                              |                                                                       | ·                                                                      |                                                                                                          |  |  |  |  |  |  |

| BUSY-1/0<br>STROBE*-1/0<br>WR/RD*-1/0<br>ACK*-1/0                            | BUSY-0<br>STROBE'-I<br><br>ACKNLG'-0                                  | READY-O<br>STROBE"-I<br><br>DEMAND"-O                                  | BUSY-VO<br>nSTROBE-VO<br>WR/RD*-O<br>nACKNLG-I                                                           |  |  |  |  |  |  |

| Auxiliary Control                                                            | Auxiliary Control Signals                                             |                                                                        |                                                                                                          |  |  |  |  |  |  |

| IP [1,2,3]<br>OP [1,2,3]<br>—<br>ENP,<br>MODE, DIR                           | FAULT'-0<br>PE-0<br>SLCT-0<br><br>INPUT-PRIME'-1                      | PARITY-ERROR*-0<br>PAPER-0<br>ON-LINE-0<br>INPUT-PRIME*-1<br>—         | nFAULT-I<br>ERROR-I<br>SELECT-I<br>nRESET*-O<br>nSELECTIN-O                                              |  |  |  |  |  |  |

NOTE: The auxilliary signals shown above indicate possible uses and connections for the IP and OP signal groups, as well as the Enabled, Mode and Direction signals. There is not a one-to-one correlation.

2

# Table of Contents

| 1. | PIN         | INFORMATION                                                            | 5  |

|----|-------------|------------------------------------------------------------------------|----|

|    | 1.1         | Pin Diagram — Top View                                                 | 5  |

|    | 1.2         | Pin Functions                                                          | 6  |

|    | 1.3         | Pin List                                                               | 6  |

|    | 1.4         | Pin Descriptions                                                       | 7  |

| 2. | FUN         | NCTIONAL DESCRIPTION                                                   | 11 |

|    | 2.1         | Device Architecture                                                    | 11 |

|    | 2.2         | Host Interface                                                         | 11 |

|    |             | 2.2.1 Host Read Cycles                                                 | 12 |

|    |             | 2.2.2 Host Write Cycles                                                |    |

|    |             | 2.2.3 Host Service Acknowledge Cycles                                  |    |

|    | 2.3         | Service Requests and Interrupts                                        |    |

|    |             | 2.3.1 Service Pending Flag and End of Service Register (ESR)           |    |

|    |             | 2.3.2 Multiple-CL-CD1190s and the Interrupt Daisy Chain                |    |

|    |             | 2.3.3 Polled Mode Operations                                           |    |

|    | 2.4         | Timer Operations                                                       |    |

|    |             | 2.4.1 The Prescale Counter                                             |    |

|    |             | 2.4.2 The General-Purpose Timer                                        |    |

|    | 2.5         | FIFO Operations                                                        |    |

|    |             | 2.5.1 Input Transfer Modes                                             |    |

|    |             | 2.5.2 Output Transfer Modes                                            |    |

|    |             | 2.5.3 FIFO Loopback Test                                               |    |

|    | 0.0         | 2.5.4 Terminology — Controllers, Peripherals and Hosts                 |    |

|    | 2.0         | Parallel Interface — Theory of Operation                               |    |

|    |             | <ul> <li>2.6.1 History — The Centronics Specification</li></ul>        |    |

|    |             | 2.6.3 Protocol                                                         |    |

|    |             | 2.6.4 Changing Directions                                              |    |

|    |             | 2.6.5 CL-CD1190 Modes of Operation                                     |    |

|    |             | 2.6.6 Controller Output Mode                                           |    |

|    |             | 2.6.7 Controller Input Mode                                            |    |

|    |             | 2.6.8 Peripheral Output Mode                                           |    |

|    |             | 2.6.9 Peripheral Input Mode                                            |    |

|    | 27          | Hardware Configurations                                                |    |

|    | <b>E</b> .1 | 2.7.1 Interfacing an Intel Microprocessor-Based System                 |    |

|    |             | 2.7.2 Interfacing a Motorola Microprocessor-Based System               |    |

|    |             | 2.7.3 Interfacing a National Semiconductor Microprocessor-Based System |    |

| 3. |             | CD1190 PROGRAMMING                                                     |    |

| 0. |             | Overview                                                               |    |

|    |             | Initialization                                                         |    |

|    | 0.2         | 3.2.1 Chip Initialization                                              |    |

|    |             | 3.2.2 Global Function Initialization                                   |    |

|    | 3.3         | Program Examples                                                       |    |

|    | 0.0         | 3.3.1 Sample CD-1190 Initialization Routine                            |    |

|    |             | 3.3.2 Sample Output Interrupt Transfer Routine                         |    |

|    |             | 3.3.3 Sample Input Interrupt Transfer Routine                          |    |

|    |             | 1 1                                                                    |    |

5

٠

# Table of Contents (cont.)

| 4. | REGISTERS                                 |    |

|----|-------------------------------------------|----|

|    | 4.1 CL-CD1190 Register Map                |    |

|    | 4.2 Register Definitions — Overview       |    |

|    | 4.3 Detailed Register Descriptions        |    |

|    | 4.3.1 Virtual Registers                   |    |

| 5. | ELECTRICAL SPECIFICATIONS                 | 48 |

|    | 5.1 Absolute Maximum Ratings              | 48 |

|    | 5.2 Recommended Operating Conditions      |    |

|    | 5.3 DC Electrical Characteristics         |    |

|    | 5.4 AC Characteristics                    | 50 |

|    | 5.4.1 Index of Timing Information         | 50 |

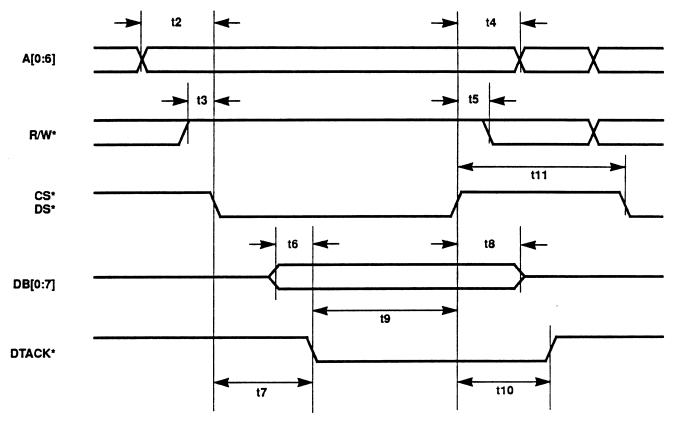

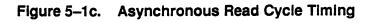

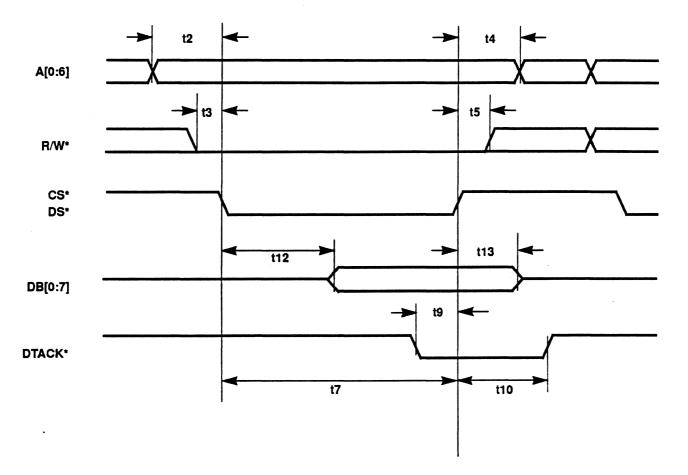

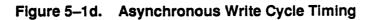

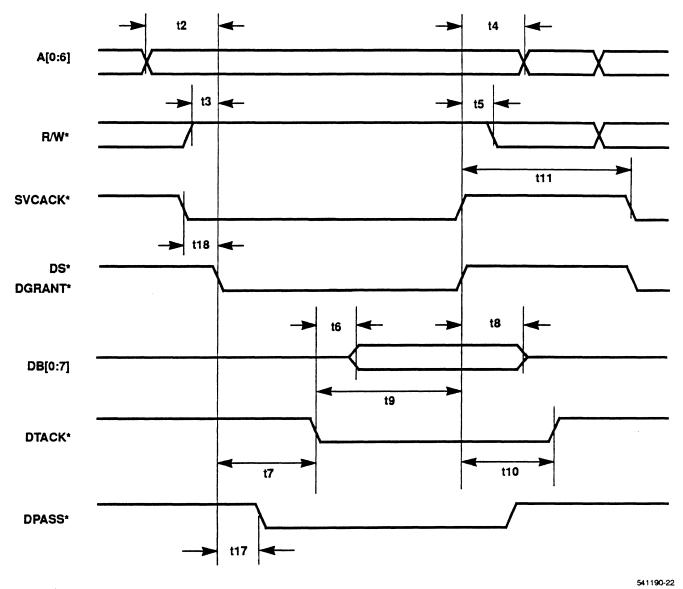

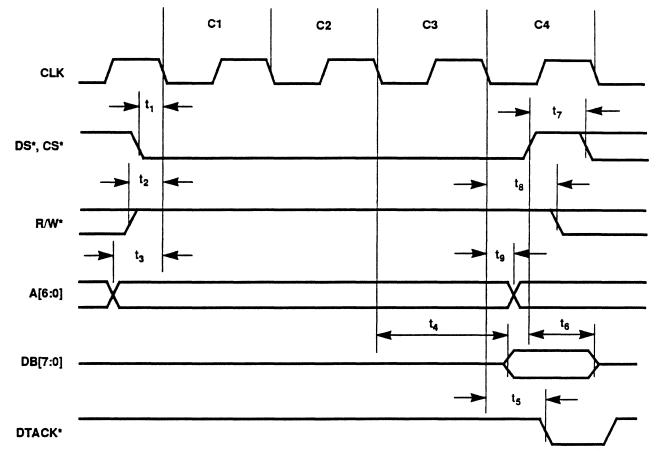

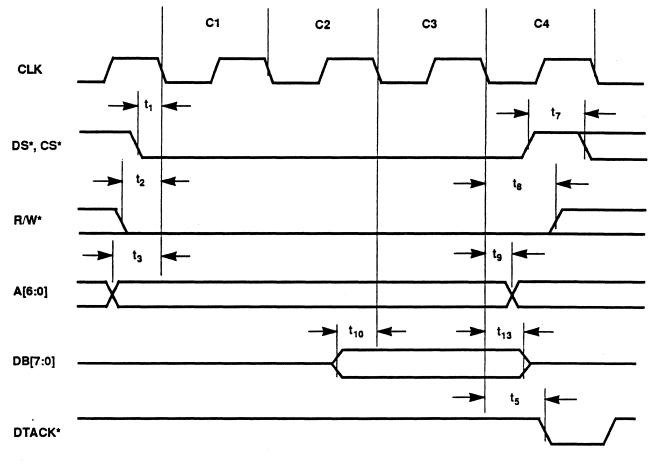

|    | 5.4.2 Asynchronous Timing                 | 51 |

|    | 5.4.3 Synchronous Timing                  |    |

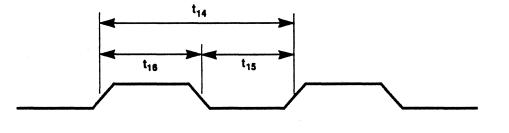

|    | 5.4.4 Parallel Port Timing Specifications | 60 |

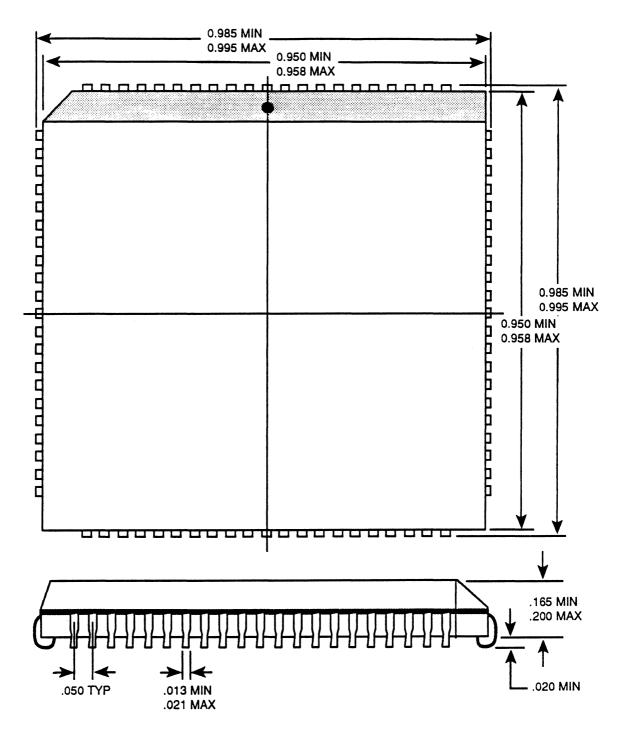

| 6. | PACKAGE DIMENSIONS — 68-Pin PLCC          | 65 |

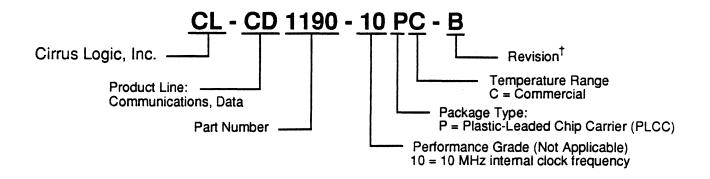

| 7. | ORDERING INFORMATION                      | 66 |

| 8. | QUICK REFERENCE                           | 67 |

|    | 8.1 Pin Diagram — Top View                | 67 |

|    | 8.2 CL-CD1190 Register Map                |    |

|    | 8.3 Bit Definitions                       |    |

## **List of Figures**

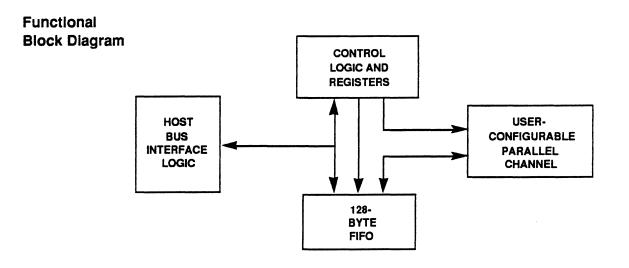

| Figure 2–1.  | Functional Block Diagram                                 |    |

|--------------|----------------------------------------------------------|----|

| Figure 2–2.  | Compressed Address Connections                           | 12 |

| Figure 2–3.  | Control Signal Configuration                             |    |

| Figure 2-4.  | Daisy-Chain Connections                                  | 14 |

| Figure 2-5.  | Timing Period ('Tick') Generation                        |    |

| Figure 2–6.  | General-Purpose Timer                                    | 17 |

| Figure 2–7.  | FIFO Timer                                               |    |

| Figure 2-8.  | CL-CD1190 Controller Output Mode                         | 20 |

| Figure 2–9.  | CL-CD1190 Controller Input Mode                          | 21 |

| Figure 2-10. | CL-CD1190 Peripheral Output Mode                         |    |

| Figure 2-11. | CL-CD1190 Peripheral Input Mode                          |    |

| Figure 2-12. | Intel 80X86 Family Interface                             |    |

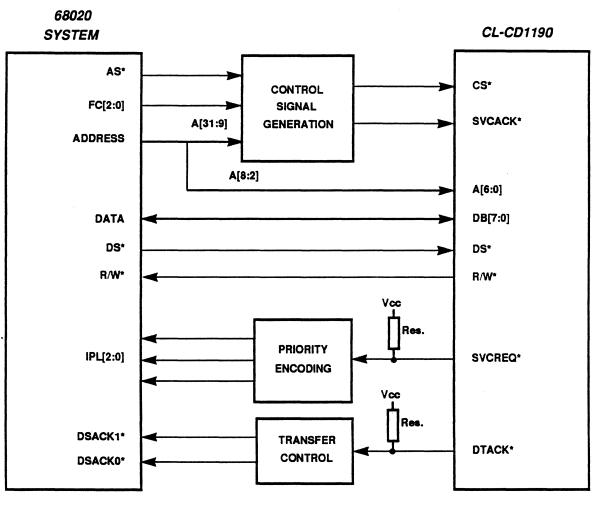

| Figure 2-13. | Motorola 68020 Interface                                 | 24 |

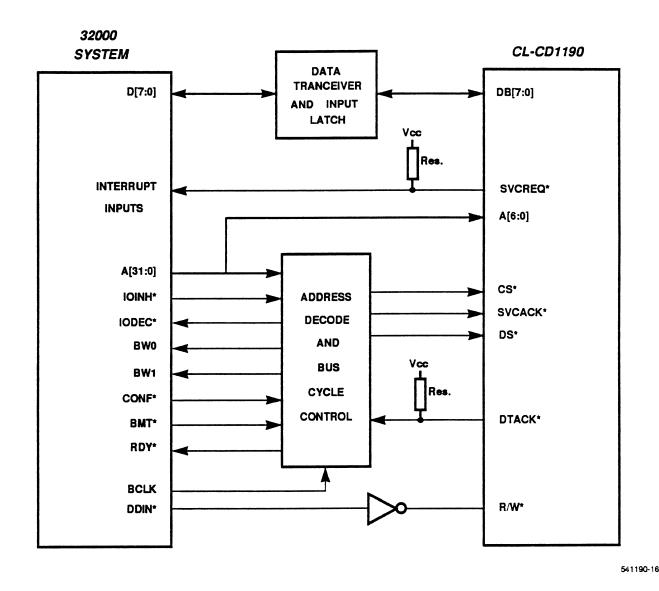

| Figure 2-14. | National 32000 Interface                                 |    |

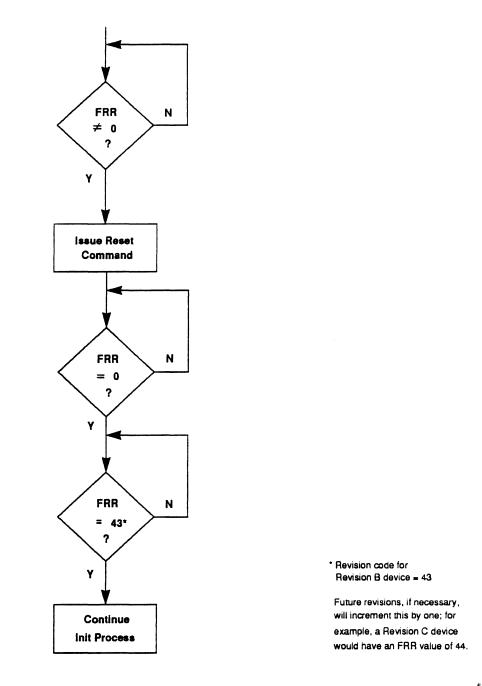

| Figure 3-1.  | Flow Diagram of CL-CD1190 Master Initialization Sequence |    |

### **1. PIN INFORMATION**

DRAFT

541190-1

#### NOTES: N/C means no connection.

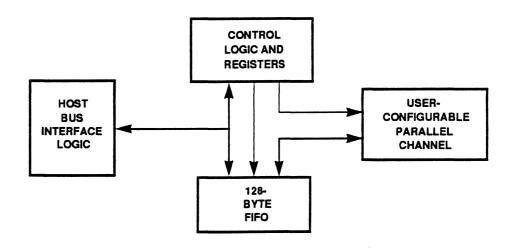

To reduce address space, A[4] can be tied to ground, and A[6] and A[5] can be tied together; therefore, only 32 address locations are occupied.

## **1.2 Pin Functions**

541190-2

#### 1.3 Pin List

6

The following conventions are used in the pin assignment tables: (\*) denotes an active-low signal; I = Input, I/O = Input/Output, O = Output, OD = Open Drain.

NOTE: All Open Drain outputs must be terminated to +5V through a 1K ohm resistor.

| Pin Name | DIR | # of Pins | Pin # | Pin Name | DIR | # of Pins | Pin #  |

|----------|-----|-----------|-------|----------|-----|-----------|--------|

| RESET*   | I   | 1         | 44    | IP[3]    | 1   | 1         | 26     |

| CLK      | 1   | 1         | 39    | IP[2]    | 1   | 1         | 25     |

| CS*      | 1   | 1         | 43    | IP[1]    | I   | 1         | 23     |

| DS*      | 1   | 1         | 42    | BUSY     | 1/0 | 1         | 24     |

| R/W*     | I   | 1         | 41    | WR/RD*   | I/O | 1         | 27     |

| DTACK*   | OD  | 1         | 40    | MODE     | Ö   | 1         | 15     |

| A[6:0]   | 1   | 7         | 45-51 | ENP      | 0   | 1         | 17     |

| DB[7:0]  | I/O | 8         | 53-60 | DIR      | 0   | 1         | 14     |

| SVCREQ*  | OD  | 1         | 35    | PD[0]    | 1/0 | 1         | 28     |

| SVCACK*  | I   | 1         | 32    | PD[1]    | 1/0 | 1         | 29     |

| DGRANT"  | I   | 1         | 37    | PD[2]    | 1/0 | 1         | 20     |

| DPASS*   | 0   | 1         | 38    | PD[3]    | I/O | 1         | 19     |

| STROBE*  | 1/0 | 1         | 61    | PD[4]    | I/O | 1         | 13     |

| ACK*     | I/O | 1         | 62    | PD[5]    | 1/0 | 1         | 12     |

| OP[3]    | 0   | 1         | 22    | PD[6]    | 1/O | 1         | 7      |

| OP[2]    | 0   | 1         | 21    | PD[7]    | 1/0 | 1         | 6      |

| OP[1]    | 0   | 1         | 18    | Vcc      |     | 2         | 3, 36  |

|          |     |           |       | GND      |     | 2         | 16, 52 |

September 1991

# CL-CD1190

Intelligent Printer/Scanner Controller

## 1.4 Pin Descriptions

| Symbol  | Pin Number | Туре  | Description                                                                                                                                                                                                                                                                                                                                       |

|---------|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET*  | 44         | Ι     | <b>RESET</b> : This signal asynchronously resets the CL-CD1190.<br>RESET must be active for a minimum of ten system clocks.<br>When RESET is removed, the CL-CD1190 will perform a soft-<br>ware initialization of its registers, disable all transmitters and<br>receivers, and when complete, place the firmware revision<br>number in the FRR. |

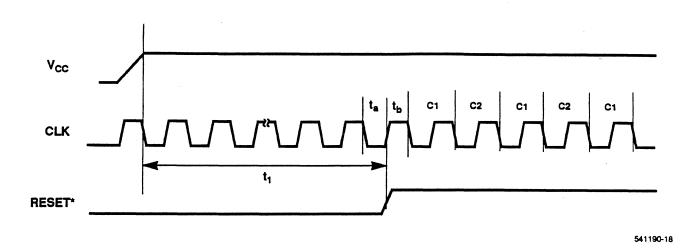

| CLK     | 39         | I     | <b>CLOCK</b> : (System Clock). The CL-CD1190 requires a nominal 20 MHz clock for proper operation. The system clock is divided by two, internally, to generate all on-chip timing clocks.                                                                                                                                                         |

| CS*     | 43         | I     | CHIP SELECT: When active, CS*, in conjunction with DS*, ini-<br>tiates a host I/O cycle with the CL-CD1190.                                                                                                                                                                                                                                       |

| DS*     | 42         | I     | <b>DATA STROBE</b> : During an active I/O cycle, DS* strobes data into on-chip registers during a write cycle or enables data onto the data bus during read cycles.                                                                                                                                                                               |

| R/W*    | 41         | I     | <b>READ/WRITE</b> : R/W* sets the direction of the data transfer be-<br>tween the host and the CL-CD1190. When high, the cycle is a<br>read cycle, and when low it is a write cycle. This signal should<br>not be confused with the WR/RD* Signal, which controls the di-<br>rection of the parallel interface.                                   |

| DTACK*  | 40         | OD, O | <b>DATA TRANSFER ACKNOWLEDGE</b> : When the CL-CD1190 has completed internal operations associated with a host I/O cycle, it activates DTACK* to indicate the end of the cycle. The host may terminate the cycle as soon as DTACK* becomes active.                                                                                                |

| A[6:0]  | 45-51      | 1     | ADDRESS[6:0]: These signals select the on-chip register be-<br>ing accessed during a host I/O cycle.                                                                                                                                                                                                                                              |

| DB[7:0] | 53-60      | 1/0   | <b>DATA BUS</b> [7:0]: These eight bidirectional signals are the data interface between the host and internal CL-CD1190 registers.                                                                                                                                                                                                                |

| SVCREQ* | 35         | OD, O | SERVICE REQUEST: When the CL-CD1190 needs host service, it activates this signal.                                                                                                                                                                                                                                                                 |

| SVCACK* | 32         | Ι     | SERVICE ACKNOWLEDGE: The host activates this signal to<br>start an interrupt service. This starts a special-case read cycle,<br>during which the CL-CD1190 places the contents of the inter-<br>rupt vector register on the data bus. CS* is not activated during<br>a SVCACK* cycle.                                                             |

| DGRANT* | 37         | I     | <b>DAISY GRANT</b> : This input, qualified with DS* and a valid service acknowledge (SVCACK*), activates the CL-CD1190 interrupt service cycle.                                                                                                                                                                                                   |

September 1991

7

÷

# 1.4 Pin Descriptions (cont.)

| Symbol  | Pin Number | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPASS*  | 38         | 0    | <b>DAISY PASS</b> : This output is driven low when no valid service<br>request exists for the type of service acknowledge active. In<br>multiple-CL-CD1190 designs, this signal is normally connect-<br>ed to the proceeding CL-CD1190 DGRANT* output, forming<br>an interrupt acknowledge daisy chain.                                                                                                                                                                                                                                                                     |

| STROBE* | 61         | I/O  | <b>STROBE:</b> STROBE* indicates that data on the Parallel Data<br>Port (PD[7:0]) is ready. It is driven active after an appropriate<br>data setup time. Data is held for an appropriate hold time after<br>STROBE* is deactivated. STROBE* is a bi-directional signal;<br>when the CL-CD1190 is configured as a sender, it drives<br>STROBE*, and when it is a receiver, STROBE* is an input.                                                                                                                                                                              |

| ACK*    | 62         | I/O  | <b>ACKNOWLEDGE</b> : ACK* is a bidirectional signal. It indicates that the data transfer is complete. When the CL-CD1190 is a peripheral, it drives ACK* once it has taken the data on the parallel data port. When it is a controller, it uses ACK* as an indication that the peripheral has accepted the data.                                                                                                                                                                                                                                                            |

| BUSY    | 24         | I/O  | <b>BUSY</b> : BUSY is a bi-directional signal. It is an input when the CL-CD1190 is in one of the output modes. It is an output when it is in one of the input modes. During data input operations, the CL-CD1190 drives BUSY active after receiving the strobe from the sender. When it has taken the data, it deaserts BUSY. During data output operations, the state of BUSY is monitored and the CL-CD1190 will not assert STROBE* when BUSY is active.                                                                                                                 |

| WR/RD*  | 27         | I/O  | WRITE/READ*: The WR/RD* indicates the direction of the parallel data transfer. When the CL-CD1190 is in the Controller Mode, this signal is an output; when in the Peripheral Mode, it is an input. The state of the output is controlled by the value written into Bit 3 of the SCR Register when the CL-CD1190 is in Controller Mode. Bit 7 of the SCR always shows the current state of the WR/RD* Output, regardless of the enabled mode. This signal should not be confused with the R/W* Signal, which controls the direction of the data bus during host I/O cycles. |

# **1.4 Pin Descriptions** (cont.)

| Symbol                                                               | Pin Number                                 | Туре                                          | Description                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD[0]<br>PD[1]<br>PD[2]<br>PD[3]<br>PD[4]<br>PD[5]<br>PD[6]<br>PD[7] | 28<br>29<br>20<br>19<br>13<br>12<br>7<br>6 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | PARALLEL DATA 0<br>PARALLEL DATA 1<br>PARALLEL DATA 2<br>PARALLEL DATA 3<br>PARALLEL DATA 4<br>PARALLEL DATA 5<br>PARALLEL DATA 6<br>PARALLEL DATA 7                                                                                                                                         |

|                                                                      |                                            |                                               | These signals provide the eight-bit parallel data interface for<br>the CL-CD1190. Their direction is controlled by the current<br>mode of operation as set by the DIR Bit in the GCR Register.<br>(See the register descriptions for detailed information on reg-<br>ister bit assignments). |

| OP[1]<br>OP[2]<br>OP[3]                                              | 18<br>21<br>22                             | 000                                           | GENERAL-PURPOSE OUTPUT 1<br>GENERAL-PURPOSE OUTPUT 2<br>GENERAL-PURPOSE OUTPUT 3                                                                                                                                                                                                             |

|                                                                      |                                            |                                               | These three signals are general-purpose outputs. Their state<br>is controlled by the lower three bits of the SCR Register. (See<br>the register descriptions for detailed information on register bit<br>assignments).                                                                       |

| IP[1]<br>IP[2]<br>IP[3]                                              | 23<br>25<br>26                             | <br> <br>                                     | GENERAL-PURPOSE INPUT 1<br>GENERAL-PURPOSE INPUT 2<br>GENERAL-PURPOSE INPUT 3                                                                                                                                                                                                                |

|                                                                      |                                            |                                               | These three signals are general-purpose inputs. Their state can be monitored via the upper four bits of the SCR Register. (See the register descriptions for detailed information on register bit assignments).                                                                              |

| DIR                                                                  | 14                                         | 0                                             | DIRECTION OUTPUT                                                                                                                                                                                                                                                                             |

|                                                                      |                                            |                                               | The DIR Signal is provided to aid in the control of external buff-<br>ers. It is high for input and low for output and is a direct reflec-<br>tion of the DIR Bit in the GCR.                                                                                                                |

| ENP                                                                  | 17                                         | 0                                             | ENABLE PARALLEL TRANSFER                                                                                                                                                                                                                                                                     |

|                                                                      |                                            |                                               | ENP is an active-high output that indicates the current state of<br>the CL-CD1190. When the device is enabled for data transfers<br>via CCR command, this output will be high; otherwise, it will be<br>low.                                                                                 |

.

**1.4 Pin Descriptions** (cont.)

| Symbol | Pin Number | Туре | Description                                                                                                                                                                                                                                                           |

|--------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE   | 15         | 0    | <b>CONTROLLER/PERIPHERAL MODE</b> : This output indicates<br>the current mode of the CL-CD1190. When it is low, the CL-<br>CD1190 is in the Controller Mode; when high, it is programmed<br>as a peripheral. It is a direct reflection of the Mode Bit in the<br>GCR. |

· ÷

.

# 2. FUNCTIONAL DESCRIPTION

#### 2.1 Device Architecture

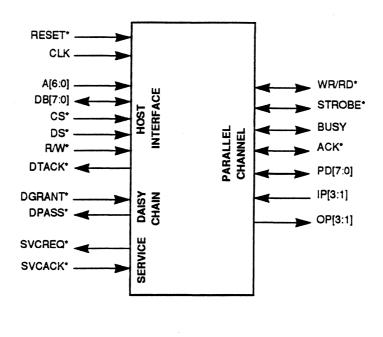

The CL-CD1190 consists of four main functional blocks, as shown in Figure 2-1. These are the host interface, the parallel port interface, a 128-byte FIFO and control logic. The host bus interface block controls and sequences host I/O activity, arbitrating accesses between the host and internal logic preventing clashes between the two. The FIFO is made up of a large static RAM array, with pointers and thresholds managed by the control logic block. In addition to FIFO management, the control block also performs the necessary control of the parallel data port strobes and signals. The parallel port block provides all of the interface functions to allow the device to be connected to a variety of peripherals and controllers.

#### 2.2 Host Interface

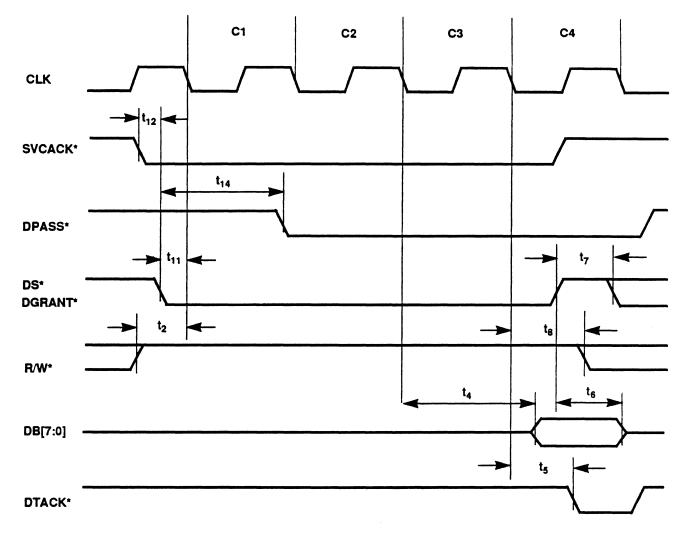

The host interface to the CL-CD1190 is made up of an 8-bit bidirectional data bus, a 7-bit address bus and various strobes that identify the type and direction of the I/O cycle that is taking place. Although the strobe names and basic timing are similar to that of the Motorola 68000 family, the CL-CD1190 easily fits into any CPU environment.

In most cases, when the host reads or writes an internal CL-CD1190 location, it actually accesses

a location in a RAM array that serves as a bank of registers. However, some locations are mapped to actual hardware resources, such as when a true signal value is required; an example is the current state of the WR/RD\* Pin in the Signal Control Register.

The CL-CD1190 is designed to be socket-compatible with the CL-CD1400; therefore, it has seven (7) address lines. The CL-CD1190, however, does not actually require an address space of this magnitude. The address space can be minimized by connecting the device, as shown in Figure 2-2 on the following page, and using the 'CA' (Compressed Address) values shown in Section 4.1, *CL-CD1190 Register Map*.

The CL-CD1190 is, by design, a synchronous device. All internal operations take place on edges and levels (phases) of the internal clock. Note that the internal clock is generated by dividing the external (system) clock by two. When the host performs an I/O cycle with the CL-CD1190, its strobes, address and data are sampled on falling edges of the internal clock. As can be seen in the timing diagrams in Section 5, external control signals must meet setup times with respect to clock edges. Once a cycle has started, the sequence of events is locked to the CL-CD1190 internal clock, with events (address setup, write data setup and read data available) occurring at predictable times.

#### Figure 2–1. CL-CD1190 Functional Block Diagram

11

541190-3

It is not necessary, however, to design a synchronous interface to the CL-CD1190. In an asynchronous design, the Data Transfer Acknowledge (DTACK\*) Signal is used as an indication that the CL-CD1190 has completed the requested data transfer. Thus, DTACK\* can be an input to wait state generation logic that will hold the host CPU until the operation is complete. If the strobes (Chip Select and Data Strobe - CS\* and DS\*) do not meet the minimum setup time with respect to a clock edge, the CL-CD1190 will not detect the I/O request, and the cycle will be delayed two full-system clock cycles, thus meeting the setup time. The I/O cycle will then commence and follow the synchronous timing, with DTACK<sup>\*</sup> signaling the end of the cycle.

#### 2.2.1 Host Read Cycles

Read cycles are initiated when the CL-CD1190 senses that both the CS\* and DS\* inputs are active and the Read/Write (R/W\*) Input is high. All strobes and address inputs must meet setup times as specified in the timing specifications in Section 3. It is important to note that *both* the CS\* and DS\* signals must be valid for a cycle to start, thus cycle times are measured from whichever of the two signals goes active *last*. The CL-CD1190 signals the fact that it has completed the read cycle (placing the data from the addressed register on the data bus pins) by activating the DTACK\* Signal. DTACK\* is released when the host removes CS\* or DS\*.

#### 2.2.2 Host Write Cycles

Write cycle timing and strobe activity is nearly identical to read cycles, except that the R/W\* Signal must be held low. Write data, strobes and address inputs must meet setup and hold times as specified in the timing diagrams in Section 3. Again, the DTACK\* Signal is used to indicate that the cycle is complete and the CL-CD1190 has taken the data. Removing either CS\* or DS\* releases DTACK\*.

#### 2.2.3 Host Service Acknowledge Cycles

Service acknowledge cycles are a special-case read cycle. Timing is basically the same as a normal read cycle, except that the SVCACK<sup>\*</sup> and DGRANT<sup>\*</sup> inputs are activated instead of the CS<sup>\*</sup> Input (a longer setup time is required on the SV-CACK<sup>\*</sup> Input than on the CS<sup>\*</sup> Input). The data that the CL-CD1190 provides during the read cycle is the contents of the Interrupt Vector Register. (See description of service request procedures later in this section). As in read and write cycles, DTACK<sup>\*</sup> will indicate the end of the cycle and removing DS<sup>\*</sup> releases DTACK<sup>\*</sup>.

#### 2.3 Service Requests and Interrupts

Four bits in the Interrupt Configuration Register (ICR) are used to specify the events that will cause the host to be notified. When an enabled event occurs, the CL-CD1190 initiates a Service

#### Figure 2–2. Compressed Address Connections

541190-4

Request. The cause of the request is recorded in the Interrupt Status Register (ISR), and an internal Service Pending Flag is set. If the IEN Bit in the ICR is set, indicating Interrupt Mode, the SVCREQ\* Pin will be asserted low. The host CPU becomes aware of the service request either by periodically reading the ISR, Polled Mode, or from the SVCREQ\* Signal via system interrupt logic. In Interrupt Mode, the host CPU responds with an interrupt acknowledge cycle that activates the SVCACK\* Pin. During the acknowledge cycle, the CL-CD1190 will present the contents of the Interrupt Vector Register (IVR) onto the data bus. The acknowledge cycle is not necessary when using Polled Mode. In either mode, the last action of the service request handler routine must be a write operation to the End of Service Register.

#### 2.3.1 Service Pending Flag and End of Service Register (ESR)

The Service Pending Flag is an internal flag used by the CL-CD1190 to keep track of whether a Service Request is in progress. The flag is invisible to the user, but its state does affect operation of the CL-CD1190. Once a Service Request is posted, there is no way of knowing exactly when the host will respond to it. If the CL-CD1190 attempts to update ISR after a request is posted, there could

be a collision between its access and that of the external host. If this occurs, status may be lost. To prevent this situation, the CL-CD1190 suspends certain operations while the Service Pending Flag is set.

During the time that this flag is set, the CL-CD1190 will stop sampling the general-purpose input pins to detect changes in their state. Since signal change detect is *not* intended to detect fast pulses (it is intended to detect conditions like 'paper empty'), a pause in sampling will not cause a problem; the change in level will be detected when sampling is resumed. The CL-CD1190 also stops threshold detection, but both functions are enabled again as soon as the Service Pending Flag is cleared by writing to the ESR at the end of a service routine.

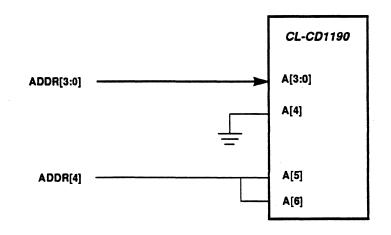

The CL-CD1190 starts its service acknowledge cycle when both DS\* and DGRANT\* are active together. If SVCREQ\* and SVCACK\* are both active before that time, then the CL-CD1190 will place its IVR contents on the data bus and assert DTACK\*. Otherwise, the CL-CD1190 will pass on the grant by asserting DPASS\*. When the grant is passed on, no DTACK\* will be asserted, and DPASS\* will remain active as long as the inputs stay unchanged.

Figure 2–3. Control Signal Configuration

13

The diagrams show SVCACK\* and DGRANT\* tied together. This can only be done if DS\* is guaranteed to be later than SVCACK\*. Otherwise, it is necessary to delay DGRANT\* until after SVCACK\*. See the timing diagrams in Section 5. Chip Select (CS\*) must remain inactive during the entire duration of a service acknowledge cycle.

A summary of Interrupt Mode service request actions is as follows:

- 1. CL-CD1190 asserts a low level on its SVCREQ\* Output Pin.

- 2. The host responds by performing an interrupt acknowledge cycle that activates the SVCACK\* Input Pin.

- 3. The host uses the value obtained from the Interrupt Vector Register during Step 2 if it is significant.

- 4. The host executes the interrupt handler routine (data transfer, etc.).

- 5. The host writes to the ESR to terminate the service and clear the service pending flag.

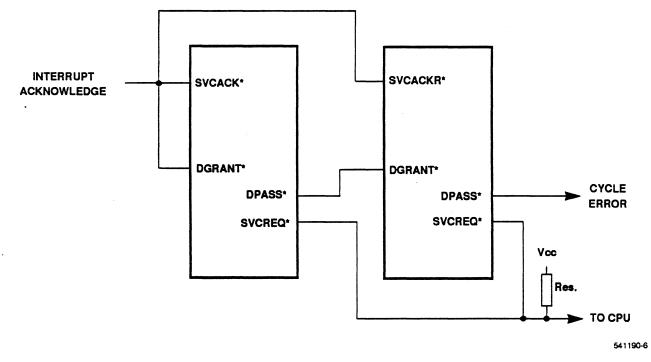

#### 2.3.2 Multiple CL-CD1190s and the Interrupt Daisy Chain

The CL-CD1190 provides a means of 'daisy chaining' the service acknowledgments of two or more devices together. Figure 2–4 shows how two CL-CD1190s would be connected. Priority is based on the position in the chain. The open-drain SVCREQ\* Outputs of the two devices are wire-ORed together to form one request. Similarly, the SVCACK\* Inputs are also connected together. The DPASS\* Output of the first CL-CD1190 drives the DGRANT\* Input of the second, forming the chain. The respective IVR of the two chips must be loaded with unique patterns, so the host will know which CL-CD1190 responded to the service acknowledge.

The DGRANT\* Input of the first CL-CD1190 may be connected to SVCACK\* if DS\* will be later than SVCACK\*. If not, then DGRANT\* must be delayed until after SVCACK\* is stable. On the second and subsequent devices, DGRANT\* will be propagated from previous CL-CD1190 DPASS\* Outputs, and thus DGRANT\* will always be later than SVCACK\*. See the timing diagrams in Section 5.

When the host acknowledges the request, both CL-CD1190s will receive the acknowledge via the SVCACK\* Input. However, only the first will receive the DGRANT\*. If it has an active SVCREQ\* request pending, it will take the acknowledge and drive its vector register onto the data bus.

If it does not have a request pending, it will pass the grant by asserting DPASS\*, which is connected to the second CL-CD1190 DGRANT\* Input. Assuming that the second has an active request pending, the second device will take the acknowledge and drive its vector register onto the data bus.

**CAUTION**: If neither CL-CD1190 has a pending request, the DPASS\* will be output by the second and neither will respond with DTACK\*, possibly causing the bus cycle to hang. The actual implementation is system-dependent; however, it is important for the designer to provide some way for the host to know that the cycle did not complete normally, if no device exists at the end of the chain.

#### 2.3.3 Polled-Mode Operations

In Polled Mode, the IEN Bit in the Interrupt Configuration Register is cleared so that the SVCREQ\* Pin will never be asserted. The host periodically checks the Interrupt Status Register (ISR) to see if there is any request for service pending. If the host detects a non-zero value in ISR, it should proceed by executing its service routine, thus clearing the cause of the service request. Once the service is complete, the operation should be followed by a write to the ESR Register.

In polled systems, the SVCREQ\*, SVCACK\* and DGRANT\* signals should all be terminated to Vcc through a 1K - 5K Ohm resistor. **Under no cir***cumstances should the SVCACK\* Input be activated if the SVCREQ\* Output is not active.* The DPASS\* Output will be asserted if SVCACK\*, DGRANT\* and DS\* inputs are active together. There is generally no need for a vector in a Polled Mode environment.

A summary of Polled Mode service request actions is as follows:

1. CL-CD1190 sets ISR bits according to the cause of the service request.

- 2. The host scans the ISR periodically, checking the INT Bit; if it is true ('1'), host service is requested.

- 3. The host performs a service-handler routine, (i.e., FIFO data transfer, if that is the source of the request).

- 4. The host writes to the ESR to terminate the service and clear the internal service pending flag.

#### 2.4 Timer Operations

The CL-CD1190 provides two on-chip timers utilized as follows: one general-purpose timer is used by the host system for any purpose; the other is used to set a maximum time that data will remain in the FIFO, if insufficient data is received to trigger the programmed FIFO threshold. Each of these timers is implemented as a two-stage counter.

#### 2.4.1 The Prescale Counter

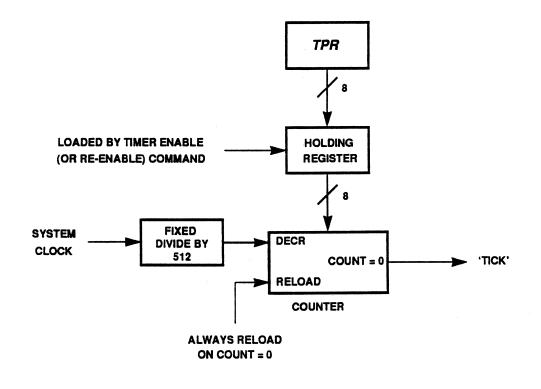

The first stage is common to both timers (see Figure 2–5). The CL-CD1190 input clock is divided by 512, and the resulting signal is used to decrement the prescale counter. The prescale counter is loaded from a holding register, whose value comes from the Timer Prescale Register (TPR).

Each time the prescale timer is decremented to zero, it is automatically reloaded from the holding register. A CCR command (timer enable) is required to update the holding register from the TPR. The output of the prescaler counter is called a 'tick', and it is used by the upper-level counters in both the general-purpose and data timers.

#### 2.4.2 The General-Purpose Timer

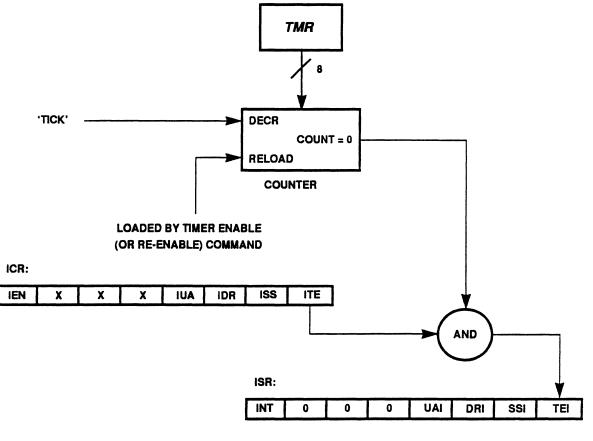

The period for the upper-level counter of the general-purpose timer is supplied by the user in the Timer Multiplier Register (TMR), as shown in Figure 2–6. This timer was designed for single timeouts and must be re-enabled via CCR command each time it needs to be started. The counter is loaded by the CCR timer enable command and decremented by the TPR tick. When the counter decrements to zero, a Timer Expired service request will be initiated if the ITE Bit in the Interrupt Configuration Register (ICR) is set.

September 1991

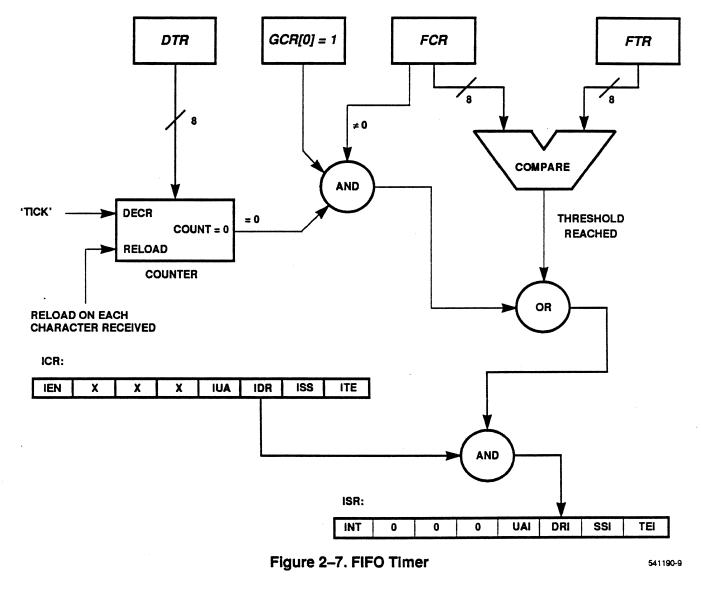

#### 2.4.3 The Data FIFO Timer

When receiving data from the parallel interface, it is possible that the end of the transfer will come before the FIFO threshold point is reached. The data timer is provided to force a Data Ready interrupt after a specified period of time.

The period for the upper level counter of this timer is supplied by the user in the Data Time-out Register (DTR). This timer is shown in Figure 4-11. The DTR counter is decremented by the TPR tick, and the counter is reloaded each time a new character is received from the parallel channel. If there are any data bytes waiting in the FIFO when counter decrements to zero, a Data Ready service request will be initiated, if IDR is enabled in the ICR.

#### 2.5 FIFO Operations

The CL-CD1190 contains a 128-byte FIFO for buffering data transfers. The FIFO Data Register (FDR) is the host interface end of the FIFO, and is a single location used for both input and output. FDR should only be accessed during a service request handler routine.

The FIFO Threshold Register (FTR) is used to set the point at which the CL-CD1190 informs the host that more space is left in the FIFO for additional data. Upon entering a service routine, the value in the FIFO Count Register (FCR) can be used to determine the minimum number of bytes available for transfer.

#### 2.5.1 Input Transfer Modes

When the number of bytes collected in the FIFO during input transfers becomes more than the value indicated by FTR Register, a Data Ready service request will be initiated, if the DRI Bit in the Interrupt Configuration Register (ICR) is set. In input modes, the value in the FCR is the number of bytes available to the host for reading.

When receiving data from the parallel interface, it is possible that the end of the transfer will come before the threshold point in FTR is reached. The

541190-7

16

Data Time-out Register (DTR) timer is provided to force a Data Ready interrupt after a specified period of time.

#### 2.5.2 Output Transfer Modes

When the number of bytes remaining in the FIFO during output transfers becomes less than the value indicated by FTR Register, a Data Ready service request will be initiated, if the DRI Bit in the ICR is set. In output modes, the value in the FCR is the number of bytes waiting to be sent. The number of open spaces available for writing by the host is: N = (128 - FCR) bytes. The DTR timer is not used in output modes.

#### 2.5.3 FIFO Loopback Test

This feature is provided for system diagnostics. It allows the host to test the entire data path through the interface controller to the CL-CD1190 FIFO. The data read back should be checked against

the data written, either directly or by checksum, etc. Comparison of individual bytes is necessary to verify that data was delivered in the correct order.

The following steps should be performed to execute the FIFO loopback test:

- 1. The host writes a CCR command with the PAR and FLUSH bits set.

- 2. Write 128 bytes to the FIFO Data Register (FDR).

- 3. Read 128 bytes from the FIFO Data Register.

- 4. Verify the data.

#### 2.6 Parallel Interface — Theory of Operation

This section describes the overall structure of the parallel interface, including some history and important terminology.

Figure 2-6. General-Purpose Timer

541190-8

# CL-CD1190 Intelligent Printer/Scanner Controller

#### 2.6.1 History — The Centronics Specification

The original Centronics specification described the interface for a parallel printer. This interface has become a de-facto industry standard and is widely used as the basis for parallel printer interfaces (with some modifications). It is limited, however, because the interface makes no provision for bidirectional operation. In addition, the maximum speed is limited by the timing requirements. Various companies have used simple modifications to the interface to enhance its capabilities. The CL-CD1190 is flexible enough to accommodate many of these modifications, including those used high-speed with

Dataproducts line printers and the fully bidirectional Hewlett Packard® Scan Jet™ Optical Page Scanner.

# 2.6.2 Terminology—Controllers, Peripherals and Hosts

In this data sheet, the terms controller and peripheral are used to identify the different modes under which the CL-CD1190 can operate. The controller is always the master of the interface and determines the direction of transfer. The normal direction of data flow is from the controller to the peripheral. The peripheral can only send data to the controller after it has been instructed to do so by the controller.

The term sender is used to indicate the device (in an output mode) transmitting data. Receiver means the device (in an input mode) to which the data is being sent. These terms are independent of the controller and peripheral. The host refers to any processor that has direct control of the CL-CD1190, regardless of whether the CL-CD1190 is acting as controller or peripheral.

#### 2.6.3 Control Signais

The mode of operation is set in the Global Configuration Register (GCR). The MODE and DIR pins reflect the values stored in the GCR; the ENP Pin is active when the CL-CD1190 is enabled for transfer. The direction and function of the four primary parallel control signals are affected by the current mode and direction of operation, controller or peripheral, and input or output. These signals are WR/RD\*, STROBE\*, BUSY, and ACK\*.

The controller determines the direction of transfer with the WR/RD\* Output. The peripheral uses this signal as an input to see which direction the controller expects data to flow. STROBE\* is always driven in the same direction as the data flow. It is driven by the sender to indicate that the data on the PD lines is ready for sampling. The receiver should use the STROBE\* pulse to latch the data. BUSY is the flow control signal. Its direction is always opposite to that of the STROBE\* Signal. A sender may not assert STROBE\* while the receiver has BUSY asserted. The ACK\* Signal is always driven by the peripheral. The ACK\* Signal is pulsed in response to a STROBE\*, or in response to a change in the state of the WR/RD\* Input. The response to STROBE\* is automatic, but the response to changing WR/RD\* requires host intervention, because the host must reprogram the GCR to change the direction of data transfer.

#### 2.6.4 Protocol

The CL-CD1190 provides the primitives necessary to construct a protocol that allows bidirectional transfers between the controller and the peripheral. A protocol is necessary because the parallel interface is half-duplex in nature. Data can only travel in one direction at a time. Some form of communication is required between the controller and peripheral to agree to change direction. Changing directions also requires host interven-

tion, to reconfigure the part for data transfer in the opposite direction. The transfer protocol is defined by the user.

#### 2.6.5 Changing Directions

When the controller host is ready to receive data from the peripheral, it can send a special character sequence that the peripheral host understands as a request for data. The controller then changes the WR/RD\* Pin to a low level to indicate that the peripheral can begin to send data back. The peripheral sends a pulse on the ACK\* Signal to confirm that the change of state of WR/RD\* was detected. The peripheral may send an unlimited amount of data, with a special character sequence to indicate the end of transmission. The controller will again change the state of WR/RD\* back to a high level, and the peripheral acknowledges this with an ACK\* pulse. The CL-CD1190 can detect these ACK\* pulses that are not part of the normal data transfer handshake in response to STROBE\*. These are called unsolicited acknowledges.

#### 2.6.6 CL-CD1190 Modes of Operation

The CL-CD1190 uses four basic modes of operation. The part can take on the role of either controller or peripheral. The controller is always the master of the interface and decides the direction of transfers. The peripheral is the slave, which performs as instructed by the master. In each of these two roles, the CL-CD1190 can transfer data in either direction. Thus the four basic modes are Controller Output, Controller Input, Peripheral Out, and Peripheral Input. There is a handshake option in Controller Output Mode, which creates a fifth mode called No Acknowledge Mode. The function and direction of the CL-CD1190 control signals depends on the mode into which the device is programmed.

Note that most if not all designs will fix the CL-CD1190 in either Controller or Peripheral Mode, depending upon the type of product in which the device is used. When the CL-CD1190 is built into a printer product, the device should be configured as a peripheral. If the CL-CD1190 is used in a controller product, it should be configured as a controller.

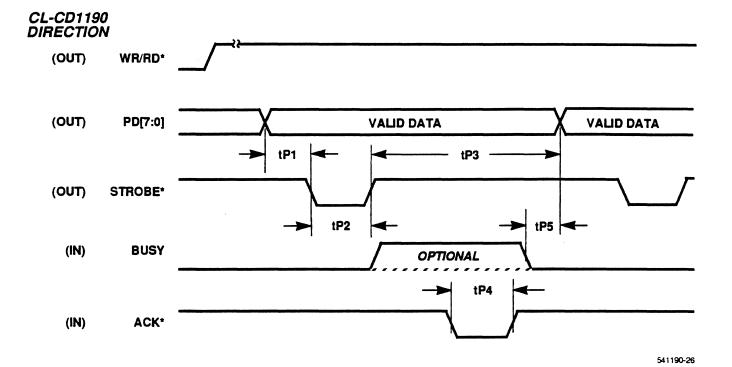

#### 2.6.7 Controller Output Mode

When the CL-CD1190 is configured for Controller Output Mode, it will send data whenever the part is enabled and there are one or more characters remaining in the FIFO. Service requests can be programmed to occur when the FIFO becomes empty or when a user-programmable threshold has been reached.

The CL-CD1190 sends data by placing each byte on the parallel data pins and asserting a pulse on the STROBE\* Signal. The setup time, hold time, and width of the STROBE\* pulse, are all equal, and this value is programmed into the SWR Register. The CL-CD1190 waits for the peripheral device to respond with a pulse on the ACK\* Input, which indicates that the data has been accepted. The peripheral device may also activate the BUSY Signal to indicate that it is busy and cannot accept any more data at this time. The CL-CD1190 will not assert another STROBE\* pulse while BUSY is high. Once ACK\* and BUSY have returned to their normal states, the CL-CD1190 will place the next data byte on the port (if the FIFO is not empty), and the cycle repeats.

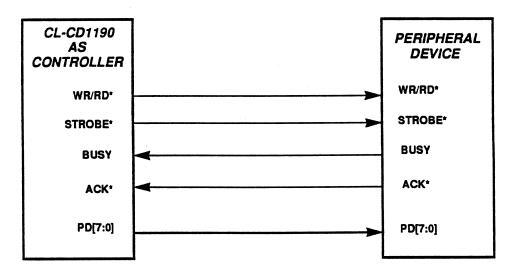

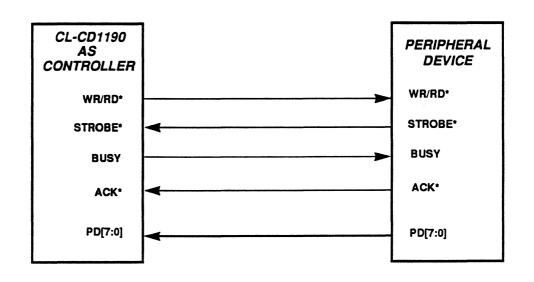

When the NOACK Bit in the GCR is set, the CL-CD1190 ignores ACK\*. In No Acknowledge Mode, only BUSY is used for handshake. Figure 2–8 shows a typical connection for a CL-CD1190 in Controller Output Mode, attached to a printer.

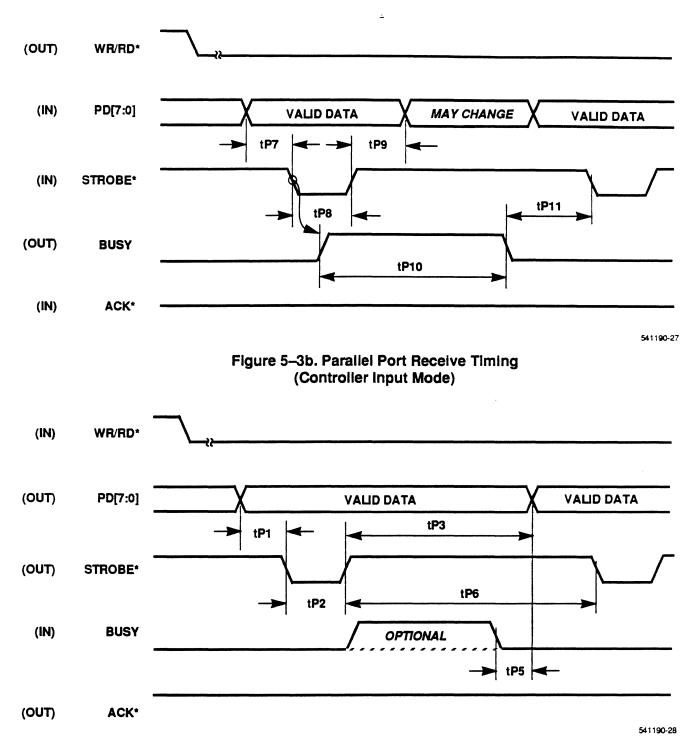

#### 2.6.8 Controller Input Mode

When the CL-CD1190 is configured for Controller Input Mode, it will accept data whenever the part is enabled and there are one or more character spaces remaining in the FIFO. Service requests can be programmed to occur when the FIFO becomes full or when the FIFO threshold has been reached.

The CL-CD1190 waits for incoming pulses on the STROBE\* Pin. Shortly after the falling edge of this signal, the data on the parallel port is sampled and copied to the FIFO. Only the BUSY Pin is used for handshake. The controller raises BUSY at the falling edge of STROBE\*, and lowers it when ready for the next data transfer. If the FIFO is full, BUSY will not be lowered until at least one byte is removed from the FIFO during a host service routine. The peripheral must not assert STROBE\* with new data until BUSY has been cleared.

The ACK<sup>\*</sup> Pin is an input when the CL-CD1190 is in Controller Mode, so this pin is not part of the normal transfer handshake in this mode. ACK<sup>\*</sup> is only used for the direction-change protocol.

541190-10

#### Figure 2–8. CL-CD1190 Controller Output Mode

September 1991

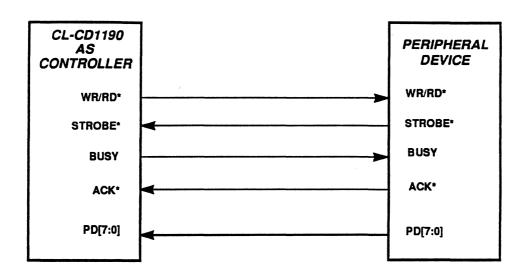

Figure 2–9 shows the connections between the CL-CD1190, acting as a controller, and a peripheral that sends data, such as a scanner.

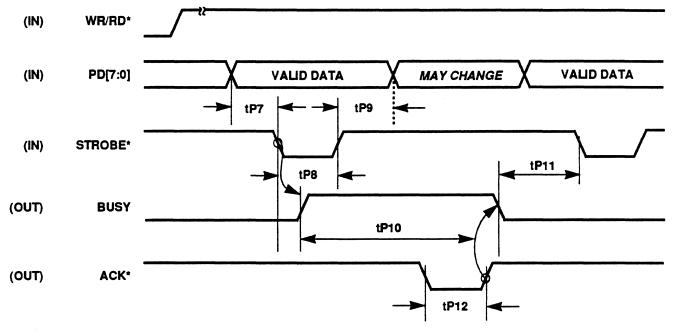

#### 2.6.9 Peripheral Output Mode

When the CL-CD1190 is configured in Peripheral Output Mode, operations are similar to Controller Output Mode, except that the ACK\* Pin is not used for data transfer handshaking; it is only used for the direction-change protocol. The peripheral host should examine the WR/RD\* Signal to verify that the controller expects the peripheral to send. The peripheral CL-CD1190 waits until BUSY is low and then asserts a pulse on the STROBE\* Output. The data setup time is identical to the width of STROBE\* and both are determined by the value in the SWR. The controller is expected to raise BUSY in response to the STROBE\*, but not to send an ACK\* pulse. The peripheral will not send new data with another STROBE\* until BUSY has returned to its low state.

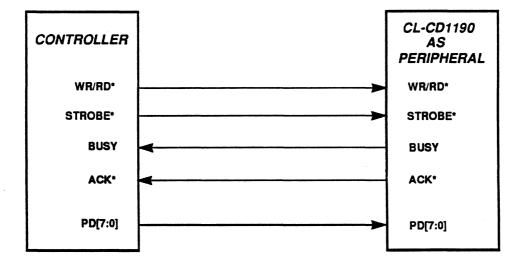

Figure 2–10, on the following page, shows the connections between a receiving controller and the CL-CD1190 in Peripheral Output Mode. The CL-CD1190 is acting as a sending device, such as a scanner.

#### 2.6.10 Peripheral Input Mode

The operation of the CL-CD1190 in Peripheral Input Mode is similar to the Controller Input Mode, except that the peripheral always responds to a STROBE\* pulse with a pulse on the ACK\* Signal. BUSY handshake is identical to Controller Input Mode.

The peripheral CL-CD1190 waits for an incoming STROBE\* pulse from the controller. The peripheral responds with a pulse on the ACK\* Output, which indicates that the data has been accepted, and by raising the BUSY Signal to indicate that it cannot accept any more data at this time. The controller must not assert another STROBE\* pulse while BUSY is high. Once the CL-CD1190 has processed the data, BUSY will be returned to its normal state, and the controller may send the next byte.

On the following page, Figure 2–11 shows the connections between the controller and the CL-CD1190 as a receiving device in a printer application.

#### Figure 2–9. CL-CD1190 Controller Input Mode

541190-11

541190-11

٠

.

Figure 2–10. CL-CD1190 Peripheral Output Mode

541190-13

#### Figure 2–11. CL-CD1190 Peripheral Input Mode

#### 2.7 Hardware Configurations

The simplicity of the host interface to the CL-CD1190 allows it to be built into systems making use of popular microprocessors, such as the Intel® 80X86 family (8086, 80286, 80386, etc.), the Motorola® family (68000, 68010, 68020, etc.), and the National® 32X32 family (32CG16, 32332, 32532, 32GX32, etc.).

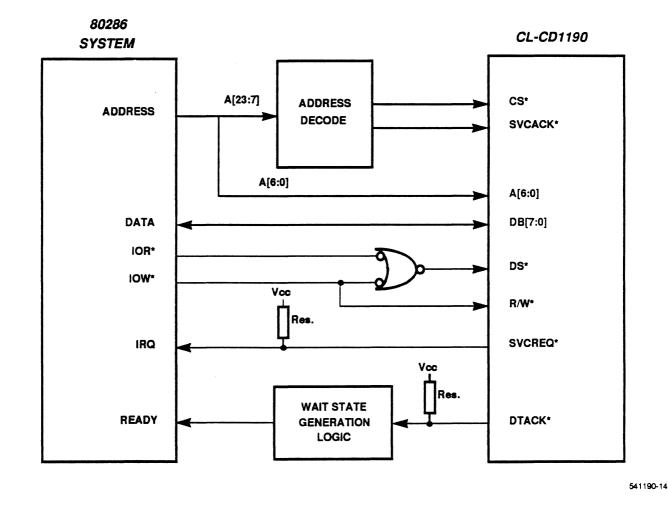

#### 2.7.1 Interfacing an Intel Microprocessor-Based System

With very little extra logic, the CL-CD1190 can interface any system based on a processor in the

Intel 80X86 family. The figure below shows a generalized view of an I/O-mapped interface with an 80286-based system. To provide the proper strobes and controls, the IOR\* and IOW\* control strobes are used to synthesize the DS\* and R/W\* signals. DTACK\* is used as an input to wait state generation logic that will hold the processor (if necessary until the CL-CD1190 has completed the I/O request.

Figure 2–12. Intel 80X86 Family Interface

Interfacing a 68000 family device is not difficult. The bus timing and the interface signal definitions very closely match those of the 68000 microprocessor, thus allowing direct connection in ٦

most cases. With later versions (68020, 68030), some additional logic is required to generate the DSACK0\* and DSACK1\* functions that replace the DTACK\* on the earlier devices. The example below is a generalized interface to a 68020 device.

541190-15

September 1991

#### 2.7.3 Interfacing a National Semiconductor Microprocessor-Based System

The connections between the CL-CD1190 and a NS32000 (32GX320, 32CG16, etc.) embedded controller are also relatively simple. As with the Intel devices, cycles are controlled by the DS, CS and R/W Signals that have been synthesized from the available I/O control signals and I/O cycle extensions (wait states) are generated by logic

connected to the DTACK Signal. Some additional consideration is required when implementing memory-mapped I/O to prevent multiple read and write cycles with the CL-CD1190 FIFOs due to the pipelined architecture of the 32000 device but all of the necessary controls are available.

The figure below depicts a simplified interface example.

Figure 2–14. National 32000 Interface

## 3. CL-CD1190 PROGRAMMING

#### 3.1 Overview

The CL-CD1190 host interface is made up of an large array of registers. These registers control aspects of chip behavior. Most of the registers will only be set up once, during initialization, and only rarely modified during normal operation. This section describes these aspects, as well as the methods of interacting with the CL-CD1190 for parallel service needs.

#### 3.2 Initialization

To operate a CL-CD1190, several procedures must be completed. These include chip initialization, programming global functions, such as interrupt vectors, and setting parallel port timing parameters. In most cases, initialization routines will only be executed once, during overall system boot-up. The following subsections describe these steps in detail.

#### 3.2.1 Chip Initialization

The chip reset procedures will normally be executed after a power-up or system-wide reset; therefore, the CL-CD1190 has performed its own internal initialization by the hardware reset control signal, RESET\*. However, it is a good practice to issue a software chip reset to verify completion prior to chip initialization. The following steps can be followed to accomplish this. (Figure 3–1 on the following page is a flow-chart version of the same steps).

- 1) Wait for FRR to become non-zero.

- 2) Write hexadecimal 81 (0x81) to the Channel Command Register (CCR).

This command causes the CL-CD1190 to perform a complete internal logic reset of all internal registers to their power-up reset values. The FIFO is flushed, and the port is disabled.

# 3) Wait for the firmware revision code to be written into the FRR.

This operation is used by the control logic to flag completion of the reset procedure. After reset, the FRR is one of the first registers to be cleared and is the last register set before normal operation begins. The initialization routine must wait for this register to become non-zero before beginning any other programming of CL-CD1190 registers. However, if the host code is sufficiently fast, it may begin testing the FRR before the control logic clears it; thus, one may assume that the CL-CD1190 has completed its internal initialization when, in fact, it has not. In order to avoid this error, the host software should look for the FRR to change to a zero and then to the current revision code. Alternatively, the host can clear the FRR just prior to issuing the global reset and then poll for the correct revision code. This would be useful in slow systems that cannot guarantee that the host will be able to check the register after it has been cleared, and before it is loaded with the revision code.

This procedure can also be used as part of a diagnostic test suite. The device will complete internal initialization within 500  $\mu$ sec (with a 20 MHz clock). Therefore, a timer (software or hardware) can be used to detect if the operation does not finish within this time and if the chip is functional or not.

#### 3.2.2 Global Function Initialization

Once chip reset has been completed, the next step is to set the global operating mode and other operational controls, such as timer period, strobe widths, etc.

1) Set the desired signal level on the WR/RD\* and general-purpose output (OP[2-0]) pins

The signal level of the WR/RD\* Output Pin must be set to the appropriate value, depending on the global operating mode (Controller Input, Controller Output). It may also be necessary to set the signal level of the general-purpose output port, depending on the design requirements.

All of these signal levels are set via the Signal Control Register (SCR). •

541190-17

### Figure 3–1. Flow Diagram of CL-CD1190 Master Initialization Sequence

September 1991

#### 2) Set Interrupt Vector Register

The interrupt vector value supplied by the CL-CD1190 during the acknowledge cycle is important if hardware service request/acknowledge cycles are employed. It should be loaded into the Interrupt Vector Register (IVR) during the initialization sequence.

#### 3) Set strobe widths

The Strobe Width (SWR) and Acknowledge Width (AWR) Registers are loaded with the appropriate value to generate the desired pulse widths. These registers can set a pulse width of any length, from 800 ns to 50  $\mu$ s in 200 ns increments; the minimum value is 4 and maximum value is 255.

# 4) Set the global configuration via the GCR and the CGC command of the CCR

The global configuration determines the mode of operation of the device. After reset, the GCR is set to all 0's. Thus, the CL-CD1190 defaults to the Controller Output Mode. If this is the intended mode for the device, nothing further needs to be done with this register. Otherwise, the mode must be set via the Control Bits (2-0). This is done by issuing the Change Global Configuration command to the CCR.

#### 5) Set the Timer Prescale Register (TPR)

The TPR sets the master time 'tick' for the CL-CD1190. It is a binary value that sets the constant by which the system clock is divided (after a fixed prescale of 512) to produce the internal clock for the on-chip timers (*not* the strobe and acknowledge pulse widths, however). This clock is used for FIFO time-out generation and the master clock that drives the on-chip timer. For example, to generate a timer clock of 1 ms, the value is computed as:

$\left(\frac{20\,MHz}{512}\right) \times 1\,ms = 39.0625$

The value 39 would be loaded into the TPR and, in effect, selects an approximate 1 KHz clock as the clock source for the timers. This register sets the value that will be loaded into the master timer each time it reaches zero.

This value of 39 is the recommended minimum value that should be placed in the TPR. Values that generate a time period of less than 1 ms adversely affect the performance of the device and, thus, overall data transfer performance.

#### 6) Set the Timer Multiplier (TMR) and Data Timeout (DTR) Registers

The TMR and DTR should be loaded with an appropriate value divisor to generate the desired time-out periods (timer and FIFO, respectively).

#### 3.3 Program Examples

This section provides some examples of CL-CD1190 programming. Included are a chip initialization sequence, and interrupt driven send and receive routines. All examples are written in Borland Turbo C $\otimes$  and should be easily converted to other versions of 'C' or other languages.

#### 3.3.1 Sample CL-CD1190 Initialization Routine

/\* This procedure initializes the CL-CD1190 for controller output mode with a low

\* FIFO threshold (16 bytes) for systems with a short interrupt response time

```

*/

```

void cd1190\_init

{

int i=0;

| outportb( SCR, 0x08 ); | /* set WR/RD*, op[3,2,1] low */                      |

|------------------------|------------------------------------------------------|

| outportb( IVR, 0x30 ); | /* set irq vector */                                 |

| outportb( ICR, 0x84 ); | /* data ready and master interrupts enabled */       |

| outportb( SWR, 0x08 ); | /* 1.6 $\mu s$ STROBE* width, assuming 20 MHz CLK */ |

| outportb( AWR, 0x08 ); | /* 1.6 µs ACK* width, assuming 20 MHz CLK */         |

| outportb( TPR, 39 );   | /* timer period (39 decimal = 1 ms) */               |

| outportb( TMR, 0x40 ); | /* timer multiplier */                               |

| outportb( SR0, 0 );    | /* disable transitions to zero */                    |

| outportb( SR1, 0 );    | /* disable transitions to one */                     |

| outportb( FTR, 0x10 ); | /* Threshold = 16 */                                 |

| outportb( DTR, 0x40 ); | /* data timer multiplier */                          |

outportb( GCR, CONJOUT ); /\* set controller output mode \*/

outportb( CCR, PAR | FLUSH | ENP | TIM|ENT );

/\* enable parallel transfers and timer \*/

while( inportb(CCR) != 0 ) /\* wait for CCR command to complete \*/

i++;

}

{

#### 3.3.2 Sample Output Interrupt Transfer Routine

/\* This is an example of a routine to service an output data interrupt request\*/

```

void interrupt cd1190_output()

int

i, ist, fcr, txn;

ist = inportb( ISR );

if(ist & DRI)

{

fcr = inportb(FCR);

/* FIFO Count Reg */

txn = 128 - fcr;

/* Number of chars to transmit */

for(i = 0; i < txn; i++)

if( bufpos < buflen )

{

outportb( FDR, outbuf[bufpos] );

bufpos++;

}

else

if(rotate)

/* Example loops on one buffer */

bufpos = 0;

/* Buffer management goes in this area */

else

{

outportb( ICR, 0 );

break;

}

}

outportb( ESR, 0 );

```

}

#### 3.3.3 Sample Input Interrupt Transfer Routine

/\* This is an example of a routine to service an input data interrupt request\*/

```

void interrupt cd1190_input()

{

int i, ist, fcr;

ist = inportb( ISR );

if(ist & DRI)

{

fcr = inportb( FCR );

/* read number of chars available in FIFO */

for(i = 0; i < fcr; i++)

{

if( bufpos > BUFSIZ )

/* Example uses only one buffer */

/* Buffer management goes in this area */

bufpos = 0;

inbuf[ bufpos ] = inportb( FDR );

bufpos++;

}

ł

outportb( ESR, 0 );

/* Write End Of Interrupt Register to terminate */

}

```

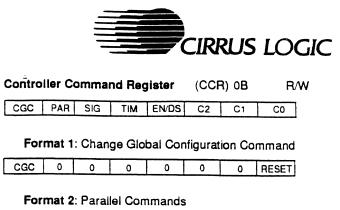

# 4. **REGISTERS**

All communication with the CL-CD1190 takes place through an array of registers. The tables on the following pages define the register symbols, names, read and write access modes, and the internal offset address for each register in the CL-CD1190; these are referenced to the A[6:0] inputs applied during a host I/O cycle. The offset address is shown in two ways: the absolute address as applied to all seven address inputs and a compressed address that is formed by connecting A[4] to ground and connecting A[6] and A[5] together. The compressed address allows the device address range to be reduced from occupying 128 consecutive address locations down to 32 address locations. This may be beneficial in some system applications. A detailed description of the host interface is presented in Section 2.

The detailed descriptions of register bit definitions and programming are presented in Section 4.3.

DRAF

Note that the addresses are shown relative to the CL-CD1190 definition of address lines. In 16- and 32bit systems, it is a common practice to connect 8-bit peripherals to only one byte lane. Thus, in 16-bit systems, the CL-CD1190 appears at every other address, that is, the CL-CD1190 A0 is connected to the host A1, etc. In 32-bit systems, the CL-CD1190 appears at every fourth address, that is, the CL-CD1190 A0 is connected to the host A2, etc. In either of these cases, the addresses used by the programmer will be different than what is shown.

For instance, in a 16-bit Motorola 68000-based system, the CL-CD1190 is placed on data lines D0-D7, which are at odd addresses in the Motorola manner of addressing. The CL-CD1190 A0 is connected to the 68000 A1, etc. Thus, CL-CD1190 address x'08 becomes x'11 to the programmer. It is 'left-shifted' 1 bit; and A0 must be '1'. for low-byte (D0-D7) accesses.

| Symbol | Register Name                 | R/W | A[6:0]   | (Hex) | (CA) <sup>1</sup> | Page <sup>2</sup> |

|--------|-------------------------------|-----|----------|-------|-------------------|-------------------|

| FRR    | Firmware Revision Register    | R/W | 000 1111 | 0F    | 0F                | 36                |

| GCR    | Global Configuration Register | R/W | 000 1010 | 0A    | 0 <b>A</b>        | 36                |

| CCR    | Controller Command Register   | R/W | 000 1011 | 0B    | 0B                | 37                |

| SWR    | STROBE* Width Register        | R/W | 000 0010 | 02    | 02                | 42                |

| AWR    | ACK* Width Register           | R/W | 000 0011 | 03    | 03                | 42                |

| TPR    | Timer Prescale Register       | R/W | 000 0100 | 04    | 04                | 42                |

| TMR    | Timer Multiplier Register     | R/W | 000 0101 | 05    | 05                | 42                |

| DTR    | Data Time-out Register        | R/W | 000 1001 | 09    | 09                | 43                |

| PSR    | Parallel Status Register      | R   | 110 1100 | 6C    | 1C                | 43                |

| SCR    | Signal Control Register       | R/W | 110 1110 | 6E    | 1E                | 43                |

| SR0    | Specification Register ZEROes | R/W | 000 0110 | 06    | 06                | 44                |

| SR1    | Specification Register ONEs   | R/W | 000 0111 | 07    | 07                | 44                |

| SSR    | Signal Status Register        | R/W | 000 1101 | 0D    | 0D                | 44                |

| IVR    | Interrupt Vector Register     | R/W | 000 0000 | 00    | 00                | 44                |

|        |                               |     |          |       |                   |                   |

#### 4.1 CL-CD1190 Register Map

September 1991

#### 4.1 CL-CD1190 Register Map (cont.)

| Symbol | Register Name                    | R/W | A[6:0]   | (Hex) | (CA) <sup>1</sup> | Page <sup>2</sup> |

|--------|----------------------------------|-----|----------|-------|-------------------|-------------------|

| ICR    | Interrupt Configuration Register | R/W | 000 0001 | 01    | 01                | 45                |

| ISR    | Interrupt Status Register        | R/W | 000 1100 | 0C    | 0C                | 45                |

| FCR    | FIFO Count Register              | R   | 000 1110 | 0E    | 0E                | 46                |

| FTR    | FIFO Threshold Register          | R/W | 000 1000 | 08    | 08                | 46                |

| FDR    | FIFO Data Register               | R/W | 110 0010 | 62    | 12                | 46                |

| ESR    | End Of Service Request Register  | W   | 110 0000 | 60    | 10                | 47                |

**NOTES:** 1)The column labeled CA in the tables above is the compressed address. See Section 2 for a description of device addressing.

2) The page numbers shown in the table indicate the page where the detailed description of the register can be located.

#### 4.2 Register Definitions — Overview

| Firmware F | nware Revision Register |                |             |            | (FRR) |           | Read/Write |       |

|------------|-------------------------|----------------|-------------|------------|-------|-----------|------------|-------|

|            | Firmware Revision Code  |                |             |            |       |           |            |       |

| Global Con | figura                  | ation Regis    | ster        | (          | (GCR) | <b>0A</b> | Read/      | Write |

|            | 0                       | 0              | 0           | 0          | 0     | NOACK     | MODE       | DIR   |

| Controller | Comn                    | nand Regis     | ster        | (          |       | 0B        | Read/Write |       |

| С          | GC                      | PAR            | SIG         | TIM        | EN/DS | C2        | C1         | CO    |

| Format     | 1: Ch                   | ange Globa     | I Configura | ation Comm | and   |           |            |       |

| С          | GC                      | 0              | 0           | 0          | 0     | 0         | 0          | RESET |

| Format     | 2: Pa                   | allel Comr     | nands       |            |       |           |            |       |

|            | 0                       | PAR            | x           | x          | ×     | DIP       | FLUSH      | ENP   |

| Format     | 3: Sig                  | nal Comma      | ands        |            |       |           |            |       |

|            | 0                       | 0              | SIG         | x          | X     | S_BSY     | ACK        | C_BSY |

| Format     | 4: Tirr                 | ner Comma      | nds         |            |       |           |            |       |