# **CL-GD5446**

64-Bit VisualMedia™ Accelerator

**Technical Reference Manual**

Second Edition

November 1996

**CL-GD5446 Extended Display Modes Summary**

| Mode<br>No. | VESA®<br>No. | Colors   | Display<br>Resolution | Chars.   | Refresh (Hz)            |

|-------------|--------------|----------|-----------------------|----------|-------------------------|

| 58, 6A      | 102          | 16/256K  | 800×600               | 100 × 37 | 56, 60, 72, 75          |

| 5C          | 103          | 256/256K | 800 × 600             | 100 × 37 | 56, 60, 72, 75, 85      |

| 5D          | 104          | 16/256K  | 1024 × 768            | 128 × 48 | 43ia, 60, 70, 72, 75    |

| 5E          | 100          | 256/256K | 640×400               | 80 × 25  | 70                      |

| 5F          | 101          | 256/256K | 640 × 480             | 80 × 30  | 60, 72, 75, 85          |

| 60          | 105          | 256/256K | 1024 × 768            | 128 × 48 | 43i, 60, 70, 72, 75, 85 |

| 64          | 111          | 64K      | 640 × 480             | -        | 60, 72, 75, 85          |

| 65          | 114          | 64K      | 800 × 600             | -        | 56, 60, 72, 75, 85      |

| 66          | 110          | 32K      | 640 × 480             |          | 60, 72, 75, 85          |

| 67          | 113          | 32K      | 800 × 600             | _        | 56, 60, 72, 75, 85      |

| 68          | 116          | 32K      | 1024 × 768            | _        | 43i, 60, 70, 75, 85     |

| 69          | 119          | 32K      | 1280 × 1024           | _        | 43i, 60                 |

| 6C          | 106          | 16/256K  | 1280 × 1024           | 160 × 64 | 43i                     |

| 6D          | 107          | 256/256K | 1280 × 1024           | 160 × 64 | 43i, 60, 75             |

| 71          | 112          | 16M      | 640 × 480             | _        | 60, 72, 75, 85          |

| 74          | 117          | 64K      | 1024 × 768            | _        | 43i, 60, 70, 75, 85     |

| 75          | 11A          | 64K      | 1280 × 1024           | _        | 43i                     |

| 78          | 115          | 16M      | 800 × 600             | _        | 56, 60, 72, 75, 85      |

| 79          | 118          | 16M      | 1024 × 768            | _        | 43i, 60, 70, 75, 85     |

| 7B          | -            | 256/256K | 1600 × 1200           | -        | 48i                     |

| 7C          | _            | 256/256K | 1152 × 864            | _        | 70, 75                  |

a. 'i' indicates interlaced.

Refer to Table 3-2, "Cirrus Logic Extended Display Modes," on page 3-25.

# **CL-GD5446**

# **Technical Reference Manual**

November 1996 Second Edition

### Notice

Cirrus Logic Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice. No responsibility is assumed by Cirrus Logic Inc. for the use of this information, nor for infringements of patents or other rights of third parties. Cirrus, Cirrus Logic, AccuPak, DIVA, FastPath, FasText, FeatureChips, Good Data, Laguna, Laguna3D, MediaDAC, MotionVideo, SimulSCAN, S/LA, SMASH, SofTarget, TextureJet, TVTap, UXART, VisualMedia, VPM, V-Port, Voyager, WavePort, and WebSet are trademarks of Cirrus Logic Inc., which may be registered in some jurisdictions. Other trademarks in this document belong to their respective companies. CRUS and Cirrus Logic International, Ltd. are trade names of Cirrus Logic Inc.

# **Copyright Notice**

This document is the property of Cirrus Logic Inc. and implies no license under patents, copyrights, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photographic, or otherwise, or used as the basis for manufacture or sale of any items without the prior written consent of Cirrus Logic Inc.

Copyright © 1995, 1996— Cirrus Logic, Inc. All rights reserved.

# **Contents**

# **Revision History**

The following are the differences between the December 1995 and November 1996 versions of this technical reference manual:

• Information pertaining to the Revision B device has been added

# **Table of Contents**

| 1. | INTF | RODUCTION                               | 1-2  |

|----|------|-----------------------------------------|------|

|    | 1.1  | Scope of Document                       | 1-2  |

|    | 1.2  | Chip Types Covered                      | 1-2  |

|    | 1.3  | Intended Audience                       | 1-2  |

|    | 1.4  | Conventions                             | 1-2  |

| 2. | OVE  | RVIEW                                   | 2-2  |

|    | 2.1  | Features                                | 2-2  |

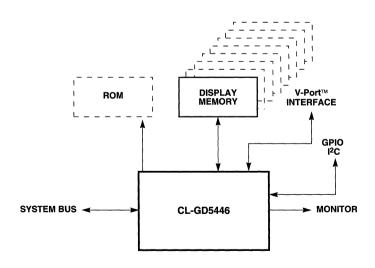

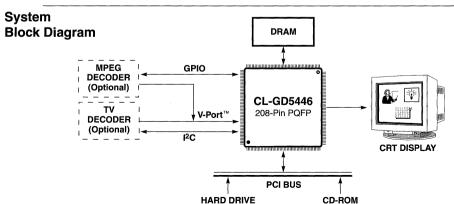

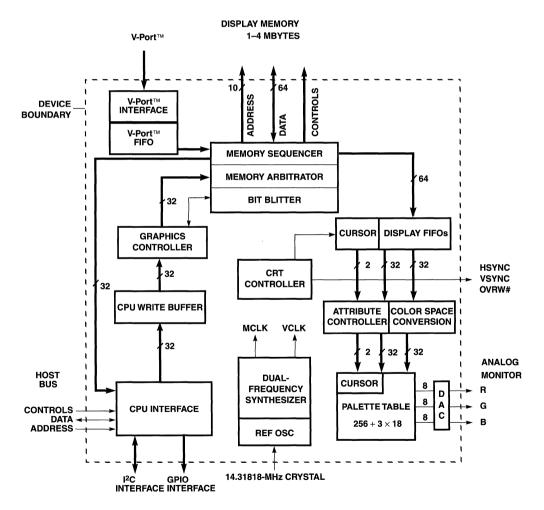

|    | 2.2  | Major Components                        | 2-4  |

|    | 2.3  | VGA Core                                |      |

|    | 2.4  | PCI Bus Interface                       | 2-12 |

|    | 2.5  | BitBLT Engine                           | 2-12 |

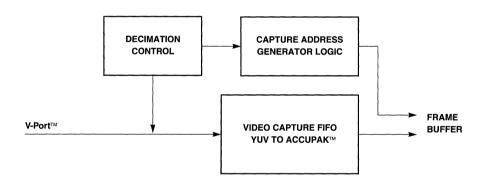

|    | 2.6  | Video Capture                           | 2-13 |

|    | 2.7  | Video Window and Video Display          | 2-13 |

|    | 2.8  | Hardware/Software Compatibility         | 2-14 |

|    | 2.9  | Computer Display Subsystem Architecture | 2-14 |

| 3. | DAT  | A BOOK                                  | 3-1  |

| 4. | VGA  | CORE REGISTERS                          | 4-2  |

|    | 4.1  | POS94: POS102 Access Control            | 4-5  |

|    | 4.2  | POS102: POS102                          | 4-6  |

|    | 4.3  | VSSM: 3C3 (Planar) Sleep Address        | 4-7  |

|    | 4.4  | VSSM: 46E8 (Adapter) Sleep Address      | 4-8  |

|    | 4.5  | MISC: Miscellaneous Output              | 4-9  |

|    | 4.6  | FC: Feature Control                     | 4-11 |

|    | 4.7  | FEAT: Input Status Register 0           | 4-12 |

|    | 4.8  | STAT: Input Status Register 1           | 4-13 |

|    | 4.9  | Pixel Mask                              | 4-14 |

|    | 4.10 | Palette Address (Read Mode, Write only) | 4-15 |

|    | 4.11 | DAC State (Read only)                   | 4-16 |

|    | 4.12 | Palette Address (Write Mode)            | 4-17 |

|    | 4.13 | Palette Data                            | 4-18 |

|    | 4.14 | SRX: Sequencer Index                    | 4-19 |

|    | 4.15 | SR0: Sequencer Reset                    | 4-20 |

|    | 4.16 | SR1: Sequencer Clocking Mode            | 4-21 |

|    | 4.17 | SR2: Sequencer Plane Mask               | 4-22 |

|    | 4.18 | SR3: Sequencer Character Map Select     | 4-23 |

|    | 4.19 | SR4: Sequencer Memory Mode              | 4-25 |

|    | 4.20 | CRX: CRTC Index                         | 4-26 |

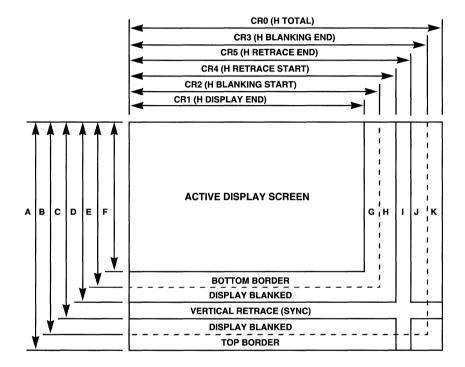

|    | 4.21 | CB0: CBTC Horizontal Total              | 4-29 |

| 4.22 | CR1: CRTC Horizontal Display End                       | 4-30   |

|------|--------------------------------------------------------|--------|

| 4.23 | CR2: CRTC Horizontal Blanking Start                    | 4-31   |

| 4.24 | CR3: CRTC Horizontal Blanking End                      | 4-32   |

| 4.25 | CR4: CRTC Horizontal Sync Start                        | 4-34   |

| 4.26 | CR5: CRTC Horizontal Sync End                          | 4-35   |

| 4.27 | CR6: CRTC Vertical Total                               | 4-37   |

| 4.28 | CR7: CRTC Overflow                                     | 4-38   |

| 4.29 | CR8: CRTC Screen A Preset Row-Scan                     | 4-39   |

| 4.30 | CR9: CRTC Character Cell Height                        | 4-40   |

| 4.31 | CRA: CRTC Text Cursor Start                            | 4-41   |

| 4.32 | CRB: CRTC Text Cursor End                              | 4-42   |

| 4.33 | CRC: CRTC Screen Start Address High                    | 4-43   |

| 4.34 | CRD: CRTC Screen Start Address Low                     | 4-44   |

| 4.35 | CRE: CRTC Text Cursor Location High                    | 4-45   |

| 4.36 | CRF: CRTC Text Cursor Location Low                     | 4-46   |

| 4.37 | CR10: CRTC Vertical Sync Start                         | 4-47   |

| 4.38 | CR11: CRTC Vertical Sync End                           | 4-48   |

| 4.39 | CR12: CRTC Vertical Display End                        | 4-50   |

| 4.40 | CR13: CRTC Offset (Pitch)                              | 4-51   |

| 4.41 | CR14: CRTC Underline Row Scanline                      | 4-52   |

| 4.42 | CR15: CRTC Vertical Blank Start                        | 4-53   |

| 4.43 | CR16: CRTC Vertical Blank End                          | 4-54   |

| 4.44 | CR17: CRTC Mode Control                                | 4-55   |

| 4.45 | CR18: CRTC Line Compare                                | 4-57   |

| 4.46 | CR22: Graphics Data Latches Readback (Read only)       | 4-58   |

| 4.47 | CR24: Attribute Controller Toggle Readback (Read only) | 4-59   |

| 4.48 | CR26: Attribute Controller Index Readback (Read only)  | 4-60   |

| 4.49 | GRX: Graphics Controller Index                         | 4-61   |

| 4.50 | GR0: Set/Reset / Background Color Byte 0               | 4-62   |

| 4.51 | GR1: Set/Reset Enable / Foreground Color Byte 0        | 4-63   |

| 4.52 | GR2: Color Compare                                     | 4-64   |

| 4.53 | GR3: Data Rotate                                       | 4-65   |

| 4.54 | GR4: Read Map Select                                   | 4-66   |

| 4.55 | GR5: Graphics Controller Mode                          | 4-67   |

| 4.56 | GR6: Miscellaneous                                     | 4-69   |

| 4.57 | GR7: Color Don't Care                                  | 4-70   |

| 4.58 | GR8: Bit Mask                                          | 4-71   |

| 4.59 | ARX: Attribute Controller Index                        |        |

| 4.60 | AR0-ARF: Attribute Controller Palette                  | 4-73   |

| 4.61 | AR10: Attribute Controller Mode                        | . 4-74 |

| 4.62 | AR11: Overscan (Border) Color                          | . 4-76 |

| 4.63 | AR12: Color Plane Enable                               | . 4-77 |

|    | 4.64 | AR13: Pixel Panning                                     | 4-78 |

|----|------|---------------------------------------------------------|------|

|    | 4.65 | AR14: Color Select                                      | 4-79 |

| 5. | BITE | BLT EXTENSION REGISTERS                                 | 5-2  |

|    | 5.1  | GR10-GR15: Color Expansion Foreground/Background Colors | 5-3  |

|    | 5.2  | GR20-GR21: BLT Width Byte 0, 1                          | 5-4  |

|    | 5.3  | GR22-GR23: BLT Height Byte 0, 1                         | 5-5  |

|    | 5.4  | GR24-GR25: BLT Destination Pitch Byte 0, 1              | 5-6  |

|    | 5.5  | GR26-GR27: BLT Source Pitch Byte 0, 1                   | 5-7  |

|    | 5.6  | GR28-GR2A: BLT Destination Start Byte 0, 1, 2           | 5-8  |

|    | 5.7  | GR2C-GR2E: BLT Source Start Byte 0, 1, 2                | 5-9  |

|    | 5.8  | GR2F: BLT Destination Left-Side Clipping                | 5-10 |

|    | 5.9  | GR30: BLT Mode                                          | 5-11 |

|    | 5.10 | GR31: BLT Start/Status                                  | 5-13 |

|    | 5.11 | GR32: BLT ROP (Raster Operation)                        | 5-15 |

|    | 5.12 | GR33: BLT Mode Extensions                               | 5-17 |

|    | 5.13 | GR34-GR35: Transparent BLT Key Color Byte 0, 1          | 5-18 |

| 6. | VIDE | EO CAPTURE AND PLAYBACK REGISTERS                       | 6-2  |

|    | 6.1  | CR31: Video Window Horizontal Zoom Control              | 6-4  |

|    | 6.2  | CR32: Video Window Vertical Zoom Control                | 6-5  |

|    | 6.3  | CR33: Video Window Horizontal Region 1 Size             | 6-6  |

|    | 6.4  | CR34: Video Window Region 2 Width                       | 6-7  |

|    | 6.5  | CR35: Video Window Region 2 Source Data Size            | 6-8  |

|    | 6.6  | CR36: Video Window Horizontal Overflow                  | 6-9  |

|    | 6.7  | CR37: Video Window Vertical Start                       | 6-10 |

|    | 6.8  | CR38: Video Window Vertical End                         | 6-11 |

|    | 6.9  | CR39: Video Window Vertical Overflow                    | 6-12 |

|    | 6.10 | CR3A-CR3B: Video Buffer 1 Start Address Byte 0, 1       | 6-13 |

|    | 6.11 | CR3C: Video Buffer 1 Start Address Byte 2               | 6-14 |

|    | 6.12 | CR3D: Video Buffer Address Offset                       | 6-15 |

|    | 6.13 | CR3E: Video Window Master Control                       | 6-16 |

|    | 6.14 | CR3F: Miscellaneous Video Control                       | 6-18 |

|    | 6.15 | CR50: Video Capture Control                             | 6-20 |

|    | 6.16 | CR51: Video Capture Data Format                         | 6-22 |

|    | 6.17 | CR52: Video Capture Horizontal Data Reduction           | 6-23 |

|    | 6.18 | CR53: Video Capture Vertical Data Reduction             | 6-24 |

|    | 6.19 | CR54: Video Capture Horizontal Delay                    | 6-25 |

|    | 6.20 | CR56: Video Capture Vertical Delay                      | 6-26 |

|    | 6.21 | CR57: Video Capture Maximum Height                      | 6-27 |

|    | 6.22 | CR58: Video Capture Miscellaneous Control               | 6-28 |

|    | 6.23 | CR59-CR5A: Video Buffer 2 Start Address Byte 0, 1       | 6-29 |

|    | 6.24 | CR5B: Video Window Brightness Adjust                    | 6-30 |

|    | 6.25  | CR5C: Luminance-Only Capture Control                        | 6-31 |

|----|-------|-------------------------------------------------------------|------|

|    | 6.26  | CR5D: Video Window Pixel Alignment                          | 6-32 |

|    | 6.27  | CR5E: Double-Buffer Control                                 | 6-33 |

|    | 6.28  | GR1C-GR1F: Chroma Key                                       | 6-35 |

| 7. | PCI ( | CONFIGURATION REGISTERS                                     | 7-2  |

|    | 7.1   | PCI00: PCI Device/Vendor ID                                 | 7-3  |

|    | 7.2   | PCI04: PCI Status/Command                                   | 7-4  |

|    | 7.3   | PCI08: PCI Class Code                                       | 7-5  |

|    | 7.4   | PCI10: PCI Display Memory Base Address                      | 7-6  |

|    | 7.5   | PCI14: PCI Relocatable I/O / GPIO Base Address (Revision A) | 7-7  |

|    | 7.6   | PCI14: PCI VGA/BitBLT Register Base Address (Revision B)    | 7-8  |

|    | 7.7   | PCI18: PCI GPIO Base Address (Revision B)                   | 7-9  |

|    | 7.8   | PCI2C: PCI Subsystem/Subsystem Vendor ID (Revision B)       | 7-10 |

|    | 7.9   | PCI30: PCI Expansion ROM Base Address Enable                | 7-11 |

|    | 7.10  | PCI3C: PCI Interrupt                                        | 7-12 |

| 8. | MISC  | CELLANEOUS EXTENSION REGISTERS                              | 8-2  |

|    | 8.1   | SR6: Key                                                    | 8-4  |

|    | 8.2   | SR7: Extended Sequencer Mode                                | 8-5  |

|    | 8.3   | SR8: DDC2B/EEPROM Control                                   | 8-7  |

|    | 8.4   | SR9-SRA: Scratch Pad 0, 1                                   | 8-9  |

|    | 8.5   | SRB-SRE: VCLK0-VCLK3 Numerator                              | 8-10 |

|    | 8.6   | SRF: DRAM Control                                           | 8-11 |

|    | 8.7   | SR10: Graphics Cursor X Position                            | 8-13 |

|    | 8.8   | SR11: Graphics Cursor Y Position                            | 8-14 |

|    | 8.9   | SR12: Graphics Cursor Attribute                             | 8-15 |

|    | 8.10  | SR13: Graphics Cursor Pattern Address Offset                | 8-16 |

|    | 8.11  | SR14–SR15: Scratch Pad 2, 3                                 | 8-17 |

|    | 8.12  | SR16: Display FIFO Threshold Control                        | 8-18 |

|    | 8.13  | SR17: Configuration Readback and Extended Control           | 8-19 |

|    | 8.14  | SR18: Signature Generator Control                           |      |

|    | 8.15  | SR19: Signature Generator Result Low-Byte                   | 8-22 |

|    | 8.16  | SR1A: Signature Generator Result High-Byte                  | 8-23 |

|    | 8.17  | SR1B-SR1E: VCLK0-VCLK3 Denominator and Post-Scalar          | 8-24 |

|    | 8.18  | SR1F: MCLK Select                                           | 8-25 |

|    | 8.19  | GR9: Offset Register 0                                      | 8-26 |

|    | 8.20  | GRA: Offset Register 1                                      |      |

|    | 8.21  | GRB: Graphics Controller Mode Extensions                    | 8-29 |

|    | 8.22  | GRC: Color Key/Chroma Key Compare                           |      |

|    | 8.23  | GRD: Color Key/Mask/Chroma Key                              |      |

|    | 8.24  | GRE: Power Management                                       | 8-33 |

|    | 8.25  | GR16: Active Display Line Readback Byte 0                   | 8-35 |

|     | 8.26 | GR17: Active Display Line Readback Byte 1 | . 8-36 |

|-----|------|-------------------------------------------|--------|

|     | 8.27 | GR18: Extended DRAM Controls              | . 8-37 |

|     | 8.28 | GR19: GPIO Port Configuration             | . 8-39 |

|     | 8.29 | GR1A-GR1B: Scratch Pad 4, 5               | . 8-40 |

|     | 8.30 | CR19: Interlace End                       | . 8-41 |

|     | 8.31 | CR1A: Miscellaneous Control               | . 8-42 |

|     | 8.32 | CR1B: Extended Display Controls           | . 8-44 |

|     | 8.33 | CR1C: Sync Adjust and GENLOCK             | . 8-46 |

|     | 8.34 | CR1D: Overlay Extended Control            | . 8-48 |

|     | 8.35 | CR25: Part Status (Read only)             | . 8-50 |

|     | 8.36 | CR27: ID (Read only)                      | . 8-51 |

|     | 8.37 | HDR: Hidden DAC Register                  | . 8-52 |

| 9.  | PRO  | GRAMMING NOTES                            | 9-2    |

|     | 9.1  | Introduction                              | 9-2    |

|     | 9.2  | Resource Addressing                       | 9-2    |

|     | 9.3  | Pixel Addressing and Formats              | . 9-11 |

|     | 9.4  | BitBLT Engine                             | . 9-18 |

|     | 9.5  | Video Window                              | . 9-31 |

|     | 9.6  | Video Capture                             | . 9-41 |

|     | 9.7  | Overlay: CL-GD543X/'4X Compatibility      | . 9-47 |

|     | 9.8  | Hardware Cursor                           | . 9-53 |

|     | 9.9  | Frequency Synthesizer Programming         | . 9-54 |

|     | 9.10 | Power Management                          | . 9-57 |

|     | 9.11 | CRTC Programming                          | . 9-58 |

|     | 9.12 | Chip Identification                       | . 9-61 |

|     | 9.13 | CL-GD5446 Interrupt System                | . 9-61 |

|     | 9.14 | Programming Examples                      | . 9-62 |

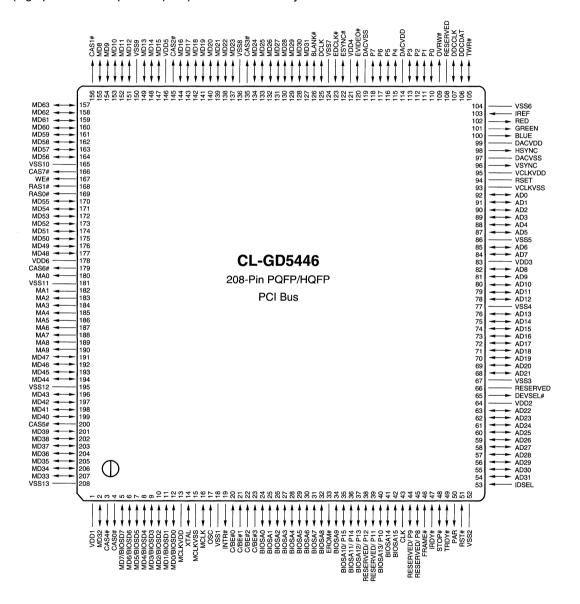

| 10. | DET/ | AILED PIN DESCRIPTIONS                    | 10-2   |

|     | 10.1 | Host Interface: PCI Bus                   | . 10-2 |

|     | 10.2 | Video Interface                           | . 10-4 |

|     | 10.3 | Display Memory Interface                  | . 10-6 |

|     | 10.4 | General-Purpose I/O                       | . 10-7 |

|     | 10.5 | V-Port™                                   | . 10-7 |

|     | 10.6 | Miscellaneous Pins                        | . 10-8 |

|     | 10.7 | Clock Synthesizer                         | . 10-8 |

|     | 10.8 | Power and Ground                          | . 10-9 |

| 11. | ELEC | CTRICAL SPECIFICATIONS                    | 11-2   |

|     | 11.1 | Absolute Maximum Ratings                  | . 11-2 |

|     | 11.2 | DC Specifications (Digital)               |        |

|     | 11.3 | DAC Characteristics                       |        |

|     | 11 / | AC Specifications                         |        |

# **APPENDIXES**

| <b>A1</b> | CON | NECT  | OR PINOUTS                                       | A1-2 |

|-----------|-----|-------|--------------------------------------------------|------|

| <b>A2</b> | REV | ISION | B NOTES                                          | A2-2 |

|           | 1.  | INTR  | RODUCTION                                        | A2-2 |

|           | 2.  |       | IGN CHANGES                                      |      |

|           |     | 2.1   | PCI10 Claims 32 Mbvtes                           |      |

|           |     | 2.2   | PCI14 Supports VGA and BitBLT Registers          | A2-2 |

|           |     | 2.3   | PCI18 Supports GPIO                              |      |

|           |     | 2.4   | PCI2C Supports Subsystem and Subsystem Vendor ID |      |

|           |     | 2.5   | General-Purpose I/O Configuration                |      |

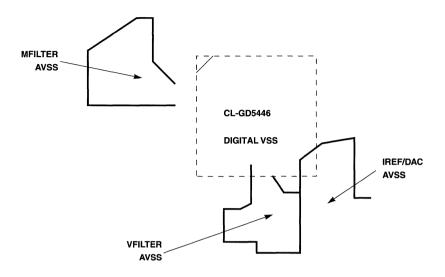

| В1        | LAY | OUT G | GUIDELINES                                       |      |

|           | 1.  |       | ODUCTION                                         |      |

|           | 2.  |       | TS PLACEMENT AND ADAPTER CARDS                   |      |

|           |     | 2.1   | PCI Bus Adapter Card                             |      |

|           |     | 2.2   | Motherboard                                      |      |

|           | 3.  | POW   | /ER                                              |      |

|           | 4.  | GRO   | UND                                              | B1-4 |

|           | 5.  |       | OUPLING CAPACITORS                               |      |

|           | 6.  |       | THESIZER                                         |      |

|           | 7.  | IREF  | CIRCUITRY                                        | B1-6 |

|           | 8.  | RGB   | LINES                                            | B1-6 |

|           | 9.  |       | M ARRAY                                          |      |

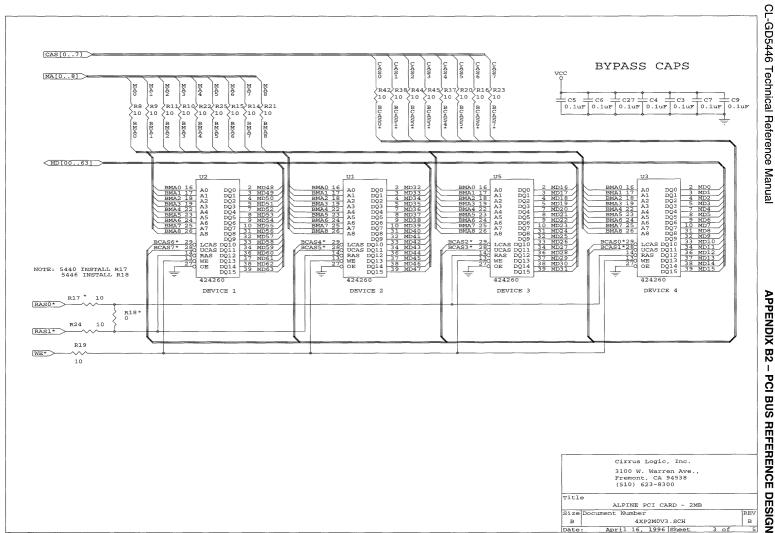

| B2        | PCI | BUS R | REFERENCE DESIGN                                 | B2-2 |

|           | 1.  | INTR  | RODUCTION                                        | B2-2 |

|           | 2.  |       | BUS INTERFACE                                    |      |

|           |     | 2.1   | Bus Connections                                  |      |

|           |     | 2.2   | INTR# Pin                                        |      |

|           |     | 2.3   | VGA BIOS                                         |      |

|           | 3.  | DISP  | PLAY MEMORY INTERFACE                            |      |

|           |     | 3.1   | Memory Configurations                            |      |

|           |     | 3.2   | Damping Resistors                                |      |

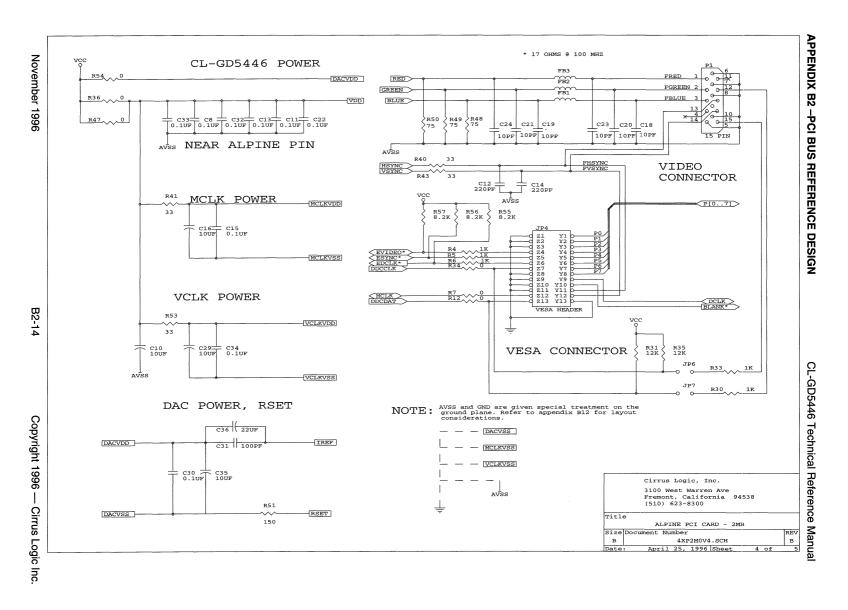

|           | 4.  | MON   | IITOR INTERFACE                                  |      |

|           |     | 4.1   | RGB Lines                                        | B2-4 |

|           |     | 4.2   | Sync Lines                                       | B2-4 |

|           |     | 4.3   | Monitor ID                                       |      |

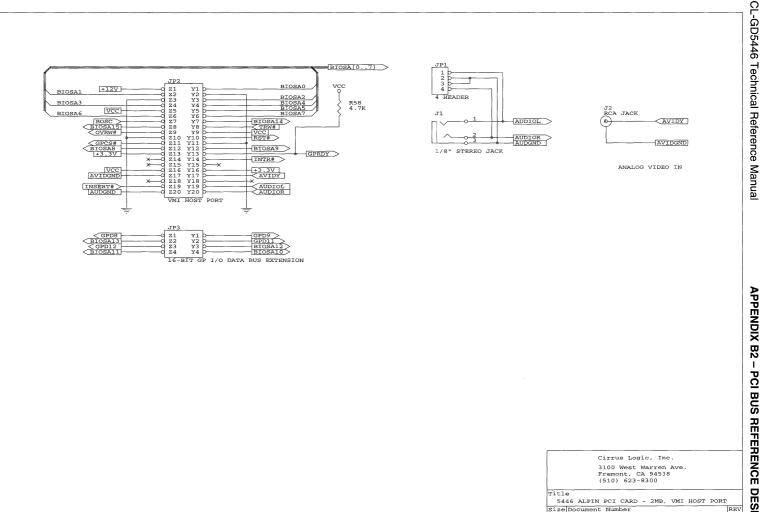

|           | 5.  | FEAT  | TURE CONNECTOR                                   | B2-5 |

|           | 6.  | VMI   | HOST PORT                                        | B2-6 |

|           | 7.  | POW   | /ER DISTRIBUTION AND CONDITIONING                | B2-8 |

|           |     | 7.1   | Introduction                                     | B2-8 |

|           |     | 7.2   | Dedicated Ground Plane                           | B2-8 |

|           |     | 7.3   | Dedicated Power Plane                            | B2-8 |

|            |       | 74 0 0                                             | D0 0  |

|------------|-------|----------------------------------------------------|-------|

|            |       | 7.4 Power Bypassing                                |       |

|            |       | 7.5 Analog Power Conditioning                      |       |

|            | 8.    | CONFIGURATION RESISTORS                            |       |

|            | 9.    | DUAL-FREQUENCY SYNTHESIZERS SUPPORT                |       |

|            |       | 9.1 Synthesizer Reference                          |       |

|            |       | 9.2 Synthesizer Filters                            |       |

|            | 10.   | DAC CURRENT REFERENCE                              |       |

|            | 11.   | PCI BUS SCHEMATICS                                 |       |

| <b>B</b> 3 | MEM   | ORY CONFIGURATIONS AND TIMING                      | B3-2  |

|            | 1.    | INTRODUCTION                                       | B3-2  |

|            | 2.    | DRAM CONFIGURATIONS                                | B3-2  |

|            | 3.    | CL-GD5440/'46 DUAL LAYOUT CONSIDERATIONS           | B3-3  |

|            | 4.    | DRAM CONNECTION TABLES                             | B3-3  |

|            | 5.    | DRAM TIMING REQUIREMENTS                           | B3-7  |

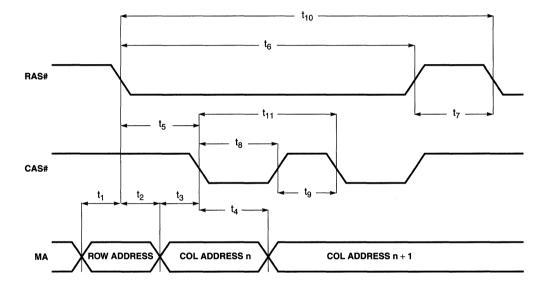

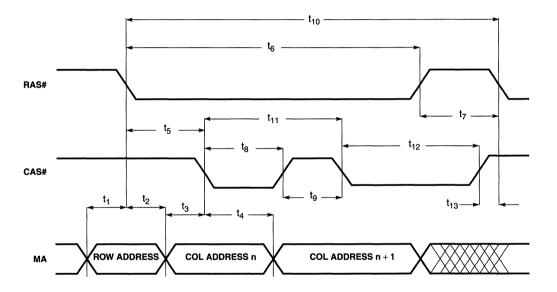

|            |       | 5.1 Extended RAS# Timing                           | B3-7  |

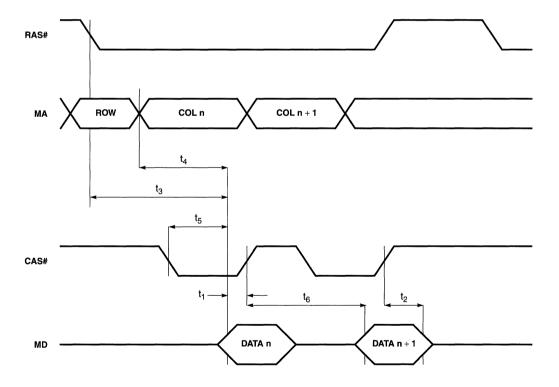

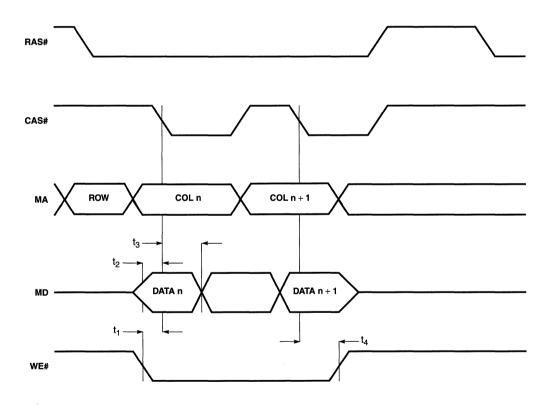

|            |       | 5.2 EDO Timing                                     | B3-7  |

|            |       | 5.3 DRAM Timing Equations Evaluated                | B3-8  |

|            | 6.    | MCLK vs. DISPLAY MODE REQUIREMENTS                 |       |

|            | 7.    | BANDWIDTH NOTE FOR CL-GD5440 WITH 64-BIT INTERFACE | B3-12 |

| В4         | CURF  | RENT REFERENCE                                     | B4-2  |

|            | 1.    | INTRODUCTION                                       |       |

|            | 2.    | RSet: FULL-SCALE CURRENT SET RESISTOR VALUE        | B4-2  |

| <b>B</b> 5 |       | FIGURATION NOTES                                   |       |

|            | 1.    | INTRODUCTION                                       |       |

|            |       | CONFIGURATION SUMMARY                              |       |

|            | 2.    |                                                    |       |

| -          | 3.    | CONFIGURATION DETAILS                              |       |

| B6         | SIGN  | ATURE GENERATOR                                    |       |

|            | 1.    | INTRODUCTION                                       |       |

|            | 2.    | TESTING                                            |       |

| B7         | PIN S | CAN                                                | B7-2  |

|            | 1.    | INTRODUCTION                                       | B7-2  |

|            | 2.    | TEST METHOD                                        | B7-2  |

|            |       | 2.1 Entering Pin-Scan Mode                         | B7-2  |

|            |       | 2.2 Exiting Pin-Scan Mode                          | B7-2  |

|            | 3.    | PIN SCAN ORDER                                     | B7-2  |

| B8         | DDC2  | 2B/I <sup>2</sup> C SUPPORT                        | B8-2  |

|            | 1.    | INTRODUCTION                                       | B8-2  |

| В9         |       | OCK SUPPORT                                        |       |

|            | 1.    | INTRODUCTION                                       |       |

|            |       | GENLOCK ON THE CL-GD5446                           |       |

|            | 2.    |                                                    |       |

|            | 3.    | VSYNC GENLOCK PROGRAMMING                          |       |

|            | 4     | HSYNC GENI OCK PROGRAMMING                         | B9-3  |

| B10 | MAN  | JFAC | TURING TEST                                   | B10-2 |

|-----|------|------|-----------------------------------------------|-------|

|     | 1.   | INTR | ODUCTION                                      | B10-2 |

|     | 2.   | OPER | RATING INSTRUCTIONS                           | B10-2 |

|     | 3.   | INST | ALLING AND STARTING MFGTST                    | B10-2 |

|     |      | 3.1  | Command Line Options                          | B10-3 |

|     | 4.   | USIN | G MFGTST                                      | B10-4 |

|     |      | 4.1  | Special Keystrokes                            |       |

|     | 5.   | UPDA | ATES                                          | B10-6 |

| B11 | GENE | RAL- | PURPOSE I/O                                   | B11-2 |

|     | 1.   | INTR | ODUCTION                                      | B11-2 |

|     | 2.   | GPIO | CONFIGURATION                                 | B11-2 |

|     | 3.   | PINS | REDEFINED                                     | B11-3 |

|     | 4.   | CYCL | E TIMING CONTROL                              | B11-4 |

|     | 5.   | GPIO | PROGRAMMING EXAMPLE                           | B11-7 |

| C1  | SOFT | WAR  | E SUPPORT                                     | C1-2  |

|     | 1.   | INTR | ODUCTION                                      | C1-2  |

|     | 2.   | CL-G | D5446 VGA SOFTWARE UTILITIES                  | C1-2  |

|     |      | 2.1  | CLMODE — A Display Mode Configuration Utility | C1-2  |

|     |      | 2.2  | VGA.EXE — RAMBIOS Utility                     | C1-2  |

|     |      | 2.3  | OEMSI (OEM System Integration) Utility        | C1-3  |

|     |      | 2.4  | WINMODE Utility                               | C1-3  |

|     | 3.   | CL-G | D5446 VGA SOFTWARE DRIVERS                    | C1-4  |

|     |      | 3.1  | Driver Applicability                          | C1-4  |

| C2  | VGA  | BIOS |                                               | C2-2  |

|     | 1.   | BIOS | OVERVIEW                                      | C2-2  |

|     |      | 1.1  | Main BIOS Features                            | C2-2  |

|     |      | 1.2  | Extended Display Mode Support                 | C2-2  |

|     |      | 1.3  | Direct-Color Operation                        | C2-2  |

|     |      | 1.4  | High Performance                              | C2-2  |

|     |      | 1.5  | System Integration                            | C2-3  |

|     |      | 1.6  | Customization                                 |       |

|     |      | 1.7  | Compatibility                                 |       |

|     | 2.   |      | D5446 VGA BIOS INITIALIZATION                 |       |

|     | 3.   |      | O BIOS INTERRUPT VECTORS                      |       |

|     | 4.   |      | RRUPT 10h: INDEX                              |       |

|     | 5.   |      | CRIPTION OF FUNCTIONS                         |       |

|     |      | 5.1  | Function 00h: Set Display Mode                |       |

|     |      | 5.2  | Function 01h: Set Cursor Type                 |       |

|     |      | 5.3  | Function 02h: Set Cursor Position             |       |

|     |      | 5.4  | Function 03h: Get Cursor Position             | C2-10 |

| 5.5  | Function 04h: Get Light Pen Position                                                              |                |

|------|---------------------------------------------------------------------------------------------------|----------------|

|      | (no longer supported)                                                                             |                |

| 5.6  | Function 05h: Select Active Display Page                                                          | . C2-11        |

| 5.7  | Function 06h: Window Scroll Up                                                                    |                |

| 5.8  | Function 07h: Window Scroll Down                                                                  |                |

| 5.9  | Function 08h: Read Character/Attribute at Cursor Position                                         | . C2-12        |

| 5.10 | Function 09h: Write Character/Attribute at Cursor Position                                        |                |

| 5.11 | Function 0Ah: Write Character at Cursor Position                                                  |                |

| 5.12 | Function 0Bh, Subfunction 00h: Set Background/Border Color                                        |                |

| 5.13 | Function 0Bh, Subfunction 01h: Select Palette Set                                                 |                |

| 5.14 | Function 0Ch: Write Dot (Pixel)                                                                   | . C2-15        |

| 5.15 | Function 0Dh: Read Dot (Pixel)                                                                    | . C2-15        |

| 5.16 | Function 0Eh: Write Character to Active RAM in Teletype Mode                                      | . C2-16        |

| 5.17 | Function 0Fh: Get Display State                                                                   | . C2-16        |

| 5.18 | Function 10h, Subfunction 00h: Set Individual Palette Register (Internal Palette Register)        | C2-16          |

| 5.19 | Function 10h, Subfunction 01h: Set Overscan (Border) Register                                     | C2-17          |

| 5.20 | Function 10h, Subfunction 02h: Set All Palette Registers and OverScan Register                    | C2-17          |

| 5.21 | Function 10h, Subfunction 03h: Toggle Intensify/Blinking Bit                                      | . C2-17        |

| 5.22 | Function 10h, Subfunction 07h: Read Individual Palette Register (Internal Palette Register)       | C2-18          |

| 5.23 | Function 10h, Subfunction 08h: Read OverScan (Border) Register                                    | . C2-18        |

| 5.24 | Function 10h, Subfunction 09h: Read All Palette Registers and Ove Register                        | rScan<br>C2-18 |

| 5.25 | Function 10h, Subfunction 10h: Set Individual Color Register (RAMDAC/External Palette Registers)  | C2-18          |

| 5.26 | Function 10h, Subfunction 12h: Set Block of Color Registers                                       | . C2-19        |

| 5.27 | Function 10h, Subfunction 13h: Select Color Page (Not valid in Mode 13h)                          | C2-19          |

| 5.28 | Function 10h, Subfunction 15h: Read Individual Color Register (RAMDAC/External Palette Registers) | C2-20          |

| 5.29 | Function 10h, Subfunction 17h: Read Block of Color Registers                                      | . C2-20        |

| 5.30 | Function 10h, Subfunction 1Ah: Read Current State of Color Page (Not valid in Mode 13h)           | C2-21          |

| 5.31 | Function 10h, Subfunction 1Bh: Sum Color Values to Grayshades                                     | C2-21          |

| 5.32 | Function 11h, Subfunction 00h: Load User Text Font                                                | . C2-21        |

| 5.33 | Function 11h, Subfunction 01h: Load 8 × 14 ROM Font                                               | . C2-22        |

| 5.34 | Function 11h, Subfunction 02h: Load 8 × 8 ROM Font                                                | . C2-23        |

| 5.35 | Function 11h, Subfunction 03h: Select Block Specifier                                             | . C2-24        |

| 5 36 | Function 11h, Subfunction 04h: Load 8 × 16 ROM Font                                               | C2-25          |

|    | 5.37  | Function 11h, Subfunction 10h: Load User Text Font and Reprogram Controller                          |       |

|----|-------|------------------------------------------------------------------------------------------------------|-------|

|    | 5.38  | Function 11h, Subfunction 11h: Load 8 × 14 ROM Font and Reprogra<br>Controller                       |       |

|    | 5.39  | Function 11h, Subfunction 12h: Load 8 × 8 ROM Font and Reprogram Controller                          |       |

|    | 5.40  | Function 11h, Subfunction 14h: Load 8 × 16 ROM Font and Reprogra<br>Controller                       |       |

|    | 5.41  | Function 11h, Subfunction 20h: Set Pointer of User's Graphics Font 7 to Interrupt 1Fh                |       |

|    | 5.42  | Function 11h, Subfunction 21h: Set Pointer of User's Graphics Font 7 to Interrupt 43h                |       |

|    | 5.43  | Function 11h, Subfunction 22h: Set Pointer of ROM 8 $\times$ 14 Graphics Font Table to Interrupt 43h | C2-31 |

|    | 5.44  | Function 11h, Subfunction 23h: Set Pointer of ROM 8 $\times$ 8 Graphics Font Table to Interrupt 43h  | C2-32 |

|    | 5.45  | Function 11h, Subfunction 24h: Set Pointer of ROM 8 $\times$ 16 Graphics Font Table to Interrupt 43h | C2-32 |

|    | 5.46  | Function 11h, Subfunction 30h: Get Pointer Information of Fonts                                      | C2-33 |

|    | 5.47  | Function 12h, Subfunction 10h: Get Current Display Configuration                                     | C2-33 |

|    | 5.48  | Function 12h, Subfunction 20h: Alternate PrintScreen Handler                                         | C2-34 |

|    | 5.49  | Function 12h, Subfunction 30h: Select Scanlines for Text Modes                                       | C2-34 |

|    | 5.50  | Function 12h, Subfunction 31h: Enable/Disable Default Palette Loading                                | C2-35 |

|    | 5.51  | Function 12h, Subfunction 32h: Enable/Disable Display                                                | C2-35 |

|    | 5.52  | Function 12h, Subfunction 33h: Enable/Disable Summing-to-Grayshades                                  | C2-35 |

|    | 5.53  | Function 12h, Subfunction 34h: Enable/Disable Cursor Emulation                                       | C2-36 |

|    | 5.54  | Function 12h, Subfunction 35h: Switch Display                                                        | C2-36 |

|    | 5.55  | Function 12h, Subfunction 36h: Enable/Disable Screen Display                                         | C2-37 |

|    | 5.56  | Function 13h: Write Teletype String                                                                  | C2-37 |

|    | 5.57  | Function 1Ah, Subfunction 00h: Get Display Combination Code (DCC)                                    | C2-38 |

|    | 5.58  | Function 1Ah, Subfunction 01h: Set Display Combination Code (DCC)                                    | C2-38 |

|    | 5.59  | Function 1Bh: Collection of Display Information                                                      | C2-39 |

|    | 5.60  | Function 1Ch, Subfunction: 00h: Get Buffer Size for Display State                                    | C2-42 |

|    | 5.61  | Function 1Ch, Subfunction 01h: Saving Display State                                                  | C2-42 |

|    | 5.62  | Function 1Ch, Subfunction 02h: Restore Display State                                                 |       |

| 6. | VGA S | SLEEP MODE AND DISPLAY SWITCHING                                                                     | C2-44 |

| 7. | ADDR  | ESS MAPS                                                                                             | C2-44 |

| C3 | BIO  | S EXT  | ENSIONS                                             | C3-2  |

|----|------|--------|-----------------------------------------------------|-------|

|    | 1.   | INTR   | ODUCTION                                            | C3-2  |

|    | 2.   | CIRR   | US LOGIC EXTENSIONS                                 | C3-2  |

|    |      | 2.1    | Function Summary                                    | C3-2  |

|    |      | 2.2    | Inquire VGA Type                                    | C3-3  |

|    |      | 2.3    | Inquire BIOS Version Number                         | C3-4  |

|    |      | 2.4    | Inquire Cirrus Logic Design Revision Code           | C3-4  |

|    |      | 2.5    | Return Installed Memory                             | C3-4  |

|    |      | 2.6    | Inquire User Options                                | C3-4  |

|    |      | 2.7    | Query Display Mode Availability                     | C3-5  |

|    |      | 2.8    | Read Monitor ID/Type                                | C3-5  |

|    |      | 2.9    | Set Monitor Type                                    | C3-5  |

|    |      | 2.10   | Process Generic Fixup Table                         | C3-7  |

|    |      | 2.11   | Return Chip Capabilities                            | C3-7  |

|    |      | 2.12   | Get High Refresh                                    | C3-7  |

|    |      | 2.13   | Set High Refresh                                    | C3-7  |

|    | 3.   | VESA   | A® SUPER VGA STANDARD                               | C3-8  |

|    |      | 3.1    | Goals and Objectives                                | C3-8  |

|    |      | 3.2    | Standard VGA BIOS                                   | C3-9  |

|    |      | 3.3    | Super VGA Mode Numbers                              |       |

|    | 4.   | EXTE   | ENDED VESA® BIOS FUNCTIONS                          | C3-10 |

|    |      | 4.1    | Status Information                                  | C3-10 |

|    |      | 4.2    | Function 00h — Return Super VGA Information         | C3-10 |

|    |      | 4.3    | Function 01h — Return Super VGA Mode Information    | C3-12 |

|    |      | 4.4    | Function 02h — Set Super VGA Display Mode           | C3-17 |

|    |      | 4.5    | Function 03h — Return Current Display Mode          | C3-17 |

|    |      | 4.6    | Function 04h — Save/Restore Super VGA Display State | C3-17 |

|    |      | 4.7    | Function 05h — CPU Display Memory Window Control    | C3-18 |

|    |      | 4.8    | Function 06h — Set/Get Logical Scanline Length      | C3-19 |

|    |      | 4.9    | Function 07h — Set/Get Display Start                | C3-20 |

|    |      | 4.10   | Function 08h — Set/Get DAC Palette Control          | C3-20 |

|    |      | 4.11   | Function 15h — Display Identification Extensions    | C3-22 |

| D1 | CIRF | RUS LO | OGIC BBS, FTP, AND WWW                              | D1-2  |

|    | 1.   | INTR   | ODUCTION                                            | D1-2  |

|    | 2.   | FIRS'  | T-TIME LOG ON                                       | D1-3  |

|    | 3.   | UPG    | RADED ACCESS                                        | D1-3  |

|    |      | 3.1    | Using the FTP Server                                | D1-3  |

|    |      | 3.2    | Web Access                                          |       |

| E1 | GLO  | SSAR   | Υ                                                   | E1-2  |

|    |      |        | 9HV                                                 |       |

# **INDEXES**

| REGISTER INDEX | F-2 |

|----------------|-----|

| INDEX          | F-8 |

# Introduction

# 1. INTRODUCTION

### 1.1 Scope of Document

This manual provides a technical discussion of the CL-GD5446 VisualMedia™ accelerator. This manual includes descriptions of each major component integrated into the device, a data book, detailed information on each register, a BIOS description, and appendices intended to assist hardware and software designers.

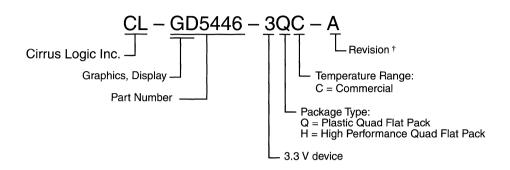

# 1.2 Chip Types Covered

This manual documents the CL-GD5446. Table 1-1 shows the production versions covered.

Table 1-1. Production Versions Covered

| Revision  | Α | В |

|-----------|---|---|

| CL-GD5446 | ~ | ~ |

The CL-GD5446 ID register — CR27, reads back a value specifying the CL-GD5446. Refer to Chapter 8, "Miscellaneous Extension Registers", for further information. The ID is also in register PCI00.

### 1.3 Intended Audience

This manual is intended for a technically sophisticated audience. It is assumed that the reader is familiar with assembly language programming on the 8088/8086, 80286/80386/80486, Pentium®, or similar microprocessor, and understands the fundamentals of computer generated graphics display technology.

Hardware engineers should find Chapter 3, "Data Book", useful. It contains the pinouts and pin summary. In addition, Chapter 10 contains the detailed pin descriptions and Chapter 11 contains the DC and AC specifications. Appendix B1 and Appendix B2 contain board design and layout information.

Software engineers should find Chapters 4–8 (register descriptions) useful for BIOS- and driver-level codes. All registers are described to the bit level. Chapter 9 contains programming notes.

### 1.4 Conventions

This section discusses conventions used throughout this document. Conventions include acronyms, abbreviations, and nomenclature usage. For a quick reference of acronyms see Table 1-2.

### Bits

Bits are always listed in descending order, most-significant (highest number) to least-significant (lowest number). When discussing a bit field within a register or memory, the bit number of the most-significant bit is given on the left, followed by a colon (:) and then the bit number of the least-significant bit (for example, bits 7:0). A field consists of a set of adjoining bits with common functionality. Registers consist of fields of one or more bits.

Table 1-2. Acronym Quick Reference

| AC alternating current ALU arithmetic logic unit ATE automatic test equipment BIOS basic input/output system BitBLT, BLT bit boundary block transfer bpp bits per pixel CAD computer-aided design CAS column address strobe CGA color graphics adapter CLUT color lookup table CMOS complementary metal-oxide semiconductor CPU central processing unit CRT cathode ray tube CRTC CRT controller DAC digital-to-analog converter DC direct current DDA digital differential algorithm DDC display data channel DMI desktop management signaling DPMS display power management signaling DRAM dynamic random access memory dword doubleword EEPROM electrically erasable/programmable read-only memory EGA enhanced graphics adapter EPROM electrically programmable read-only memory EVAFC extended VESA® advanced feature connector FIFO first in/first out GPIO general-purpose IO GSC graphics system controller GUI graphical user interface HDR Hidden DAC register HRQ host read queue HSYNC/VSYNC horizontal/vertical synchronization HWQ host write queue IC integrated circuit I/O input/output LBI local bus interface LSB least-significant bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Acronym     | Definition                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|

| ATE automatic test equipment BIOS basic input/output system BitBLT, BLT bit boundary block transfer bpp bits per pixel CAD computer-aided design CAS column address strobe CGA color graphics adapter CLUT color lookup table CMOS complementary metal-oxide semiconductor CPU central processing unit CRT cathode ray tube CRTC CRT controller DAC digital-to-analog converter DC direct current DDA display data channel DMI desktop management signaling DPMS display power management signaling DPMS display power management signaling DPMS display power management signaling DRAM dynamic random access memory dword doubleword EEPROM electrically erasable/programmable read-only memory EGA enhanced graphics adapter EPROM electrically programmable read-only memory EVAFC extended VESA® advanced feature connector FIFO first in/first out GPIO general-purpose IO GSC graphics system controller GUI graphical user interface HDR Hidden DAC register HRQ host read queue HSYNC/VSYNC horizontal/vertical synchronization HWQ host write queue IC integrated circuit I/O input/output LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AC          | alternating current                 |

| BIOS basic input/output system BitBLT, BLT bit boundary block transfer bpp bits per pixel CAD computer-aided design CAS column address strobe CGA color graphics adapter CLUT color lookup table CMOS complementary metal-oxide semiconductor CPU central processing unit CRT cathode ray tube CRTC CRT controller DAC digital-to-analog converter DC direct current DDA digital differential algorithm DDC display data channel DMI desktop management signaling DPMS display power management signaling DPMS display power management signaling DRAM dynamic random access memory dword doubleword EEPROM electrically erasable/programmable read-only memory EGA enhanced graphics adapter EPROM electrically programmable read-only memory EVAFC extended VESA® advanced feature connector FIFO first in/first out GPIO general-purpose IO GSC graphics system controller GUI graphical user interface HDR Hidden DAC register HRQ host read queue HSYNC/VSYNC horizontal/vertical synchronization HWQ host write queue IC integrated circuit I/O input/output LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ALU         | arithmetic logic unit               |

| BitBLT, BLT bit boundary block transfer bpp bits per pixel  CAD computer-aided design  CAS column address strobe  CGA color graphics adapter  CLUT color lookup table  CMOS complementary metal-oxide semiconductor  CPU central processing unit  CRT cathode ray tube  CRTC CRT controller  DAC digital-to-analog converter  DC direct current  DDA digital differential algorithm  DDC display data channel  DMI desktop management signaling  DPMS display power management signaling  DRAM dynamic random access memory  dword doubleword  EEPROM electrically erasable/programmable read-only memory  EGA enhanced graphics adapter  EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector  FIFO first in/first out  GPIO general-purpose IO GSC graphics system controller  GUI graphical user interface  HDR Hidden DAC register  HRQ host write queue  HSYNC/VSYNC horizontal/vertical synchronization  HWQ host write queue  IC integrated circuit  I/O input/output  LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ATE         | automatic test equipment            |

| bpp bits per pixel  CAD computer-aided design  CAS column address strobe  CGA color graphics adapter  CLUT color lookup table  CMOS complementary metal-oxide semiconductor  CPU central processing unit  CRT cathode ray tube  CRTC CRT controller  DAC digital-to-analog converter  DC direct current  DDA digital differential algorithm  DDC display data channel  DMI desktop management signaling  DPMS display power management signaling  DPMS display power management signaling  DRAM dynamic random access memory dword doubleword  EEPROM electrically erasable/programmable read-only memory  EGA enhanced graphics adapter  EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector  FIFO first in/first out  GPIO general-purpose IO  GSC graphics system controller  GUI graphical user interface  HDR Hidden DAC register  HRQ host read queue  HSYNC/VSYNC horizontal/vertical synchronization  HWQ host write queue  IC integrated circuit  I/O input/output  LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BIOS        | basic input/output system           |

| CAD computer-aided design CAS column address strobe CGA color graphics adapter CLUT color lookup table CMOS complementary metal-oxide semiconductor CPU central processing unit CRT cathode ray tube CRTC CRT controller DAC digital-to-analog converter DC direct current DDA digital differential algorithm DDC display data channel DMI desktop management signaling DPMS display power management signaling DPMS doubleword EEPROM electrically erasable/programmable read-only memory EGA enhanced graphics adapter EPROM electrically programmable read-only memory EVAFC extended VESA® advanced feature connector FIFO first in/first out GPIO general-purpose IO GSC graphics system controller GUI graphical user interface HDR Hidden DAC register HRQ host read queue HSYNC/VSYNC horizontal/vertical synchronization HWQ host write queue IC integrated circuit I/O input/output LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BitBLT, BLT | bit boundary block transfer         |

| CAS column address strobe CGA color graphics adapter CLUT color lookup table CMOS complementary metal-oxide semiconductor CPU central processing unit CRT cathode ray tube CRTC CRT controller DAC digital-to-analog converter DC direct current DDA digital differential algorithm DDC display data channel DMI desktop management signaling DPMS display power management si | bpp         | bits per pixel                      |

| CGA color graphics adapter CLUT color lookup table CMOS complementary metal-oxide semiconductor CPU central processing unit CRT cathode ray tube CRTC CRT controller DAC digital-to-analog converter DC direct current DDA digital differential algorithm DDC display data channel DMI desktop management signaling DPMS display power management signaling DPMS dynamic random access memory dword doubleword EEPROM electrically erasable/programmable read-only memory EGA enhanced graphics adapter EPROM electrically programmable read-only memory EVAFC extended VESA® advanced feature connector FIFO first in/first out GPIO general-purpose IO GSC graphics system controller GUI graphical user interface HDR Hidden DAC register HRQ host read queue HSYNC/VSYNC horizontal/vertical synchronization HWQ host write queue IC integrated circuit I/O input/output LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CAD         | computer-aided design               |

| CLUT  CMOS  complementary metal-oxide semiconductor  CPU  central processing unit  CRT  cathode ray tube  CRTC  CRT controller  DAC  digital-to-analog converter  DC  direct current  DDA  digital differential algorithm  DDC  display data channel  DMI  desktop management signaling  DPMS  display power management signaling  display power management signaling  DPMS  d | CAS         | column address strobe               |

| CMOS complementary metal-oxide semiconductor  CPU central processing unit  CRT cathode ray tube  CRTC CRT controller  DAC digital-to-analog converter  DC direct current  DDA digital differential algorithm  DDC display data channel  DMI desktop management signaling  DPMS display power management signaling  DPMS display power management signaling  DRAM dynamic random access memory  dword doubleword  EEPROM electrically erasable/programmable read-only memory  EGA enhanced graphics adapter  EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector  FIFO first in/first out  GPIO general-purpose IO  GSC graphics system controller  GUI graphical user interface  HDR Hidden DAC register  HRQ host read queue  HSYNC/VSYNC horizontal/vertical synchronization  HWQ host write queue  IC integrated circuit  I/O input/output  LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CGA         | color graphics adapter              |

| Semiconductor  CPU central processing unit  CRT cathode ray tube  CRTC CRT controller  DAC digital-to-analog converter  DC direct current  DDA digital differential algorithm  DDC display data channel  DMI desktop management signaling  DPMS display power management signaling  DPMS display power management signaling  DRAM dynamic random access memory  dword doubleword  EEPROM electrically erasable/programmable read-only memory  EGA enhanced graphics adapter  EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector  FIFO first in/first out  GPIO general-purpose IO  GSC graphics system controller  GUI graphical user interface  HDR Hidden DAC register  HRQ host read queue  HSYNC/VSYNC horizontal/vertical synchronization  HWQ host write queue  IC integrated circuit  I/O input/output  LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CLUT        | color lookup table                  |

| CRTC CAT controller  DAC digital-to-analog converter  DC direct current  DDA digital differential algorithm  DDC display data channel  DMI desktop management signaling  DPMS display power management signaling  EEPROM electrically erasable/programmable read-only memory  EVAFC extended VESA® advanced feature connector  FIFO first in/first out  GPIO general-purpose IO  GSC graphics system controller  GUI graphical user interface  HDR Hidden DAC register  HRQ host read queue  HSYNC/VSYNC horizontal/vertical synchronization  HWQ host write queue  IC integrated circuit  I/O input/output  LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CMOS        |                                     |

| CRTC CRT controller  DAC digital-to-analog converter  DC direct current  DDA digital differential algorithm  DDC display data channel  DMI desktop management signaling  DPMS display power management signaling  DPMS display power management signaling  DRAM dynamic random access memory  dword doubleword  EEPROM electrically erasable/programmable read-only memory  EGA enhanced graphics adapter  EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector  FIFO first in/first out  GPIO general-purpose IO  GSC graphics system controller  GUI graphical user interface  HDR Hidden DAC register  HRQ host read queue  HSYNC/VSYNC horizontal/vertical synchronization  HWQ host write queue  IC integrated circuit  I/O input/output  LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CPU         | central processing unit             |

| DAC digital-to-analog converter DC direct current DDA digital differential algorithm DDC display data channel DMI desktop management signaling DPMS display power management signaling DPMS display power management signaling DRAM dynamic random access memory dword doubleword EEPROM electrically erasable/programmable read-only memory EGA enhanced graphics adapter EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector FIFO first in/first out GPIO general-purpose IO GSC graphics system controller GUI graphical user interface HDR Hidden DAC register HRQ host read queue HSYNC/VSYNC horizontal/vertical synchronization HWQ host write queue IC integrated circuit I/O input/output LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CRT         | cathode ray tube                    |

| DC direct current  DDA digital differential algorithm  DDC display data channel  DMI desktop management signaling  DPMS display power management signaling  DRAM dynamic random access memory  dword doubleword  EEPROM electrically erasable/programmable read-only memory  EGA enhanced graphics adapter  EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector  FIFO first in/first out  GPIO general-purpose IO  GSC graphics system controller  GUI graphical user interface  HDR Hidden DAC register  HRQ host read queue  HSYNC/VSYNC horizontal/vertical synchronization  HWQ host write queue  IC integrated circuit  I/O input/output  LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CRTC        | CRT controller                      |

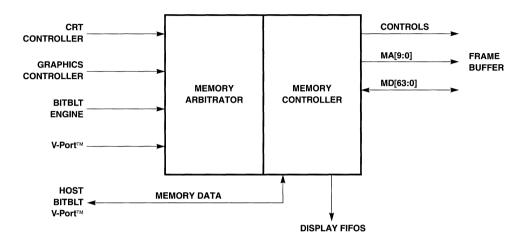

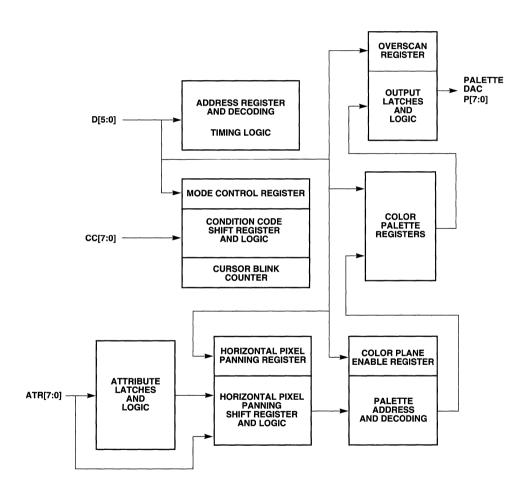

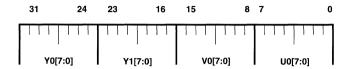

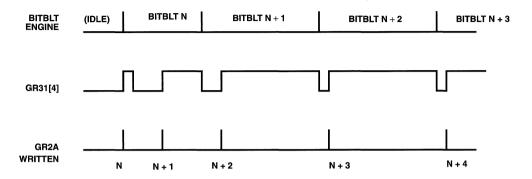

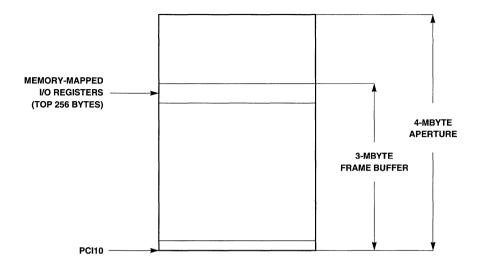

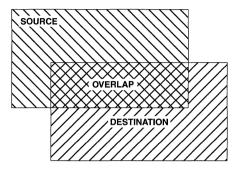

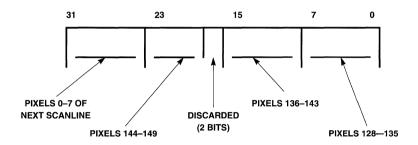

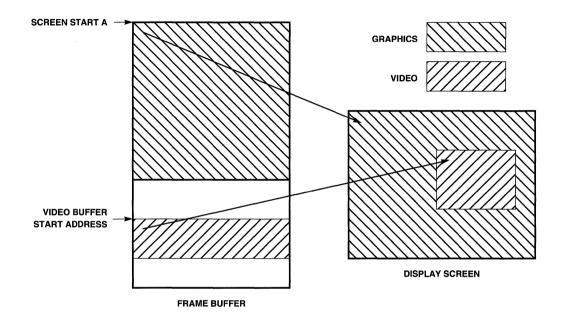

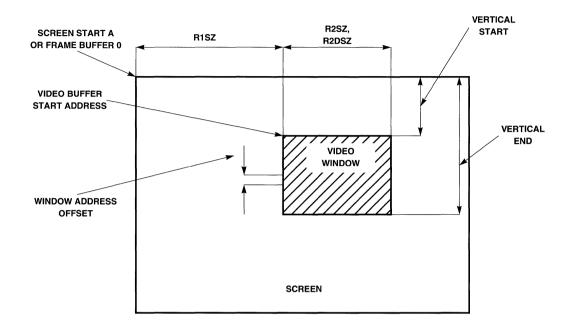

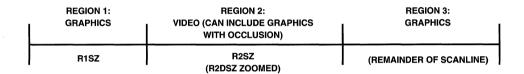

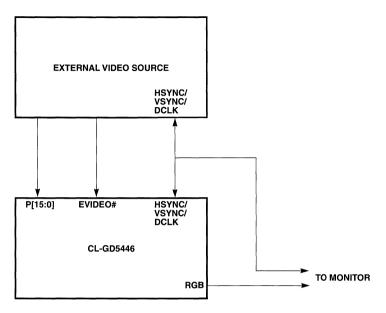

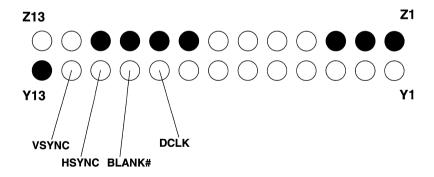

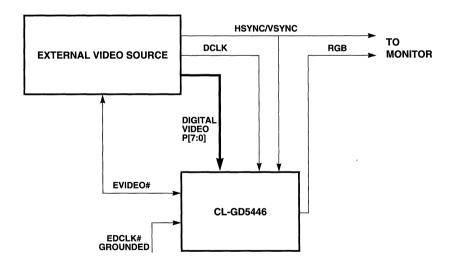

| DDA digital differential algorithm DDC display data channel DMI desktop management signaling DPMS display power management signaling DRAM dynamic random access memory dword doubleword EEPROM electrically erasable/programmable read-only memory EGA enhanced graphics adapter EPROM electrically programmable read-only memory  EVAFC extended VESA® advanced feature connector FIFO first in/first out GPIO general-purpose IO GSC graphics system controller GUI graphical user interface HDR Hidden DAC register HRQ host read queue HSYNC/VSYNC horizontal/vertical synchronization HWQ host write queue IC integrated circuit I/O input/output LBI local bus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DAC         | digital-to-analog converter         |