DESIGN FOR ENGINEERS REVISED SECOND EDITION

PRACTICAL ERROR CORRECTION DESIGN FOR ENGINEERS

# Neal Glover and Trent Dudley

# PRACTICAL ERROR CORRECTION DESIGN FOR ENGINEERS

**REVISED SECOND EDITION**

# **Neal Glover** and **Trent Dudley**

# PRACTICAL ERROR CORRECTION DESIGN FOR ENGINEERS

#### Neal Glover and Trent Dudley CIRRUS LOGIC - COLORADO

The study of error-correcting codes is now more than forty years old. There are several excellent texts on the subject, but they were written mainly by coding theorists and are based on a rigorous mathematical approach. This book is written from a more intuitive, practical viewpoint. It is intended for practicing engineers who must specify, architect, and design error-correcting code hardware and software. It is an outgrowth of a series of seminars presented during 1981 and 1982 on practical error-correction design.

An engineer who must design an error-control system to meet data recoverability, data accuracy, and performance goals must become familiar with the characteristics and capabilities of different types of EDAC codes as well as their implementation alternatives, including tradeoffs between hardware and software complexity, speed/space/cost, etc. The goal of this book is to provide this information in a concise manner from a practical engineering viewpoint. Numerous examples are used throughout to develop familiarity and confidence in the methods presented. Most proofs and complex derivations have been omitted; these may be found in theoretical texts on error correction coding. CIRRUS LOGIC - COLORADO INTERLOCKEN BUSINESS PARK 100 Technology Drive, Suite 300 Broomfield, Colorado 80021 Telephone (303) 466-5228 FAX (303) 466-5482

If you wish to receive updates to this book, please copy this form, complete it and send it to the above address.

| updates to  | the book: | PRACTIC    | AL ERROI | CORRI | ECTION                                | DESIC |

|-------------|-----------|------------|----------|-------|---------------------------------------|-------|

| FOR ENGINEE |           |            |          |       |                                       |       |

| Name        |           |            |          |       |                                       |       |

| Title       |           |            |          |       |                                       |       |

| Organizatio | n         | . <b>s</b> |          |       | · · · · · · · · · · · · · · · · · · · |       |

| Address     |           |            |          |       |                                       |       |

| *           |           |            |          |       |                                       |       |

| Phone       |           |            | •        |       |                                       |       |

| Other Areas | of Intere | est        |          |       |                                       |       |

|             |           |            | · .      |       |                                       |       |

n for each free that the second of the second s I have the second sec I have the second se

# PRACTICAL ERROR CORRECTION

# DESIGN FOR ENGINEERS

**REVISED SECOND EDITION**

entra di company partiti da anteri da anteri da partiti da per la transferi da segui da company da segui da se Anteri da segui da se

# PRACTICAL ERROR CORRECTION DESIGN FOR ENGINEERS

**REVISED SECOND EDITION**

Neal Glover and Trent Dudley

Published By: Cirrus Logic - Colorado Broomfield, Colorado 80020 (303) 466-5228 Cirrus Logic believes the information contained in this book to be accurate. However, neither Cirrus Logic nor its authors guarantees the accuracy or completeness of any information published herein and neither Cirrus Logic nor its authors shall be responsible for any errors, omissions or damages arising out of use of this information. Cirrus Logic does not assume any responsibility or liability arising out of the application or use of any software, circuit, method, technique, or algorithm described herein, nor does the purchase of this book convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property or trade secret rights of Cirrus Logic or third parties.

This work is published with the understanding the Cirrus Logic and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

#### Second Edition Revision 1.1

#### Copyright © 1991 by CIRRUS LOGIC, INC.

Revised Second Edition COPYRIGHT © 1991. Second Edition COPYRIGHT © 1988. First Edition COPYRIGHT © 1982. ALL RIGHTS RESERVED.

No part of this book may be reproduced in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without the prior written permission of DATA SYSTEMS TECHNOLOGY, CORP. or CIRRUS LOGIC, INC.

Published by:

*CIRRUS LOGIC* - COLORADO INTERLOCKEN BUSINESS PARK 100 Technology Drive, Suite 300 Broomfield, Colorado 80021 Phone (303) 466-5228 FAX (303) 466-5482

Second Printing 1990. ISBN #0-927239-00-0 To my children,

Rhonda, Karen, Sean, and Robert

Neal Glover

To the memory of my parents,

Robert and Constance

Trent Dudley

#### a state and a state of the

### PREFACE

The study of error-correcting codes is now more than forty years old. There are several excellent texts on the subject, but they were written mainly by coding theorists and are based on a rigorous mathematical approach. This book is written from a more intuitive, practical viewpoint. It is intended for practicing engineers who must specify, architect, and design error-correcting code hardware and software. It is an outgrowth of a series of seminars presented during 1981 and 1982 on practical error-correction design.

An engineer who must design an error-control system to meet data recoverability, data accuracy, and performance goals must become familiar with the characteristics and capabilities of different types of EDAC codes as well as their implementation alternatives, including tradeoffs between hardware and software complexity, speed/space/ cost, etc. Our goal is to provide this information in a concise manner from a practical engineering viewpoint. Numerous examples are used throughout to develop familiarity and confidence in the methods presented. Most proofs and complex derivations have been omitted; these may be found in theoretical texts on error correction coding.

We would like to thank our friends for their assistance and advice. The engineers attending DST's seminars also deserve thanks for their suggestions.

Neal Glover Trent Dudley

Broomfield, Colorado August 1988

## **ABOUT CIRRUS LOGIC - COLORADO**

Cirrus Logic - Colorado was originally founded in 1979 as Data System Technology (DST) and was sold to Cirrus Logic, Inc., of Milpitas, California, on January 18, 1990. Cirrus Logic - Colorado provides error detection and correction (EDAC) products and services to the electronics industries. We specializes in the practical implementation of EDAC, recording and data compression codes to enhance the reliability and efficiency of data storage and transmission in computer and communications systems, and all aspects of error tolerance, including framing, synchronization, data formats, and error management.

Cirrus Logic - Colorado also develops innovative VLSI products that perform complex peripheral control functions in high-performance personal computers, workstations and other office automation products. The company develops advanced standard and semi-standard VLSI controllers for data communications, graphics and mass storage.

Cirrus Logic - Colorado was a pioneer in the development and implementation of computer-generated codes to improve data accuracy. These codes have become widely used in magnetic disk systems over the past few years and are now defacto standards for 5¼ inch Winchester drives. Cirrus Logic - Colorado developed the first low-cost high-performance Reed-Solomon code integrated circuits; the codes implemented therein have become worldwide standards for the optical storage industry. EDAC codes produced by Cirrus Logic - Colorado have become so associated with high data integrity that many users include them in their lists of requirements when selecting storage subsystems.

Cirrus Logic - Colorado licenses EDAC software and discrete and integrated circuit designs for various EDAC codes, offers books and technical reports on EDAC and recording codes, and conducts seminars on error tolerance and data integrity as well as EDAC, recording, and data compression codes.

#### <u>PRODUCTS</u>

- Error tolerant controller designs for magnetic and optical storage.

- Turnkey integrated circuit development.

- Low-cost, high-performance EDAC integrated circuit designs.

- Discrete and integrated circuit designs for high-performance Reed-Solomon codes, product codes, and computer-generated codes.

- Universal encoder/decoder designs for Reed-Solomon codes including bit-serial, time slice, and function sharing designs.

- Multiple-burst EDAC designs for high-end storage devices with highspeed parallel interfaces, supporting record lengths beyond 100,000 bytes.

- EDAC designs supporting QIC tape formats.

- Software written for a number of processors to support integrated circuits implementing Cirrus Logic Colorado's EDAC technology.

- Practical Error Correction Design for Engineers, a book on EDAC written especially for engineers.

- Cirrus Logic Colorado develops polynomials for use in storage products.

#### CONSULTING SERVICES

Consulting services are offered in the following areas:

- Semiconductor memories and large cache memories

- Magnetic disk devices

- Magnetic tape devices

- Optical storage devices using read-only, write-once, and erasable media

- Smart cards

- Communications

#### Consulting services offered include:

- Code selection

- Design of discrete hardware and integrated circuits

- Design of software

- Advice in the selection of synchronization, header, and defect management strategies

- Complex MTBF computations

- Analysis of existing codes and/or designs

- Establishing EDAC requirements from defect data

- Assistance in system integration of integrated circuits implementing Cirrus Logic's EDAC technology.

## PROLOGUE THE COMING REVOLUTION IN ERROR CORRECTION TECHNOLOGY

#### By: Neal Glover

#### Presented at ENDL's 1988 Disk/Test Conference

#### **INTRODUCTION**

The changes that are occurring today in error detection and correction, error tolerance, and failure tolerance are indeed revolutionary. Two major factors are driving the revolution: need and capability. The need arises from more stringent error and failure tolerance requirements due to changes in capacity, through-put, and storage technology. The capability is developing due to continuing increases in VLSI density and decreases in VLSI cost, along with more sophisticated error-correction techniques. This preface discusses the changes in requirements, technology, and techniques that are presently occurring and those that are expected to occur over the next few years.

Some features of today's error-tolerant systems would have been hard to imagine a few years ago.

Some optical storage systems now available are so error tolerant that user data is correctly recovered even if there exists a defect situation so gross that the sector mark, header and sync mark areas of a sector are totally obliterated along with dozens of data bytes.

Magnetic disk drive array systems under development today are so tolerant to errors and failures that simultaneous head crashes on two magnetic disk drives would neither take the system down nor cause any loss of data. Some of these systems will also be able to detect and correct many errors that today go undetected, such as transient errors in unprotected data paths and buffers and even software errors that result in the transfer of the wrong sector. Some magnetic disk drive array systems specify mean time between data loss (MTBDL) in the hundreds of thousands of hours.

The contrast with prior-generation computer systems is stark. Before entering development I spent some time on a team maintaining a large computer at a plant in California that developed nuclear reactors. I will never forget an occasion when the head of computer operations pounded his fist on a desk and firmly stated that if we saw a mushroom cloud over Vallecito it would be the fault of our computer. The mainframe's core memory was prone to intermittent errors. The only checking in the entire computer was parity on tape. Punch card decks were read to tape twice and compared. By the mid-seventies, the computer industry had come a long way in improving data integrity. I had become an advisory engineer in storage-subsystem development, and in 1975 I was again to encounter a very unhappy operations manager when a microcode bug, which I must claim responsibility for, intermittently caused undetected erroneous data to be transferred in a computer system at an automobile manufacturing plant. Needless to say, the consequences were disastrous. This experience taught me the importance of exhaustive firmware verification testing and has influenced my desire to incorporate data-integrity features in Cirrus Logic's designs that are intended to detect and in some cases even correct for firmware errors as well as hardware errors.

Changes in hardware and software data-integrity protection methods are occurring today at a truly revolutionary rate and soon the weaknesses we knew of in the past and those that we live with today will be history forever.

#### THE CHANGING REQUIREMENTS

Requirements for error and failure tolerance increase with capacity and throughput, and changing storage technology. Over the years, many storage systems have specified their non-recoverable read error rate as 1.E-12 events per bit. In many cases this is no longer acceptable. As more sophisticated applications require ever faster access to ever larger amounts of information, system integrators will demand that storage system manufacturers meet much higher data-integrity standards.

As an example of how capacity influences error tolerance requirements, consider a hypothetical write-once optical storage device employing removable 5 gigabyte cartridges. Twenty-five such cartridges would hold 1.E+12 bits, so a non-recoverable read error rate of 1.E-12 would imply the existence of a non-recoverable read error on about one in twenty-five cartridges. Is this acceptable? Would one non-recoverable read error in every 250 platters be acceptable?

As an example of how through-put influences error tolerance requirements, consider a magnetic disk array subsystem which is designed to transfer data simultaneously from all drives and has no redundant drives. The through-put of ten 10-megabit-persecond magnetic disk drives operating with a ten percent read duty cycle would be 8.64E+11 bits per day. A 1.E-12 non-recoverable read error rate would imply one non-recoverable read error every eleven days. Is this acceptable? Would one non-recoverable read error per year be acceptable?

For new storage technologies, it is often not practical to achieve the low media defect event rates which we have been accustomed to handling in magnetic storage. New techniques have been and must continue to be developed and implemented to accommodate higher defect rates and different defect characteristics.

#### THE CHANGING TECHNOLOGY

VLSI density continues to increase, allowing us to incorporate logic on a single integrated circuit today that a few years ago would have required several separate boards. This allows us to implement very complex data-integrity functions within a single IC. Cirrus Logic's low-cost, high-performance, Reed-Solomon code IC's for optical storage devices are a good example. As VLSI densities increase, such functions will occupy a small fraction of the silicon area of a multi-function IC. The ability to place very complex functions on a single IC and further to integrate multiple complex functions on a single IC opens the door for greater data integrity. Our ability to achieve greater data integrity at reasonable cost is clearly one of the forces behind the revolution in error and failure tolerant technology.

Even with the development of cheaper, higher density VLSI technology, it is often more economical to split the implementation of high-performance EDAC systems between hardware and software. Using advanced software algorithms and buffer management techniques, nearly "on-the-fly" correction performance can be achieved at lower cost than using an all-hardware approach.

#### **CHANGES IN ERROR CORRECTION**

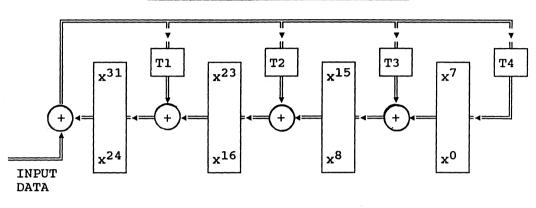

For single-burst correction, Cirrus Logic - Colorado still recommends computergenerated codes. Most new designs employing computer-generated codes are using binary polynomials of degree 48, 56, and 64. In many cases, implementations of the higher degree polynomials include hardware to assist in performing on-the-fly correction.

Economic and technical factors are driving the industry to accommodate higher defect rates to which single-burst error-correction codes are not suited. Consequently, Reed-Solomon codes, a class of powerful codes which allow efficient correction of multiple bursts, are currently being designed into a wide variety of storage products including magnetic tape, magnetic disk, and optical disk. Reed-Solomon codes were discovered more than twenty-five years ago but only recently have improved encoding and decoding algorithms, along with decreased VLSI costs, made them economical to implement. Using software decoding techniques running on standard processors, Cirrus Logic - Colorado now routinely achieves correction times for Reed-Solomon codes that were difficult to achieve with bit-slice designs just a few years ago.

IBM has announced a new version of its 3380 magnetic disk drive that employs multiple-burst error detection and correction, using Reed-Solomon codes, to achieve track densities significantly higher than realizable with previous technology. Single-burst error correction can handle modest defect densities, but defect densities increase exponentially with track density. On-the-fly, multiple-burst error correction and error-tolerant synchronization are required to handle these higher defect densities. On earlier models of the 3380, IBM corrected a single burst in a record of up to several thousand bytes. Using IBM's 3380K error-correction code, under the right circumstances it would be possible to correct hundreds of bursts in a record. A unique feature of the 3380K code is that it can be implemented to perform on-the-fly correction with a data delay that is roughly 100 bytes.

The impact of this IBM announcement, coupled with the general push toward higher track densities, the success of high-performance error detection and correction on optical storage devices, and the availability of low-cost, high-performance EDAC IC's, will stimulate the use of high-performance EDAC codes on a wide range of magnetic disk products. Cirrus Logic - Colorado itself is currently implementing double-burst correcting, Reed-Solomon codes on a wide range of magnetic disk products, ranging from low-end designs which process one bit per clock edge to high-end designs which process sixteen bits per clock edge.

#### **CHANGES IN ERROR DETECTION**

When an error goes undetected, erroneous data is transferred to the user as if it were error free. The transfer of undetected erroneous data can be one of the most catastrophic failures of a data storage system. Some causes of undetected erroneous data transfer are listed below.

- Miscorrection by an error-correction code.

- Misdetection by an error-detection or error-correction code.

- Synchronization failure in an implementation without synchronization framing error protection.

- Intermittent failure in an unprotected data path on write or read.

- Intermittent failure in an unprotected RAM buffer on write or read.

- A software error resulting in the transfer of the wrong sector.

- Failed hardware, such as a failed error latch that never flags an error.

It is important to understand that no error-correction code is perfect; all are subject to miscorrection when an error event occurs that exceeds the code's guarantees. However, it is also important to understand that the miscorrection probability for a code can be reduced to any arbitrarily low level simply by adding enough redundancy. As VLSI costs go down, more redundancy is being added to error-detection and errorcorrection codes to achieve greater detectability of error events exceeding code guarantees. New single-burst error-correction code designs use polynomials of degree 48, 56, and 64 to accomplish the same correctability achieved with degree 32 codes several years ago, but with significantly improved detectability. If correctability is kept the same, detectability is improved more than nine orders of magnitude in moving from a degree 32 code to a degree 64 code.

Error-detection codes are not perfect either; they are subject to misdetection. Like miscorrection, misdetection can be reduced to any arbitrarily low level by adding enough redundancy. Unfortunately, the industry has not, in general, increased the level of detectability of implemented error-detection codes significantly in the last twenty-five years. Two degree 16 polynomials, CRC-16 and CRC-CCITT, have been in wide use for many years. For many storage device applications, there are degree 16 polynomials with superior detection capability, and moreover, the requirements of many applications

would be better met by error-detection polynomials of degree 32 or greater.

In the last few years, the industry has been doing a better job of avoiding pattern sensitivities of error-detection and error-correction codes. Cirrus Logic - Colorado avoids using the Fire code because of its pattern sensitivity, and we use 32-bit auxiliary error detection codes in conjunction with our Reed-Solomon codes in order to overcome their interleave pattern sensitivity.

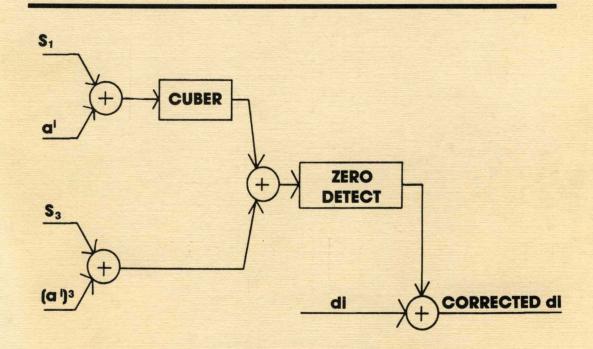

Auxiliary error-detection codes that are used in conjunction with ECC codes to enhance detectability have special requirements. The error-detection code check cannot be made until after correction is complete. It is undesirable to run corrected data through error-detection hardware after performing correction due to the delay involved. It is also not feasible to perform the error-detection code check as data is transferred to the host after correction, since some standard interfaces have no provision for a device to flag an uncorrectable sector after the transfer of data has been completed. To meet these requirements, some error-detection codes developed over the last few years are specially constructed so that their residues can be adjusted as correction occurs. When correction is complete, the residue should have been adjusted to zero. Cirrus Logic - Colorado has been using such error-detection codes since 1982, and such a code is included within Cirrus Logic - Colorado Reed-Solomon code IC's for optical storage. IBM's 3380K also uses such an auxiliary error-detection code.

As the requirements for data integrity have increased, Cirrus Logic - Colorado has tightened its recommendations accordingly. One of the areas needing more attention in the industry is synchronization framing error protection. To accomplish this protection, Cirrus Logic - Colorado now recommends either the initialization of EDAC shift registers to a specially selected pattern or the inversion of a specially selected set of EDAC redundancy bits.

The magnetic disk drive array segment of the industry is making significant gains in detectability. Some manufacturers are adding two redundant drives to strings of ten data drives in order to handle the simultaneous failure of any two drives without losing data. The mean time between data loss (MTBDL) for such a system computed from the MTBF for individual drives may be in the millions of hours. In order for these systems to meet such a high MTBDL, all sources of errors and transient failures that could dominate and limit MTBDL must be identified, and means for detection and correction of such errors and failures must be developed. For these systems, Cirrus Logic - Colorado recommends that a four-byte error-detection code be appended and checked at the host adapter. We also recommend that the logical block number and logical drive number be included in this check. This allows the detection with high probability of a wide variety of errors and transient failures, including the transfer of a wrong sector or transfer of a sector from the wrong drive.

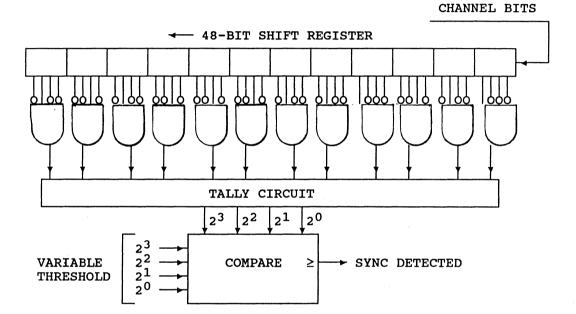

#### CHANGES IN TRACK-FORMAT ERROR TOLERANCE

In many of today's single-burst-correcting EDAC designs, tolerance to errors is limited by the ability to handle errors in the track format rather than by the capability of the data-field EDAC code. In upgrading such designs, it is pointless to change from single-burst to multiple-burst error correction without also improving track-format error tolerance. In the future, all magnetic disk products will use error-tolerant synchronization and header strategies. The optical storage industry has already proved the feasibility of handling error rates as high as 1.E-4 through track-format error tolerance as well as powerful datafield EDAC codes. Optical track-format error tolerance has been achieved using multiple headers, error-tolerant sync marks, and periodic resynchronization within data fields. Some systems now available are so error tolerant that user data is correctly recovered even if there exists a defect situation so gross that the sector mark, header, and sync mark areas of a sector are totally obliterated along with dozens of data bytes.

#### CHANGES IN DEFECT MANAGEMENT

As track densities increase in magnetic recording, and as erasable optical technology becomes more common, many companies will implement defect skipping to handle higher defect densities without significantly affecting performance. This technique is not applicable to write-once optical applications, where sector retirement and reassignment will be used. Such techniques also work well within dynamic defect management strategies. Combining the two will allow the full power of the EDAC code to be used for margin against new defects. Dynamic defect management will become more common, especially for write-once and erasable optical technologies subject to relatively high new defect rates and defect growth.

As more complex and intelligent device interfaces and controllers are implemented, more responsibility for defect management will be shifted from the host to the device controller.

#### CHANGES IN SELF-CHECKING

As data integrity requirements increase, it becomes very important to detect transient hardware failures. New designs for component IC's for controller implementations are carrying parity through the data paths of the part when possible, rather than just checking and regenerating parity. Cirrus Logic - Colorado sees this as a step forward, but we also look beyond, to the day when all data paths are protected by CRC as well.

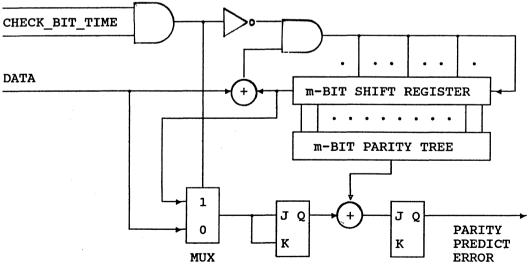

It is especially important to detect transient failures in EDAC hardware. Some companies have implemented parity-predict circuitry to continuously monitor their EDAC shift registers for proper operation.

When possible, Cirrus Logic - Colorado has incorporated circuitry to divide codewords on write by a factor of the code generator polynomial and check for zero remainder. This function is performed as close to the recording head as possible.

Cirrus Logic - Colorado's 8520 IC uses dynamic cells for the major EDAC shift registers. To detect transient failures in the shift registers themselves, we incorporated a feature whereby the parity of all bits going into a shift register is compared with the parity of all bits coming out of the shift register.

#### CHANGES IN VERIFICATION AND TESTING

The traditional diagnostic technique for storage-device EDAC circuitry uses write

long and read long. For write-once optical media, this technique has two problems. Since these are high error rate devices, real errors may be encountered along with simulated errors. Also, each write long operation uses up write-once media. Cirrus Logic - Colorado incorporates a special diagnostic mode in its EDAC IC's that allows the EDAC hardware to be tested without writing to or reading from the media.

The introduction of complex, high-performance hardware and software algorithms for error correction and track-format error tolerance introduce new verification and testing challenges. Cirrus Logic - Colorado verifies its error-correction software for optical storage devices against millions of test cases. To verify the track-format error tolerance of optical storage devices, Cirrus Logic - Colorado recommends a track format simulator that allows all forms of errors to be simulated, including slipped PLL cycles. Cirrus Logic - Colorado plans to market such a track simulator in the future. Cirrus Logic - Colorado also recommends programmable buggers to allow all forms of errors to be simulated during the performance of a wide range of operational tasks on real devices.

#### CHALLENGES FOR THE FUTURE

Many of the factors shaping the future of error correction and error tolerance have already been discussed. One of the most significant will be carry-through error detection that will be generated and checked for each sector at the host adapter. The redundancy for this overall check will include the logical block number and the logical drive number and will cover the entire path from the host adapter to the media and back. A logical next step will be for hosts to provide an option for carrying all or part of the overall check code redundancy through host memory when data is being moved from one device to another. Looking further into the future, we may also see the redundancy for the overall check maintained in host memory for those sectors that are to be updated. In this case, an updatable error-detection code will be used and the error-detection redundancy will be adjusted for each change made to the contents of the sector.

An area that needs more attention is verification that we will be able to properly read back all the data that we write. To avoid adversely impacting performance, we must be able to accomplish this without following each write with a verify read. At the closest possible point to the head we need to verify that the written user write data and associated redundancy constitute a valid codeword. A good forward step in this direction would be to decode the write encoded RLL bits back to data bits and to divide this data stream by the code generator polynomial or compare it to the write data stream going into the encoder.

## CONTENTS

| l                                            | Page        |

|----------------------------------------------|-------------|

| Preface                                      | v           |

| About Cirrus Logic - Colorado                | vi          |

| Prologue                                     | <b>'iii</b> |

| CHAPTER 1 - INTRODUCTION.                    | 1           |

| 1.1 Introduction to Error Correction         | 1           |

| 1.2 Mathematical Foundations                 | 8           |

| 1.3 Polynomials and Shift Register Sequences | 16          |

| CHAPTER 2 - EDAC FUNDAMENTALS                | 49          |

| 2.1 Detection Fundamentals                   | 49          |

| 2.2 Correction Fundamentals                  | 56          |

| 2.3 Decoding Fundamentals                    | 67          |

| 2.4 Decoding Shortened Cyclic Codes          | 32          |

| 2.5 Introduction to Finite Fields            | 37          |

| 2.6 Finite Field Circuits                    | )3          |

| 2.7 Subfield Computation                     | 29          |

| CHAPTER 3 - CODES AND CIRCUITS               | 35          |

| 3.1 Fire Codes                               | 35          |

| 3.2 Computer-Generated Codes                 | ю           |

| 3.3 Binary BCH Codes                         | 5           |

| 3.4 Reed-Solomon Codes                       | 8           |

| 3.5 b-Adjacent Codes                         | 15          |

| CHAPTER 4 - APPLICATION CONSIDERATIONS              |

|-----------------------------------------------------|

| 4.1 Raw Error Rates and Nature of Error             |

| 4.2 Decoded Error Rates                             |

| 4.3 Data Recoverability                             |

| 4.4 Data Accuracy                                   |

| 4.5 Performance Requirements                        |

| 4.6 Pattern Sensitivity                             |

| 4.7 K-Bit-Serial Techniques                         |

| 4.8 Synchronization                                 |

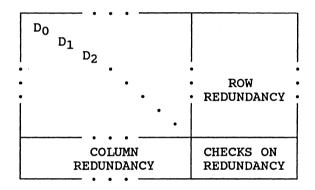

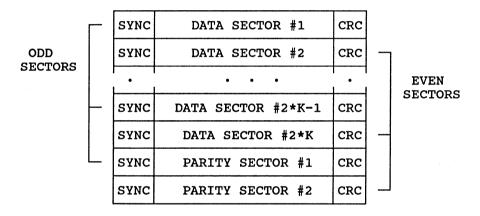

| 4.9 Interleaved, Product and Redundant Sector Codes |

| CHAPTER 5 - SPECIFIC APPLICATIONS                   |

| 5.1 Evolution of EDAC Schemes                       |

| 5.2 Application to Large-Systems Magnetic Disk      |

| 5.3 Application to Small-Systems Magnetic Disk      |

| 5.4 Application to Mass-Storage Devices             |

| CHAPTER 6 - TESTING OF ERROR-CONTROL SYSTEMS        |

| 6.1 Microdiagnostics                                |

| 6.2 Host Software Diagnostics                       |

| 6.3 Verifying an ECC Implementation                 |

| 6.4 Error Logging                                   |

| 6.5 Hardware Self-Checking                          |

## **CHAPTER 1 - INTRODUCTION**

#### 1.1 INTRODUCTION TO ERROR CORRECTION

#### 1.1.1 A REVIEW OF PARITY

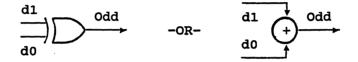

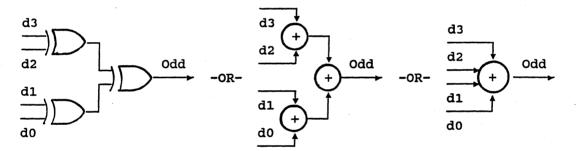

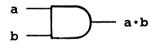

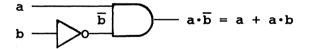

A byte, word, vector, or data stream is said to have odd parity if the number of '1's it contains is odd. Otherwise, the byte, word, vector, or data stream is said to have even parity. Parity may be determined with combinational or sequential logic.

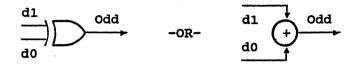

The parity of two bits may be determined with an EXCLUSIVE-OR (XOR) gate. The circled '+' symbol is understood to represent XOR throughout this book.

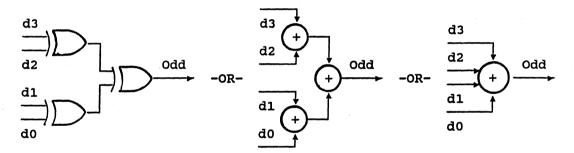

Parity across a nibble may be determined with a parity tree.

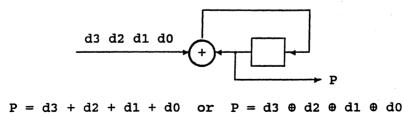

Parity of a bit stream may be determined by a single shift register stage and one XOR gate. The shift register is assumed to be initialized to zero. The highest numbered bit is always transmitted and received first.

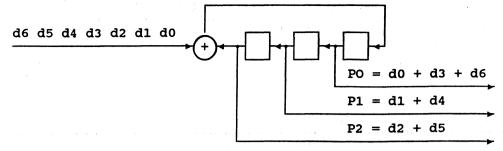

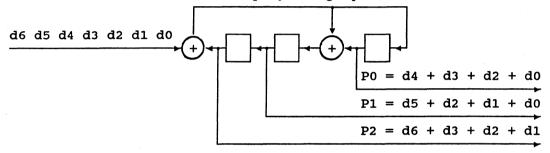

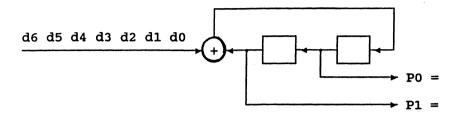

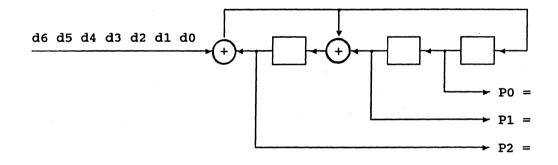

The circuit below determines parity across groups of data stream bits.

Note that each bit is included in only one parity check.

The circuit below will also determine parity across groups of data stream bits.

The contribution of each data bit to the final shift register state is shown below. Each data bit affects a unique combination of parity checks.

| <u>Data Bit</u> | Contribution <u>P2 P1 P0</u> |

|-----------------|------------------------------|

|                 |                              |

| d6              | 100                          |

| d5              | 010                          |

| d4              | 001                          |

| d3              | 101                          |

| d2              | 111                          |

| d1              | 110                          |

| d0              | 011                          |

|                 |                              |

The contributions to the final shift register state made by several strings of data bits are shown below.

|               |    | Contribution    |

|---------------|----|-----------------|

| <u>String</u> |    | <u>P2 P1 P0</u> |

| d6,d4         | => | 101             |

| d3,d2,d0      | => | 001             |

| d4,d0         | => | 010             |

- 2 -

| SUPPLEMENTAR         | Y P         | ROB         | LEI        | MS        | •        | •         | •         | •         |            | •  | •      | •        | •       | •        | •        | •  | • | • | • | • | • | • | • | • | • | 370 |

|----------------------|-------------|-------------|------------|-----------|----------|-----------|-----------|-----------|------------|----|--------|----------|---------|----------|----------|----|---|---|---|---|---|---|---|---|---|-----|

| APPENDIX A.PR        | IME         | FAC         | сто        | RS        | 0        | F2        | 2N        | -1.       | •          | •  | •      | •        | •       | •        | •        | •  | • | • | • | • | • | • | • | • | • | 374 |

| APPENDIX B. ME<br>EX | ETHO<br>PON | DDS<br>IENT | OF<br>[IA] | FII<br>LS | NE<br>O` | DIN<br>/E | ig<br>R / | LC<br>A F | )G.<br>FIN | AF | E<br>E | TH<br>FI | M<br>EI | S /<br>D | A1<br>'. | NE | ) | • | • | • | • | • | • | • | • | 375 |

| ABBREVIATIONS        | ;           | • •         | • •        | •         | •        | •         | •         |           | •          | •  | •      | •        | •       | •        | •        | •  | • | • | • | • | • | • | • | • | • | 403 |

| GLOSSARY             | •••         | •••         | • •        | •         | •        | •         | •         |           | •          | •  | •      | •        | •       | •        | •        | •  | • | • | • | • | • | • | • | • | • | 404 |

| BIBLIOGRAPHY.        | ••          | •••         | • •        | •         | •        | •         | •         | ••        | •          | •  | • ·    | •        | •       | •        | •        | •  | • | • | • | • | • | • | • | • | • | 419 |

| INDEX                |             |             |            | •         | •        | •         | •         |           | •          | •  | •      | •        | •       | •        | •        | •  | • | • | • | • | • | • | • | • | • | 463 |

:

## **CHAPTER 1 - INTRODUCTION**

#### 1.1 INTRODUCTION TO ERROR CORRECTION

#### 1.1.1 A REVIEW OF PARITY

A byte, word, vector, or data stream is said to have odd parity if the number of '1's it contains is odd. Otherwise, the byte, word, vector, or data stream is said to have even parity. Parity may be determined with combinational or sequential logic.

The parity of two bits may be determined with an EXCLUSIVE-OR (XOR) gate. The circled '+' symbol is understood to represent XOR throughout this book.

Parity across a nibble may be determined with a parity tree.

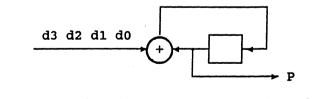

Parity of a bit stream may be determined by a single shift register stage and one XOR gate. The shift register is assumed to be initialized to zero. The highest numbered bit is always transmitted and received first.

$P = d3 + d2 + d1 + d0 \quad or \quad P = d3 \oplus d2 \oplus d1 \oplus d0$

- 1 -

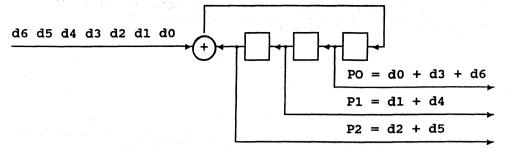

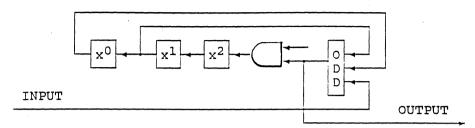

The circuit below determines parity across groups of data stream bits.

Note that each bit is included in only one parity check.

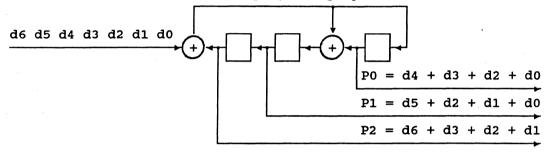

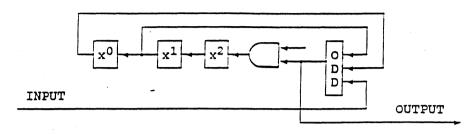

The circuit below will also determine parity across groups of data stream bits.

The contribution of each data bit to the final shift register state is shown below. Each data bit affects a unique combination of parity checks.

| <u>Data Bit</u> | Contribution<br><u>P2 P1 P0</u> |

|-----------------|---------------------------------|

| d6              | 100                             |

| d5              | 010                             |

| d4              | 001                             |

| d3              | 101                             |

| d2              | 111                             |

| d1              | 110                             |

| <b>d</b> 0      | 011                             |

|                 |                                 |

The contributions to the final shift register state made by several strings of data bits are shown below.

|               |    | Contribution    |

|---------------|----|-----------------|

| <u>String</u> |    | <u>P2 P1 P0</u> |

| d6,d4         | => | 101             |

| d3,d2,d0      | => | 001             |

| d4,d0         | => | 010             |

- 2 -

The contribution to the final shift register state by each string is the XOR sum of contributions from individual bits of the string, because the circuit is linear. For a linear function f:

$$f(x+y) = f(x)+f(y)$$

The parity function P is linear, and therefore

$$P(x+y) = P(x)+P(y)$$

Circuits of this type are the basis of many error-correction systems.

#### 1.1.2 A FIRST LOOK AT ERROR CORRECTION

This discussion presents an introduction to single-bit error correction using a code that is intuitive and simple. Consider the two-dimensional parity-check code defined below.

| + P0 |

|------|

| + P1 |

| + P2 |

| + P3 |

| + P4 |

| + P5 |

| + P6 |

| + P7 |

|      |

|   | d0            | d1  | d2  | d3  |  | P7 |  |  |  |  |  |

|---|---------------|-----|-----|-----|--|----|--|--|--|--|--|

|   | d4            | d5  | d6  | d7  |  | Pe |  |  |  |  |  |

|   | d8            | d9  | d10 | d11 |  | P5 |  |  |  |  |  |

|   | d12           | d13 | d14 | d15 |  | P4 |  |  |  |  |  |

| 1 |               |     |     |     |  |    |  |  |  |  |  |

|   | P0            | P1  | P2  | P3  |  |    |  |  |  |  |  |

|   | Column Checks |     |     |     |  |    |  |  |  |  |  |

|   |               |     |     |     |  |    |  |  |  |  |  |

Row Checks

One of the eight required check/syndrome circuits is shown below.

On write, each row check bit is selected to make the parity of its row even. Each column check bit is selected to make the parity of its column even. The data bits and the parity bits together are called a codeword.

On read, row syndrome bits are generated by checking parity across each row, including the row check bit. Column syndrome bits are generated in a similar fashion. Syndrome means symptom of error. For this code, syndrome bits can be viewed as the XOR differences between read checks and write checks. If there is no error, all syndrome bits are zero.

When a single-bit error occurs, one row and one column will have inverted syndrome bits (odd parity). The bit in error is at the intersection of this row and column.

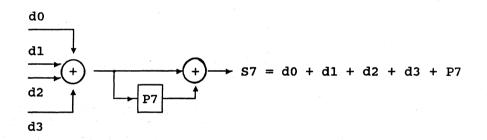

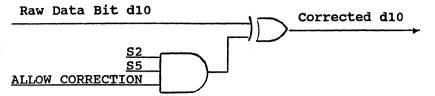

The circuit above shows the logic necessary for generating the write-check bit and the syndrome bit for one row. For parallel decoding, this logic is required for each row and column. Also, 16 AND gates are required for detecting the intersections of inverted row and column syndrome bits. In addition, 16 XOR gates are required for inverting data bits. The correction circuit for one particular data bit is shown below.

Two data bits in error will cause either two rows, two columns, or both to have inverted syndrome bits (odd parity). This condition can be trapped to give the code the capability to detect double-bit errors in data.

All single check-bit errors are detected, but not all double check-bit errors. One row and one column check bit in error will result in miscorrection (false correction). If an overall check bit across data is added, the code is capable of detecting all double-bit errors in data and check bits. This includes the case where one data bit and one parity bit are in error. The overall check bit can be generated by forming parity across all row or all column check bits. With the overall check bit added, all double-bit errors are detectable but uncorrectable.

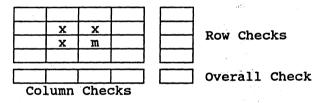

Miscorrection occurs when three bits are in error on three corners of a rectangle. For example:

The three errors which are illustrated above cause the decoder to respond as if there were a single-bit error at location m. Miscorrection does not result for all combinations of three bits in error, only for those where there are errors on three corners of a rectangle.

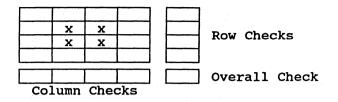

Miscorrection probability for three-bit errors is the ratio of three-bit error combinations that result in miscorrection to all possible three bit-error combinations. Misdetection (error condition not detected at all) occurs when four-bits are in error on the corners of a rectangle. For example:

This error condition leaves all syndrome bits equal to zero.

Misdetection does not result for all combinations of four bits in error, only those where there are errors on four corners of a rectangle. Misdetection probability for four-bit errors is the ratio of four-bit error combinations that result in misdetection to all possible four-bit error combinations.

This discussion introduced the following error-correction concepts:

- Check bits

- Syndromes

- Codeword

- Correctable error

- Detectable error

- Miscorrection

- Misdetection

- Miscorrection probability

- Misdetection probability

#### **PROBLEMS**

1. Write the parity check equations for the circuit below.

2. Write the parity check equations for the circuit below.

3. Generate a chart showing the contribution of each data bit to the final shift register state for the circuits shown above.

If the data stream is zeros except for d3 and d1, what is the final shift register state?

#### **1.2 MATHEMATICAL FOUNDATIONS**

#### 1.2.1 SOME DEFINITIONS, THEOREMS AND ALGORITHMS FOR INTEGERS

<u>Definition 1.2.1</u>. When we say an integer a divides an integer b we mean a divides b with zero remainder. "a divides b" is written as a|b. "a does not divide b" is written as a/b.

<u>Examples</u>: 3|6, 3/4, 2/1

**Definition 1.2.2.** An integer a is called prime if a is greater than 1 and there are no divisors of a that are less than a but greater than 1. If an integer a greater than 1 is not prime, then it is called composite.

Examples: 2, 3, and 5 are prime

4, 6, and 8 are composite

<u>Definition 1.2.3</u>. The greatest common divisor (GCD) of a set of integers  $\{a_1, a_2, \dots, a_n\}$  is the largest positive integer that divides each of  $a_1, a_2, \dots, a_n$ . The greatest common divisor may be written as  $GCD(a_1, a_2, \dots, a_n)$ .

<u>Algorithm 1.2.1</u>. To find GCD $(a_1, a_2, \dots, a_n)$ , express each integer as the product of prime factors. Form the product of their common factors. For repeated factors, include in the product the highest power that is a factor of all the given integers. The GCD is the absolute value of the product. If there are no common factors, the GCD is one.

Examples:  $GCD(3,9,15) = GCD(3,3^2,3^{*5}) = 3$   $GCD(-165,231) = GCD(-3^{*5}*11,3^{*7}*11) = 33$   $GCD(105,165) = GCD(3^{*5}*7,3^{*5}*11) = 15$  $GCD(45,63,297) = GCD(3^{2}*5,3^{2}*7,3^{3}*11) = 9$

The GCD can also be found using Euclid's Algorithm.

<u>Definition 1.2.4</u>. The least common multiple (LCM) of a set of integers  $\{a_1, a_2, \dots, a_n\}$  is the smallest positive integer that is divisible by each of  $a_1, a_2, \dots, a_n$ . The least common multiple may be written LCM $(a_1, a_2, \dots, a_n)$ .

<u>Algorithm 1.2.2</u>. To find LCM $(a_1, a_2, \dots, a_n)$ , express each integer as a product of prime factors. Form the product of primes that are a factor of any of the given integers. Common factors between two or more integers are included in the product only once. For repeated factors, include in the product the highest power that occurs in any of the prime factorizations. The LCM is the absolute value of the product.

| Examples: | LCM(6,15,21) = LCM(2*3,3*5,3*7)                  | = | 210   |

|-----------|--------------------------------------------------|---|-------|

|           | LCM(30,42,66) = LCM(2*3*5,2*3*7,2*3*11)          | = | 2310  |

|           | LCM(-15,21,11)=LCM(-3*5,3*7,11)                  | = | 1155  |

|           | $LCM(45,63,297) = LCM(3^{2}*5,3^{2}*7,3^{3}*11)$ | = | 10395 |

- 8 -

<u>Theorem 1.2.1</u>. Every integer a > 1 can be expressed as the product of primes, (with at least one factor).

Examples: 3 = 36 = 2\*315 = 3\*5

<u>Definition 1.2.5</u>. Integers a and b are relatively prime if their greatest common divisor is 1.

Examples: 3, 7 3, 4 15, 77

<u>Theorem 1.2.2</u>. Let integers a, b, and c be relatively prime in pairs, then a\*b\*c divides d if, and only if, each of a, b, and c divide d.

Examples: 3|15, 5|15, 7∤15, therefore, (3\*5\*7)∤15 3|210, 5|210, 7|210, therefore, (3\*5\*7)|210

<u>Theorem 1.2.3</u>. Let an integer a be prime, then a divides b\*c\*d if, and only if, a divides b or c or d.

Examples: 3|6, therefore, 3|(6\*5\*7)3/5, 3/7, 3/11, therefore, 3/385

<u>Definition 1.2.6</u>. Let x be any real number. The integer function of x, written as INT(x), is the greatest integer less than or equal to x.

Examples: INT(1/2) = 0INT(5/3) = 1INT(-1/2) = -1

<u>Definition 1.2.7</u>. Let x and y be any real numbers. x modulo y, written as x MOD y, is defined as follows:

x MOD y = x - y \* INT(x/y)

~

Examples: 5 MOD 3 = 29 MOD 3 = 0 -5 MOD 7 = 2

#### **1.2.2 SOME DEFINITIONS, THEOREMS AND ALGORITHMS FOR POLYNOMIALS**

<u>Definition 1.2.8</u>. A polynomial is said to be monic if the coefficient of the term with the highest degree is 1.

<u>Definition 1.2.9</u>. The greatest common divisor of two polynomials is the monic polynomial of greatest degree which divides both.

<u>Definition 1.2.10</u>. The least common multiple of a(x) and b(x) is some c(x) divisible by each of a(x) and b(x), which itself divides any other polynomial that is divisible by each of a(x) and b(x).

<u>Definition 1.2.11</u>. If the greatest common divisor of two polynomials is 1, they are said to be relatively prime.

<u>Definition 1.2.12</u>. A polynomial of degree n is said to be irreducible if it is not divisible by any polynomial of degree greater than 0 but less than n.

<u>Theorem 1.2.4</u>. Let a(x), b(x), and c(x) be relatively prime in pairs, then  $a(x) \cdot b(x) \cdot c(x)$  divides d(x) if, and only if, a(x) and b(x) and c(x) divide d(x).

<u>Theorem 1.2.5.</u> Let a(x) be irreducible, then a(x) divides  $b(x) \cdot c(x) \cdot d(x)$  if, and only if, a(x) divides b(x) or c(x) or d(x).

<u>Definition 1.2.13</u>. A function is said to be linear if the properties stated below hold:

a. <u>Linearity</u>:  $f(a \cdot x) = a \cdot f(x)$

b. <u>Superposition</u>: f(x+y) = f(x)+f(y)

#### 1.2.3 THE CHINESE REMAINDER METHOD

There are times when integer arithmetic in a modular notation is preferred to a fixed radix notation. The integers are represented by residues modulo a set of relatively prime moduli.

Example: Assume integers are represented by residues modulo the moduli 3 and 5.

|                         | <u>Integer(k)</u> | Resid | ues(r0, | <u>r1)</u> |

|-------------------------|-------------------|-------|---------|------------|

|                         | 0                 | 0     | 0       |            |

| .7                      | 1                 | 1     | 1       |            |

| 0                       | 2                 | 2     | 2       |            |

| <b>_</b>                | 3                 | 0     | 3       |            |

|                         | 4                 | 1     | 4       |            |

| 0 / )                   | 5                 | 2     | 0       |            |

| 4 1                     | 6                 | 0     | 1       |            |

|                         | 7                 | 1     | 2       |            |

|                         | 8                 | 2     | 3       |            |

| $2 \ 1 \ 3 \ 2$         | 9                 | 0     | 4       |            |

|                         | 10                | 1     | 0       |            |

| MODULUS = 3 MODULUS = 5 | 11                | 2     | 1       |            |

|                         | 12                | 0     | 2       |            |

|                         | 13                | 1     | 3       |            |

|                         | 14                | 2     | 4       | -          |

|                         | 15                | 0     | 0       | -          |

|                         | 16                | 1     | 1       |            |

Notice that the integer k has a unique representation in residues from k=0 through k=14. The integer k=15 has the same representation as k=0. In this case, the total number of integers that have unique representation is 15. In general, the total number of integers n having unique representation is given by the equation:

$n = LCM(e_0, e_1, \cdot \cdot \cdot)$

where the e; are moduli.

There are also times when an integer d must be determined if its residues modulo a set of moduli are given. This can be accomplished with the Chinese Remainder Method. This method is based on the Chinese Remainder Theorem. See any number theory text.

11 -

### <u>METHOD</u>

$e_{i} = Moduli \quad (The e_{i} must be relatively prime in pairs)$   $n = LCM (e_{0}, e_{1}, \cdots)$   $m_{i} = n/e_{i}$   $A_{i} = Constants such that (A_{i}*m_{i}) MOD e_{i} = 1$   $r_{i} = Residues$   $d = desired integer = (A_{0}*m_{0}*r_{0} + A_{1}*m_{1}*r_{1} + \cdots) MOD n$   $e_{i} = 3,5 (e_{0}=3, e_{1}=5)$  n = LCM(3,5) = 15  $m_{0} = n/e_{0} = 15/3 = 5$ This calculation

is performed at

#### **EXAMPLE**

$e_{1} = 3,5 (e_{0}=3, e_{1}=5)$  n = LCM(3,5) = 15  $m_{0} = n/e_{0} = 15/3 = 5$   $m_{1} = n/e_{1} = 15/5 = 3$   $A_{0}*5 \text{ MOD } 3 = 1$ , therefore  $A_{0} = 2$   $A_{1}*3 \text{ MOD } 5 = 1$ , therefore  $A_{1} = 2$   $d = (10*r_{0} + 6*r_{1}) \text{ MOD } 15$ If  $r_{0}, r_{1} = 2,3$  then d = 8If  $r_{0}, r_{1} = 1,3$  then d = 13This calculation is performed at execution time.

# <u>A PROCEDURE FOR PERFORMING THE CHINESE REMAINDER METHOD</u> <u>WITHOUT USING MULTIPLICATION</u>

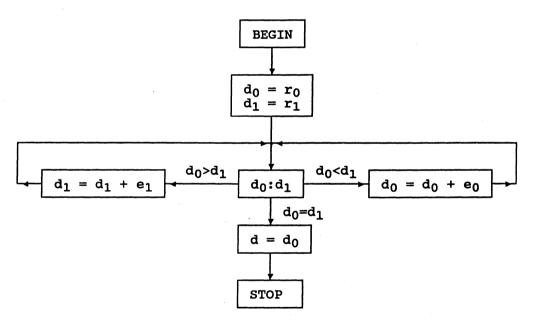

Frequently, the Chinese Remainder Method must be solved on a processor that does not have a multiply instruction. A procedure using only addition and compare instructions is described below.

The integer d is to be determined where d is the least integer such that:

d MOD

$$e_0 = r_0$$

and simultaneously d MOD  $e_1 = r_1$

or equivalently,

$\frac{d}{e_0} = n_0 + \frac{r_0}{e_0} \quad \text{and simultaneously} \quad \frac{d}{e_1} = n_1 + \frac{r_1}{e_1}$

**Rearranging gives**

$d = n_0 * e_0 + r_0$  and simultaneously  $d = n_1 * e_1 + r_1$

or,

$d = n_0 * e_0 + r_0 = n_1 * e_1 + r_1$

Multiplication can be expressed as repeated addition. Therefore,

$$d = r_0 + \underbrace{e_0 + e_0 + \cdots}_{n_0 \text{ times}} = r_1 + \underbrace{e_1 + e_1 + \cdots}_{n_1 \text{ times}}$$

A procedure for finding d based on the relationship above is detailed in the following flowchart.

#### 1.2.4 MULTIPLICATION BY SHIFTING, ADDING, AND SUBTRACTING

Many 8-bit processors do not have a multiply instruction. This discussion describes techniques to minimize the complexity of multiplying a variable by a constant, These techniques provide another alternative for when these processors are used. accomplishing the multiplications required in performing the Chinese Remainder Method.

On an 8-bit processor any shift that is a multiple of 8 bits can be accomplished with register moves. Therefore, multiplying by a power of 2 that is a multiple of 8 can be accomplished by register moves. Any string of ones in a binary value can be represented by the power of 2 that is just greater than the highest power of 2 in the string minus the lowest power of 2 in the string. These results can be used to minimize the complexity of multiplying a variable by a constant using register moves, shifts, adds and subtracts.

Examples: In all examples, x is less than 256. The results are shown in a form where register moves and shifts are identifiable.

$$y = 255 * x$$

=  $(2^{8}-1) * x$

=  $2^{8} * x - x$

$$y = 257 * x$$

=  $(2^{8}+1) * x$

=  $2^{8} * x + x$

$$y = 992 * x$$

=  $(2^{9}+2^{8}+2^{7}+2^{6}+2^{5}) * x$

=  $(2^{10}-2^{5}) * x$

=  $2^{10} * x - 2^{5} * x$

$$y = 32131 * x$$

=  $(2^{14}+2^{13}+2^{12}+2^{11}+2^{10}+2^{8}+2^{7}+2^{1}+2^{0}) * x$

$$= (2^{15} - 2^9 - 2^7 + 2^1 + 2^0) * x$$

=  $2^{15} * x - 2^9 * x - 2^7 * x + 2^1 * x + 2^0 * x$

=

$= 2^{8} * (2^{7} * x) - (2^{7} * x) - 2^{8} * (2^{1} * x) + (2^{1} * x) + x$

In the last example, only two unique shift operations are required even though the original constant contains nine powers of 2. This particular example is from the Chinese Remainder Method when moduli 255 and 127 are used.

### <u>PROBLEMS</u>

- 1. Find the GCD of 70 and 15.

- 2. Find the GCD of 70 and 11.

- 3. Find the LCM of 30 and 42.

- 4. Find the LCM of 33 and 10.

- 5. Express 210 as a product of primes.

- 6. Are 70 and 15 relatively prime?

- 7. Are 70 and 11 relatively prime?

- 8. Determine a

- $\begin{array}{rcl} a &=& INT(7/3) &=& \\ a &=& -INT(1/3) &=& \\ a &=& INT(-1/3) &=& \\ a &=& 10 \text{ MOD } 3 &=& \\ a &=& -3 \text{ MOD } 15 &=& \\ a &=& 254 \text{ MOD } 255 =& \end{array}$

- 9. Is  $2 \cdot x^2 + 1$  a monic polynomial?

- 10. Write the residues modulo the moduli 5 and 7 of the integer 8.

- 11. The residues for several integers modulo 5 and 7 are listed below. Compute the  $A_i$  of the Chinese Remainder Method. Then use the Chinese Remainder Method to determine the integers.

a MOD 5 = 4, a MOD 7 = 6, a = ? a MOD 5 = 3, a MOD 7 = 5, a = ? a MOD 5 = 0, a MOD 7 = 4, a = ?

What is the total number of unique integers that can be represented by residues modulo 5 and 7?

- 12. Define a fast division algorithm for dividing by 255 on an 8-bit processor that does not have a divide instruction. The dividend must be less than 65536.

- 13. What is the total number of unique integers that can be represented by residues modulo 4 and 11?

#### 1.3 POLYNOMIALS AND SHIFT REGISTER SEQUENCES

#### **1.3.1 INTRODUCTION TO POLYNOMIALS**

It is convenient to consider the symbols of a binary data stream to be coefficients of a polynomial in a variable x, with the powers of x serving as positional indicators. These polynomials can be treated according to the laws of ordinary algebra with one exception: coefficients are to be added modulo-2 (EXCLUSIVE-OR sum). The '+' operator will be used to represent both ordinary addition and modulo-2 addition; when used to represent modulo-2 addition, it will usually be separated from its operands by a preceding and a following space.

As with polynomials of ordinary algebra, these polynomials have properties of associativity, distributivity, and commutativity. These polynomials also factor into prime or irreducible factors in only one way, just as do those of ordinary algebra.

For now, the value of coefficients will be either '1' or '0' depending on the value of the corresponding data bit. Such polynomials are said to have binary coefficients or to have coefficients from the field of two elements. Later, polynomials with coefficients other than '1' and '0' will be discussed. When transmitting and receiving polynomials, the highest order symbol is always transmitted or received first.

#### MULTIPLICATION OF POLYNOMIALS

Multiplication is just like ordinary multiplication of polynomials, except the addition of coefficients is accomplished with the XOR operation (modulo-2 addition).

| Example #1: | $\begin{array}{r} x^3 \\ \cdot x^3 + x + 1 \end{array}$ | -or- | 1000<br>• 1011       |

|-------------|---------------------------------------------------------|------|----------------------|

|             | $x^{6} + x^{4} + x^{3}$                                 |      | 1000<br>1000<br>1000 |

|             |                                                         |      | 1011000              |

| Example #2: | x+1 -or-              | 11            |

|-------------|-----------------------|---------------|

|             | $\cdot x^3 + x + 1$   | <u>• 1011</u> |

|             | $x^4 + x^3$           | 11            |

|             | $x^2 + x$             | 11            |

|             | <u> </u>              | 11            |

|             | $x^4 + x^3 + x^2 + 1$ | 11101         |

In example #2, unlike in ordinary polynomial multiplication, the two x terms cancel.

# **DIVISION OF POLYNOMIALS**

Division is just like ordinary division of polynomials, except the addition of coefficients is accomplished with the XOR operation (modulo-2 addition).

Example #1:

| <u>.010   1</u> . | $x^2 + 1$          |      |      | 101    |

|-------------------|--------------------|------|------|--------|

| $x^3 + x + 1$     | x <sup>5</sup> + 1 | -OR- | 1011 | 100001 |

|                   | $x^5 + x^3 + x^2$  |      |      | 1011   |

|                   | $x^3 + x^2 + 1$    |      |      | 1101   |

|                   | $x^3 + x + 1$      |      |      | 1011   |

|                   | $x^2 + x$          |      |      | 0110   |

|                   |                    |      |      |        |

Example #2:

|               | $x^2 + 1$         |      |      | 101    |

|---------------|-------------------|------|------|--------|

| $x^3 + x + 1$ | $x^5 + x^2 + 1$   | -OR- | 1011 | 100101 |

|               | $x^5 + x^3 + x^2$ |      |      | 1011   |

| • .           | $x^{3} + 1$       |      |      | 1001   |

|               | $x^3 + x + 1$     |      |      | 1011   |

|               | x                 |      |      | 0010   |

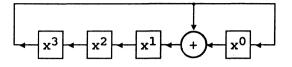

### **1.3.2 INTRODUCTION TO SHIFT REGISTERS**

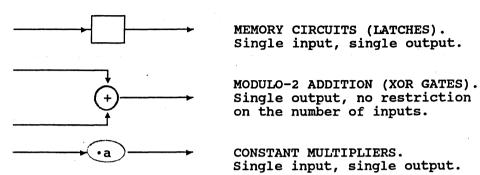

A linear sequential circuit (LSC) is constructed with three building blocks. Any connection is permissible as long as a single output arrow of one block is mated to a single input arrow of another block.

Latches are clocked by a synchronous clock. The output of a latch at any point in time is the binary value that appeared on its input one time unit earlier.

The output of a modulo-2 adder at any point in time is the modulo-2 sum of the inputs at that time.

For now, a constant multiplier ' $\cdot a$ ' will be either ' $\cdot 1$ ' or ' $\cdot 0$ '. If such a constant multiplier is ' $\cdot 1$ ', a connection exists. No connection exists for a constant multiplier of ' $\cdot 0$ '.

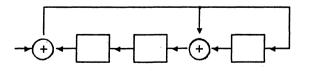

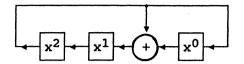

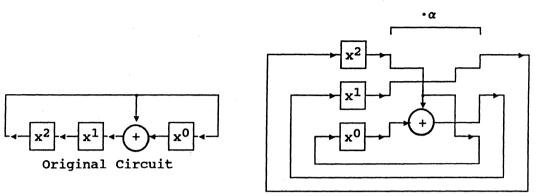

AN EXAMPLE OF AN LSC

A linear sequential circuit of the above form is also called a linear feedback shift register (LFSR), a linear shift register (LSR) or simply a shift register (S/R).

AN EOUIVALENT CIRCUIT WHERE  $a_1 = 0$ ,  $a_2 = 1$ ,  $a_3 = 1$

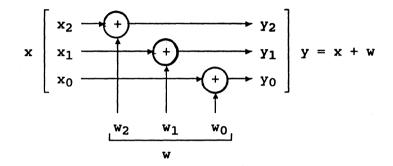

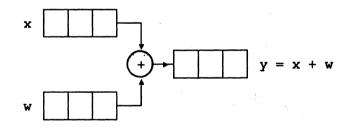

## SHIFT REGISTER IMPLEMENTATION OF MULTIPLICATION

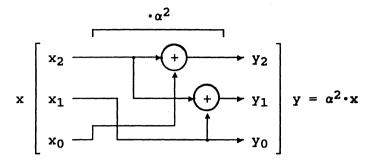

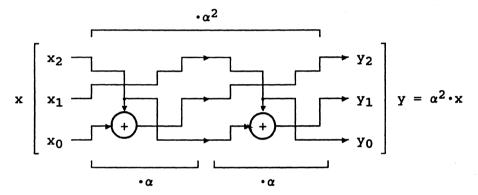

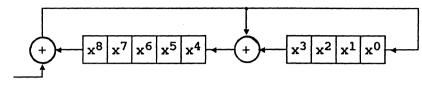

Polynomial multiplication can be implemented with a linear shift register.

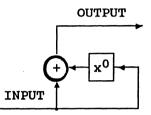

The circuit below will multiply any input bit stream (input polynomial) by (x + 1). The product appears on the output line. The number of shifts required is equal to the sum of the degrees of the input polynomial and the multiplier polynomial plus one.

| Example #1: | Assume the in | put pol | ynomial to be ( | (x <sup>3</sup> + x | <sup>3</sup> + 1). |  |

|-------------|---------------|---------|-----------------|---------------------|--------------------|--|

|             |               |         |                 |                     |                    |  |

| Input                                                              | Shift Reg                  | Output                                    |

|--------------------------------------------------------------------|----------------------------|-------------------------------------------|

| Bit                                                                | <u>State</u>               | Bit                                       |

| 1 (x <sup>5</sup> )<br>0<br>1 (x <sup>3</sup> )<br>0<br>1 (1)<br>0 | 1<br>0<br>1<br>0<br>0<br>1 | 1 (x6) 1 (x5) 1 (x4) 1 (x3) 0 1 (x) 1 (1) |

<u>Example #2</u>: Assume the input polynomial to be  $x^3$ .

| Input<br>Bit             | Shift Reg<br><u>State</u> | Output<br>Bit                    |

|--------------------------|---------------------------|----------------------------------|

| 1 (x <sup>3</sup> )<br>0 | 1<br>0                    | $1 (x^4)$<br>1 (x <sup>3</sup> ) |

| 0                        | 0                         | 0                                |

| 0                        | 0                         | 0                                |

| 0                        | 0                         | 0                                |

NOTE:

The shift register state is shown after the indicated input bit is clocked.

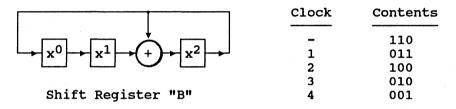

The circuits below will multiply any input bit stream (input polynomial) by  $(x^3 + x + 1)$ .

Shift Register "B"

<u>Example #1</u>: Assume the input polynomial to be  $x^3$ .

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | I |

|------------------------------------------------------|---|

Example #2: Assume the input polynomial to be (x + 1).

| Input      | Shift Req | Output              |

|------------|-----------|---------------------|

| <u>Bit</u> | 'B' State | <u>Bit</u>          |

| 1(x)       | 011       | 1 (x <sup>4</sup> ) |

| 1(1)       | 101       | 1 (x <sup>3</sup> ) |

| 0          | 010       | 1 (x <sup>2</sup> ) |

| 0          | 100       | 0                   |

| 0          | 000       | 1 (1)               |

NOTE: The shift register state is shown after the indicated input bit is clocked.

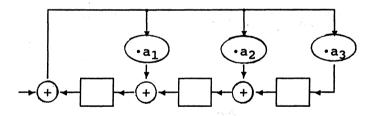

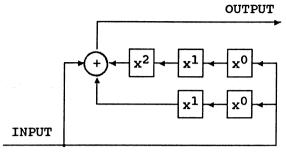

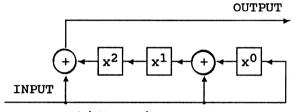

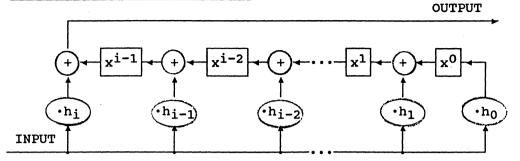

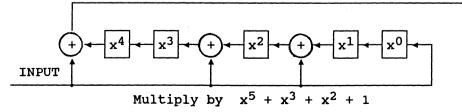

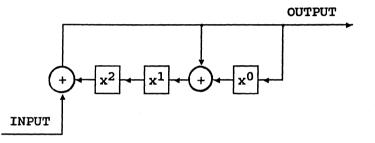

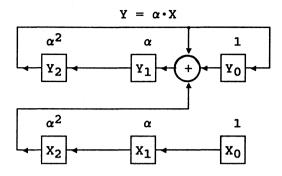

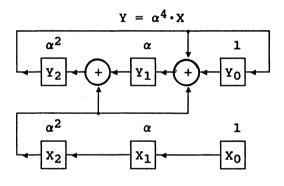

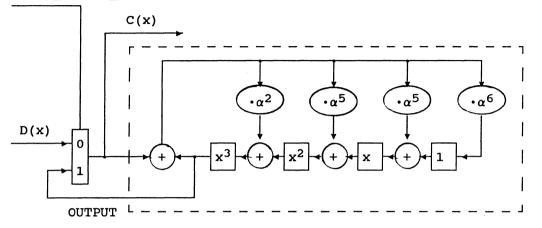

## A GENERAL MULTIPLICATION CIRCUIT

The circuit shown above multiplies any input polynomial D(x) by a fixed polynomial P(x). The product appears on the output line.

$$P(x) = h_i \cdot x^i + h_{i-1} \cdot x^{i-1} + h_{i-2} \cdot x^{i-2} + \dots + h_1 \cdot x + h_0$$

The number of shifts required is equal to the sum of the degrees of the input polynomial and multiplier polynomial, plus one.

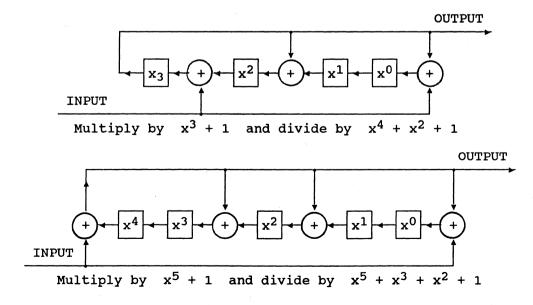

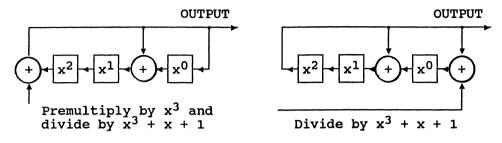

# MULTIPLY CIRCUIT EXAMPLES

OUTPUT

OUTPUT

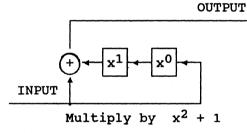

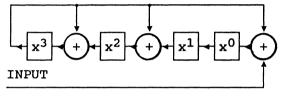

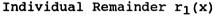

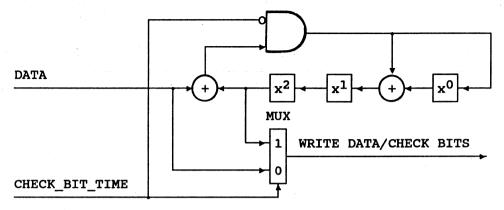

## SHIFT REGISTER IMPLEMENTATION OF DIVISION

Polynomial division can be implemented with an LSR.

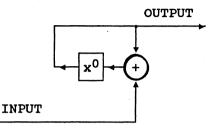

The circuit below will divide any input bit stream by (x + 1). One shift is required for each input bit. The quotient appears on the output line. The final state of the LSR represents the remainder.

Example #1: Assume the input polynomial to be

$x^{6} + x^{5} + x^{4} + x^{3} + x + 1$ .

| Input<br>Bit                                           | Shift Reg<br><u>State</u> | Output<br><u>Bit</u> |

|--------------------------------------------------------|---------------------------|----------------------|

| $\frac{1}{1}$ (x <sup>6</sup> )<br>1 (x <sup>5</sup> ) | 1 (1)                     | _ 0                  |

| $1(x^{2})$                                             | 0                         | 1 (x <sup>5</sup> )  |

| $1(x^4)$                                               | 1 (1)                     | 0                    |

| $1(x^3)$                                               | 0                         | $1(x^3)$             |

| 0                                                      | 0                         | 0`´                  |

| 1 (x)                                                  | 1 (1)                     | 0                    |

| 1 (1)                                                  | 0`´                       | 1 (1)                |

Example #2: Assume the input polynomial to be  $(x^4 + x^3 + 1)$ .

| Input<br>Bit                                           | Shift Reg | Output              |

|--------------------------------------------------------|-----------|---------------------|

| Bit                                                    | State     | Bit                 |

| $\frac{1}{1}$ (x <sup>4</sup> )<br>1 (x <sup>3</sup> ) | 1 (1)     | 0                   |

| 1 (x <sup>3</sup> )                                    | 0         | 1 (x <sup>3</sup> ) |

| 0                                                      | 0         | 0                   |

| 0                                                      | 0         | 0                   |

| 1 (1)                                                  | 1 (1)     | 0                   |

The shift register state is shown after the indicated input bit is clocked.

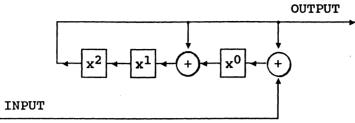

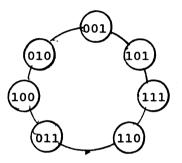

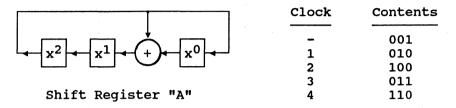

The circuit below will divide any input bit stream by  $(x^3 + x + 1)$ .

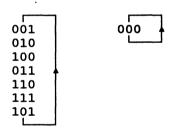

Example #1: Assume the input polynomial to be  $(x^5 + 1)$ .

| Input                                            | Shift Reg                                                                                                             | Output                                      |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| <u>Bit</u>                                       | State                                                                                                                 | <u>Bit</u>                                  |

| 1 (x <sup>5</sup> )<br>0<br>0<br>0<br>0<br>1 (1) | $\begin{array}{c} 001 \ (1) \\ 010 \ (x) \\ 100 \ (x^2) \\ 011 \ (x+1) \\ 110 \ (x^2+x) \\ 110 \ (x^2+x) \end{array}$ | 0<br>0<br>1 (x <sup>2</sup> )<br>0<br>1 (1) |

Example #2: Assume the input polynomial to be  $x^6$ .

| Input                                                  | Shift Reg                                                                                                                                | Output                                               |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| <u>Bit_</u>                                            | State                                                                                                                                    | <u>Bit</u>                                           |

| 1 (x <sup>6</sup> )<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | $\begin{array}{c} 001 \ (1) \\ 010 \ (x) \\ 100 \ (x^2) \\ 011 \ (x+1) \\ 110 \ (x^2+x) \\ 111 \ (x^2+x+1) \\ 101 \ (x^2+1) \end{array}$ | 0<br>0<br>1 (x <sup>3</sup> )<br>0<br>1 (x)<br>1 (1) |

NOTE: The shift register state is shown after the indicated input bit is clocked.

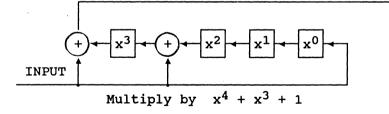

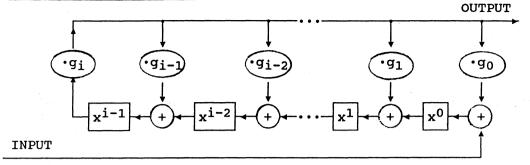

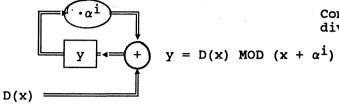

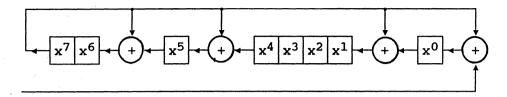

## A GENERAL DIVISION CIRCUIT

The circuit above divides any input polynomial D(x) by a fixed polynomial P(x). The quotient appears on the output line. The remainder is the final shift register state.

$$P(x) = g_i x^i + g_{i-1} x^{i-1} + \dots + g_1 x + g_0$$

The number of shifts required is equal to the degree of the input polynomial plus one.

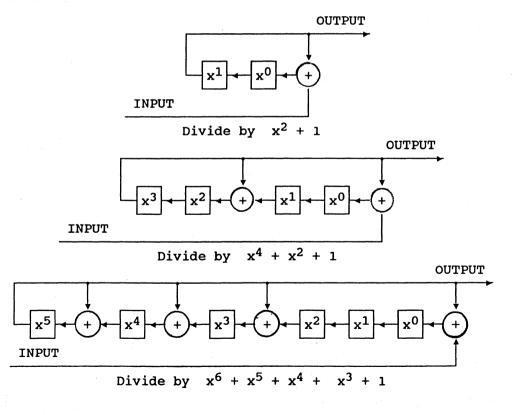

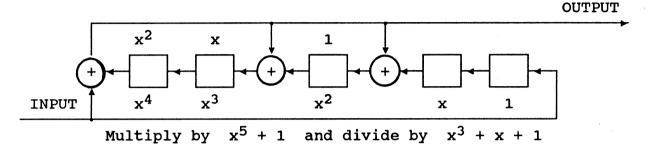

## **DIVIDE CIRCUIT EXAMPLES**

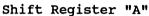

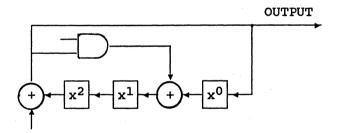

# <u>SHIFT REGISTER IMPLEMENTATION OF SIMULTANEOUS</u> MULTIPLICATION AND DIVISION

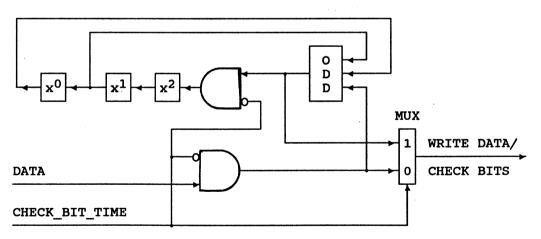

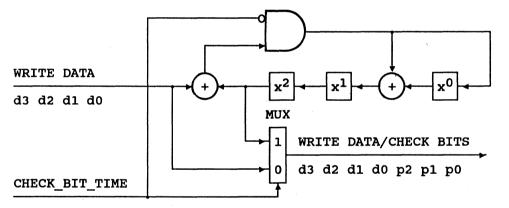

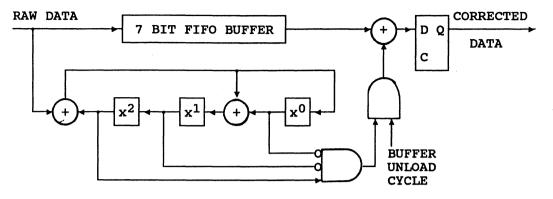

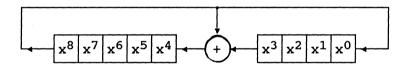

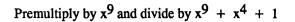

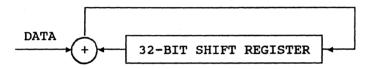

It is possible to use a shift register to accomplish simultaneous multiplication and division. The circuit below will multiply any input bit stream (input polynomial) by  $x^3$  and simultaneously divide by  $(x^3 + x + 1)$ . The number of shifts required is equal to the degree of the input polynomial plus one. The quotient appears on output line. The remainder is the final state of shift register.

Example #1: Assume the input polynomial to be  $(x^5 + 1)$ .

| Input                                            | Shift Reg                                                                                                                 | Output                                                                                |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <u>Bit</u>                                       | State                                                                                                                     | <u>Bit</u>                                                                            |

| 1 (x <sup>5</sup> )<br>0<br>0<br>0<br>0<br>1 (1) | $\begin{array}{c} 011 \ (x+1) \\ 110 \ (x^2+x) \\ 111 \ (x^2+x+1) \\ 101 \ (x^2+1) \\ 001 \ (1) \\ 001 \ (1) \end{array}$ | $ \begin{array}{c} 1 (x^5) \\ 0 \\ 1 (x^3) \\ 1 (x^2) \\ 1 (x) \\ 1 (1) \end{array} $ |

<u>Example #2</u>: Assume the input polynomial to be  $x^6$ .

| Input                                                  | Shift Reg                                                                                                                                | Output                            |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| <u>Bit</u>                                             | State                                                                                                                                    | Bit                               |

| 1 (x <sup>6</sup> )<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | $\begin{array}{c} 011 \ (x+1) \\ 110 \ (x^2+1) \\ 111 \ (x^2+x+1) \\ 101 \ (x^2+1) \\ 001 \ (1) \\ 010 \ (x) \\ 100 \ (x^2) \end{array}$ | 1 (x6) 0 1 (x4) 1 (x3) 1 (x2) 0 0 |

NOTE:

The shift register state is shown after the indicated input bit is clocked.

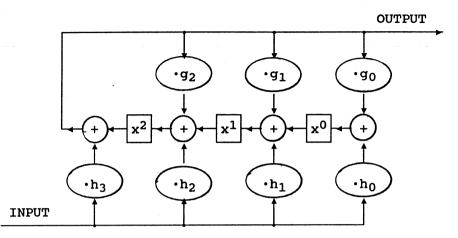

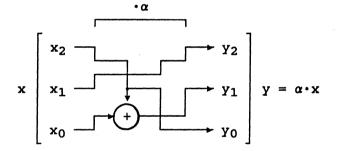

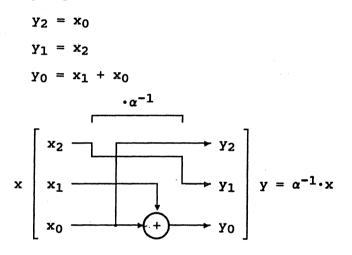

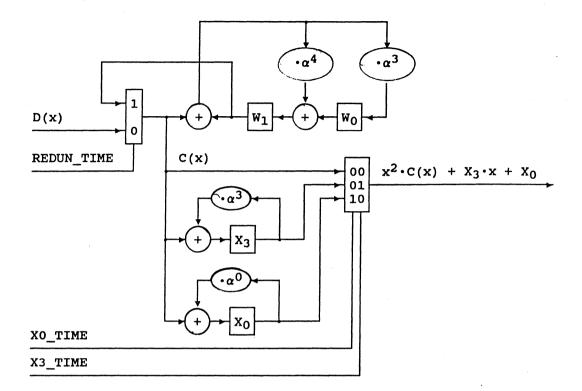

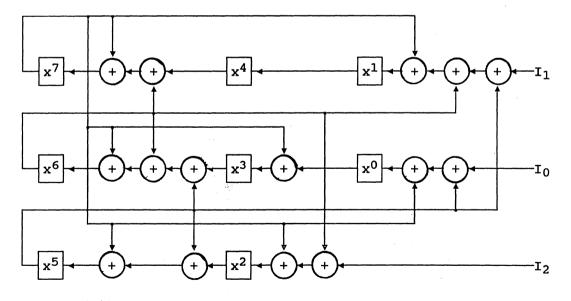

## A CIRCUIT TO MULTIPLY AND DIVIDE SIMULTANEOUSLY

A general circuit to accomplish simultaneous multiplication by a polynomial h(x) of degree three and division by a polynomial g(x) of degree two is shown below. The multipliers are all '•1' (connection) or '•0' (no connection).

To multiply by  $x^3$ , set  $h_3=1$  and set all other multipliers to 0.

To multiply by 1 and divide by  $(x^3 + x + 1)$ , set  $h_0=1$ ,  $g_0=1$  and  $g_1=1$  and set all other multipliers to 0.

To multiply by  $x^3$  and divide by  $(x^3 + x + 1)$ , set  $h_3 = 1$   $g_0 = 1$ , and  $g_1 = 1$  and set all other multipliers to 0. This is a form of simultaneous multiplication and division that is encountered frequently in error-correction circuits.

To multiply by (x + 1) and divide by  $x^3$ , set  $h_0=1$  and  $h_1=1$  and set all other multipliers to 0.

INPUT

The circuit above multiplies any input polynomial by P1(x) and simultaneously divides by P2(x).

$$P1(x) = h_{i}x^{i} + h_{i-1}x^{i-1} + h_{i-2}x^{i-2} + \dots + h_{1}x + h_{0}$$

$$P2(x) = g_{i}x^{i} + g_{i-1}x^{i-1} + g_{i-2}x^{i-2} + \dots + g_{1}x + g_{0}$$

The number of shifts required is equal to the degree of the input polynomial plus one.

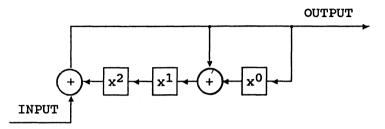

## EXAMPLES OF CIRCUITS TO MULTIPLY AND DIVIDE SIMULTANEOUSLY

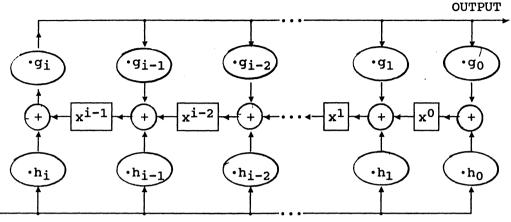

# <u>SIMULTANEOUS MULTIPLICATION AND DIVISION</u> <u>WHEN THE MULTIPLIER POLYNOMIAL HAS A HIGHER DEGREE</u>

The circuit below shows how to construct a shift register to multiply and divide simultaneously when the multiplier polynomial has a higher degree. The number of shifts required is equal to the degree of the input polynomial, plus the degree of the multiplier polynomial, minus the degree of the divider polynomial, plus one. Register states are labeled below for the multiply polynomial and above for the divide polynomial.

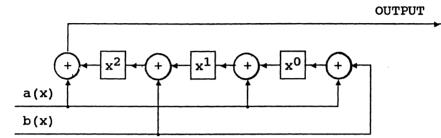

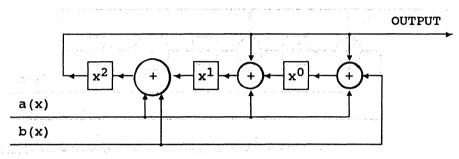

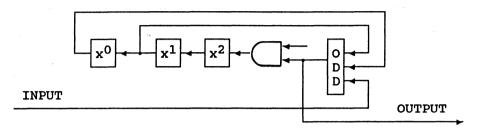

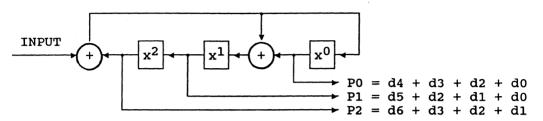

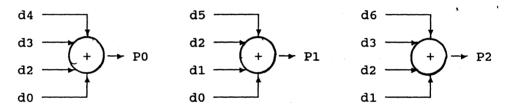

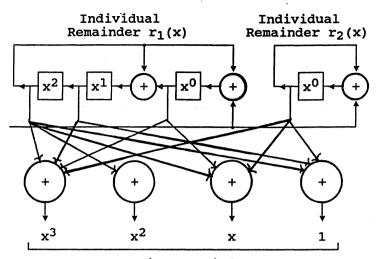

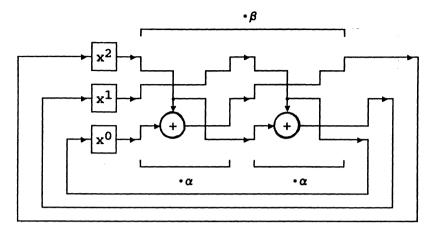

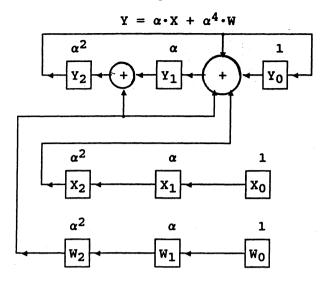

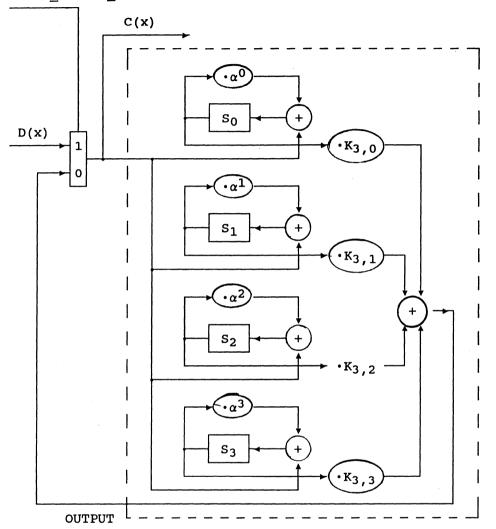

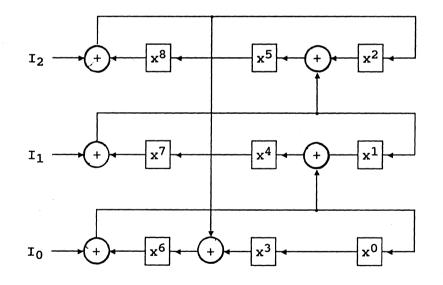

### SHIFT REGISTER IMPLEMENTATION TO COMPUTE A SUM OF PRODUCTS

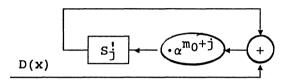

A single shift register can be used to compute the sum of the products of different variable polynomials with different fixed polynomials  $e.g. a(x) \cdot h_1(x) + b(x) \cdot h_2(x)$ .

The circuit below will multiply an input polynomial a(x) by a fixed polynomial  $x^3 + x + 1$  and simultaneously multiply an input polynomial b(x) by the fixed polynomial  $x^2 + 1$  and sum the products. The sum of the products appears on the output line. The number of shifts required is equal to the sum of the degrees of the input polynomial of the highest degree and the fixed polynomial of the highest degree plus one.

Example #1: Assume a(x) to be  $x^3$  and b(x) to be  $(x^5 + x^3 + 1)$ .

| a(x)<br><u>Input</u>                                             | b(x)<br><u>Input</u>                                                                       | Shift Req<br>State                                          | Output<br>Bit                                                       |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------|

| 0<br>0<br>1 (x <sup>3</sup> )<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | $ \begin{array}{c} 1 (x^5) \\ 0 \\ 1 (x^3) \\ 0 \\ 0 \\ 1 (1) \\ 0 \\ 0 \\ 0 \end{array} $ | 101<br>010<br>010<br>100<br>000<br>101<br>010<br>100<br>000 | $0 \\ 1 (x7) \\ 1 (x6) \\ 0 \\ 1 (x4) \\ 0 \\ 1 (x2) \\ 0 \\ 1 (1)$ |

| U                                                                | U                                                                                          | 000                                                         | I (I)                                                               |

TE: The shift register state is shown after the indicated input bit is clocked.

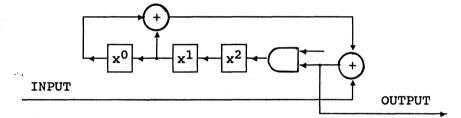

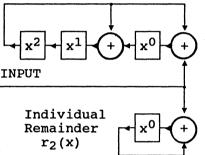

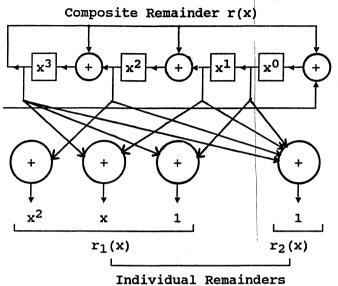

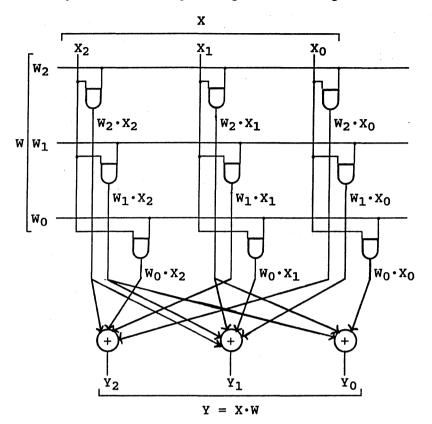

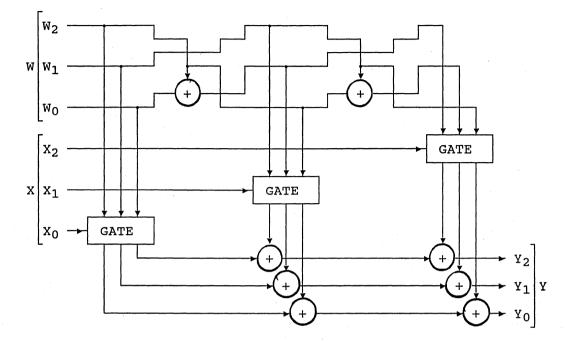

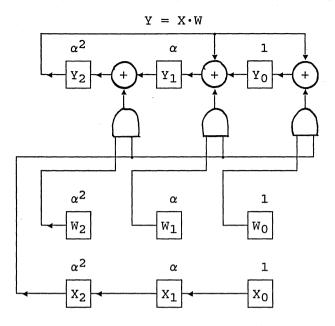

# SHIFT REGISTER IMPLEMENTATION TO COMPUTE A SUM OF PRODUCTS MODULO A DIVISOR

A single shift register can be used to compute the remainder of the sum of products of different variable polynomials with different fixed polynomials when divided by another polynomial  $e.g. [a(x) \cdot h_1(x) + b(x) \cdot h_2(x)]$  MOD g(x).

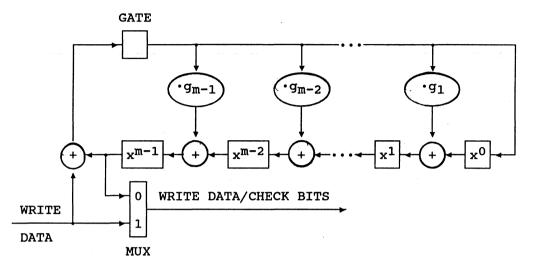

The circuit below will multiply an input polynomial a(x) by a fixed polynomial  $x^2 + x + 1$  and simultaneously multiply an input polynomial b(x) by the fixed polynomial  $x^2 + 1$  and sum the products. The sum of the products is reduced modulo  $x^3 + x + 1$ .