ATET

# **Communication Devices**

1988

Data Book

# **Communication Devices**

January 1988

# 1988

# **Communication Devices**

# Data Book

## A Word About Trademarks . . .

The following product mentioned in this data book is identified with an AT&T trademark:

ESS<sup>™</sup> Switching Equipment

The following products mentioned in this data book are identified with AT&T registered trademarks:

5ESS<sup>®</sup> Switching Equipment, or Switch

WE<sup>®</sup> 32100 Microprocessor, CPU

WE<sup>®</sup> DSP16 Digital Signal Processor

WE<sup>®</sup> DSP16-DS Digital Signal Processor Development System

WE<sup>®</sup> DSP20 Digital Signal Processor

WE<sup>®</sup> DSP32 Digital Signal Processor

WE<sup>®</sup> DSP32-DS Digital Signal Processor Development System, or DSP Development System

WE<sup>®</sup> DSP32-SL Support Software Library

SLC<sup>®</sup> Carrier System, or Carrier

SLC<sup>®</sup> 96 Series 5 Carrier System, or Carrier System

ODL<sup>®</sup> 50 Lightwave Data Link

UNIX<sup>®</sup> Operating System, or System

MS-DOS® is a registered trademark of the Microsoft Corporation.

## Data Sheet Status Markings . . .

Data sheets without a status marking are final and are issued when tool made samples are approved or when the product is delivered for usage, whichever occurs first. The other data sheet status markings used throughout this catalog are defined as:

Advance – Issued at the exploratory stage of development when the principal characteristics are available. Some functional characteristics are subject to change.

**Preliminary** – Issued after development for manufacture has been started. Some electrical and timing parameters are subject to change.

# **1988 Communication Devices Data Book**

## Contents

| AI | phanumeric Index                     | 1-1<br>1-1<br>1-1 |

|----|--------------------------------------|-------------------|

| 1. | General                              |                   |

|    | Introduction                         |                   |

|    | Quality and Reliability              | 1-1               |

|    | Handling and Mounting                | 1-1               |

|    | Handling Hybrid ICs                  | 1-2               |

| 2. | Network                              |                   |

|    | 41LF Quad Differential Line Receiver | 2-1               |

|    | 41LG Quad Differential Line Driver   |                   |

| 4 ILG Quad Differential Line Driver                               | 2-1   |

|-------------------------------------------------------------------|-------|

| 41LK, 41LL, and 41LM Dual Differential Line Driver-Receiver Pairs | 2-13  |

| T7274A Quad Differential Line Driver                              | 2-21  |

| T7275B Quad Differential Line Receiver                            | 2-25  |

| T7500 PCM Codec with Filters                                      | 2-29  |

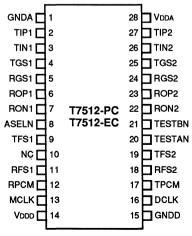

| T7512 Dual PCM Codec with Filters                                 | 2-41  |

| T7513 PCM Codec with Filters                                      | 2-55  |

| T7513A PCM Codec with Filters                                     | 2-73  |

| T7520 High-Precision PCM Codec with Filters                       |       |

| T7521 High-Precision PCM Codec without Filters                    | 2-107 |

| T7522 High-Precision PCM Codec with Filters                       | 2-121 |

| T7523 High-Precision PCM Codec with Filters                       | 2-139 |

| Custom Codecs                                                     | 2-157 |

|                                                                   |       |

#### 3. Data Communications

| T7000A Digital Encryption Processor                             | 3-1   |

|-----------------------------------------------------------------|-------|

| T7001 Random Number Generator                                   |       |

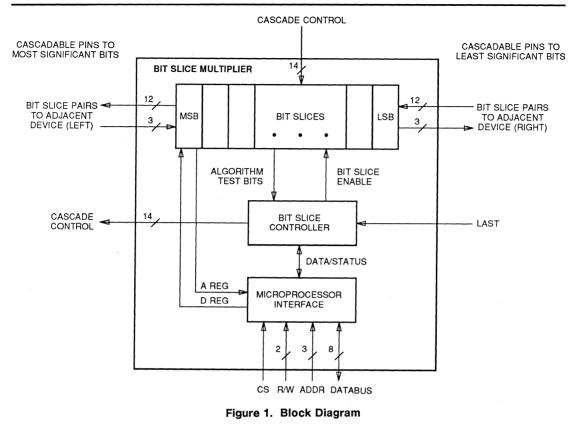

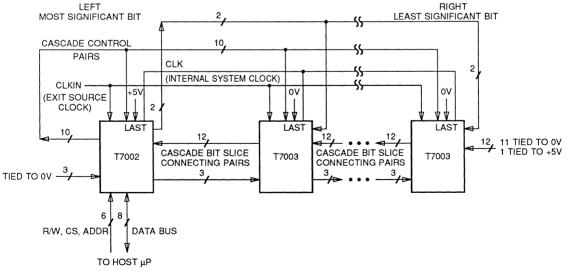

| T7002 Bit Slice Multiplier and T7003 BSM Extender               | 3-43  |

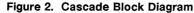

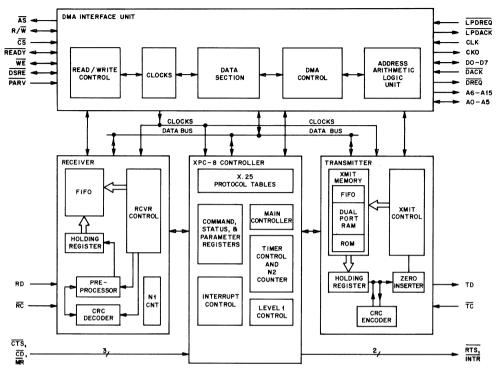

| T7100A X.25 Protocol Controller                                 | 3-45  |

| T7102A X.25/X.75 Protocol Controller                            | 3-71  |

| T7110 Synchronous Protocol Data Formatter with Serial Interface | 3-117 |

| T7111A Synchronous Packet Data Formatter                        | 3-119 |

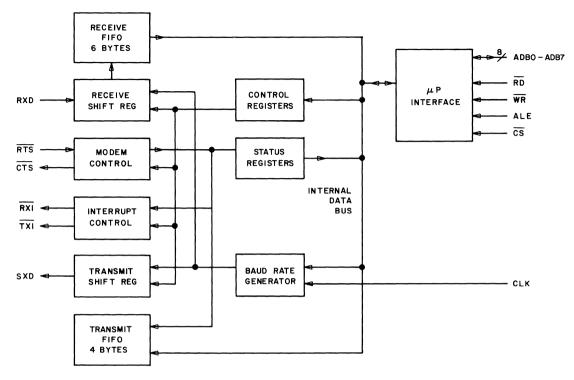

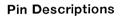

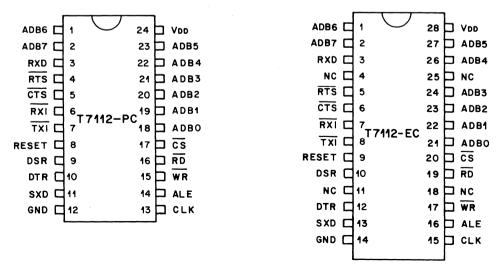

| T7112 Asynchronous Receiver/Transmitter Interface               | 3-143 |

| T7115 Synchronous Protocol Data Formatter                       | 3-165 |

#### 4. ISDN Basic Rate

| T7250A User Network Interface for Terminal Equipment               | 4-1  |

|--------------------------------------------------------------------|------|

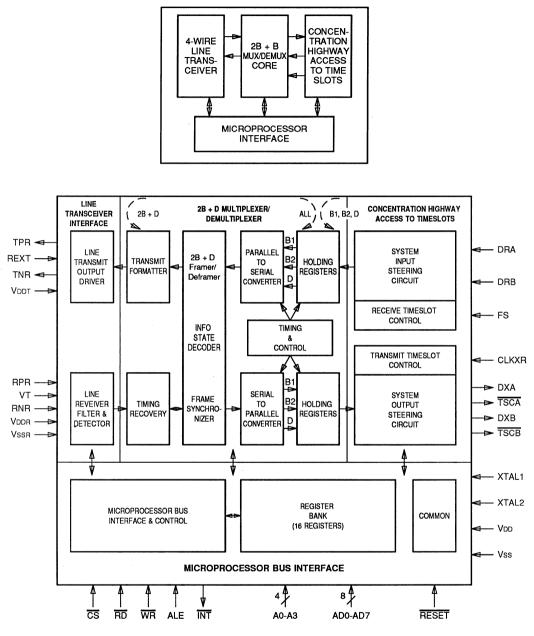

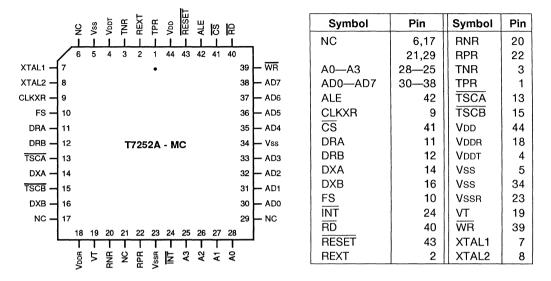

| T7252A User Network Interface Termination for Switches             | 4-3  |

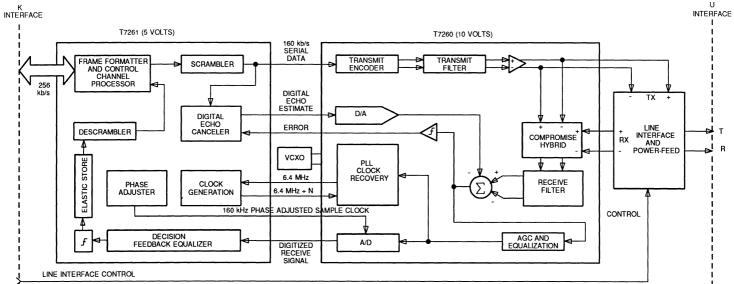

| T7260 and T7261 ISDN U-Interface Basic Access Transceiver Chip Set | 4-45 |

## 5. ISDN Primary Rate/T1

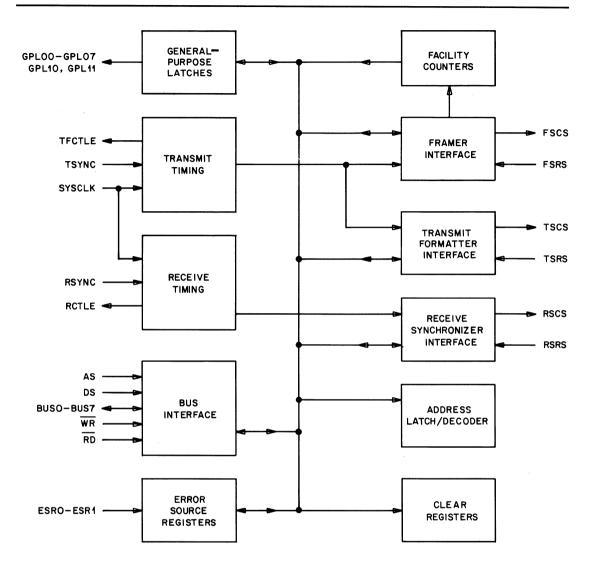

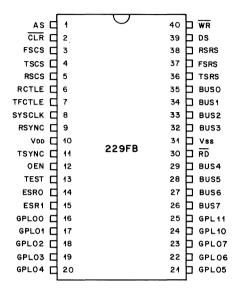

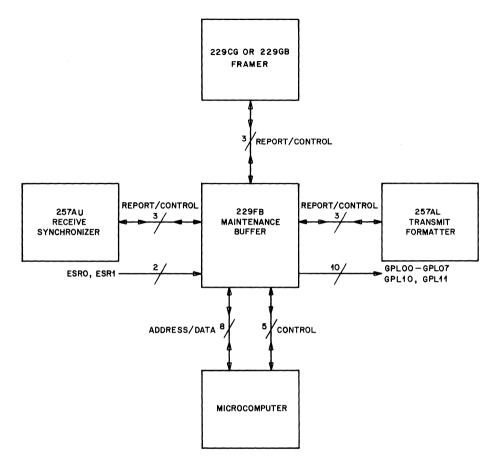

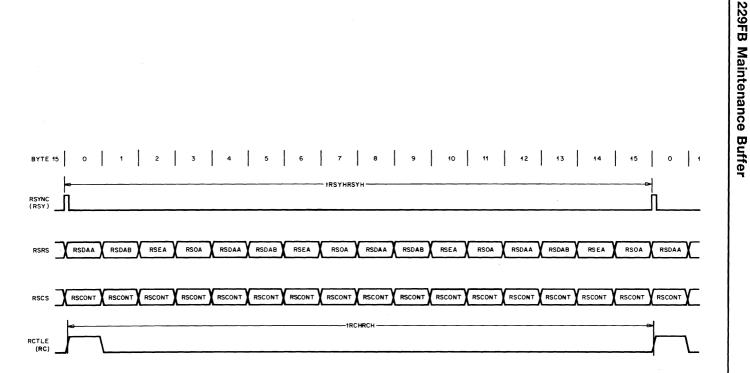

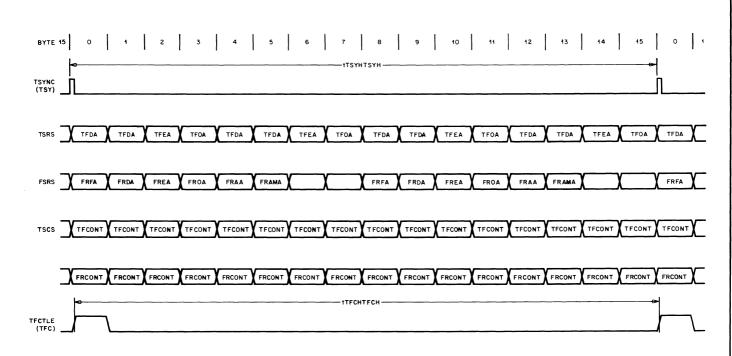

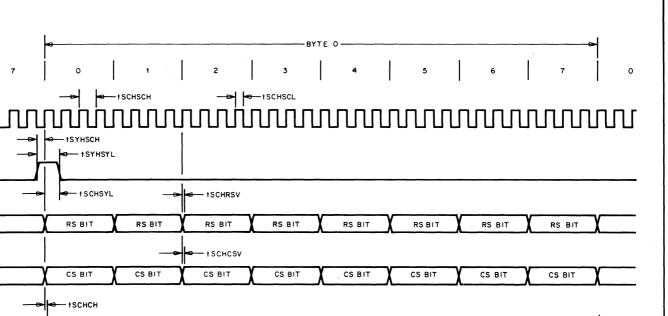

| 229FB Maintenance Buffer            | 5-1   |

|-------------------------------------|-------|

| 229GB Primary Access Framer         | 5-21  |

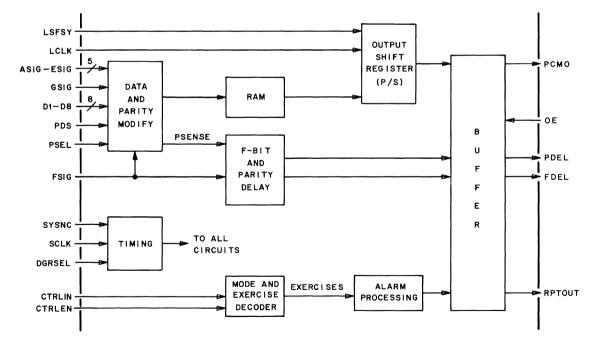

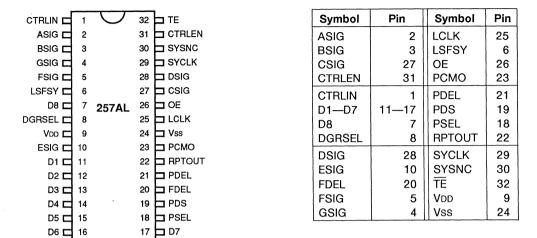

| 257AL Transmit Formatter            | 5-55  |

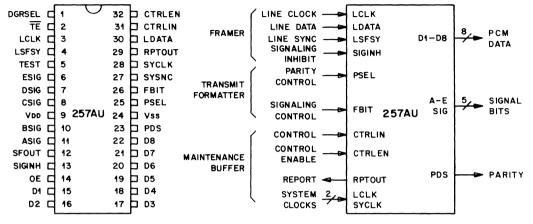

| 257AU Receive Synchronizer          | 5-71  |

| 606HM Transmit Converter            | 5-93  |

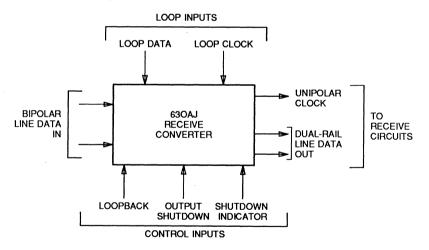

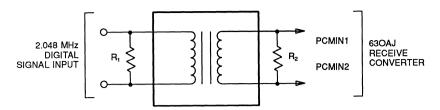

| 630AG Receive Converter             | 5-103 |

| 630AJ Receive Converter             | 5-109 |

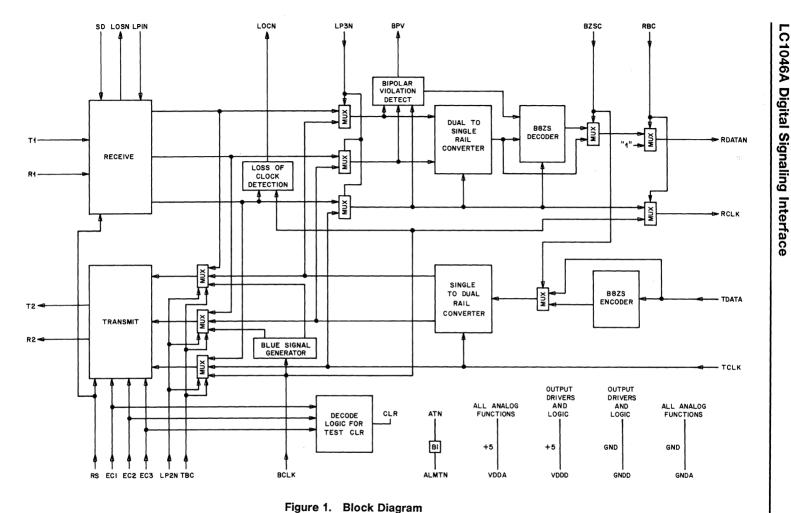

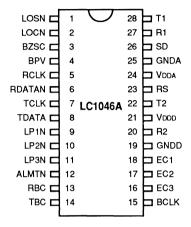

| LC1046A Digital Signaling Interface | 5-115 |

| LC1135B Digital Signaling Interface | 5-129 |

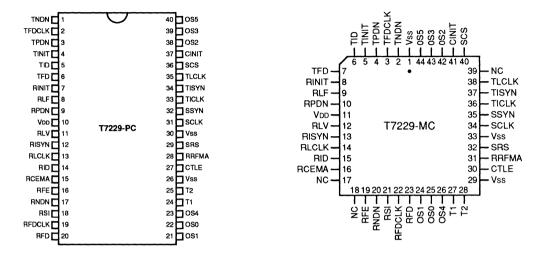

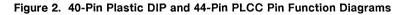

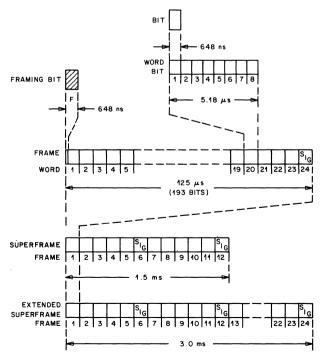

| T7229 Primary Access Framer         |       |

#### 6. Signal Processing

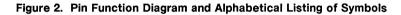

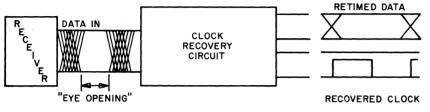

| T7032 Clock Recovery Circuit             | 6-1   |

|------------------------------------------|-------|

| T7033 Clock Recovery Circuit             |       |

| T7034 Clock Recovery Circuit             |       |

| WE DSP16 Digital Signal Processor        | 6-23  |

| DSP16 Support                            |       |

| WE DSP32 Digital Signal Processor        | 6-65  |

| WE DSP32C Digital Signal Processor       |       |

| DSP32 and DSP32C Support                 | 6-121 |

|                                          |       |

| Application and Technical Note Summaries | 7-1   |

| 8. Package Information | ••••• | 8- | 1 |

|------------------------|-------|----|---|

|------------------------|-------|----|---|

# Alphanumeric Index

| Custom Codecs                                                      |       |

|--------------------------------------------------------------------|-------|

| 41LF Quad Differential Line Receiver                               |       |

| 41LG Quad Differential Line Driver                                 |       |

| 41LK, 41LL, and 41LM Dual Differential Line Driver-Receiver Pairs  |       |

| 229FB Maintenance Buffer                                           |       |

| 229GB Primary Access Framer                                        | 5-21  |

| 257AL Transmit Formatter                                           |       |

| 257AU Receive Synchronizer                                         | 5-71  |

| 606HM Transmit Converter                                           | 5-93  |

| 630AG Receive Converter                                            | 5-103 |

| 630AJ Receiver Converter                                           |       |

| LC1046A Digital Signaling Interface                                | 5-115 |

| LC1135B Digital Signaling Interface                                | 5-129 |

| T7000A Digital Encryption Processor                                | 3-1   |

| T7001 Random Number GeneratorN                                     |       |

| T7002 Bit Slice Multiplier and T7003 BSM Extender                  |       |

| T7032 Clock Recovery Circuit                                       | 6-1   |

| T7033 Clock Recovery Circuit                                       | 6-9   |

| T7034 Clock Recovery Circuit                                       | 6-17  |

| T7100A X.25 Protocol Controller                                    |       |

| T7102A X.25/X.75 Protocol Controller                               | 3-71  |

| T7110 Synchronous Protocol Data Formatter with Serial Interface    | 3-117 |

| T7111A Synchronous Packet Data Formatter                           | 3-119 |

| T7112 Asynchronous Receiver/Transmitter Interface                  | 3-143 |

| T7115 Synchronous Protocol Data Formatter                          | 3-165 |

| T7229 Primary Access Framer                                        | 5-143 |

| T7250A User Network Interface for Terminal Equipment               | 4-1   |

| T7252A User Network Interface Termination for Switches             | 4-3   |

| T7260 and T7261 ISDN U-Interface Basic Access Transceiver Chip Set | 4-45  |

| T7274A Quad Differential Line Driver                               | 2-21  |

| T7275B Quad Differential Line Receiver                             | 2-25  |

| T7500 PCM Codec with Filters                                       | 2-29  |

| T7512 Dual PCM Codec with Filters                                  | 2-41  |

| T7513 PCM Codec with Filters                                       | 2-55  |

| T7513A PCM Codec with Filters                                      | 2-73  |

| T7520 High-Precision PCM Codec with Filters                        | 2-91  |

| T7521 High-Precision PCM Codec without Filters                     | 2-107 |

| T7522 High-Precision PCM Codec with Filters                        | 2-121 |

| T7523 High-Precision PCM Codec with Filters                        | 2-139 |

| WE DSP16 Digital Signal Processor                                  | 6-23  |

| DSP16 Support                                                      |       |

| WE DSP32 Digital Signal Processor                                  | 6-65  |

| WE DSP32C Digital Signal Processor                                 | 6-119 |

| DSP32 and DSP32C Support                                           | 6-121 |

| · ·                                                                |       |

.

1. General

# Introduction

For more than a century, AT&T has set the standard for information exchange. AT&T innovation and excellence have created the most extensive, efficient, and reliable communication system in the world. This sophisticated voice and data communication system demands components of superior technology, quality, and reliability.

AT&T manufactures integrated circuits specifically designed to meet the needs of the communications market. The strong research and design capabilities of AT&T Bell Laboratories, combined with the high-volume, high-quality manufacturing capabilities of AT&T Technology Systems, allow AT&T to maintain the leading edge in advanced technology devices.

In this new Information Age, the telephone and the computer are becoming one, and AT&T is building upon this merger with new products and services. New devices have been developed to interface these two complex fields into a highly flexible and reliable network. This catalog contains the technical information on devices used for switching, analog and digital transmission, data transmission and protocol control, T1 interfacing, integrated services digital network (ISDN) interfacing, and signal processing.

# **Quality and Reliability**

AT&T standards and stringent processing controls, along with the design and construction techniques developed at AT&T Bell Laboratories, ensure the excellent quality and reliability of AT&T devices. Laboratory tests and field failure data confirm that high-quality, reliable AT&T products are produced at the component, circuit pack/board, and system levels. Devices are tested by comparing the actual electrical, mechanical, and visual properties of the device to user specifications and manufacturing requirements. Quality is determined at a single point in time; reliability is ascertained over a longer period of time.

The engineering quality control (QC) and final inspection (FI) organizations located at each integrated circuit (IC) manufacturing plant perform the actual inspection and testing of devices. After the products have been inspected, the resident quality assurance (QA) organizations audit the results of the tests to determine acceptability. Quality is usually stated in terms of the number of defects contained in an IC population.

Various mechanical tests are performed to ensure the integrity of internal lead bonds and the strength of exterior leads. Packages are visually inspected during assembly to check for such reliability risk defects as poor alignment of bonds or damaged wires. Assembly shop tests are repeated by QA and FI on a sample of devices prior to shipment. Tests performed include worst-case conditions, speed, leakage, power supply current, etc. The tests are usually performed at room temperature and/or elevated temperature.

Operational life testing (OTL), based on simulated worst-case field conditions, is used to test reliability. Mechanical and electrical stress conditions beyond normal specifications are applied to accelerate latent manufacturing defects. Since some mechanical defects are only minimally affected by accelerated stress conditions, mechanical problems are effectively screened by thermal cycling and hot testing.

# Handling and Mounting

AT&T products have a long life expectancy and a correspondingly low failure rate when handling and operating specifications are followed by the user. Operating specifications include product mounting, use, operating limits, power requirements, environmental conditions, and other items specific to the product. Device temperature specifications are usually given as TA (ambient temperature); however, in a few cases, they are given as TC (case temperature).

Precaution against static discharge must always be observed since devices may be damaged or destroyed by electrostatic discharge. This includes grounding all personnel and equipment before contact with static-sensitive devices. Circuit packs/boards must be shipped in and stored in conductive plastic bags. Nonconductive plastic foam or boxes must never be used for device storage.

Integrated circuit devices can be inserted directly into printed circuit boards and mounted in any position. The leads on the opposite side of the board can be bent to facilitate assembly. Devices can be soldered to printed circuit boards or inserted into sockets but are not intended for spring-type socket insertion.

In solder bath assembly, the solder bath fountain temperature should not exceed 300 °C for a maximum bath time of 10 seconds, unless otherwise stated. For assembly with a soldering iron, the soldering iron tip temperature should not exceed 500 °C, and solder time per lead should be limited to 5 seconds, unless otherwise stated.

Following completion of assembly and soldering operations, all printed wiring assemblies should be cleaned to remove fingerprints, dust, dirt, grease, excessive flux residue, and other foreign matter. Hybrid ICs require a special cleaning process (see below). A brush cleaning process using solvents is an acceptable cleaning method, provided only occasional isolated droplets of solvent come in contact with the devices and the component side of the board. The recommended solvents are such chlorinated hydrocarbons as trichloroethylene, 1,1,1-trichloroethane, and perchloroethylene.

Where aggressive fluxes are employed in assembly of printed wiring, total immersion cleaning with high-velocity spraying of an aqueous solution or such solvents as fluorinated azeotrope is required. Stringent requirements must be placed on the cleanliness of the assemblies to assure removal of ionic residues.

# **Handling Hybrid ICs**

Additional handling procedures are required for Hybrid ICs. Hybrid ICs are encapsulated with a single layer of RTV silicone rubber. This material is solvent-sensitive and special precautions are required in removing solder flux residues from printed circuit boards containing these devices. Unless otherwise designated by specific agreement with the responsible AT&T organizations, cleaning procedures must fall within the conditions that follow.

#### **Cleaning Procedure**

Cleaning processes that avoid contact between solvents and the room temperature vulcanizing (RTV) silicone rubber are preferred. The following cleaning constraints should be observed:

**CAUTION:** It is recommended that these devices be subjected to either of the following procedures only once. Repeated exposure may yield cumulative effects that result in device damage.

- 1. Brush cleaning processes are acceptable, provided that only occasional isolated droplets fall on areas of the devices and the component side of the board.

- 2. RTV areas in which solvent can be trapped should be cleaned by using one of two types of solvents:

- a. Immersion of one minute maximum in Freon TE or Freon TE-35 or equivalents followed by:

- Forced air drying or shaking to remove excess liquid solvent

- Transferring to an air oven in one minute or less

- Baking for 15 minutes at 55 °C

- b. Specially denatured alcohol (SDA), which contains between 5% and 30% methyl alcohol. May be used for a cumulative exposure time of 10 minutes.

# 2. Network

# **41LF Quad Differential Line Receiver**

#### Features

- Pin-equivalent to the general-trade AM26LS32 device, with improved speed and reduced power consumption

- Four line receivers per package

- Meets ESDI Standards

- Complementary inputs for each line receiver

- Maximum power dissipation, 250 mW

- Maximum propagation delay, 7 ns

- 0.20 V input sensitivity

- Common mode rejection range of ±4 V

- Single 5 V supply

- 0 to 85 °C operating temperature

#### Description

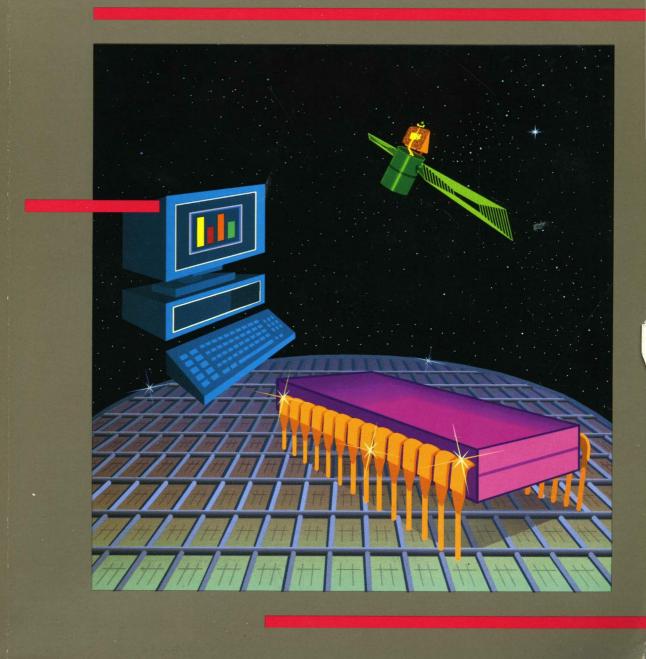

The 41LF Quad Differential Line Receiver integrated circuit is a quad differential input to a TTL output line receiver. This OXIL-technology device contains enable circuitry and four receiver clusters. The average propagation delay is 4 ns and the common mode operating range is  $\pm 4$  V. The 41LF Line Receiver is pin-equivalent to the general-trade AM26LS32 device, but has improved speed and reduced power consumption.

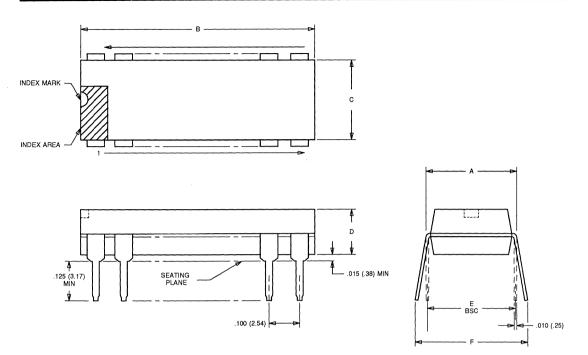

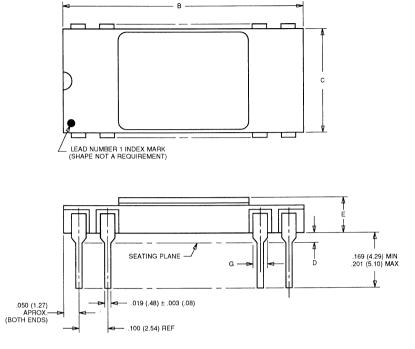

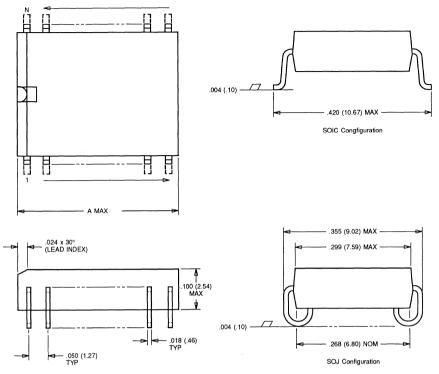

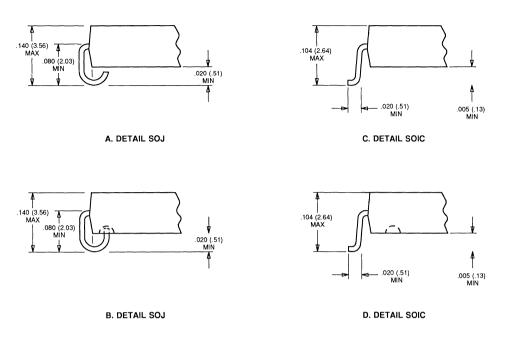

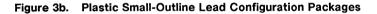

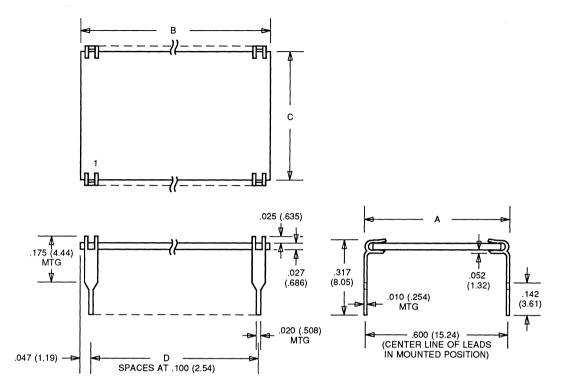

The quad differential line receiver is available in a 16-pin plastic DIP (41LF), SOJ package (1041LG), and SOIC package (1141LG).

The 41LG Line Driver and 41LF Line Receiver application note (AP86-35DBIP) describes two modes of propagation with balanced twisted-pair transmission lines.

# **User Information**

# **Pin Descriptions**

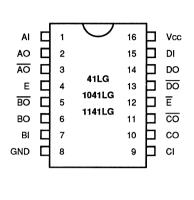

Figure 1. Pin Function and Logic Diagrams

# Characteristics

#### **Electrical Characteristics**

TA = 0 to 85 °C, VCC = 5 V  $\pm$  0.5 V

| Parameter                                       | Sym  | Min | Тур | Мах  | Unit |

|-------------------------------------------------|------|-----|-----|------|------|

| Output voltage, Vcc = 4.5 V:                    |      |     |     |      |      |

| low, lol = 8 mA                                 | VOL  |     |     | 0.5  | V    |

| high, IOH = $-400 \ \mu A$                      | Vон  | 2.5 | —   |      | V    |

| Enable input voltages:                          |      |     |     |      |      |

| low, VCC = $5.5 V$                              | Vi∟* |     |     | 0.7  | V    |

| high, Vcc = 4.5 V                               | VIH* | 2.0 | _   |      | V    |

| clamp, VCC = $4.5$ V; IIN = $-18$ mA            | Vik  |     |     | _1.5 | V    |

| Differential input voltages,** VO = VOL or VOH, |      |     |     |      |      |

| -0.80  V < Vih < 7.2  V, -1.2  V < Vil < 6.8  V | VTH* | 0.2 | 0.1 |      | V    |

\* These input levels and difference voltage provide zero noise immunity and should be tested only in a static, noise-free environment.

\*\* Unused differential input pairs should be biased alternately to Vcc and GND. No protection resistor is required.

| Parameter                           | Sym   | Min   | Тур | Мах  | Unit |

|-------------------------------------|-------|-------|-----|------|------|

| Output currents, VCC = 5.5 V:       |       |       |     |      |      |

| off-state (high-Z), Vo = 0.4 V      | lozl  |       |     | 20   | μA   |

| off-state (high-Z), Vo = 2.4 V      | lozн  |       |     | 20   | μA   |

| short-circuit                       | Isc   | -25.0 |     | -100 | mA   |

| Enable input currents, VCC = 5.5 V: |       |       |     |      |      |

| Iow, $VIN = 0.4 V$                  | lı∟   | _     |     | -360 | μΑ   |

| high, VIN = 2.7 V                   | Ιн    | _     |     | 20   | μA   |

| reverse, $VIN = 5.5 V$              | Ін    |       |     | 100  | μA   |

| Differential input currents:        |       |       |     |      |      |

| Iow, $VIN = -1.2 V$                 | ] li∟ |       | -   | -1.0 | mA   |

| high, VIN = 7.2 V                   | ΪН    |       | - 1 | 1.0  | mA   |

| Power supply current, Vcc = 5.5 V   |       |       |     |      |      |

| all outputs disabled                | Icc   |       | 35  | 45   | mA   |

#### **Maximum Ratings**

| DC power supply voltage (Vcc)                        | 1 |

|------------------------------------------------------|---|

| Ambient operating temperature (TA) range 0 to 125 °C | ; |

| Storage temperature (Tstg) range                     |   |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

External leads can be bonded or soldered safely at temperatures up to 300 °C.

Timing Characteristics (See Figures 4 and 5)

TA = 25 °C, VCC = 5 V

| Symbol         | Description                       | Тур | Max | Unit |

|----------------|-----------------------------------|-----|-----|------|

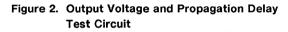

|                | Propagation delay (see Figure 2): |     |     |      |

| <b>t</b> PLH   | input high (low) to output high   | 3.5 | 7.0 | ns   |

| <b>t</b> PHL   | input low (high) to output low    | 4.5 | 7.0 | ns   |

| Disable time:* |                                   |     |     |      |

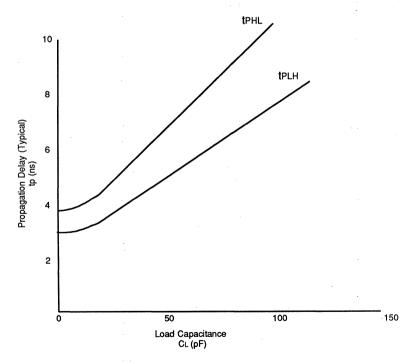

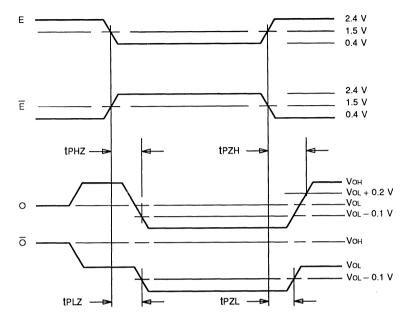

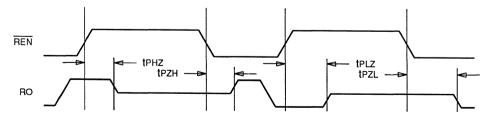

| <b>t</b> PHZ   | high to high impedance            | 30  |     | ns   |

| <b>t</b> PLZ   | low to high impedance             | 30  |     | ns   |

|                | Enable time:*                     |     |     |      |

| <b>t</b> PZH   | high impedance to high            | 35  |     | ns   |

| <b>t</b> PZL   | high impedance to low             | 35  |     | ns   |

\* The device is disabled when E = 0 and  $\overline{E}$  = 1; all other combinations of E and  $\overline{E}$  enable the device.

# **41LF Quad Differential Line Receiver**

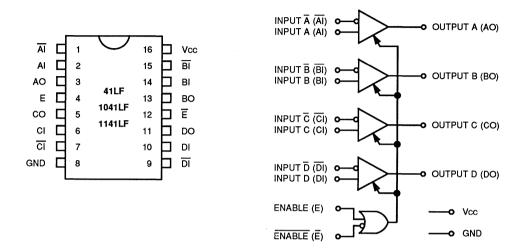

Note: All 458E or 1N4148 diodes. \* Includes probe and jig capacitances.

Figure 3. Propagation Delay Versus Load Capacitance

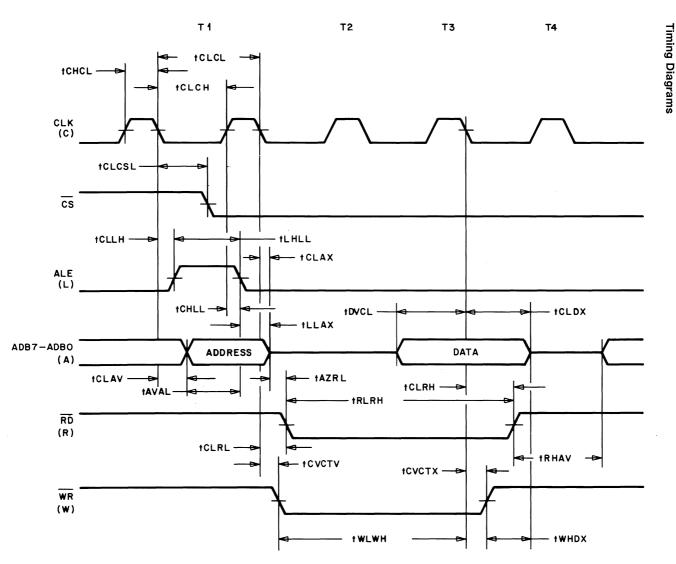

**Timing Diagrams**

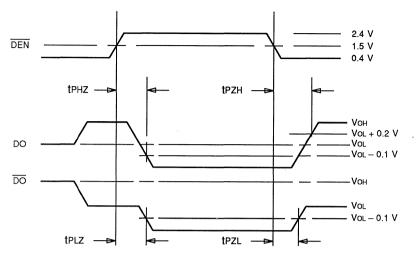

Figure 4. Enable and Disable Timing

2-6

# **41LG Quad Differential Line Driver**

#### Features

- Pin-equivalent to the general-trade AM26LS31 device, with improved speed, reduced power consumption, and reduced EMI

- Four line drivers per package

- Meets ESDI standards

- Complementary outputs from each line driver

- No line loading when VCC = 0 V

- Maximum power dissipation, 300 mW

#### Description

- Maximum propagation delay, 6 ns

- Drive capability, 40 mA

- High output drive for 50-Ω lines

- Minimum output short-circuit current, 100 mA

- Output skew 0.2 ns, typical

- Single 5 V supply

- = 0 to 85 °C operating temperature

The 41LG Quad Differential Line Driver integrated circuit transmits digital data over balanced transmission lines. It translates TTL input logic levels to ECL output levels that directly drive the line. This OXIL-technology device contains enable circuitry and four drivers. It is pin-equivalent to the general-trade AM26LS31 device; however, it has reduced power consumption and generates lower levels of electromagnetic interference (EMI). The 41LG line driver is compatible with many line receivers, including the AT&T 41LF and 858B HIC (built-in terminations) devices, and the general-trade AM26LS32 device.

The quad differential line driver is available in a 16-pin plastic DIP (41LG), SOJ package (1041LG), and SOIC package (1141LG).

The 41LG Line Driver and 41LF Line Receiver application note (AP86-35DBIP) describes two modes of propagation with balanced twisted-pair transmission lines.

# **User Information**

## **Pin Descriptions**

# Characteristics

#### **Electrical Characteristics**

TA = 0 to 85 °C, VCC = 5 V  $\pm$  0.5 V

| Parameter                                           | Sym              | Min  | Тур      | Max                            | Unit |

|-----------------------------------------------------|------------------|------|----------|--------------------------------|------|

| Output voltages, Vcc = 4.5 V (see Figures 2 and 3): |                  |      |          |                                |      |

| $low, lol = -8.0 mA^*$                              | Vol              |      | _        | Voн – <b>0.80<sup>**</sup></b> | v    |

| high, Iон = -40.0 mA*                               | Vон              | 3.0  | —        |                                | v    |

| high-Z                                              | Voz              |      | 2.0      | Vol – 0.05                     | V    |

| high-Z, Vcc = 4.75 V                                | Voz              |      | 2.0      | Vol – 0.20                     | V    |

| Input voltages:                                     |                  |      |          |                                |      |

| low, $VCC = 5.5 V$                                  | Vi∟ <sup>†</sup> | —    | —        | 0.8                            | v    |

| high, $VCC = 4.5 V$                                 | Viн <sup>†</sup> | 2.0  |          |                                | v    |

| clamp, Vcc = 4.5 V, IIN = -18.0 mA                  | νικ              | —    |          | -1.5                           | V    |

| Output current                                      |                  |      |          |                                |      |

| short-circuit                                       | Isc              | -100 | -200     | -300                           | mA   |

| Input currents, Vcc = 5.5 V:                        |                  |      |          |                                |      |

| low, $VIN = 0.4 V$                                  | liL –            |      |          | _400                           | μΑ   |

| high, VIN = 2.7 V                                   | lін              |      | <u> </u> | 20                             | μΑ   |

| reverse, VIN = 5.5 V                                | Ін               |      |          | 100                            | μA   |

| Power supply current, Vcc = 5.5 V:                  |                  |      |          |                                |      |

| all outputs disabled                                | Icc              | _    | 60       | 85                             | mA   |

| all outputs enabled                                 | ICC              |      | 40       | 65                             | mA   |

\* Typical value of output current when the load shown in Figure 4 is used.

\*\* VoL must be a minimum of 0.8 V less than its complementary output.

<sup>+</sup> These input levels provide zero noise immunity and should be tested only in a static, noise-free environment.

#### **Maximum Ratings**

| Power supply voltage (VCC)               | 7.0 V          |

|------------------------------------------|----------------|

| Ambient operating temperature (TA) range | 0 to 125 °C    |

| Storage temperature (Tstg) range         | –40 to +125 °C |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

External leads can be bonded or soldered safely at temperatures up to 300 °C.

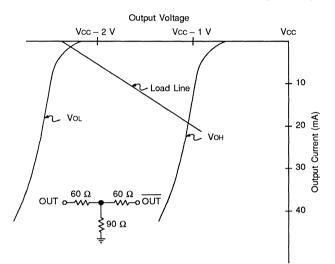

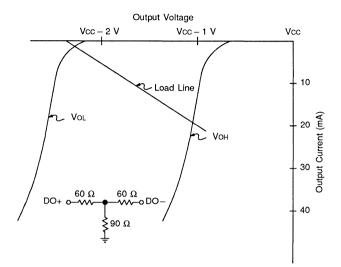

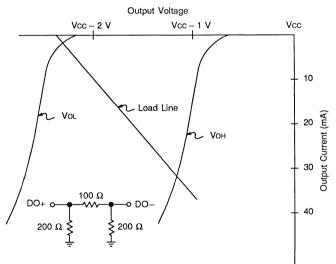

Figure 2. Driver Output Current — Voltage Characteristics (Y-Load)

Characteristics ( $\pi$ -Load)

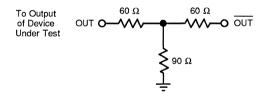

Figure 4. Parametric Test Circuit

#### Timing Characteristics (See Figures 6 and 7)

TA = 25 °C Vcc = 5 V, timing management test circuit (shown in Figure 5) connected to output.

| Symbol       | Description                     | Тур | Мах | Unit |

|--------------|---------------------------------|-----|-----|------|

|              | Propagation delay:              |     |     |      |

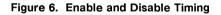

| <b>t</b> PLH | input high (low) to output high | 3.0 | 6.0 | ns   |

| <b>t</b> PHL | input low (high) to output low  | 3.0 | 6.0 | ns   |

|              | Disable time:*                  |     |     |      |

| <b>t</b> PHZ | high to high impedance          | 30  | 50  | ns   |

| tPLZ         | low to high impedance           | 30  | 50  | ns   |

|              | Enable time:*                   |     |     |      |

| tpzh         | high impedance to high          | 35  | 40  | ns   |

| tPZL         | high impedance to low           | 35  | 40  | ns   |

| tskew        | Output skew,  tPLH – tPHL       | 0.2 | 0.5 | ns   |

| ∆tskew       | Difference between drivers      | 0.3 |     | ns   |

\* The device is disabled when E = 0 and  $\overline{E}$  = 1; all other combinations of E and  $\overline{E}$  enable the device.

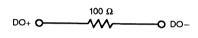

Figure 5. Timing Management Test Circuit

#### **Timing Diagrams**

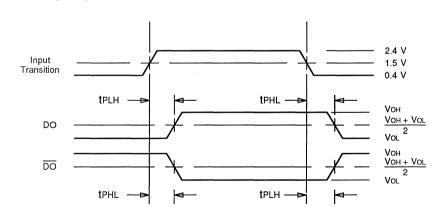

Figure 7. Propagation Delay

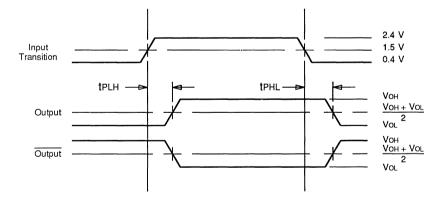

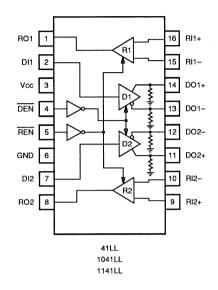

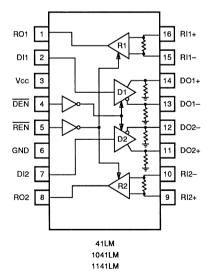

# 41LK, 41LL, and 41LM Dual Differential Line Driver-Receiver Pairs

#### **Features**

#### Device

- Single 5 V supply

- 0 to 85 °C operating temperature

- Meets ESDI standards

#### Driver

- Two line drivers per package

- Complementary outputs from each line driver

- Maximum propagation delay, 6.0 ns

#### Receiver

- Two line receivers per package

- Complementary inputs for each line receiver

- Maximum propagation delay, 7.0 ns

- No line loading when VCC = 0 V

- Minimum output short-circuit current, 100 mA

- Output skew 0.2 ns, typical

- 0.20 V input sensitivity

- Common mode rejection of ±4 V

- TTL- and ECL-compatible inputs

# Description

The 41LK, 41LL, and 41LM devices are dual differential line driver-receiver pairs that are compatible with the 41LG Quad Line Driver and 41LF Quad Line Receiver devices. These dual pair devices consist of two line receivers with differential ECL-to-TTL converters, two line drivers with TTL-to-differential ECL converters, and individual 3-state enabling circuitry for the driver and receiver pairs. This allows serial data and a control clock to be transmitted and received on a single integrated circuit. The typical propagation delays for the driver and receiver of these OXIL-technology devices are 3.0 ns and 4.0 ns, respectively.

The 41LK device is intended for use where the minimization of electromagnetic interference is required, and it has characteristics similar to those of the 41LG and 41LF devices. The 41LL device has internal 200- $\Omega$  discharge resistors on each driver output and is equivalent to the NSC DS8923A. The 41LM device has internal resistor terminations for both the driver (200  $\Omega$ ) and receiver (100  $\Omega$ ), eliminating the need for external resistors, and it is intended for use with 100- $\Omega$  impedance (Z) twisted-pair or flat cable.

The dual differential line driver-receiver pairs are available in a 16-pin plastic DIP (41LK, 41LL, and 41LM), SOJ package (1041LK, 1041LL, and 1041LM), or SOIC (1141LK, 1141LL, 1141LM) package.

# **User Information**

## **Pin Descriptions**

| DEN | REN | DO1    | DO2    | RO1    | RO2    |

|-----|-----|--------|--------|--------|--------|

| 0   | 0   | Active | Active | Active | Active |

| 1   | 0   | High-Z | High-Z | Active | Active |

| 0   | 1   | Active | Active | High-Z | High-Z |

| 1   | 1   | High-Z | High-Z | High-Z | High-Z |

# **Characteristics**

#### **Electrical Characteristics**

TA = 0 to 85 °C, VCC = 5 V  $\pm$  0.5 V

#### Device

| Parameter                          | Sym | Min | Тур | Мах | Unit |

|------------------------------------|-----|-----|-----|-----|------|

| Power supply current, VCC = 5.5 V: |     |     |     |     |      |

| 41LK                               |     |     |     |     |      |

| all outputs disabled               | Icc | -   | 40  | 70  | mA   |

| all outputs enabled                | Icc | -   | 25  | 45  | mA   |

| 41LL and 41LM                      |     | ļ   |     |     |      |

| all outputs disabled               | Icc | -   | 60  | 90  | mA   |

| all outputs enabled                | Icc |     | 90  | 135 | mA   |

#### Driver

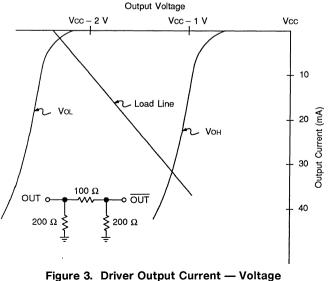

Output voltage test circuit connected to output (see Figures 2 and 3).

| Parameter                                 | Sym   | Min  | Тур  | Max        | Unit |

|-------------------------------------------|-------|------|------|------------|------|

| Output voltages, VCC = 4.5 V:             |       |      |      |            |      |

| low                                       | Vol   | _    | —    | Vон – 0.8* | V    |

| high                                      | Vон   | 3.0  |      | —          | v    |

| high-Z, Іон = _1.0 mA                     | Voz   |      | 2.0  | Vol – .05  | v    |

| high-Z, Vcc = 4.75 V                      | Voz   |      | 2.0  | Vol – 0.2  | V    |

| Input voltages:                           |       |      |      |            |      |

| low, VCC = $5.5 V$                        | VIL** |      |      | 0.7        | v    |

| high, Vcc = 4.5 V                         | VIH** | 2.0  | _    |            | v    |

| clamp, VCC = $4.5$ V, IIN = $-18.0$ mA    | Vik   |      |      | -1.5       | v    |

| Output current                            |       |      |      |            |      |

| short-circuit                             | Isc   | _100 | -200 | _300       | mA   |

| Input currents, VCC = 5.5 V:              |       |      |      |            |      |

| Iow, $VIN = 0.4 V$                        | liL.  | _    | _    | -400       | μA   |

| high, VIN = 2.7 V                         | Іін   |      |      | 20         | μA   |

| reverse, $VIN = 5.5 V$                    | Ін    | —    |      | 100        | μA   |

| Differential output resistor (41LL, 41LM) | Ro    |      | 200  |            | Ω    |

\* VoL must be a minimum of 0.8 V less than its complementary output.

\*\* The input levels and difference voltage provide zero noise immunity and should be tested only in a static, noise-free environment.

#### Receiver

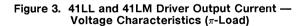

Output voltage test circuit connected to output (see Figure 4).

| Parameter                                       | Sym  | Min   | Тур | Мах  | Unit |

|-------------------------------------------------|------|-------|-----|------|------|

| Output voltage, Vcc = 4.5 V:                    |      |       |     |      |      |

| low, IOL = 8 mA                                 | VOL  | _     |     | 0.5  | v    |

| high, Iон = _400 µА                             | Vон  | 2.5   |     |      | V    |

| Enable input voltages:                          |      |       |     |      |      |

| low, $VCC = 5.5 V$                              | VIL* | -     |     | 0.7  | v    |

| high, Vcc = 4.5 V                               | VIH* | 2.0   |     |      | V    |

| Differential input voltages,** VO = VOL or VOH  |      |       |     |      |      |

| -0.80  V < Vih < 7.2  V, -1.2  V < Vil < 6.8  V | VTH* | 0.20  | 0.1 |      | v    |

| Output currents, Vcc = 5.5 V:                   |      |       |     |      |      |

| off-state (high-Z), Vo = 0.4 V                  | IOZL | _     | —   | -20  | μΑ   |

| off-state (high-Z), Vo = 2.4 V                  | lozн | _     |     | 20   | μA   |

| short-circuit                                   | Isc  | -25.0 |     | _100 | mA   |

| Enable input currents, VCC = 5.5 V:             |      |       |     |      |      |

| Iow, $VIN = 0.4 V$                              | liL. |       | —   | -400 | μA   |

| high, $VIN = 2.7 V$                             | lін  | —     |     | 20   | μA   |

| reverse, VIN = 5.5 V                            | Ін   | —     |     | 100  | μA   |

| Differential input currents (41LK, 41LL):       |      |       |     |      |      |

| low, $VIN = -1.2 V$                             | lı.  |       |     | -1.0 | mA   |

| high, VIN = 7.2 V                               | Іін  |       | —   | 1.0  | mA   |

| Differential input impedance (41LM)             |      |       |     |      |      |

| measured between RI+ and RI-                    | RI   |       | 105 | —    | Ω    |

\* The input levels and difference voltage provide zero noise immunity and should be tested only in a static, noise-free environment.

\*\* The input of unused differential input pairs should be biased to Vcc. No protection resistor is required.

#### **Maximum Ratings**

| Power supply voltage (Vcc)               | 7.0 V |

|------------------------------------------|-------|

| Ambient operating temperature (TA) range |       |

| Storage temperature (Tstg) range         |       |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

External leads can be bonded or soldered safely at temperatures up to 300 °C.

Figure 2. 41LK Driver Output Current — Voltage Characteristics (Y-Load)

Note: 200-Ω resistors are internal to device.

Note: All 458E or 1N4148 diodes. \* Includes probe and jig capacitances.

#### **Timing Characteristics**

Driver (See Figures 7 and 8)

| TA = 25 °C, VCC = 5 V, timing management test circuit connected to outp | ut (see Figures 5 and 6). |

|-------------------------------------------------------------------------|---------------------------|

|-------------------------------------------------------------------------|---------------------------|

| Symbol       | Description                | Тур | Мах | Unit |

|--------------|----------------------------|-----|-----|------|

|              | Propagation delay:         |     |     |      |

| <b>t</b> PLH | input high to output high  | 3.0 | 6.0 | ns   |

| <b>t</b> PHL | input low to output low    | 3.0 | 6.0 | ns   |

|              | Disable time:              |     |     |      |

| tPHZ         | high to high impedance     | 20  | —   | ns   |

| tPLZ         | low to high impedance      | 20  |     | ns   |

|              | Enable time:               |     |     |      |

| tрzн         | high impedance to high     | 20  |     | ns   |

| tPZL         | high impedance to low      | 20  |     | ns   |

| tskew        | Output skew,  tPLH - tPHL  | 0.2 | 0.5 | ns   |

| ∆tskew       | Difference between drivers | 0.3 |     | ns   |

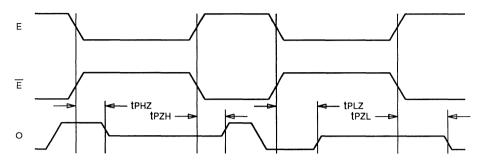

Figure 4. Output Voltage and Propagation Delay Test Circuit

#### Receiver (See Figures 9 and 10)

TA = 25 °C, VCC = 5 V, propagation delay test circuit connected to output (see Figure 4).

| Symbol       | Description                     | Тур | Мах | Unit |

|--------------|---------------------------------|-----|-----|------|

| 1            | Propagation delay:              |     |     |      |

| <b>t</b> PLH | input high (low) to output high | 3.5 | 7.0 | ns   |

| <b>t</b> PHL | input low (high) to output low  | 4.5 | 7.0 | ns   |

|              | Disable time:                   |     |     |      |

| t PHZ        | high to high impedance          | 20  |     | ns   |

| t PLZ        | low to high impedance           | 20  |     | ns   |

|              | Enable time:                    |     |     |      |

| tPZH         | high impedance to high          | 20  |     | ns   |

| tPZL         | high impedance to low           | 20  |     | ns   |

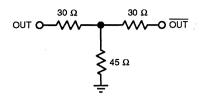

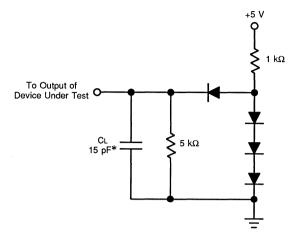

#### Figure 5. 41LK Timing Management Test Circuit

**Timing Diagrams**

Figure 6. 41LL and 41LM Timing Management Test Circuit

Figure 7. Driver Propagation Delay Timing

Network

#### 2-19

Figure 8. Driver Enable and Disable Timing

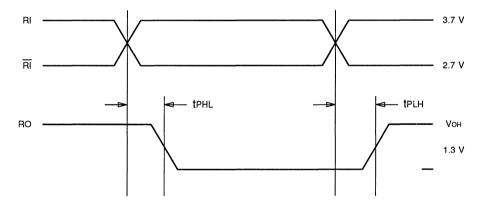

Figure 9. Receiver Propagation Delay Timing

Figure 10. Receiver Enable and Disable Timing

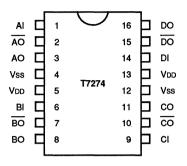

# **T7274A Quad Differential Line Driver**

#### Features

- Four line drivers per package

- Complementary outputs from each line driver

- 24-mA drive capability

- High output drive for 100-Ω, 110-Ω, and 150-Ω lines

- 2.0-ns minimum and 4.75-ns maximum propagation delays

- 0.1-ns output skew, typical

- 140 Mb/s data rate

- 300-mW maximum power dissipation

- Single 5 V supply

- 0 to 85 °C operating temperature

#### Description

The T7274A Quad Differential Line Driver integrated circuit is a single-input-to-balanced-output converter that drives differential transmission lines. The input requires typical CMOS signals, and the output has typical CMOS voltage swings and can drive  $100-\Omega$ ,  $110-\Omega$ , and  $150-\Omega$  twisted pair lines through a resistor attenuation network.

This CMOS device is similar to the general-trade 26LS31 device; however, it has decreased power consumption and generates lower levels of electromagnetic interference (EMI).

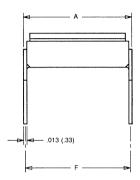

The T7274A line driver is compatible with many line receivers, including the AT&T T7275B and 41LF devices and the general-trade 26LS32 device. The quad differential line driver is available in a 16-pin plastic DIP and small-outline J-lead (SOJ) package.

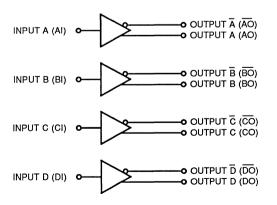

Figure 1. Logic Diagram

# **User Information**

# **Pin Descriptions**

Figure 2. Pin Function Diagram

| Table | 1. | Pin | Descriptions |  |

|-------|----|-----|--------------|--|

|-------|----|-----|--------------|--|

| Symbol | Туре | Name                          |

|--------|------|-------------------------------|

| AI     | I    | A-line driver input           |

| ĀŌ     | 0    | Inverted A-line driver output |

| AO     | 0    | A-line driver output          |

| BI     | 1    | B-line driver input           |

| BO     | 0    | Inverted B-line driver output |

| BO     | 0    | B-line driver output          |

| CI     | 1    | C-line driver input           |

| CO     | 0    | Inverted C-line driver output |

| CO     | 0    | C-line driver output          |

| DI     | l    | D-line driver input           |

| DO     | 0    | Inverted D-line driver output |

| DO     | 0    | D-line driver output          |

| Vss    | _    | Ground pins                   |

| Vdd    | _    | 5 V supply pins               |

# **Characteristics**

## **Electrical Characteristics**

TA = 0 to 85 °C, VDD = 5.0 V  $\pm$  0.25 V

| Parameter                           |     | Min Typ |       | Мах  | Unit |

|-------------------------------------|-----|---------|-------|------|------|

| Output voltages, VDD = 4.75 V:*     |     |         |       |      |      |

| low, IOL = +12.5 mA                 | VOL |         | —     | 0.5  | v    |

| high, IOн = _12.5 mA                | Vон | 4.25    |       |      | V    |

| Output Impedance                    | _   |         | 20    | 40   | Ω    |

| Input voltages:**                   |     |         |       |      |      |

| low                                 | Vi∟ |         | _     | 1.0  | v    |

| high                                | VIH | 3.75    |       | —    | V    |

| threshold                           | Vтн |         | VDD/2 |      | V    |

| Output currents, short-circuit      | Isc | -100    |       | -200 | mA   |

| Input currents, VDD = 5.25 V:       |     |         |       |      |      |

| Iow, $VIN = 0.5 V$                  | lıL |         |       | _1.0 | μΑ   |

| high, VIN = 5.25 V                  | Ін  |         |       | 100  | μΑ   |

| Power supply current, VDD = 5.25 V: |     |         |       |      |      |

| DC conditions                       | IDD |         | 0.25  | 0.5  | mA   |

| 100 Mb/s                            | IDD |         | 75    | 80   | mA   |

\* IoL and IoH can increase to 25 mA. The reduced VoL and VoH are computed from the output impedance. \*\* Each input has typically 100 k $\Omega$  to Vss. Thus, a no connect input is pulled low.

#### **Maximum Ratings**

| Power supply voltage (VDD)                   | 7.0 V |

|----------------------------------------------|-------|

| Ambient operating temperature (TA) range0 to |       |

| Storage temperature (Tstg) range40 to +1     |       |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

External leads can be bonded or soldered safely at temperatures up to 300 °C.

#### **Timing Characteristics**

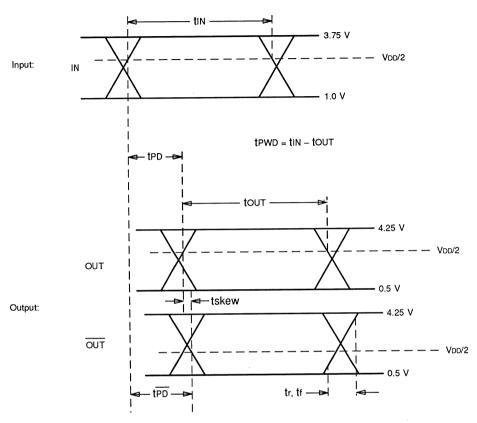

TA = 0 to 85 °C, VDD = 5.0 V  $\pm$  0.25 V, test circuit connected to output (see Figure 3).\*

| Symbol | Description                                                               |     | Тур | Max  | Unit |

|--------|---------------------------------------------------------------------------|-----|-----|------|------|

|        | Propagation delay, input to output:                                       |     |     |      |      |

| tPD    | AO, BO, CO, and DO                                                        | 2.0 | 3.0 | 4.75 | ns   |

| tPD    | $\overline{AO}$ , $\overline{BO}$ , $\overline{CO}$ , and $\overline{DO}$ | 2.0 | 3.0 | 4.75 | ns   |

| tskew  | Difference between propagation delays                                     |     |     |      |      |

|        | tPD - tPD                                                                 |     | 100 | 300  | ps   |

| tpwD   | Pulse width distortion,   tIN – tOUT                                      |     | 200 | 500  | ps   |

| tr, tf | Rise and fall time (10% to 90%)                                           |     | 1.5 | 3.0  | ns   |

| tin    | Input pulse width                                                         | 7   |     |      | ns   |

\* Input rise and fall times (10% to 90%) of less than 4 ns are necessary to guarantee maximum propagation delay, pulse width distortion, and skew characteristics.

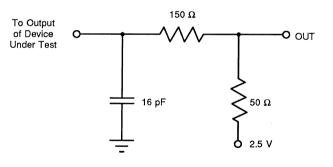

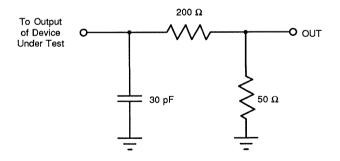

Figure 3. Timing Test Circuit

# T7274A Quad Differential Line Driver

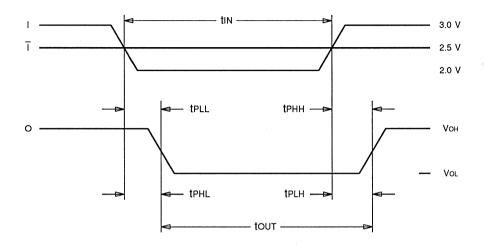

Figure 4. Timing Waveforms

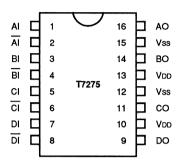

# **T7275B Quad Differential Line Receiver**

#### **Features**

- Low pulse width distortion

- 140-Mb/s data rate

- 800-mW maximum power dissipation

- 8.0-ns maximum propagation delay

- 0.6 V input sensitivity

- ±1 V common mode rejection

- 120-Ω HIC line-to-line input

- 7800-Ω SIC input

- Single 5 V supply

- 0 to 85 °C operating temperature

# Description

The T7275B Quad Differential Line Receiver integrated circuit is a quad differential input to CMOS output line receiver. It is functionally an ECL-level-to-CMOS converter. Direct interfacing to ECL signals is possible by AC coupling through a capacitor. The CMOS technology device is similar to the general-trade 26LS32 device; however, it has increased speed and decreased power consumption. By having four receivers in one T7275B device, circuit board package count is reduced. The average propagation delay is 5 ns and the common mode operating range is  $\pm 1$  V. Input dc offset is less than 50 mV. The inputs typically have 10 mV of hysteresis.

The T7275B line receiver is compatible with many line drivers, including the AT&T T7274A and 41LG devices, and the general-trade 26LS31 device. The quad differential line receiver is available in a 16-pin plastic DIP and small-outline J-lead (SOJ) package.

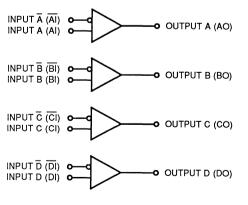

Figure 1. Logic Diagram

# **User Information**

# **Pin Descriptions**

Figure 2. Pin Function Diagram

#### Table 1. Pin Descriptions

| Symbol | Туре | Name                           |

|--------|------|--------------------------------|

| AI     | I    | A-line receiver input          |

| ĀĪ     | 1    | Inverted A-line receiver input |

| AO     | 0    | A-line receiver output         |

| BI     | 1    | B-line receiver input          |

| BI     | 1    | Inverted B-line receiver input |

| BO     | 0    | B-line receiver output         |

| CI     | 1    | C-line receiver input          |

| CI     | 1    | Inverted C-line receiver input |

| co     | 0    | C-line receiver output         |

| DI     | 1    | D-line receiver input          |

| DI     | 1    | Inverted D-line receiver input |

| DO     | 0    | D-line receiver output         |

| Vss    |      | Ground pins                    |

| VDD    |      | 5 V supply pins                |

# **Characteristics**

## **Electrical Characteristics**

TA = 0 to 85 °C, VDD =  $5.0 \text{ V} \pm 0.25 \text{ V}$

| Parameter                                                        | Sym | Min    | Тур  | Max    | Unit |

|------------------------------------------------------------------|-----|--------|------|--------|------|

| Output voltages, VDD = 4.75 V:*                                  |     |        |      |        |      |

| low, IOL = +12.5 mA                                              | VOL |        |      | 0.5    | V    |

| high, Iо́н = –12.5 mA                                            | Vон | 4.25   |      |        | V    |

| Output impedance                                                 | _   |        | 15   | 30     | Ω    |

| Differential input voltages:** VO = VOL or VOH                   |     |        |      |        |      |

| –2.1 V < Vсм < 2.9 V                                             | Vтн | 0.3    | 0.6  |        | v    |

| Output currents, short-circuit                                   | Isc | -150.0 |      | -300.0 | mA   |

| Differential Input currents:                                     |     |        |      |        |      |

| low                                                              | hL  |        |      | 1.0    | μΑ   |

| high                                                             | Іін |        |      | 1.0    | μA   |

| Power supply current, VDD = 5.25 V<br>DC conditions <sup>†</sup> | IDD | 0.0    | 12.0 | 20.0   | mA   |

\* IoL and IoH can increase to 25 mA. The reduced VoL and VoH are computed from the output impedance. \*\* Operation with 1 V < VcM < 4 V is possible, but with relaxed propagation delay and pulse width distortion characteristics.

<sup>†</sup> Pulling all inputs below 0.6 V powers down the device. All outputs are then equal to VDD.

#### **Maximum Ratings**

| Power supply voltage (VDD)                    | 7.0 V |

|-----------------------------------------------|-------|

| Ambient operating temperature (TA) range 0 to | 85 °C |

| Storage temperature (Tstg) range40 to +1      | 25 °C |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

External leads can be bonded or soldered safely at temperatures up to 300 °C.

#### **Timing Characteristics**

TA = 0 to 85 °C, VDD = 5.0 V  $\pm$  0.25 V, test circuit connected to output\* (see Figure 3).\*

| Symbol | Description                                                                                     | Min | Тур | Мах | Unit |

|--------|-------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|        | Propagation delay (AI, BI, CI, and DI)                                                          |     |     |     |      |

|        | (see Figure 4):                                                                                 |     |     |     |      |

| tрнн   | input high to output high                                                                       | 3.5 | 5.0 | 8.0 | ns   |

| tPLL   | input low to output low                                                                         | 3.5 | 5.0 | 8.0 | ns   |

|        | Propagation delay ( $\overline{AI}$ , $\overline{BI}$ , $\overline{CI}$ , and $\overline{DI}$ ) |     |     |     |      |

|        | (see Figure 4):                                                                                 |     |     |     |      |

| TPHL   | input high to output low                                                                        | 3.5 | 5.0 | 8.0 | ns   |

| tPLH   | input low to output high                                                                        | 3.5 | 5.0 | 8.0 | ns   |

| tPWD   | Pulse width distortion,   tin - tout                                                            | _   | 100 | 500 | ps   |

| tr,tf  | Rise and fall times (10% to 90%)                                                                | _   | 1.5 | 3.0 | ns   |

| tin    | Input pulse width                                                                               | 7   |     |     | ns   |

\* Input rise and fall times (10% to 90%) of less than 3 ns are necessary to guarantee maximum propagation delay and pulse width distortion characteristics.

Figure 3. Output Voltage and Propagation Delay Test Circuit

## Timing Diagram

# **T7500 PCM Codec with Filters**

## Features

- AT&T/CCITT-compatible

- Pin-selectable µ-law or A-law operation

- Pin-selectable transmit and receive gain

- Variable data rate (128 kHz to 4.096 MHz)

- On-chip voltage reference

- TTL-compatible I/O

# Description

- No external components required

- ±5 V supply

- Latch-up free CMOS technology

- Low power dissipation

20-mW typical power-down

80-mW typical operation

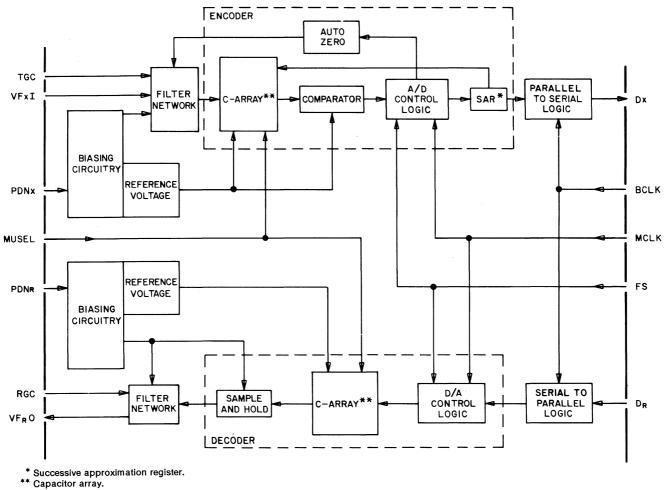

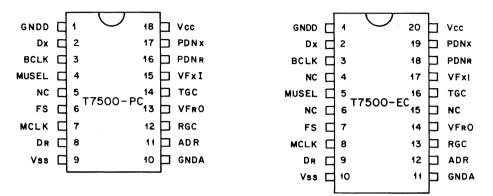

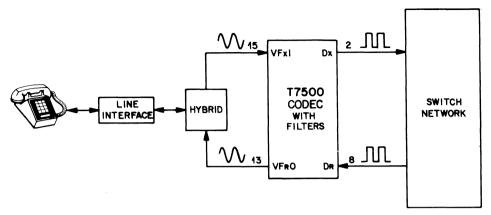

The T7500 PCM Codec with Filters is a single-chip integrated circuit that provides analog-to-digital and digital-to-analog conversion, as well as the transmit and receive filtering necessary to interface a voice telephone circuit to a time-division multiplexed system. The T7500 device is available in an 18-pin plastic DIP or a 20-pin plastic small-outline J-lead (SOJ) package for surface mounting.

Figure 1. Block Diagram

2-30

**T7500 PCM Codec with Filters**

# **User Information**

#### **Pin Descriptions**

| Table 1. Pin Descriptio |

|-------------------------|

|-------------------------|

| Symbol | Туре | Name/Function                                                                                                                                 |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| GNDD   |      | Ground (Digital).                                                                                                                             |

| Dx     | 0    | Data Transmit. Eight-bit µ-law or A-law PCM inverted binary output.                                                                           |

| BCLK   | 1    | <b>Bit Clock.</b> PCM is transmitted and received at a rate defined by this input clock (128 kHz—4.096-MHz).                                  |

| MUSEL  | I    | $\mu$ -law Select. A high (1) or no connection on this pin results in $\mu$ -law conversion. Apply a low (0) to this pin for A-law encodings. |

| NC     |      | No Connection.                                                                                                                                |

| FS     | 1    | Frame Synchronization. An 8-kHz timing pulse is applied to this pin to initiate A/D and D/A conversion processes.                             |

| MCLK   |      | Master Clock. 2.048-MHz                                                                                                                       |

| Dr     | 1    | Data Receive. This is the 8-bit $\mu$ -law or A-law PCM inverted binary input.                                                                |

| GNDA   |      | Ground (Analog).                                                                                                                              |

| Symbol | Туре | Name/Function                                                                                                                                                                                                                                                                  |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vss    |      | –5 V Supply ( $\pm$ 5%).                                                                                                                                                                                                                                                       |

| ADR    | I    | <b>Address.</b> A low or no connection on this pin enables the FS pulse. It is used for channel selection when more than one codec is used on a PCM bus.                                                                                                                       |

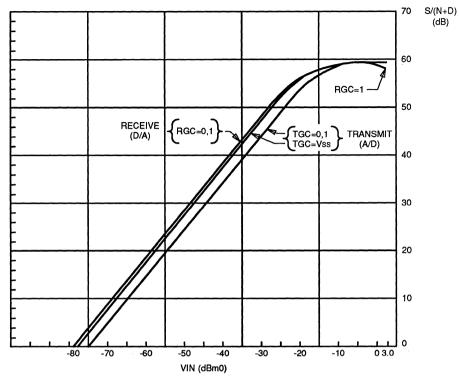

| RGC    | I    | <b>Receive Gain Control.</b> A low or no connection on this pin sets the gain to 0 dB (0 output TLP); a high on this pin sets the receive gain to +3 dB $\pm$ 0.1 dB (+3 output TLP). When high, the gain is set with respect to the gain measured at 0 dB setting.            |

| VFrO   | 0    | Voice Frequency Receive Output. The maximum load permitted on this pin is 20 k $\Omega$ in parallel with 50 pF.                                                                                                                                                                |

| TGC    | I    | <b>Transmit Gain Control.</b> A high or no connection on this pin sets the transmit gain to 0 dB (0 input TLP); a low sets the transmit gain to $-3$ dB $\pm$ 0.1 dB (+3 input TLP). When low, the gain is set with respect to the gain measured at 0 dB setting.              |

| VFxI   | I    | Voice Frequency Transmit Input. Analog input to the transmit filters. The input impedance on this pin is greater than 400 k $\Omega$ .                                                                                                                                         |

| PDNR   |      | <b>Power-Down Receive.</b> A high on this pin causes power-down of receive side. During receive-side power-down, VFRO is grounded through a low impedance and the receive-side analog circuitry is disabled. A low or no connection allows normal receive-side operation.      |

| PDNx   | I    | <b>Power-Down Transmit.</b> A high on this pin causes power-down of transmit side. A transmit power-down causes the Dx buffer to go into a high-impedance state and all encoder analog circuitry to be disabled. A low or no connection allows normal transmit-side operation. |

| Vcc    |      | +5 V Supply (± 5%).                                                                                                                                                                                                                                                            |

#### Overview

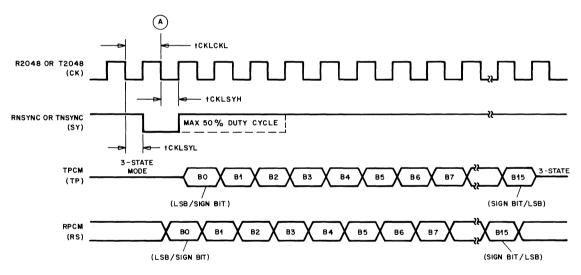

The T7500 PCM Codec is a synchronous device with a common master clock and synchronization input that drives both the transmit and receive sections. Device operation requires three logic inputs: MCLK, FS, and BCLK.

On power-up, the codec becomes active only after receiving a FS and ADR signal. The serial transfer of data to DR and from Dx proceeds at a rate determined by BCLK (see Figure 4).

The digital output returns to a high-impedance state upon completion of this process and remains in this state until another set of synchronization and address signals is received. This allows the device to be used with a shared PCM bus (up to 64 channels at 4.096 MHz).

Figure 3. PCM System Block Diagram

The T7500 codec has a power-down mode that reduces power consumption and heat dissipation when the device is inactive. Two pins are used for this power-down option. A high applied to PDNR disables the receive side of the device; PDNx performs the same function on the transmit side of the device. Each side can be independently disabled. When the receive side is powered-down, output VFRO is grounded through a low impedance and all receive-side analog circuitry is disabled. Transmit power-down results in output Dx going into a high-impedance state and all transmit-side analog circuitry being disabled. The device is activated by applying a low to both leads.

This device implements either  $\mu$ -law or A-law PCM encoding. MUSEL is used to determine the type of encoding. Inverted binary format is used for  $\mu$ -law encoding. Alternate digit inversion is used for A-law transmission.

Separate gain controls provide gain settings for the transmit and receive sections. Either 0 dB or -3 dB gain can be selected for the transmit side and either 0 dB or +3 dB for the receive side.

On-chip voltage referencing is provided, eliminating the need for external circuitry and gain trimming.

# **Characteristics**

#### **DC** Characteristics

TA = 0 to 70 °C; Vcc = +5 V  $\pm$  5%; Vss = -5 V  $\pm$  5%; GNDA = 0 V; GNDD = 0 V; OTLP, unless otherwise specified. Typical values are for TA = 25 °C and nominal power supply values.

#### Table 2. Digital Interface

| Symbol | Parameter                 | Min | Мах | Unit | Test Condition           |

|--------|---------------------------|-----|-----|------|--------------------------|

| 11L    | Low-level input current   | -20 |     | μA   | $GNDD \leq Vin \leq ViL$ |

| Ін     | High-level input current  | -   | 20  | μA   | $ViH \leq ViN \leq VCC$  |

| VIL    | Input low voltage         |     | 0.8 | v    | —                        |

| VIH    | Input high voltage        | 2.0 |     | V    |                          |

| Vol    | Output low voltage        | _   | 0.4 | V    |                          |

| Voн    | Output high voltage       | 2.4 |     | V    |                          |

| Сі     | Digital input capacitance |     | 5   | pF   |                          |

| IL     | Output leakage current    | -50 | 50  | μA   |                          |

# Table 3. Power Dissipation\*

| Symbol | Parameter                   | Min   | Тур  | Мах     | Unit |

|--------|-----------------------------|-------|------|---------|------|

| ICC1   | Vcc operating current       | _     | 8.5  | 15      | mA   |

| ISS1   | Vss operating current       |       | -7.5 | _13     | mA   |

| ICCO   | Vcc power-down current      |       | 2.0  | 7.0     | mA   |

| ISSO   | Vss power-down current      |       | -2.0 | -4.0    | mA   |

| Vcc    | Positive operating voltage  | 4.75  | 5    | 5.25**  | ۷    |

| Vss    | Negative operating voltage  | -4.75 | 5    | -5.25** | ۷    |

| P1     | Operating power dissipation |       | 80   | 147     | mW   |

| P0     | Power-down dissipation      |       | 20   | 55      | mW   |

\* All measurements made at fBCLK = 2.048 MHz, outputs loaded. \*\* Absolute maximum ratings are Vcc = +7.5 V, Vss = -7.5 V. Exceeding these values may result in permanent internal damage.

## Table 4. Analog Interface — Transmit Filter Input Stage

| Symbol | Parameter                   |     | Тур | Мах | Unit |

|--------|-----------------------------|-----|-----|-----|------|

| Ri     | Input resistance @ VFxI     | 0.4 | 1.1 |     | MΩ   |

| VOFF   | Input offset voltage @ VFxI |     |     | 20  | mV   |

| CL     | Load capacitance @ VFxI     |     | 20  | 40  | pF   |

| Symbol | Parameter                                         | Min    | Тур | Мах   | Unit | Test Conditions  |

|--------|---------------------------------------------------|--------|-----|-------|------|------------------|

| Ro     | Output resistance @ VFRO<br>for voice frequencies |        | 50  |       | Ω    | _                |

| VOFF   | Output DC offset @ VFRO                           |        | 50  |       | mV   | Relative to GNDA |

| CL     | Load capacitance @ VFRO1                          | _      | -   | 50    | pF   |                  |

| Vo     | Maximum voltage output<br>(swing across RL):      |        |     |       |      |                  |

|        | μ-law                                             | -2.229 |     | 2.229 | V    | RGC = high       |

|        | A-law                                             | -2.229 |     | 2.229 | V    | (+3TLP)          |

|        | μ-law                                             | -1.578 | —   | 1.578 | v    | RGC = low        |

|        | A-law                                             | -1.572 |     | 1.572 | V    | (OTLP)           |

| RL     | Load resistance @ VFRO                            | 20     |     |       | kΩ   |                  |

| Table 5. | Analog | Interface — | Receive | Filter | Driver | Amplifier | Stage |

|----------|--------|-------------|---------|--------|--------|-----------|-------|

|----------|--------|-------------|---------|--------|--------|-----------|-------|

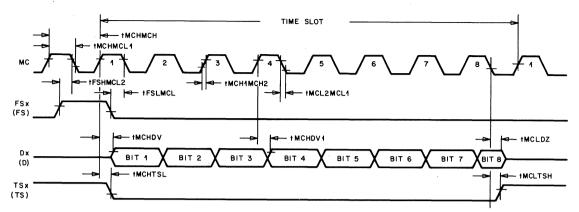

# **Timing Characteristics**

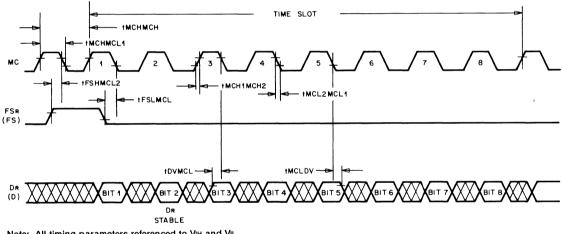

### Table 6. Clock Section

| Symbol    | Parameter                | Min       | Тур       | Мах       | Unit |

|-----------|--------------------------|-----------|-----------|-----------|------|

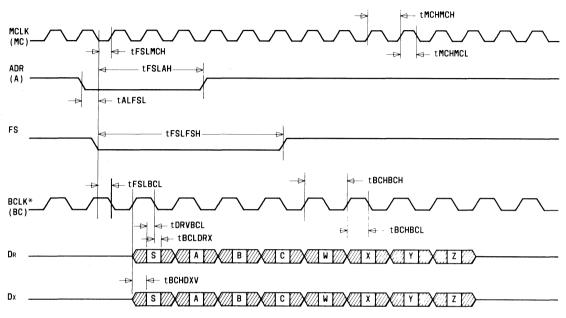

| tBCHBCH*  | Bit clock period         | .244      | _         | 7.8       | μS   |

| tBCHBCL   | Bit clock pulse width    | .4tBCHBCH | .5tBCHBCH | .6tBCHBCH |      |

| tMCHMCH** | Master clock period      |           | 488       |           | ns   |

| tMCHMCL   | Master clock pulse width | .4tMCHMCH | .5tMCHMCH | .6tMCHMCH |      |

\* BCLK ranges from 128 kHz to 4.096 MHz. \*\* 2.048 MHz.

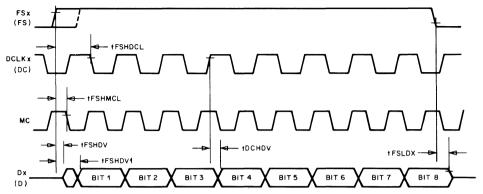

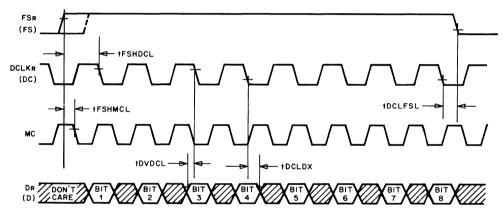

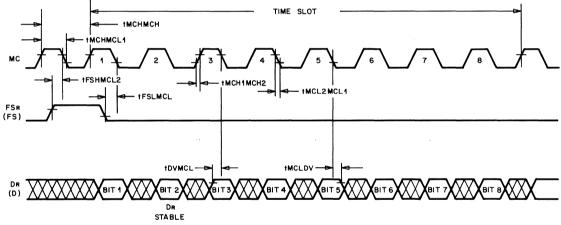

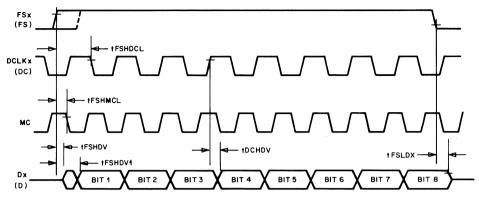

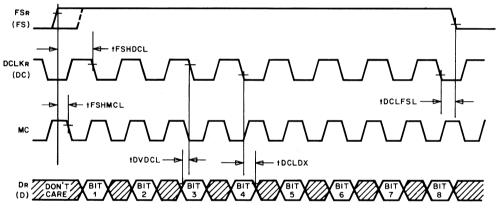

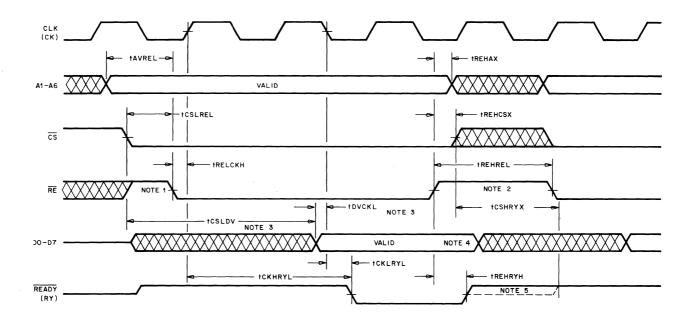

Table 7. Data Section

| Symbol               | Parameter                              | Min        | Тур             | Max          | Unit |

|----------------------|----------------------------------------|------------|-----------------|--------------|------|

| tFSLMCH              | Sync set-up time in<br>reference to MC | 90         | .5tMCHMCH       | tMCHMCH      | ns   |

| tFSLAH*              | Address hold time                      | 1.5tBCHBCH | <b>3tBCHBCH</b> |              |      |

| tALFSL               | Address set-up time                    | 10         | .5tBCHBCH       |              | ns   |

| tFSLFSH**            | Sync pulse width                       | 1.5tBCHBCH | 2tBCHBCH        | 63           | μS   |

| tFSLBCL              | Sync set-up time                       | 75         | 200             | tBCHBCH - 50 | ns   |

| tDRVBCL              | DR set-up time                         | 50         | 200             |              | ns   |

| tBCLDRX              | DR hold time                           | 50         | 300             |              | ns   |

| tBCHDXV <sup>†</sup> | DX delay time                          | 30         | 80              | 150          | ns   |

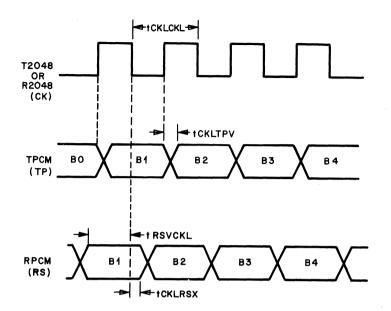

\* Max - constant low. \*\* Negative logic sense. <sup>†</sup> DX max load ≤ 300 pF plus 1 medium-power TTL load.

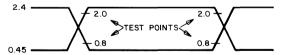

#### **Timing Diagram**

\* BCLK ranges from 128 kHz to 4.096 MHz. It determines ADR, FS, DR, and Dx timing.

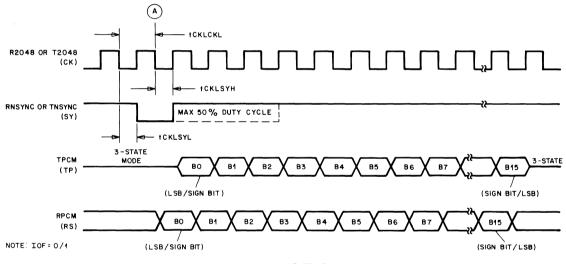

Figure 4. Input/Output Timing

## **AC Characteristics — Transmission Parameters**

#### Table 8. Gain and Dynamic Range

| Symbol | Parameter                                                | Min   | Тур   | Max   | Unit | Test Conditions                                                          |

|--------|----------------------------------------------------------|-------|-------|-------|------|--------------------------------------------------------------------------|

| GE     | Encoder milliwatt response<br>(transmit gain tolerance): |       |       |       |      | Signal input = .7746 Vrms<br>Vcc and Vss are $\pm$ 5%<br>TA = 0 to 70 °C |

|        | μ-law                                                    | -0.15 | ±0.08 | 0.15  | dBm0 |                                                                          |

|        | A-law                                                    | -0.18 | ±0.08 | ±0.18 | dBm0 |                                                                          |

| GD     | GD Digital milliwatt response (receive gain tolerance):  |       |       |       |      | VCC and VSS are $\pm 5\%$<br>TA = 0 to 70 °C                             |

|        | μ-law                                                    | -0.15 | ±0.08 | 0.15  | dBm0 |                                                                          |

|        | A-law                                                    | -0.18 | ±0.08 | 0.18  | dBm0 |                                                                          |

| Symbol            | Parameter                      | Min   | Мах  | Unit | Test Conditions |

|-------------------|--------------------------------|-------|------|------|-----------------|

| <b>G</b> TXμ      | Transmit gain tracking error   | -0.25 | 0.25 | dB   | 3 to –37 dBm0   |

|                   | (sinusoidal input, μ-law)      | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

| GTXA              | Transmit gain tracking error   | -0.25 | 0.25 | dB   | 3 to -37 dBm0   |

|                   | (sinusoidal input, A-law)      | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

| <b>G</b> TR $\mu$ | Receive gain tracking error    | -0.25 | 0.25 | dB   | 3 to -37 dBm0   |

|                   | (sinusoidal input, $\mu$ -law) | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

| GTRA              | Receive gain tracking error    | -0.25 | 0.25 | dB   | 3 to -37 dBm0   |

|                   | (sinusoidal input, A-law)      | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

## Table 9. Gain Tracking — Reference Level = 1.02 kHz, 0 dBm

## Table 10. Distortion

| Symbol   | Parameter                      | Min      | Тур | Мах        | Unit         | Test Conditions                             |

|----------|--------------------------------|----------|-----|------------|--------------|---------------------------------------------|

| Dxs      | Transmit signal to distortion  |          |     |            |              |                                             |

|          | (sinusoidal input = 1.02 kHz): |          |     |            |              |                                             |

|          | μ-law                          | 36       |     | —          | dB           | 0 < VFxl <30 dBm0                           |

|          | A-law                          | 35       |     |            | dB           |                                             |

|          | μ-law                          | 30       | —   |            | dB           | –40 dBm0                                    |

|          | A-law                          | 29       |     |            | dB           |                                             |

|          | μ-law                          | 25       |     |            | dB           | –45 dBm0                                    |

|          | A-law                          | 25       |     |            | dB           |                                             |

| DRS      | Receive signal to distortion   |          |     |            |              |                                             |

|          | (sinusoidal input = 1.02 kHz): |          |     |            | JD           |                                             |

|          | μ-law<br>A-law                 | 36<br>35 |     | _          | dB<br>dB     | $0 \le DR \le -30 \text{ dBm0}$             |

|          |                                |          |     |            |              |                                             |

|          | μ-law<br>A-law                 | 30<br>29 |     | _          | dB<br>dB     | –40 dBm0                                    |

|          |                                |          |     |            |              |                                             |

|          | μ-law<br>A-law                 | 25<br>25 |     |            | dB<br>dB     | –45 dBm0                                    |

|          |                                | 25       |     |            |              | 0 1 1 0 M                                   |

| DXSF     | Transmit single frequency      | -        | -   | -28<br>-40 | dBm0<br>dBm0 | $0 \le \text{input} \le 2 \text{ MHz}$      |

| <u> </u> | (distortion products)          |          |     |            |              | $.2 \leq \text{input} \leq 3.4 \text{ kHz}$ |

| DRSF     | Receive single frequency       | -        |     | -28        | dBm0         | $0 \le \text{input} \le 2 \text{ MHz}$      |

|          | (distortion products)          |          |     | _40        | dBm0         | $.2 \leq input \leq 3.4 \text{ kHz}$        |

| DxD      | Transmit absolute delay        |          | 340 |            | μS           |                                             |

| DRD      | Receive absolute delay         |          | 240 |            | μS           |                                             |

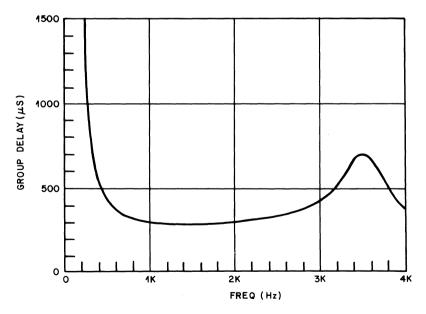

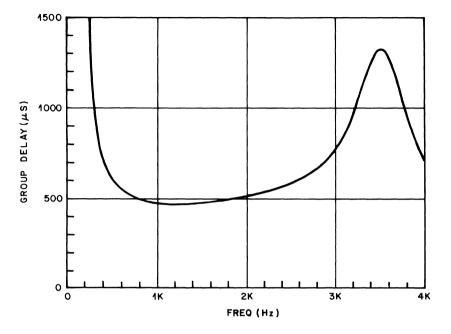

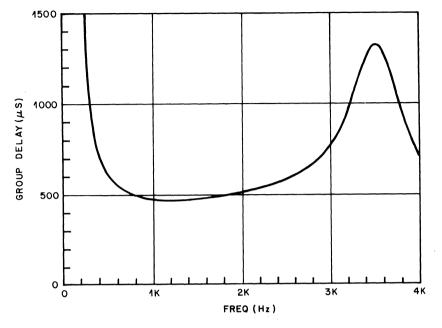

| DDAA     | Delay distortion               | -        | 250 | -          | μS           | f = 500 Hz                                  |

|          | (analog-to-analog)             | -        | 60  | -          | μS           | f = 1 kHz                                   |

|          |                                | -        | 20  | -          | · ·          | f = 1.5 kHz                                 |

|          |                                |          | 20  | -          | μs           | f = 2  kHz                                  |

|          |                                | -        | 50  | -          | μS           | f = 2.5 kHz                                 |

|          | L                              |          | 220 |            | μS           | f = 3 kHz                                   |

## Table 11. Noise

| Symbol | Parameter                                                    | Min | Тур | Max        | Unit             | Test Conditions                                                                                     |

|--------|--------------------------------------------------------------|-----|-----|------------|------------------|-----------------------------------------------------------------------------------------------------|

| FxC    | Transmit idle channel noise<br>(C-message weighted)          |     | 14  | 18<br>23   | dBrnC0<br>dBrnC0 | μ-law<br>A-law                                                                                      |

| FRC    | Receive idle channel noise<br>(C-message weighted)           |     | 9   | 13<br>15   | dBrnC0<br>dBrnC0 | µ-law<br>A-law                                                                                      |

| Fxp    | Transmit idle channel noise<br>(psophometric weighted)       | _   | -69 | 67         | dBm0p            | _                                                                                                   |

| FRP    | Receive idle channel noise<br>(psophometric weighted)        |     | 81  | -75        | dBm0p            | _                                                                                                   |

| PSRxcc | VCC power supply rejection<br>(transmit channel)             | -30 | -35 |            | dB               | Idle channel; 100-<br>mVpp, 1.02-kHz<br>signal on dc supply;<br>measured 1.02-kHz<br>signal at Dx   |

| PSRxss | Vss power supply rejection<br>(transmit channel)             | -30 | -35 |            | dB               | Idle channel; 100-<br>mVpp, 1.02-kHz<br>signal on dc supply;<br>measured 1.02-kHz<br>signal at Dx   |

| PSRRCC | Vcc power supply rejection<br>(receive channel)              | -30 | -35 |            | dB               | Idle channel; 100-<br>mVpp, 1.02-kHz<br>signal on dc supply;<br>measured 1.02-kHz<br>signal at VFRO |

| PSRRSS | Vss power supply rejection<br>(receive channel)              | -30 | -35 |            | dB               | Idle channel; 100-<br>mVpp, 1.02-kHz<br>signal on dc supply;<br>measured 1.02-kHz<br>signal at VFRO |

| FCXR   | Crosstalk (transmit to<br>receive, single-ended<br>outputs): |     |     |            |                  | VFxI = 0 dBm0;<br>1.02-kHz signal<br>measured at VFR;<br>DR = idle code                             |

|        | μ-law<br>A-law                                               |     | _   | _71<br>_70 | dB<br>dB         |                                                                                                     |