#### **NONVOLATILE MEMORY**

EPROM . EPROM . FLASH

DATA BOOK

S AN ISO BOOK ARTHUR PROPERTY CONNORNAL

# Atmel Corporation Nonvolatile Memory Data Book May 1996

E<sup>2</sup>PROM • EPROM • Flash

is the registered trademark of Atmel Corporation, 2325 Orchard Parkway, San Jose, CA 95131

#### Important Notice

Atmel guarantees that its circuits will be free from defects of material and work-manship under normal use and service, and that these circuits will perform to current specifications in accordance with, and subject to, the Company's standard warranty which is detailed in Atmel's Purchasing Order Acknowledgment.

Atmel reserves the right to change devices or specifications detailed in this data book at any time without notice, and assumes no responsibility for any errors within this document. Atmel does not make any commitment to update this information. Atmel assumes no responsibility for the use of any circuits described in this data book, nor does the Company assume responsibility for the functioning of undescribed features or parameters.

In the absence of a written agreement to the contrary, Atmel assumes no liability with respect to the use of semiconductor devices described in this data book for applications assistance, customers' product design or infringement of patents or copyrights of third parties.

Atmel's products are not authorized for use as critical components in life support devices or systems and the use as such implies that user bears all risk of such use.

If Atmel is an approved vendor on a Standard Microcircuit Drawing (SMD), the Atmel similar part number specification is compliant with the SMD.

© Atmel Corporation 1996

Printed on recycled paper.

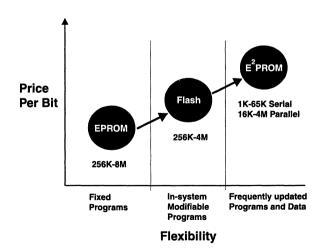

#### Nonvolatile Memory Overview

With the nonvolatile memories available from Atmel, you are given the ability to program devices late in a system's development cycle, or even after the system is complete. This feature gives you the flexibility for meeting changing market conditions. The principle products of nonvolatile memory are EPROMs (erasable programmable read-only memories), E<sup>2</sup>PROMs (electronically erasable programmable read-only memories) and Flash devices.

#### **EPROMs**

Atmel is a leading supplier of high-speed and low-voltage EPROMs and is recognized as one of the top three world suppliers in the market. EPROMs, the lowest cost user-programmable nonvolatile memory, can be programmed electrically in a programmer or its current system. These devices are used for program storage in computer and communications equipment, such as cellular phones, pagers, modems, and other computer peripherals. Atmel's EPROMs are manufactured in 5V and 2.7V versions with capacities up to 8M bits and access times as fast as 45 ns.

#### Flash Memory

Known as the major volume supplier of 2.7V read and write Flash memories, Atmel leads the industry as one of the top three Flash makers in the world. Flash memories combine the electrically erasable flexibility of E²PROMs with the higher density and lower cost per bit of EPROMs—representing the fastest growing product sector in the semiconductor industry. What distinguishes Atmel's Flash products from its competitors is its use of a single low-voltage power source, for write and read functions. Atmel's Flash devices are used primarily to store operating programs in telecommunications, graphics, networking systems, and home video game systems. With Atmel's 2.7V low-voltage devices, you can extend battery life or reduce the number of batteries necessary for portable systems such as cellular telephones, pagers, laptop and palmtop devices.

#### Parallel E<sup>2</sup>PROMs

Since 1991 Atmel has been the world's largest supplier of these in-system, reprogrammable nonvolatile memories. E<sup>2</sup>PROMs are distinguished as Parallel- or Serial-interface through their connection to the system's microcontroller or microprocessor. Atmel offers the industry's most complex full-featured Parallel E<sup>2</sup>PROM, the world's first single-chip 4M bit monolithic E<sup>2</sup>PROM, which is used extensively in many military and commercial avionics applications. Atmel produces industry's only complete line of standard-voltage and battery-voltage Parallel devices that serve the growing portable equipment market. Parallel E<sup>2</sup>PROM leadership; first to market with battery-voltage devices and first to market with the largest density devices.

#### Serial E<sup>2</sup>PROMs

Serial-interface E<sup>2</sup>PROMs are used in a broad spectrum of consumer, telecommunication and automotive products, primarily for recording and holding personal preference data, such as programmable radio stations, seat comfort controls, auto-dial in telephones and program memory in camcorders. Key to Atmel's success in Serials is its 1.8V low-voltage family. Atmel is the only manufacturer to offer all Serial devices available in today's market.

Atmel Corporation designs, manufactures, and markets high quality and high performance CMOS memory, logic and analog integrated circuits. Founded in 1984, the Company serves the manufacturers of computation, communications and instrumentation equipment in commercial, industrial and military environments.

Atmel's broad line of products provide customers with a variety of solutions to their memory and logic applications. Atmel offers high-density, high-speed memory and logic standard products as well as custom gate arrays.

Atmel guarantees quality and reliability by fabricating all products— no matter what their intended application— to meet or exceed the specifications of Military Standard 883.

Whether you are new to programmable logic or an experienced user, Atmel is committed to your success. If you have any questions or would like to place an order, please contact your local Atmel sales office as listed in the back of this data book, or contact Atmel's corporate headquarters:

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 TEL: (408) 441-0311 FAX: (408) 436-4300 Fax-on-Demand

North America: 1-(800) 29-ATMEL 1-(800) 292-8635

International: 1-(408) 441-0732

e-mail

literature@atmel.com

Web Site

http://www.atmel.com

BBS

1-(408) 436-4309

We thank you for considering Atmel semiconductors. Battery-Voltage, Cache Logic, and Rapid are trademarks of Atmel Corporation.

Overview

# Table of Contents

| Section 1 | Product Selection Information  Nonvolatile Memory Selection Guide |                                       |                                             |       |  |

|-----------|-------------------------------------------------------------------|---------------------------------------|---------------------------------------------|-------|--|

| Section 2 | CMOS E <sup>2</sup> PROMs                                         |                                       |                                             |       |  |

|           | Serial E <sup>2</sup> PROMs                                       |                                       |                                             |       |  |

|           | AT24C01                                                           | 128 x 8                               | 2-Wire, 1K Serial E <sup>2</sup> PROM       | 2-3   |  |

|           | AT24C21                                                           | 128 x 8                               | 2-Wire, 1K Serial E <sup>2</sup> PROM       |       |  |

|           | AT24C01A                                                          | 128 x 8                               | 2-Wire, 1K Serial E <sup>2</sup> PROM       |       |  |

|           | AT24C02                                                           | 256 x 8                               | 2-Wire, 2K Serial E <sup>2</sup> PROM       | 2-25  |  |

|           | AT24C04                                                           | 512 x 8                               | 2-Wire, 4K Serial E <sup>2</sup> PROM       | 2-25  |  |

|           | AT24C08                                                           | 1024 x 8                              | 2-Wire, 8K Serial E <sup>2</sup> PROM       | 2-25  |  |

|           | AT24C16                                                           | 2048 x 8                              | 2-Wire, 16K Serial E <sup>2</sup> PROM      | 2-25  |  |

|           | AT24C164                                                          | 2048 x 8                              | 2-Wire, 16K Serial E <sup>2</sup> PROM      | 2-39  |  |

|           | AT24C32                                                           | 4096 x 8                              | 2-Wire, 32K Serial E <sup>2</sup> PROM      |       |  |

|           | AT24C64                                                           | 8192 x 8                              | 2-Wire, 64K Serial E <sup>2</sup> PROM      | 2-49  |  |

|           | AT93C46                                                           | 64 x 16 / 128 x 8                     | 3-Wire, 1K Serial E <sup>2</sup> PROM       | 2-63  |  |

|           | AT93C46A                                                          | 64 x 16                               | 3-Wire, 1K Serial E <sup>2</sup> PROM       | 2-79  |  |

|           | AT93C56                                                           | 128 x 16 / 256 x 8                    | 3-Wire, 2K Serial E <sup>2</sup> PROM       |       |  |

|           | AT93C57                                                           | 128 x 16 / 256 x 8                    | 3-Wire, 2K Serial E <sup>2</sup> PROM       |       |  |

|           | AT93C66                                                           | 256 x 16 / 512 x 8                    | 3-Wire, 4K Serial E <sup>2</sup> PROM       | 2-63  |  |

|           | AT59C11                                                           | 64 x 16 / 128 x 8                     | 4-Wire, 1K Serial E <sup>2</sup> PROM       | 2-89  |  |

|           | AT59C22                                                           | 128 x 16 / 256 x 8                    | 4-Wire, 2K Serial E <sup>2</sup> PROM       | 2-89  |  |

|           | AT59C13                                                           | 256 x 16 / 512 x 8                    | 4-Wire, 4K Serial E <sup>2</sup> PROM       |       |  |

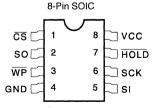

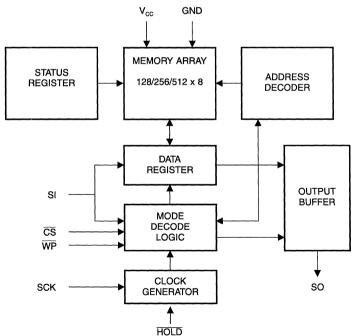

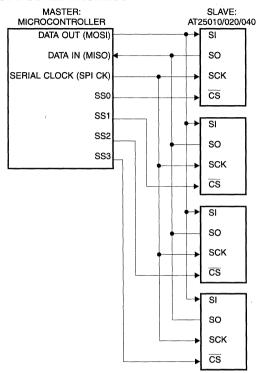

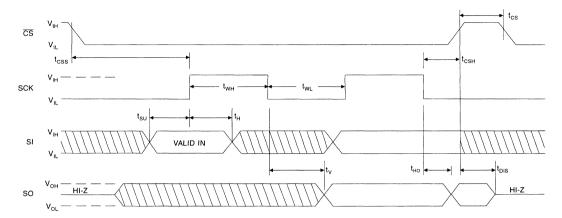

|           | AT25010                                                           | 128 x 8                               | SPI, 1K Serial E <sup>2</sup> PROM          | 2-101 |  |

|           | AT25020                                                           | 256 x 8                               | SPI, 2K Serial E <sup>2</sup> PROM          |       |  |

|           | AT25040                                                           | 512 x 8                               | SPI, 4K Serial E <sup>2</sup> PROM          | 2-101 |  |

|           | AT25320                                                           | 4096 x 8                              | SPI, 32K Serial E <sup>2</sup> PROM         |       |  |

|           | AT25640                                                           | 8192 x 8                              | SPI, 64K Serial E <sup>2</sup> PROM         |       |  |

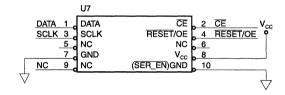

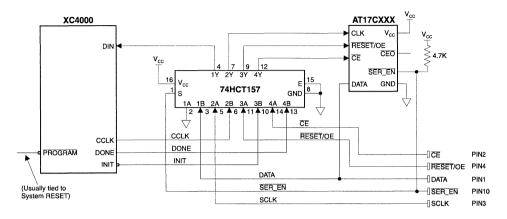

|           | AT17C65                                                           | 65,536 x 1                            | 65K FPGA Configuration E <sup>2</sup> PROM  |       |  |

|           | AT17C128                                                          | 131,072 x 1                           | 128K FPGA Configuration E <sup>2</sup> PROM |       |  |

|           | AT17C256                                                          | 262,144 x 1                           | 256K FPGA Configuration E <sup>2</sup> PROM | 2-117 |  |

|           | Parallel E <sup>2</sup> PROMs Battery-Voltage  AT28BV16           | • <b>2.7V - 3.6V Ope</b> ra<br>2K x 8 | <b>tion</b><br>16K E <sup>2</sup> PROM      | 2-119 |  |

| Section 2 | CMOS E <sup>2</sup> PROMs (Continued)                |                                  |                                                          |  |  |  |

|-----------|------------------------------------------------------|----------------------------------|----------------------------------------------------------|--|--|--|

|           | Battery-Voltage <sup>™</sup> • 2.7V - 3.6V Operation |                                  |                                                          |  |  |  |

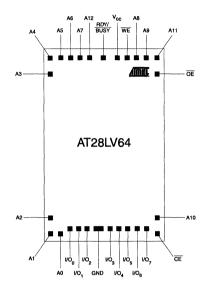

|           | AT28BV64                                             | 8K x 8                           | 64K E <sup>2</sup> PROM2-127                             |  |  |  |

|           | Low Voltage • 3.0V                                   | - 3.6V Operation                 |                                                          |  |  |  |

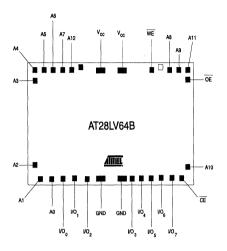

|           | AT28LV64B                                            | 8K x 8                           | 3-Volt, 64K E <sup>2</sup> PROM w/ Data Protection 2-135 |  |  |  |

|           | AT28LV256                                            | 32K x 8                          | 3-Volt, 256K E <sup>2</sup> PROM2-145                    |  |  |  |

|           | AT28LV010                                            | 128K x 8                         | 3-Volt, 128K E <sup>2</sup> PROM2-155                    |  |  |  |

|           | Standard • 5V Ope                                    | ration                           |                                                          |  |  |  |

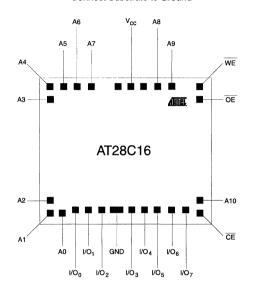

|           | AT28C16                                              | 2K x 8                           | 16K E <sup>2</sup> PROM2-165                             |  |  |  |

|           | AT28C16-T                                            | 2K x 8                           | 16K PCMCIA                                               |  |  |  |

|           |                                                      |                                  | Nonvolatile Attribute Memory2-175                        |  |  |  |

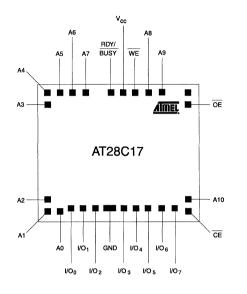

|           | AT28C17                                              | 2K x 8                           | 16K E <sup>2</sup> PROM2-183                             |  |  |  |

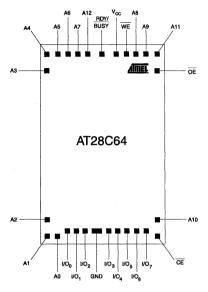

|           | AT28C64                                              | 8K x 8                           | 64K E <sup>2</sup> PROM2-193                             |  |  |  |

|           | AT28C64X                                             | 8K x 8                           | 64K E <sup>2</sup> PROM without Ready-Busy 2-193         |  |  |  |

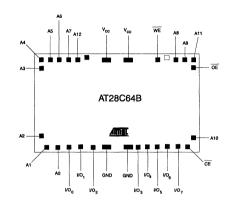

|           | AT28C64B                                             | 8K x 8                           | 64K E <sup>2</sup> PROM with S/W Data Protection 2-205   |  |  |  |

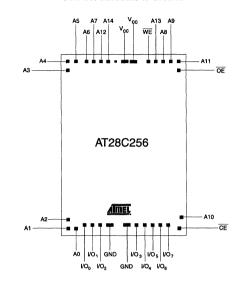

|           | AT28C256                                             | 32K x 8                          | 256K E <sup>2</sup> PROM2-217                            |  |  |  |

|           | AT28C010 Com/Ind                                     | 128K x 8                         | 1M bit E <sup>2</sup> PROM with 128-Byte Page,           |  |  |  |

|           |                                                      |                                  | Commercial and Industrial2-231                           |  |  |  |

|           | AT28C010 Mil                                         | 128K x 8                         | 1M bit E <sup>2</sup> PROM with 128-Byte Page,           |  |  |  |

|           | i                                                    |                                  | Military 2-243                                           |  |  |  |

|           | AT28C040                                             | 512K x 8                         | 4M bit E <sup>2</sup> PROM with 512-Byte Page 2-255      |  |  |  |

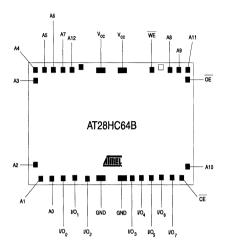

|           | AT28HC64B                                            | 8K x 8                           | High Speed, 64K E <sup>2</sup> PROM with                 |  |  |  |

|           |                                                      |                                  | S/W Data Protection2-267                                 |  |  |  |

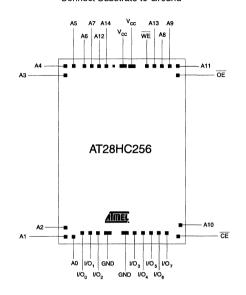

|           | AT28HC256                                            | 32K x 8                          | High Speed, 256K E <sup>2</sup> PROM2-279                |  |  |  |

|           | E <sup>2</sup> PROM Application                      | on Notes                         |                                                          |  |  |  |

|           |                                                      |                                  | 2-291                                                    |  |  |  |

|           | Software Chip Erase                                  |                                  | 2-295                                                    |  |  |  |

|           |                                                      |                                  | s2-297                                                   |  |  |  |

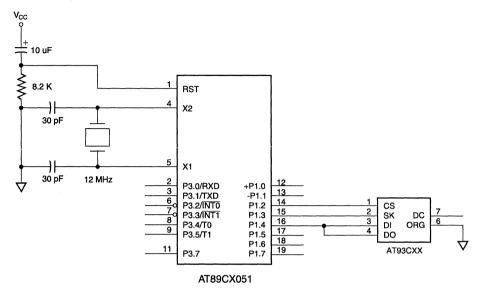

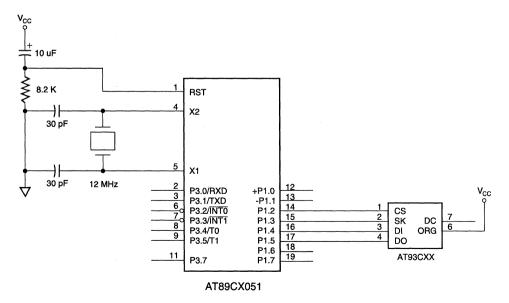

|           |                                                      |                                  | AT89CX051 Microcontrollers2-299                          |  |  |  |

|           |                                                      |                                  | AT89CX051 Microcontrollers2-301                          |  |  |  |

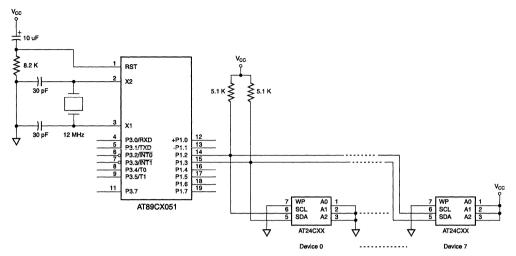

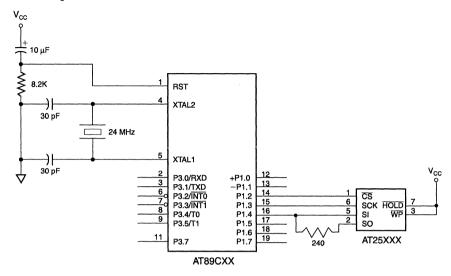

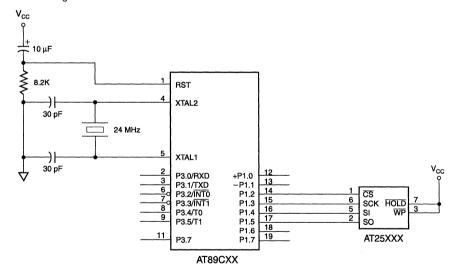

|           | Interfacing AT25XXX                                  | Serial E <sup>2</sup> PROMs with | AT89CXX Microcontrollers2-303                            |  |  |  |

# Table of Contents

| Section 3 | CMOS EPROMs                                     |                                 |                              |       |  |

|-----------|-------------------------------------------------|---------------------------------|------------------------------|-------|--|

|           | Battery-Voltage                                 | ™ • 2.7V - 3.6V Op              | eration                      |       |  |

|           | AT27BV256                                       | 32K x 8                         | 256K, 2.7-Volt EPROM         | 3-3   |  |

|           | AT27BV512                                       | 64K x 8                         | 512K, 2.7-Volt EPROM         |       |  |

|           | AT27BV010                                       | 128K x 8                        | 1M bit, 2.7-Volt EPROM       | 3-23  |  |

|           | AT27BV1024                                      | 64K x 16                        | 1M bit, 2.7-Volt EPROM       | 3-33  |  |

|           | AT27BV020                                       | 256K x 8                        | 2M bit, 2.7-Volt EPROM       | 3-43  |  |

|           | AT27BV040                                       | 512K x 8                        | 4M bit, 2.7-Volt EPROM       | 3-53  |  |

|           | AT27BV4096                                      | 256K x 16                       | 4M bit, 2.7-Volt EPROM       | 3-63  |  |

|           | Low Voltage ● 3                                 | .0V - 3.6V Operatio             | on                           |       |  |

|           |                                                 | •                               |                              | 3-73  |  |

|           | AT27LV256A                                      | 32K x 8                         | 256K, 3-Volt EPROM           | 3-75  |  |

|           | AT27LV512A                                      | 64K x 8                         | 512K, 3-Volt EPROM           | 3-85  |  |

|           | AT27LV010A                                      | 128K x 8                        | 1M bit, 3-Volt EPROM         | 3-95  |  |

|           | AT27LV020A                                      | 256K x 8                        | 2M bit, 3-Volt EPROM         | 3-105 |  |

|           | AT27LV040A                                      | 512K x 8                        | 4M bit, 3-Volt EPROM         | 3-115 |  |

|           | Standard • 5V C                                 | peration                        |                              |       |  |

|           | AT27C256R                                       | 32K x 8                         | 256K EPROM                   | 3-125 |  |

|           | AT27C512R                                       | 64K x 8                         | 512K EPROM                   | 3-135 |  |

|           | AT27C516                                        | 32K x 16                        | 512K EPROM                   | 3-145 |  |

|           | AT27C010/L                                      | 128K x 8                        | 1M bit EPROM                 | 3-153 |  |

|           | AT27C1024                                       | 64K x 16                        | 1M bit EPROM                 | 3-163 |  |

|           | AT27C020                                        | 256K x 8                        | 2M bit EPROM                 | 3-171 |  |

|           | AT27C2048                                       | 128K x 16                       | 2M bit EPROM                 | 3-179 |  |

|           | AT27C040                                        | 512K x 8                        | 4M bit EPROM                 | 3-187 |  |

|           | AT27C4096                                       | 256K x 16                       | 4M bit EPROM                 | 3-195 |  |

|           | AT27C080                                        | 1M x 8                          | 8M bit EPROM                 | 3-203 |  |

|           | AT27C8192                                       | 512K x 16 /                     |                              |       |  |

|           |                                                 | 1024K x 8                       | 8M bit EPROM                 | 3-211 |  |

|           | EPROM Product C                                 | Characteristics for AT          | 27CXXX Series Parts          | 3-221 |  |

|           | EPROM Applica                                   | tion Notes                      |                              |       |  |

|           | Interfacing Atmel L                             | .V/BV EPROMs on a               | Mixed 3-Volt/5-Volt Data Bus | 3-223 |  |

|           | The Benefits of Atr                             | mel's RAPID <sup>™</sup> Progra | mming Algorithm              | 3-229 |  |

|           | Surface Mount Programming Adapter Manufacturers |                                 |                              |       |  |

|           | EPROM Programn                                  | ner Firmware Suppor             | t                            | 3-241 |  |

# AMEL

| Section 4 | CMOS Flash Memories                                 |                   |                                          |  |  |

|-----------|-----------------------------------------------------|-------------------|------------------------------------------|--|--|

|           | Battery-Voltage <sup>™</sup> •                      | 2.7V - 3.6V Opera | ition                                    |  |  |

|           | AT29BV010A                                          | 128K x 8          | 1M bit, 2.7-Volt Reprogrammable ROM 4-3  |  |  |

|           | AT29BV020                                           | 256K x 8          | 2M bit, 2.7-Volt Reprogrammable ROM 4-13 |  |  |

|           | AT29BV040A                                          | 512K x 8          | 4M bit, 2.7-Volt Reprogrammable ROM 4-23 |  |  |

|           | Low Voltage • 3.0V                                  | - 3.6V Operation  |                                          |  |  |

|           | AT29LV256                                           | 32K x 8           | 256K, 3-Volt Reprogrammable ROM 4-33     |  |  |

|           | AT29LV512                                           | 64K x 8           | 512K, 3-Volt Reprogrammable ROM 4-43     |  |  |

|           | AT29LV010A                                          | 128K x 8          | 1M bit, 3-Volt Reprogrammable ROM 4-53   |  |  |

|           | AT29LV1024                                          | 64K x 16          | 1M bit, 3-Volt Reprogrammable ROM 4-63   |  |  |

|           | AT29LV020                                           | 256K x 8          | 2M bit, 3-Volt Reprogrammable ROM 4-73   |  |  |

|           | AT29LV040A                                          | 512K x 8          | 4M bit, 3-Volt, Reprogrammable ROM 4-83  |  |  |

|           | Standard Voltage •                                  | 5V Operation      |                                          |  |  |

|           | AT29C256                                            | 32K x 8           | 256K, 5-Volt Reprogrammable ROM 4-93     |  |  |

|           | AT29C257                                            | 32K x 8           | 256K, 5-Volt Reprogrammable ROM 4-105    |  |  |

|           | AT29C512                                            | 64K x 8           | 512K, 5-Volt Reprogrammable ROM 4-117    |  |  |

|           | AT29C010A                                           | 128K x 8          | 1M bit, 5-Volt Reprogrammable ROM 4-129  |  |  |

|           | AT29C1024                                           | 64K x 16          | 1M bit, 5-Volt Reprogrammable ROM 4-141  |  |  |

|           | AT29C020                                            | 256K x 8          | 2M bit, 5-Volt Reprogrammable ROM 4-153  |  |  |

|           | AT29C040A                                           | 512K x 8          | 4M bit, 5-Volt, Reprogrammable ROM 4-165 |  |  |

|           | AT49F010                                            | 128K x 8          | 1M bit, 5-Volt, Reprogrammable ROM 4-177 |  |  |

|           | AT49F020                                            | 256K x 8          | 2M bit, 5-Volt, Reprogrammable ROM 4-187 |  |  |

|           | AT49F2048                                           | 128K x 16         | 2M bit, 5-Volt, Reprogrammable ROM 4-197 |  |  |

|           | AT49F040                                            | 512K x 8          | 4M bit, 5-Volt, Reprogrammable ROM 4-209 |  |  |

|           | AT49F4096                                           | 256K x 16         | 4M bit, 5-Volt, Reprogrammable ROM 4-219 |  |  |

|           | AT49F008                                            | 1M x 8            | 8M bit, 5-Volt, Reprogrammable ROM 4-231 |  |  |

|           | AT49F8192                                           | 512K x 16         | 8M bit, 5-Volt, Reprogrammable ROM 4-233 |  |  |

|           | Flash Memory App                                    | lication Notes    |                                          |  |  |

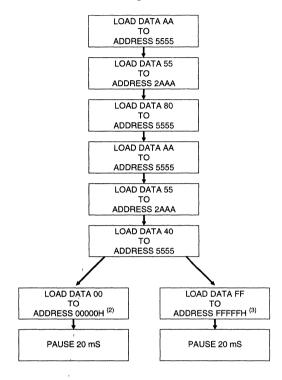

|           |                                                     |                   | 4-245                                    |  |  |

|           | Software Chip Erase (for AT29 Series Flash Family)4 |                   |                                          |  |  |

|           |                                                     |                   | 4-251                                    |  |  |

# Table of Contents

| Section 5 | FPGA Configuration Memories |                          |                                             |       |  |  |

|-----------|-----------------------------|--------------------------|---------------------------------------------|-------|--|--|

|           | AT17C65                     | 65,536 x 1               | 65K FPGA Configuration E <sup>2</sup> PROM  | 5-3   |  |  |

|           | AT17C128                    | 131,072 x 1              | 128K FPGA Configuration E <sup>2</sup> PROM |       |  |  |

|           | AT17C256                    | 262,144 x 1              |                                             |       |  |  |

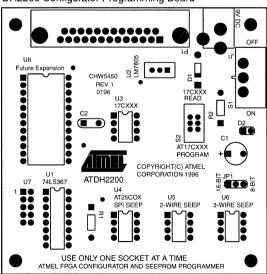

|           | Configurator Pro            |                          |                                             | 5-11  |  |  |

|           | Configurator Pro            | gramming Board           |                                             | 5-23  |  |  |

|           |                             |                          |                                             |       |  |  |

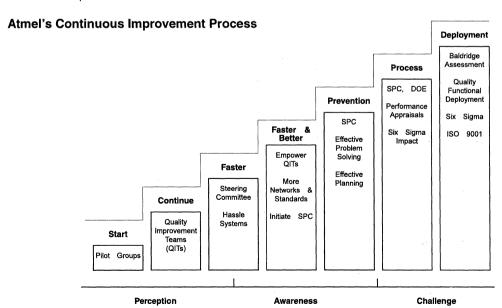

| Section 6 | Quality and Re              | -                        |                                             |       |  |  |

|           | Atmel's Policy or           | n Quality                |                                             | 6-3   |  |  |

| Section 7 | Military                    |                          |                                             |       |  |  |

| ocotion r | Military Products           | -                        | sting Overview                              |       |  |  |

|           | Standard Microc             | redit Drawing 1 roudet o | Jileting                                    | 1 - 1 |  |  |

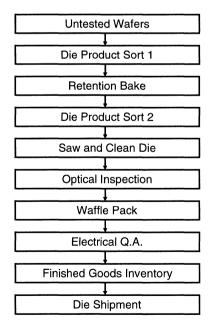

| Section 8 | Die Products                |                          |                                             |       |  |  |

|           |                             | oducts                   |                                             | 8-3   |  |  |

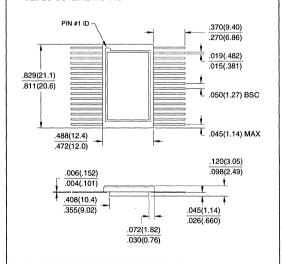

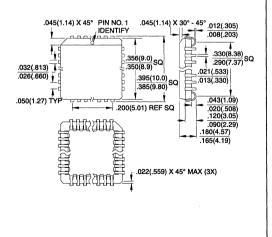

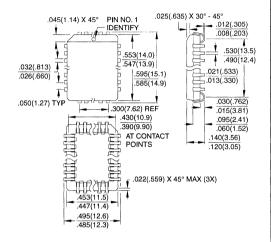

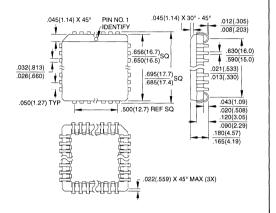

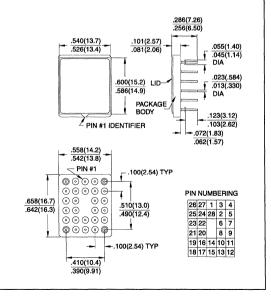

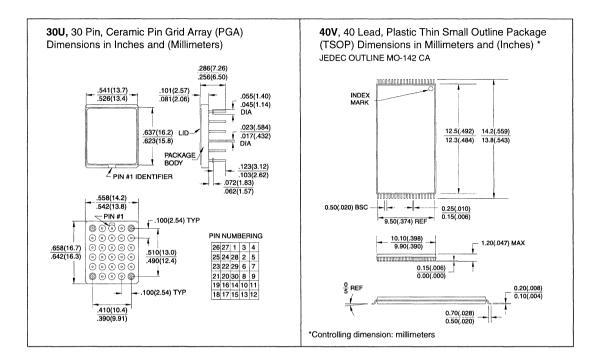

| Section 9 | Package Outli               | nes                      |                                             |       |  |  |

|           | •                           |                          |                                             | 9-3   |  |  |

|           |                             |                          | ges                                         |       |  |  |

|           |                             |                          | es                                          |       |  |  |

#### Section 10 Miscellaneous Information

| Atmel Product Line Guide             | 10-3  |

|--------------------------------------|-------|

| Atmel Sales Offices & Operations     | 10-7  |

| Atmel North American Distributors    | 10-9  |

| Atmel North American Representatives | 10-19 |

| Atmel International Representatives  | 10-23 |

| Nonvolatile Memory Product Information | on 1 |

|----------------------------------------|------|

| E <sup>2</sup> PROMS                   | 2    |

| EPROMs                                 | 3    |

| Flash Memories                         | 4    |

| FPGA Configuration Memories            | 5    |

| Quality and Reliability                | 6    |

| Military                               | 7    |

| Die Products                           | .8   |

| Package Outlines                       | 3    |

**Miscellaneous Information**

# **Contents**

1

| Section 1 | Product Selection Information                  |     |

|-----------|------------------------------------------------|-----|

|           | Nonvolatile Memory Selection Guide             | 1-3 |

|           | Ordering Information (Part Number Description) | 1-7 |

# **Nonvolatile Memory Selection Guide**

#### **EPROMs**

| Part Number                    | Organization  | Speeds     | Description                                |

|--------------------------------|---------------|------------|--------------------------------------------|

| Battery-Voltage <sup>™</sup> ( | 2.7V to 3.6V) |            |                                            |

| AT27BV256                      | 32K x 8       | 70-150 ns  | 256K bit, 2.7-Volt to 3.6-Volt             |

| AT27BV512                      | 64K x 8       | 90-150 ns  | 512K bit, 2.7-Volt to 3.6-Volt             |

| AT27BV010                      | 128K x 8      | 90-150 ns  | 1M bit, 2.7-Volt to 3.6-Volt EPROM         |

| AT27BV1024                     | 64K x 16      | 120-150 ns | 1M bit, 2.7-Volt to 3.6-Volt               |

| AT27BV020                      | 256K x 8      | 120-150 ns | 2M bit, 2.7-Volt to 3.6-Volt EPROM         |

| AT27BV4096                     | 256K x 16     | 150 ns     | 4M bit, 2.7-Volt to 3.6-Volt               |

| AT27BV040                      | 512K x 8      | 150 ns     | 4M bit, 2.7-Volt to 3.6-Volt EPROM         |

| Low Voltage (3.0 to 3          | 3.6V)         |            |                                            |

| AT27LV256A                     | 32K x 8       | 70-150 ns  | 256K bit, 3-Volt EPROM                     |

| AT27LV512A                     | 64K x 8       | 90-150 ns  | 512K bit, 3-Volt EPROM                     |

| AT27LV010A                     | 128K x 8      | 90-150 ns  | 1M bit, 3-Volt EPROM                       |

| AT27LV020A                     | 256K x 8      | 120-150 ns | 2M bit, 3-Volt EPROM                       |

| AT27LV040A                     | 512K x 8      | 150 ns     | 4M bit, 3-Volt EPROM                       |

| Standard Voltage (5\           | <i>'</i> )    |            |                                            |

| AT27C256R                      | 32K x 8       | 45-150 ns  | 256K, 5-Volt EPROM                         |

| AT27C512R                      | 64K x 8       | 45-150 ns  | 512K, 5-Volt EPROM                         |

| AT27C516                       | 32K x 16      | 45-150 ns  | 512K, 5-Volt EPROM                         |

| AT27C1024                      | 64K x 16      | 45-150 ns  | 1M bit, 5-Volt EPROM                       |

| AT27C010,L                     | 128K x 8      | 45-150 ns  | 1M bit, 5-Volt EPROM, Standard & Low Power |

| AT27C2048                      | 128K x 16     | 70-150 ns  | 2M bit, 5-Volt EPROM                       |

| AT27C020                       | 256K x 8      | 85-150 ns  | 2M bit, 5-Volt EPROM                       |

| AT27C4096                      | 256K x 16     | 85-150 ns  | 4M bit, 5-Volt EPROM                       |

| AT27C040                       | 512K x 8      | 80-150 ns  | 4M bit, 5-Volt EPROM                       |

| AT27C080                       | 1024K x 8     | 100-150 ns | 8M bit, 5-Volt EPROM                       |

| AT27C8192                      | 512K x 16     | 100-150 ns | 8M bit, 5-Volt EPROM                       |

#### Flash Memory

| Part Number                  | Organization   | Speeds     | Description                                    |

|------------------------------|----------------|------------|------------------------------------------------|

| Battery-Voltage <sup>™</sup> | (2.7V to 3.6V) |            |                                                |

| AT29BV010A                   | 128K x 8       | 200-350 ns | 1M bit, 2.7-Volt Read and 2.7-Volt Write Flash |

| AT29BV020                    | 256K x 8       | 250-350 ns | 2M bit, 2.7-Volt Read and 2.7-Volt Write Flash |

| AT29BV040A                   | 512K x 8       | 250-350 ns | 4M bit, 2.7-Volt Read and 2.7-Volt Write Flash |

| Low Voltage (3V to           | 3.6V)          |            |                                                |

| AT29LV256                    | 32K x 8        | 150-250 ns | 256K, 3-Volt Read and 3-Volt Write Flash       |

| AT29LV512                    | 64K x 8        | 150-250 ns | 512K, 3-Volt Read and 3-Volt Write Flash       |

| AT29LV010A                   | 128K x 8       | 150-250 ns | 1M bit, 3-Volt Read and 3-Volt Write Flash     |

| AT29LV1024                   | 64K x 16       | 150-250 ns | 1M bit, 3-Volt Read and 3-Volt Write Flash     |

| AT29LV020                    | 256K x 8       | 200-250 ns | 2M bit, 3-Volt Read and 3-Volt Write Flash     |

| AT29LV040A                   | 512K x 8       | 200-250 ns | 4M bit, 3-Volt Read and 3-Volt Write Flash     |

| Standard Voltage (           | 5V)            |            |                                                |

| AT29C256                     | 32K x 8        | 70-250 ns  | 256K, 5-Volt Read and 5-Volt Write Flash       |

| AT29C257                     | 32K x 8        | 70-250 ns  | 256K, 5-Volt Read and 5-Volt Write Flash       |

| AT29C512                     | 64K x 8        | 70-200 ns  | 512K, 5-Volt Read and 5-Volt Write Flash       |

| AT29C1024                    | 64K x 16       | 70-200 ns  | 1M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT29C010A                    | 128K x 8       | 70-200 ns  | 1M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT29C020                     | 256K x 8       | 90-200 ns  | 2M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT29C040A                    | 512K x 8       | 120-250 ns | 4M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT49F010                     | 128K x 8       | 70-200 ns  | 1M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT49F020                     | 256K x 8       | 90-200 ns  | 2M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT49F2048                    | 128K x 16      | 90-200 ns  | 2M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT49F040                     | 512K x 8       | 120-250 ns | 4M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT49F4096                    | 256K x 16      | 90-200 ns  | 4M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT49F008                     | 1M x 8         | 120-200 ns | 8M bit, 5-Volt Read and 5-Volt Write Flash     |

| AT49F8192                    | 512K x 16      | 120-200 ns | 8M bit, 5-Volt Read and 5-Volt Write Flash     |

# FPGA Serial Configuration E<sup>2</sup>PROM

| Part Number                     | Memory Size |                                                                                                                                          | Description |  |

|---------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| AT17C65<br>AT17C128<br>AT17C256 | 131,072 x 1 | 65K FPGA Configuration E <sup>2</sup> PROM<br>128K FPGA Configuration E <sup>2</sup> PROM<br>256K FPGA Configuration E <sup>2</sup> PROM |             |  |

# **Nonvolatile Memory Selection Guide**

# Parallel E<sup>2</sup>PROMs

| Part Number      | Organization                 | Speeds      | Description                                                                                   |

|------------------|------------------------------|-------------|-----------------------------------------------------------------------------------------------|

| High Speed       |                              |             |                                                                                               |

| AT28HC64B        | 8K x 8                       | 55-120 ns   | 64K E <sup>2</sup> PROM with 64-Byte Page & Software Data Protection                          |

| AT28HC256        | 32K x 8                      | 70-120 ns   | 256K E <sup>2</sup> PROM with 64-Byte Page & Software Data Protection                         |

| AT28HC256E       | 32K x 8                      | 70-120 ns   | 256K E <sup>2</sup> PROM with Extended Endurance, Standard & Low Power                        |

| Battery-Voltage  | <sup>TM</sup> (2.7V to 3.6V) | <del></del> |                                                                                               |

| AT28BV16         | 2K x 8                       | 250-300 ns  | 16K E <sup>2</sup> PROM, 2.7-Volt                                                             |

| AT28BV64         | 8K x 8                       | 300 ns      | 64K E <sup>2</sup> PROM, 2.7-Volt                                                             |

| Low Voltage (3.0 | V to 3.6V)                   |             |                                                                                               |

| AT28LV64B        | 8K x 8                       | 200-300 ns  | 64K E <sup>2</sup> PROM with 64-Byte Page & Software Data Protection, 3.0-Volt                |

| AT28LV256        | 32K x 8                      | 200-300 ns  | 256K E <sup>2</sup> PROM with 64-Byte Page & Software Data Protection, 3.0-Volt               |

| AT28LV010        | 128K x 8                     | 200-250 ns  | 1M bit E <sup>2</sup> PROM with 128-Byte Page & Software Data Protection, 3.0-Volt            |

| Standard Voltage | e (5V)                       |             |                                                                                               |

| AT28C16          | 2K x 8                       | 150-250 ns  | 16K E <sup>2</sup> PROM                                                                       |

| AT28C16E         | 2K x 8                       | 150-250 ns  | 16K E <sup>2</sup> PROM with Extended Endurance & Fast Write                                  |

| AT28C17          | 2K x 8                       | 150-250 ns  | 16K E <sup>2</sup> PROM with Ready/Busy                                                       |

| AT28C17E         | 2K x 8                       | 150-250 ns  | 16K E <sup>2</sup> PROM with Ready/Busy & Extended Endurance & Fast Write                     |

| AT28C64          | 8K x 8                       | 120-350 ns  | 64K E <sup>2</sup> PROM                                                                       |

| AT28C64E         | 8K x 8                       | 120-350 ns  | 64K E <sup>2</sup> PROM with Extended Endurance & Fast Write                                  |

| AT28C64X         | 8K x 8                       | 150-450 ns  | 64K E <sup>2</sup> PROM without Ready-Busy                                                    |

| AT28C64B         | 8K x 8                       | 150-250 ns  | 64K E <sup>2</sup> PROM with 64-Byte Page & Software Data Protection                          |

| AT28C256         | 32K x 8                      | 150-350 ns  | 256K E <sup>2</sup> PROM with 64-Byte Page & Software Data Protection                         |

| AT28C256E        | 32K x 8                      | 150-350 ns  | 256K E <sup>2</sup> PROM with Extended Endurance                                              |

| AT28C010         | 128K x 8                     | 120-250 ns  | 1M bit E <sup>2</sup> PROM with 128-Byte Page & Software Data Protection                      |

| AT28C010E        | 128K x 8                     | 120-250 ns  | 1M bit E <sup>2</sup> PROM with 128-Byte Page & Extended Endurance & Software Data Protection |

| AT28C040         | 512K x 8                     | 150-250 ns  | 4M bit E <sup>2</sup> PROM with 256-Byte Page & Software Data Protection                      |

#### Serial E<sup>2</sup>PROMs

| Part Number | Organization       | Vcc                  | Description                                                                 |

|-------------|--------------------|----------------------|-----------------------------------------------------------------------------|

|             | O Gamea III        |                      | _                                                                           |

| AT24C01     | 128 x 8            | 1.8, 2.5, 2.7, 5.0 V | 1K, 2-Wire Bus Serial E <sup>2</sup> PROM, Non-Cascadable                   |

| AT24C21     | 128 x 8            | 2.5 V                | 1K, 2-Wire Bus Serial E <sup>2</sup> PROM, Dual Mode, Plug & Play Operation |

| AT24C01A    | 128 x 8            | 1.8, 2.5, 2.7, 5.0 V | 1K, 2-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT24C02     | 256 x 8            | 1.8, 2.5, 2.7, 5.0 V | 2K, 2-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT24C04     | 512 x 8            | 1.8, 2.5, 2.7, 5.0 V | 4K, 2-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT24C08     | 1024 x 8           | 1.8, 2.5, 2.7, 5.0 V | 8K, 2-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT24C16     | 2048 x 8           | 1.8, 2.5, 2.7, 5.0 V | 16K, 2-Wire Bus Serial E <sup>2</sup> PROM                                  |

| AT24C164    | 2048 x 8           | 1.8, 2.5, 2.7, 5.0 V | 16K, 2-Wire Bus Serial E <sup>2</sup> PROM with Cascadable Feature          |

| AT24C32     | 4096 x 8           | 1.8, 2.5, 2.7, 5.0 V | 32K, 2-Wire Bus Serial E <sup>2</sup> PROM with Cascadable Feature          |

| AT24C64     | 8192 x 8           | 1.8, 2.5, 2.7, 5.0 V | 64K, 2-Wire Bus Serial E <sup>2</sup> PROM with Cascadable Feature          |

| AT25010     | 128 x 8            | 1.8, 2.7, 5.0 V      | 1K, SPI Bus Serial E <sup>2</sup> PROM, Supports SPI Mode 0 and 3           |

| AT25020     | 256 x 8            | 1.8, 2.7, 5.0 V      | 2K, SPI Bus Serial E <sup>2</sup> PROM, Supports SPI Mode 0 and 3           |

| AT25040     | 512 x 8            | 1.8, 2.7, 5.0 V      | 4K, SPI Bus Serial E <sup>2</sup> PROM, Supports SPI Mode 0 and 3           |

| AT25320     | 4096 x 8           | 1.8, 2.7, 5.0 V      | 32K, SPI Bus Serial E <sup>2</sup> PROM, Supports SPI Mode 0 and 3          |

| AT25640     | 8192 x 8           | 1.8, 2.7, 5.0 V      | 64K, SPI Bus Serial E <sup>2</sup> PROM, Supports SPI Mode 0 and 3          |

| AT93C46     | 64 x 16 / 128 x 8  | 1.8, 2.5, 2.7, 5.0 V | 1K, 3-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT93C46A    | 64 x 16            | 1.8, 2.5, 2.7, 5.0 V | 1K, 3-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT93C56     | 128 x 16 / 256 x 8 | 2.5, 2.7, 5.0 V      | 2K, 3-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT93C57     | 128 x 16 / 256 x 8 | 2.5, 2.7, 5.0 V      | 2K, 3-Wire Bus Serial E <sup>2</sup> PROM with Special Address              |

| AT93C66     | 256 x 16 / 512 x 8 | 2.5, 2.7, 5.0 V      | 4K, 3-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT59C11     | 64 x 16 / 128 x 8  | 2.5, 2.7, 5.0 V      | 1K, 4-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT59C22     | 128 x 16 / 256 x 8 | 2.5, 2.7, 5.0 V      | 2K, 4-Wire Bus Serial E <sup>2</sup> PROM                                   |

| AT59C13     | 256 x 16 / 512 x 8 | 2.5, 2.7, 5.0 V      | 4K, 4-Wire Bus Serial E <sup>2</sup> PROM                                   |

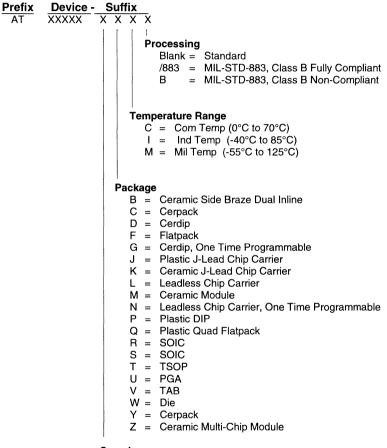

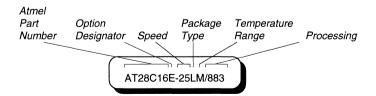

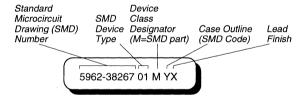

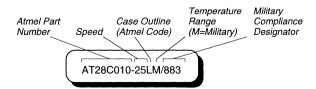

#### **Explanation of Atmel's Part Number Code**

All Atmel part numbers begin with the prefix "AT." The next four to nine digits are the part number. In addition, Atmel parts can be ordered in particular speeds, in specific packages, for particular temperature ranges and with the option of 883C level B military compliance. The available options

for each part are listed at the back of its data sheet in its "Ordering Information" table. These options are designated by the following suffixes placed at the end of the Atmel part number, in the order given:

#### Speed

Here is an example Atmel part number:

0538A

Ordering =

# **Nonvolatile Memory Product Information**

E<sup>2</sup>PROMS

OMS 2014-11-1-year - That was the compression of the second of the second of the second of the second of the second

**EPROMs**

**Flash Memories**

**FPGA Configuration Memories**

**Quality and Reliability**

**Military**

**Die Products**

**Package Outlines**

Miscellaneous Information

**AIMEL**

2

10

| Section 2 | CMOS E <sup>2</sup> PROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                                    |         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------|---------|

|           | Serial E <sup>2</sup> PROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                                                    |         |

|           | AT24C01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 128 x 8            | 2-Wire, 1K Serial E <sup>2</sup> PROM              | . 2-3   |

|           | AT24C21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 128 x 8            | 2-Wire, 1K Serial E <sup>2</sup> PROM              | . 2-13  |

|           | AT24C01A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 128 x 8            | 2-Wire, 1K Serial E <sup>2</sup> PROM              | . 2-25  |

|           | AT24C02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 256 x 8            | 2-Wire, 2K Serial E <sup>2</sup> PROM              | . 2-25  |

|           | AT24C04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 512 x 8            | 2-Wire, 4K Serial E <sup>2</sup> PROM              | . 2-25  |

|           | AT24C08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1024 x 8           | 2-Wire, 8K Serial E <sup>2</sup> PROM              | . 2-25  |

|           | AT24C16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2048 x 8           | 2-Wire, 16K Serial E <sup>2</sup> PROM             | . 2-25  |

|           | AT24C164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2048 x 8           | 2-Wire, 16K Serial E <sup>2</sup> PROM             | . 2-39  |

|           | AT24C32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4096 x 8           | 2-Wire, 32K Serial E <sup>2</sup> PROM             |         |

|           | AT24C64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8192 x 8           | 2-Wire, 64K Serial E <sup>2</sup> PROM             |         |

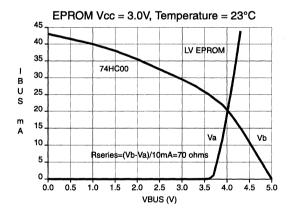

|           | AT93C46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 x 16 / 128 x 8  | 3-Wire, 1K Serial E <sup>2</sup> PROM              |         |