# **HIGH SPEED DESIGN SEMINAR**

INDEX

2

3

4

5

6

8

9

10

HIGH SPEED A/D CONVERSION

**DIGITAL VIDEO APPLICATIONS**

HIGH SPEED SAMPLE AND HOLD AMPLIFIERS

HIGH SPEED OP AMPS

HIGH SPEED NON-LINEAR SIGNAL PROCESSORS: MULTIPLIERS, MODULATORS AND LOG AMPS

> TIME DOMAIN FUNCTIONS: COMPARATORS AND PIN ELECTRONICS

> > TIME DOMAIN FUNCTIONS: TIME DELAY GENERATORS

FREQUENCY DOMAIN FUNCTIONS: PHASE LOCKED LOOPS

FREQUENCY DOMAIN FUNCTIONS: D/A CONVERSION AND DIRECT DIGITAL SYNTHESIS

**COMPUTER GRAPHICS AND RAM-DACs**

**HIGH SPEED TECHNIQUES**

# HIGH SPEED DESIGN SEMINAR

#### ACKNOWLEDGEMENTS

Thanks are due to the technical staff members of Analog Devices in Engineering and Marketing who provided invaluable inputs during the preparation of this seminar. A special note of thanks goes to Linda Grimes Brandon of Brandon's WordService for layout, typesetting, and preparation of most of the illustrations.

#### DEDICATION

This seminar is respectfully dedicated to the memory of the late Edward L. Graves, whose long range vision and insights regarding future trends in high-speed data acquisition technology have stood the test of time.

> Walt Kester Greensboro, NC 1990

#### Copyright © 1989 and 1990 by Analog Devices, Inc. Printed in the United States of America

All rights reserved. This book, or parts thereof, must not be reproduced in any form without permission of the copyright owner.

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices, Inc., for its use.

Analog Devices, Inc., makes no representation that the interconnections of its circuits as described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith.

Specifications are subject to change without notice.

# **Worldwide Service Directory**

# North America

Alabama (205) 536-1506

Alaska \*(206) 575-6344 \*(714) 641-9391 Arizona (602) 949-0048

\*(719) 590-9952

Arkansas \*(214) 231-5094

California \*(714) 641-9391 \*(408) 559-2037 \*(619) 268-4621

Colorado (303) 443-5337 \*(719) 590-9952

Connecticut (516) 673-1900 \*(617) 329-4700

**Delaware** \*(215) 643-7790

Florida (407) 855-0843 (407) 724-6795

(813) 963-1076 Georgia

(404) 497-9404

Hawaii \*(714) 641-9391 Idaho (303) 443-5337

\*(719) 590-9952 \*(206) 575-6344 Illinois

(708) 520-0710

Indiana (317) 244-7867 Iowa

(319) 373-0200

Kansas (913) 829-2800

Kentucky (615) 459-0743

\*(617) 329-4700 Louisiana \*(214) 231-5094

Maine

\*(617) 329-4700 Maryland \*(301) 992-1994

Massachusetts \*(617) 329-4700 Michigan

(313) 489-1500

New York (516) 673-1900 (716) 425-4101

Minnesota

Mississippi

Missouri

Montana

Nebraska

Nevada

(612) 835-2414

(205) 536-1506

(314) 521-2044

(913) 829-2800

(801) 466-9336

\*(714) 641-9391

(913) 829-2800

(505) 828-1300

\*(408) 559-2037

\*(714) 641-9391

**New Hampshire**

\*(617) 329-4700

(516) 673-1900

\*(617) 329-4700

\*(215) 643-7790

(505) 828-1300

\*(719) 590-9952

**New Mexico**

**New Jersey**

North Carolina (919) 373-0380 (704) 846-1702

North Dakota (612) 835-2414

Ohio (216) 248-4995 \*(614) 764-8795

Oklahoma \*(214) 231-5094

Oregon \*(206) 575-6344

Pennsylvania \*(215) 643-7790 (412) 745-8441

Rhode Island \*(617) 329-4700

South Carolina (919) 373-0380

South Dakota (612) 835-2414

Tennessee (205) 536-1506 (615) 459-0743

**Texas** \*(214) 231-5094

Utah (801) 466-9336

\*(719) 590-9952

Vermont \*(617) 329-4700

Virginia \*(301) 992-1994

Washington \*(206) 575-6344

West Virginia \*(614) 764-8795

Wisconsin (414) 784-7736

Wyoming (801) 466-9336

Puerto Rico \*(617) 329-4700

#### Canada

(416) 821-7800 (613) 729-0023 (514) 697-0804 (604) 941-7707

Mexico

\*(617) 329-4700

\*Analog Devices, Inc. Direct Sales Offices

#### WORLDWIDE HEADQUARTERS

One Technology Way, P.O. Box 9106, Norwood, Massachusetts 02062-9106 U.S.A. Tel: (617) 329-4700, TWX: (710) 394-6577, FAX: (617) 326-8703, Telex: 924491 Cable: ANALOG NORWOODMASS

# **Worldwide Service Directory**

# International

Australia

(02) 4178777 (613) 5931033

Austria \*(222) 885504-0

Belgium \*(3) 2371672

Brazil (11) 531-9355

Denmark \*(42) 845800

Finland (0) 8041041

France \*(1) 46662525 \*(76) 222190

\*(61) 408562 \*(99) 834666 Holland

\*(1620) 81500

Hong Kong (5) 8339013 India (212) 333880 (11) 6862460 (812) 560506

Ireland \*(932) 253320 (United Kingdom Sales)

Israel \*(52) 911415 \*(52) 913551

#### italy

\*(2) 6140977 \*(6) 8393405 \*(11) 6504572 (2) 9520551 (51) 555614 (49) 633600 (6) 390083 (11) 599224

Japan \*(3) 2636826 \*(6) 3721814

Korea (2) 554-3301

Malaysia (65) 2848537 Mexico (83) 351721 (83) 351661

New Zealand (9) 592629

Norway (3) 847099

People's Republic of China – Beijing (1) 890721, Ext. 120

Romania \*(222) 885504-0 (Austria)

Singapore (65) 2848537

South Africa (11) 882-1620

Spain (1) 7543001 (3) 3007712

Sweden \*(8) 282740

Switzerland \*(22) 7315760 \*(1) 8200102 Taiwan (2) 501-8170

Turkey (1) 3372245

United Kingdom \*(932) 232222 \*(932) 253320 (Sales) \*(1) 9411066 \*(635) 35335 \*(506) 30306 \*(21) 5011166 \*(279) 418611

United States of America \*(617) 329-4700

(017) 323-4700

West Germany \*(89) 570050

\*(4181) 8051

\*(721) 48567

\*(30) 316441

\*(221) 686006

Yugoslavia \*(222) 885504-0 (Austria)

\*Analog Devices, Inc. Direct Sales Offices

#### WORLDWIDE HEADQUARTERS

One Technology Way, P.O. Box 9106, Norwood, Massachusetts 02062-9106 U.S.A. Tel: (617) 329-4700, TWX: (710) 394-6577, FAX: (617) 326-8703, Telex: 924491 Cable: ANALOG NORWOODMASS

# **HIGH SPEED DESIGN SEMINAR**

INDEX

**1**

2

3

4

5

6

8

9

10

HIGH SPEED A/D CONVERSION

**DIGITAL VIDEO APPLICATIONS**

HIGH SPEED SAMPLE AND HOLD AMPLIFIERS

HIGH SPEED OP AMPS

HIGH SPEED NON-LINEAR SIGNAL PROCESSORS: MULTIPLIERS, MODULATORS AND LOG AMPS

> TIME DOMAIN FUNCTIONS: COMPARATORS AND PIN ELECTRONICS

> > TIME DOMAIN FUNCTIONS: TIME DELAY GENERATORS

FREQUENCY DOMAIN FUNCTIONS: PHASE LOCKED LOOPS

FREQUENCY DOMAIN FUNCTIONS: D/A CONVERSION AND DIRECT DIGITAL SYNTHESIS

**COMPUTER GRAPHICS AND RAM-DACs**

HIGH SPEED TECHNIQUES

# ANALOG DEVICES HIGH SPEED SEMINAR

## SECTION I HIGH SPEED A/D CONVERSION

#### High Speed A/D Converter Architectures:

Flash, Successive Approximation, Subranging, Digitally Corrected Subranging

#### A/D Converter Applications:

Undersampling (Super-Nyquist), Oversampling, Dithering, Multiplexing

#### A/D Converter Dynamic Specifications and Testing:

DSP Testing, Quantization Theory, DFTs and FFTs, Signal to Noise Ratio, Effective Bits, Harmonic Distortion, Two-Tone Intermodulation Distortion, Spurious Free Dynamic Range, Coherent Sampling, Non-Coherent Sampling, Windowing, Sinewave Curve Fit, Beat Frequency Tests, Histogram Tests, Noise Power Ratio, Transient Response, Overvoltage Recovery, Aperture Time, Composite Video Tests, Error Rates

i

#### References

Technical Article: Multistage Error Correcting A/D Converters

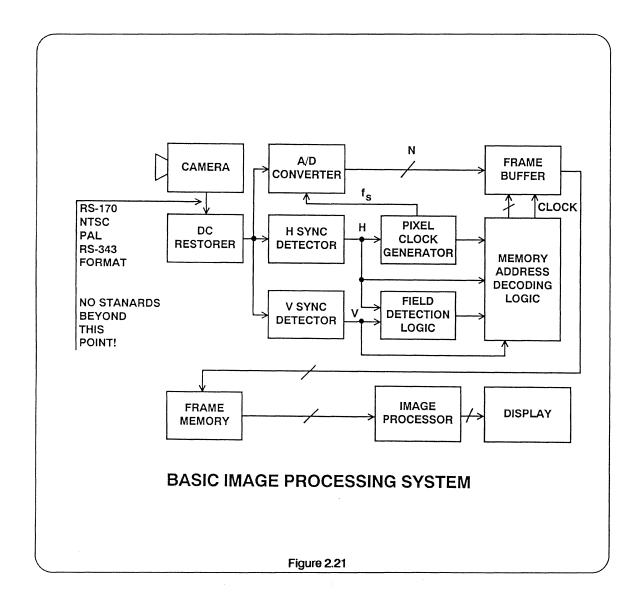

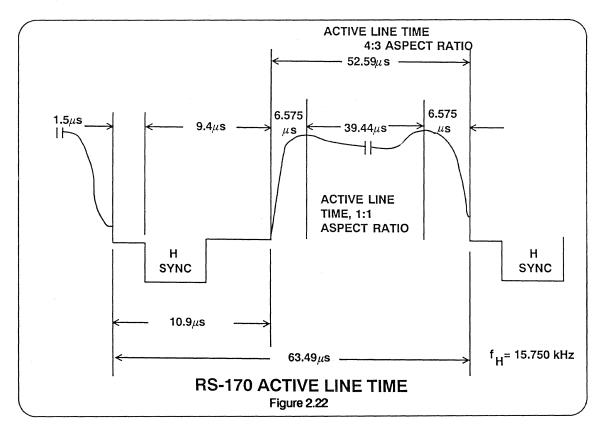

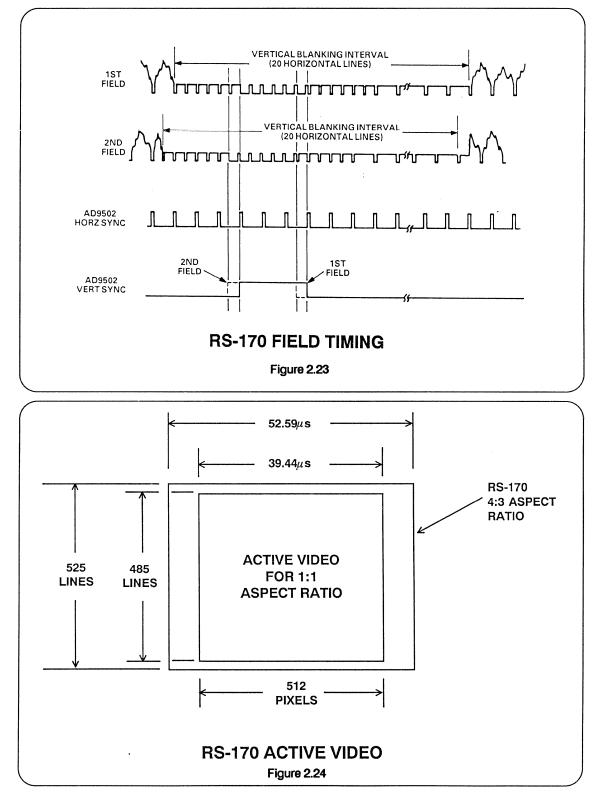

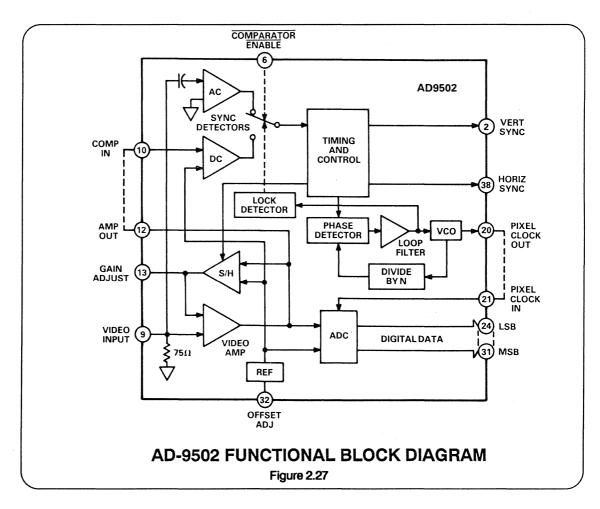

#### SECTION II DIGITAL VIDEO APPLICATIONS

**Broadcast Video Digitization**

**High Definition TV**

Multiplexing and Switching Video Signals

**Electronic Image Processing**

# SECTION III SAMPLE AND HOLD AMPLIFIERS

Sample and Holds/Track and Holds **Basic SHA Operation Track Mode Specifications Track to Hold Transition Specifications** Hold Mode Specifications Hold to Track Transition Specifications High Speed Open Loop SHAs **Closed Loop SHAs** SHA Applications **Driving Flash Converters with High Speed SHAs**

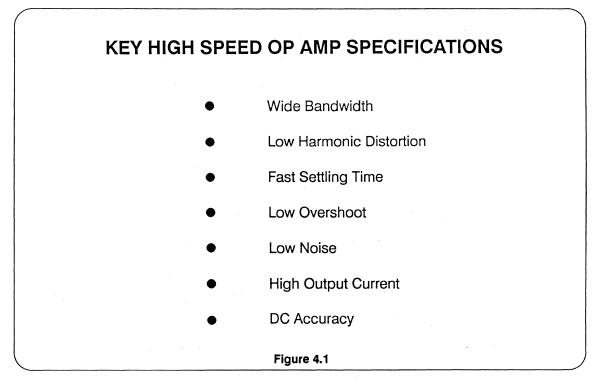

#### SECTION IV **HIGH SPEED OP AMPS**

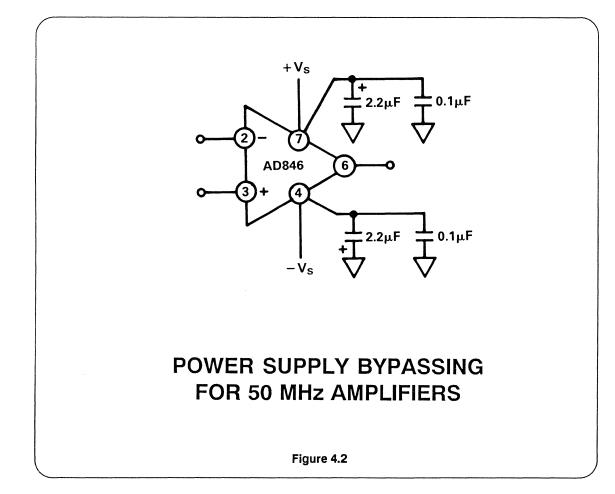

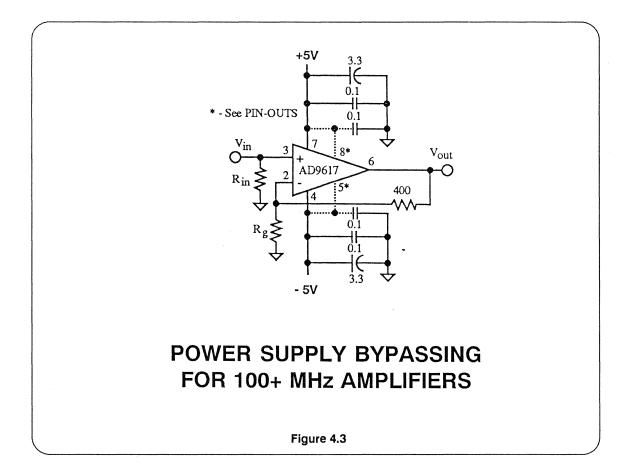

#### **High Speed Op Amp Characteristics**

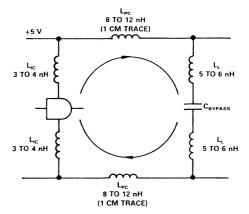

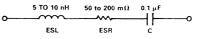

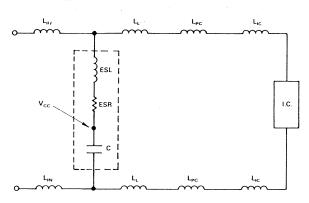

#### Grounding and Bypassing

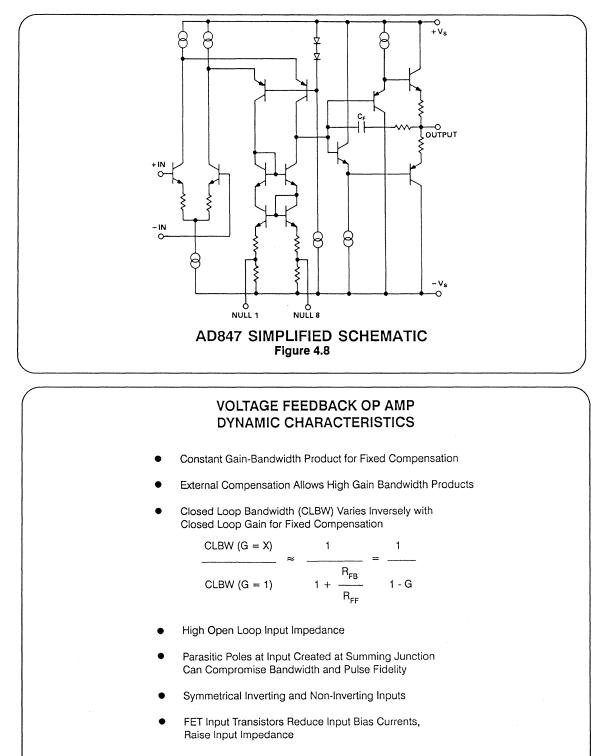

High Speed Voltage Feedback Op Amps: The AD847 Voltage Feedback Op Amp

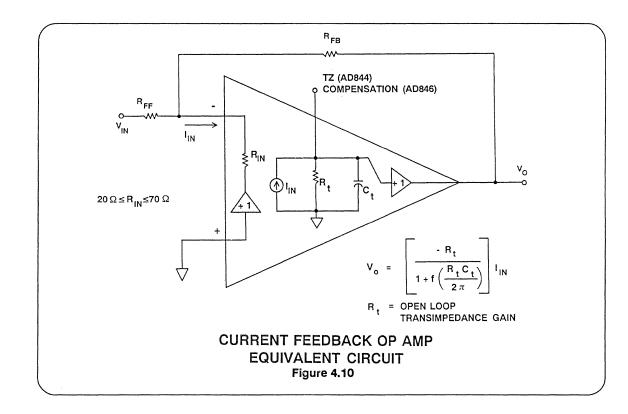

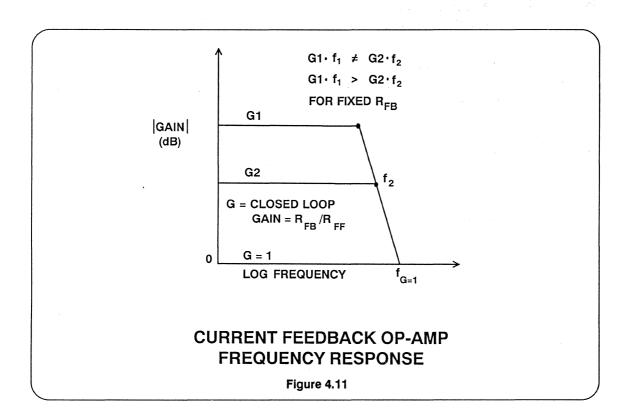

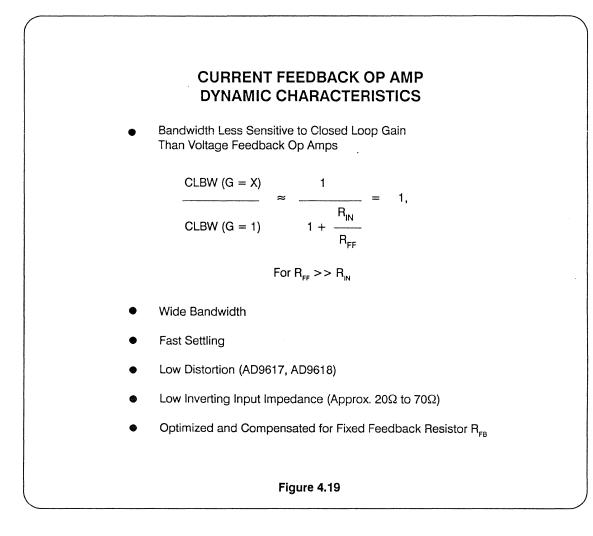

#### High Speed Current Feedback Op Amps:

Effects of Feedback Resistor on Bandwidth, Compensating for Peaking in the Non-Inverting Mode

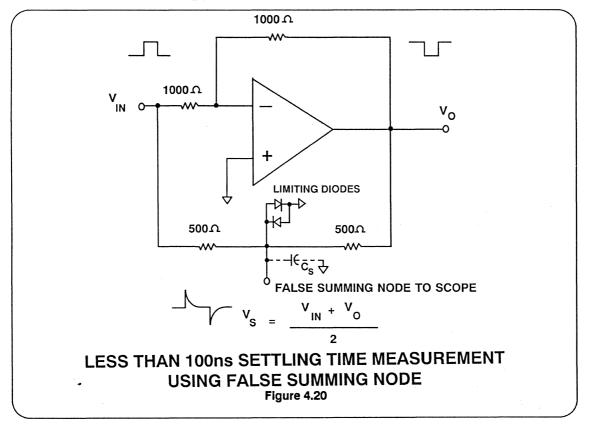

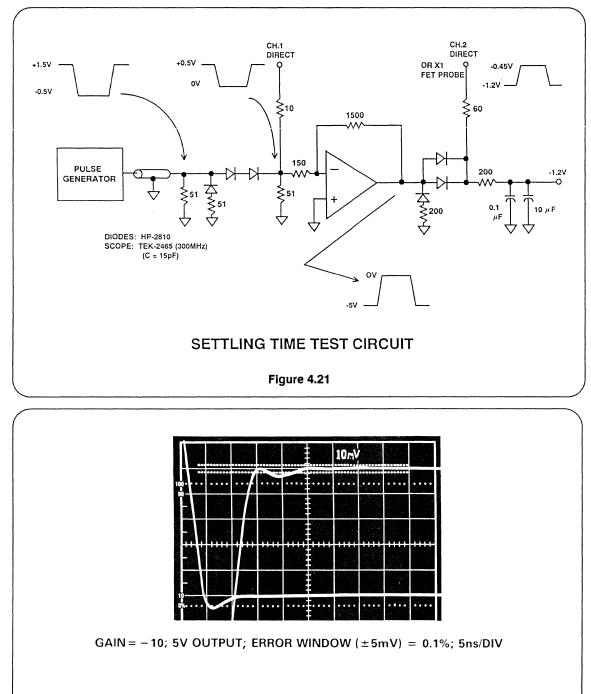

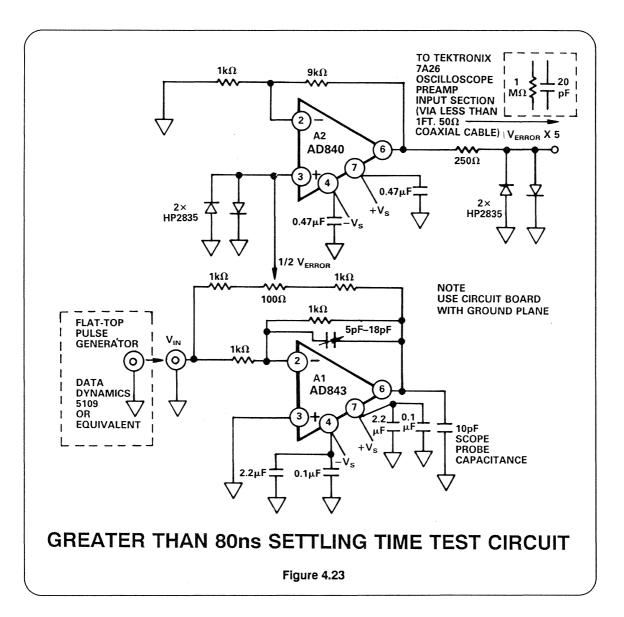

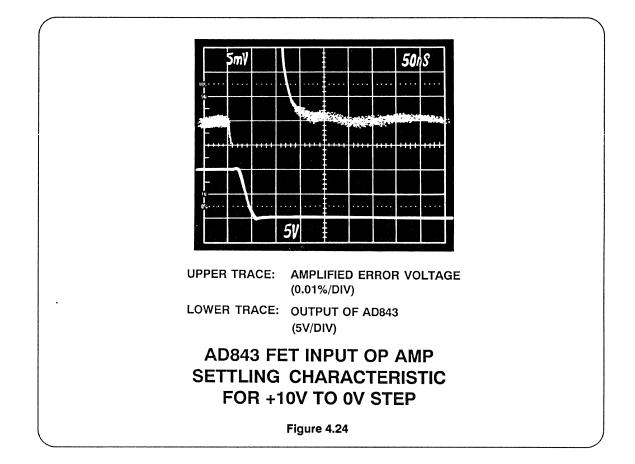

#### Settling Time Characteristics of High Speed Amplifiers

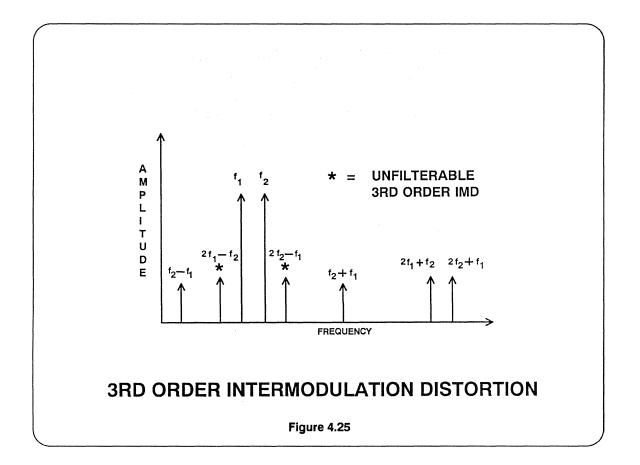

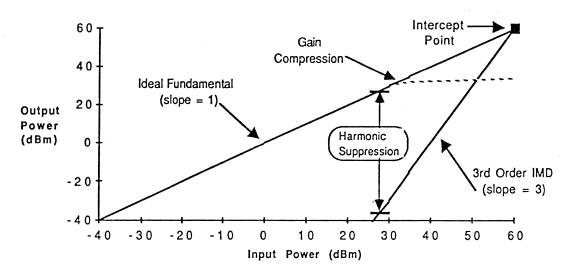

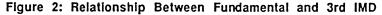

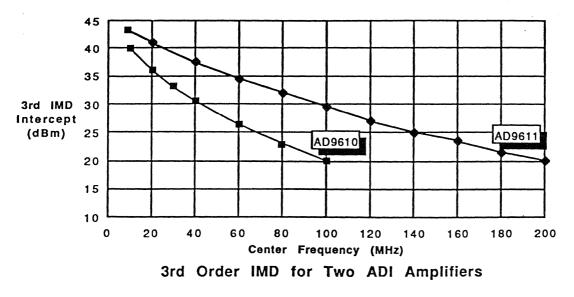

Intermodulation Distortion (IMD)

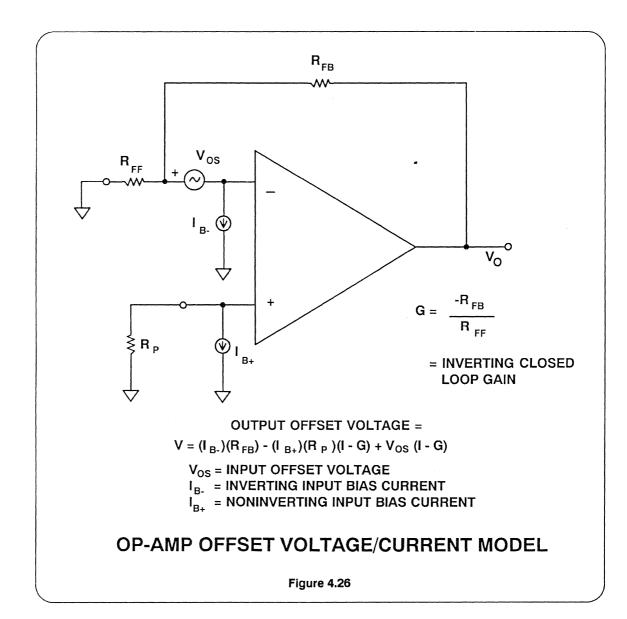

#### **Op Amp Bias Current and Offset Voltage Model**

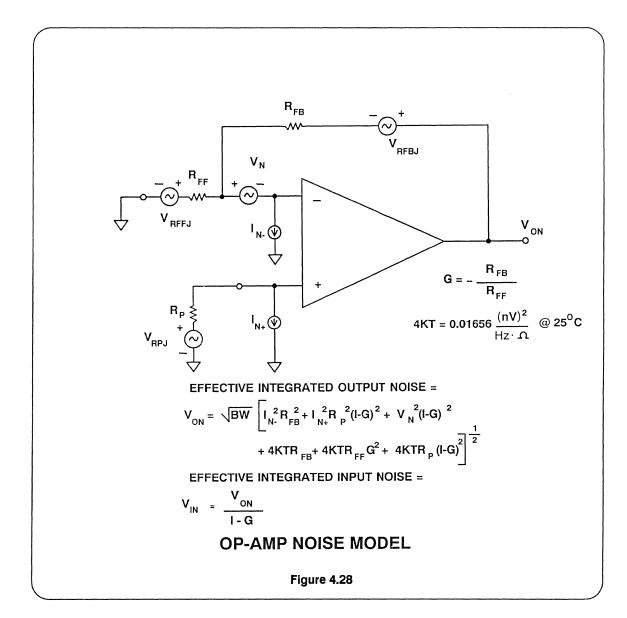

#### **Op Amp Noise Model**

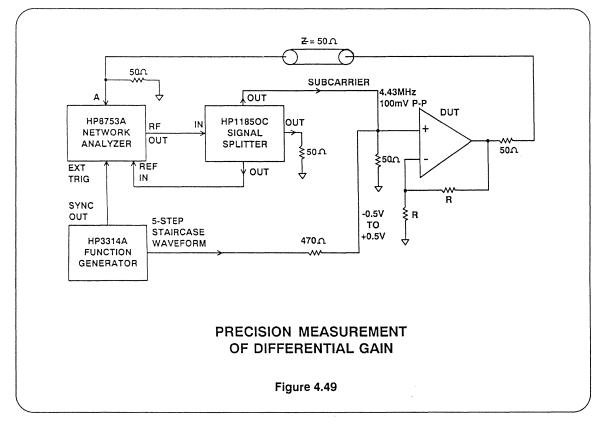

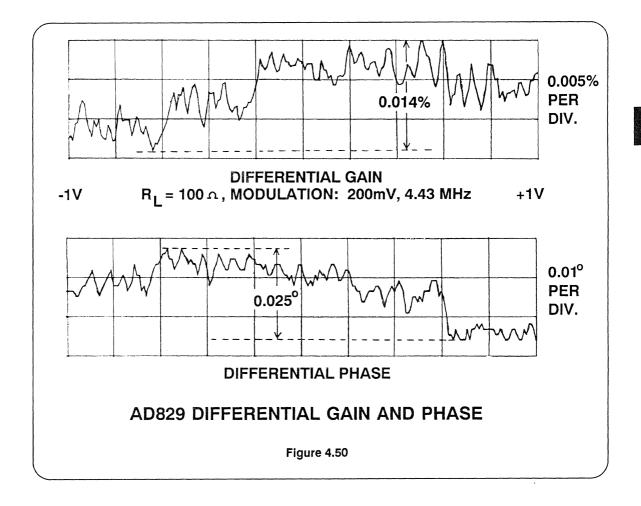

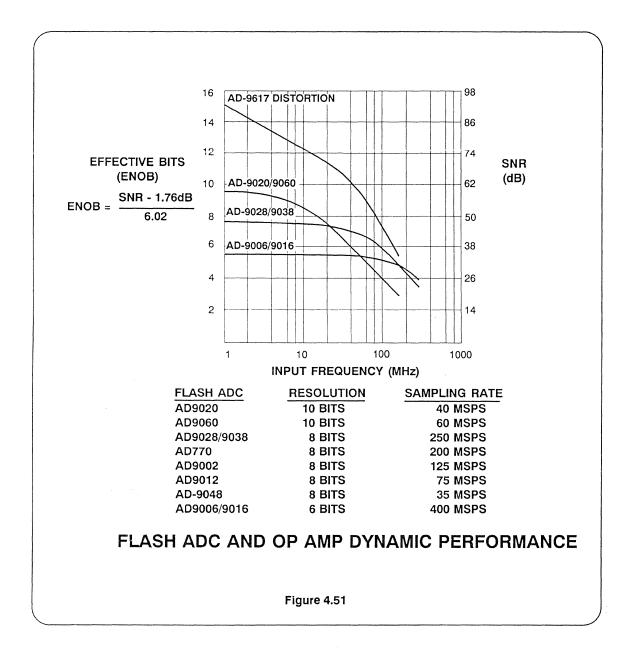

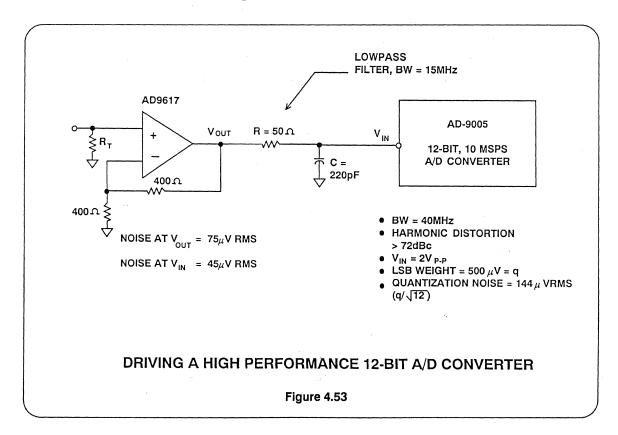

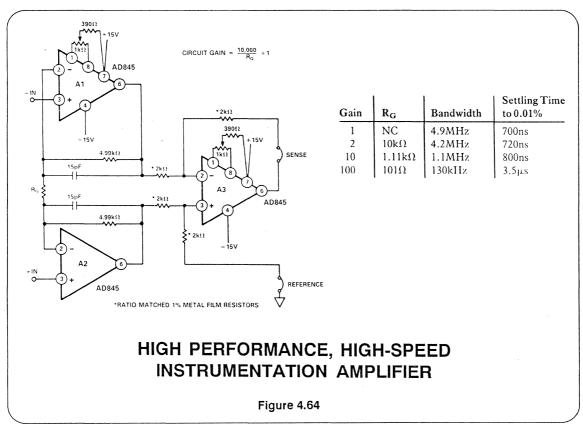

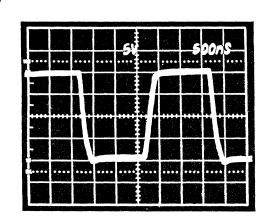

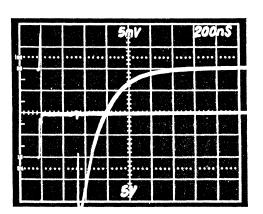

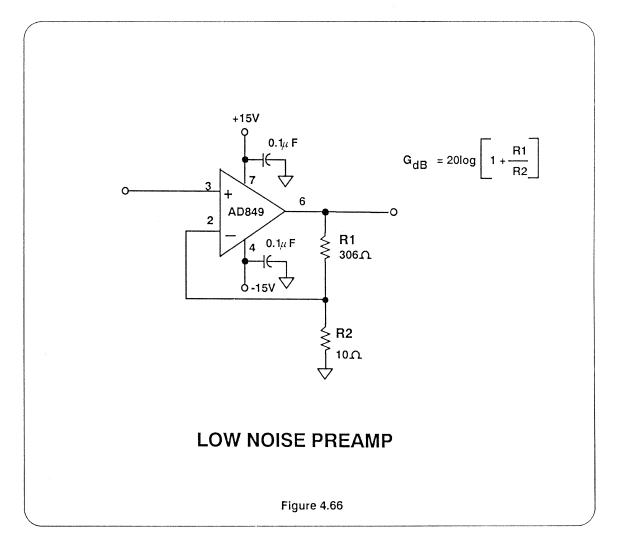

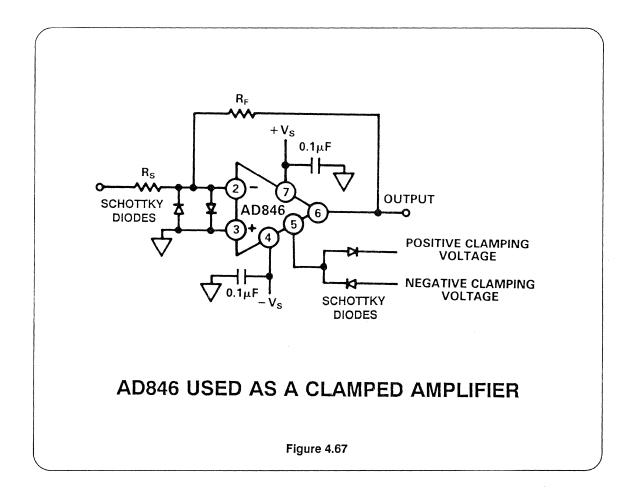

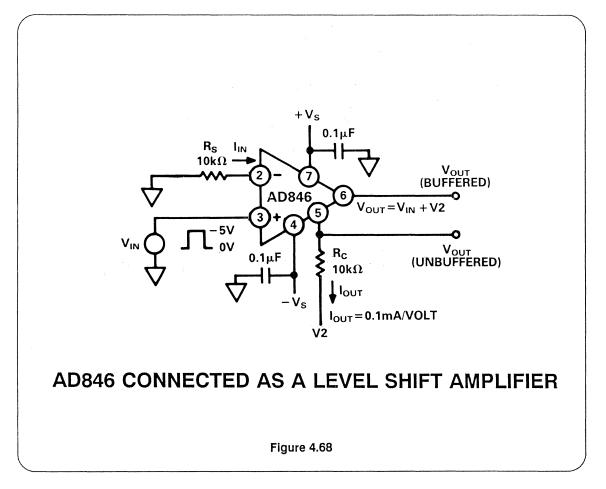

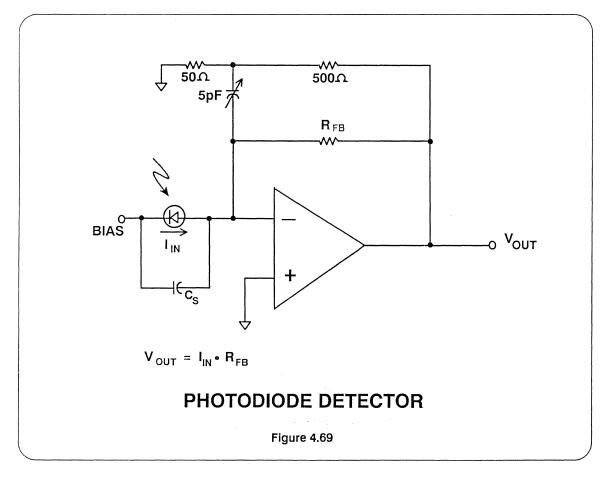

High Speed Op Amp Applications Stabilizing High Gain Op Amps at Lower Gain, Driving Capacitive Loads, High Speed Cable Drivers and Receivers, Low Differential Gain and Phase Video Line Driver, Precision Measurement of Differential Gain and Phase, Driving A/D Converters, Driving High Performance 12-Bit A/D Converters, Use of High Speed Op Amps as D/A Converter Output Buffers, A Fast Peak Detector Circuit, Variable Gain Current Feedback Amps, 20MHz Variable Gain Amp, High Speed Instrumentation Amp, Low Noise Preamp Using the AD849, Clamped Amplifier, Level Shifting, Photodiode Detectors, Active Filters

Technical Article (Intermodulation Distortion)

11

# SECTION V HIGH SPEED NON-LINEAR SIGNAL PROCESSORS: MULTIPLIERS, LODULATORS, AND LOG AMPS

Introduction Multipliers Modulators Logarithmic Amplifiers

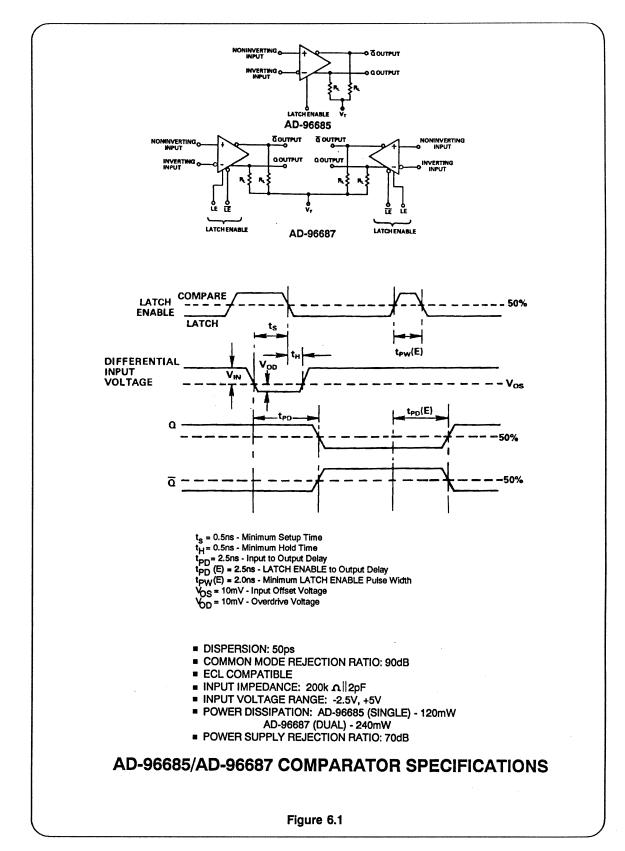

# SECTION VI TIME DOMAIN FUNCTIONS: COMPARATORS AND PIN ELECTRONICS

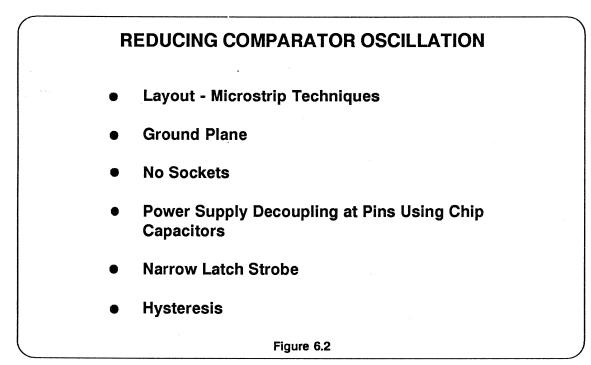

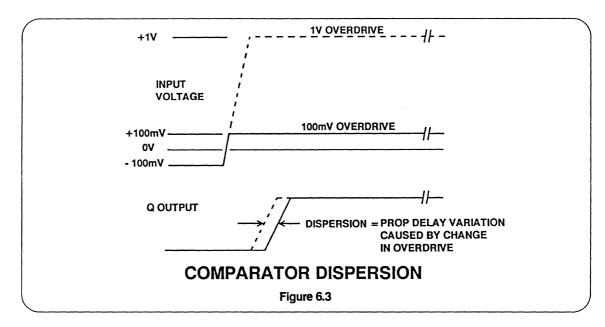

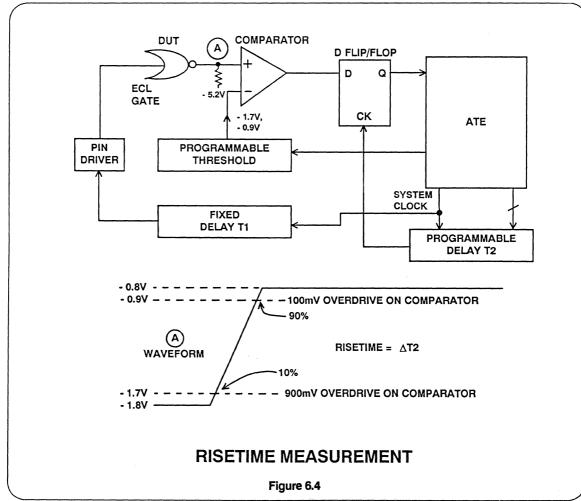

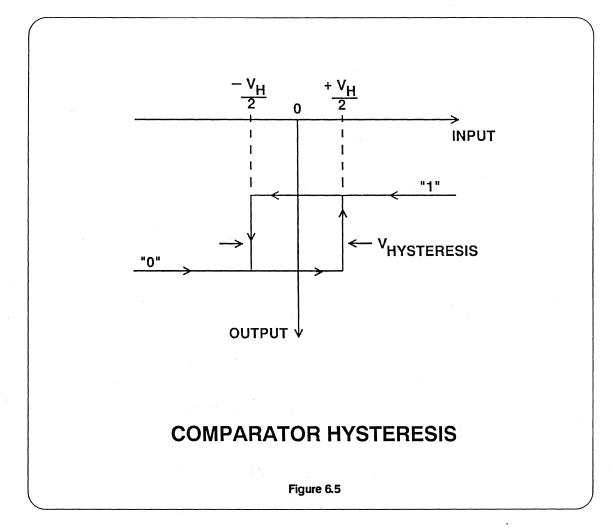

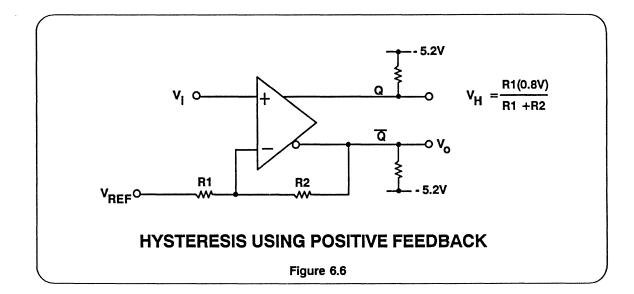

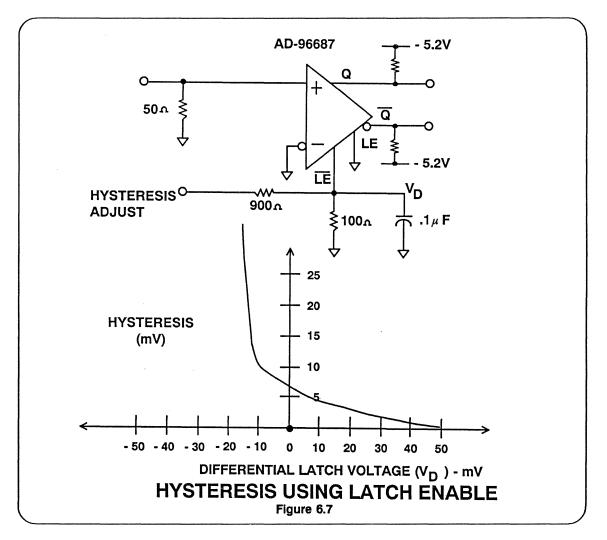

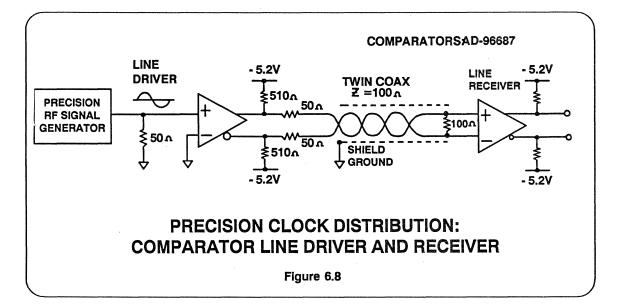

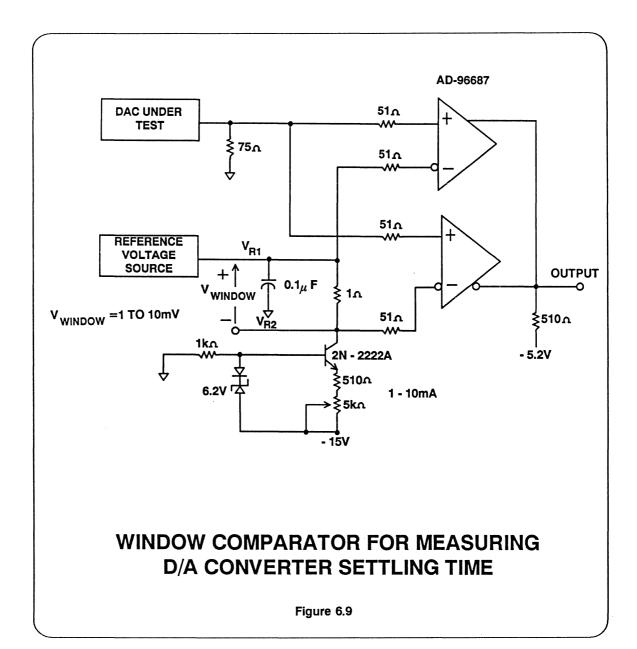

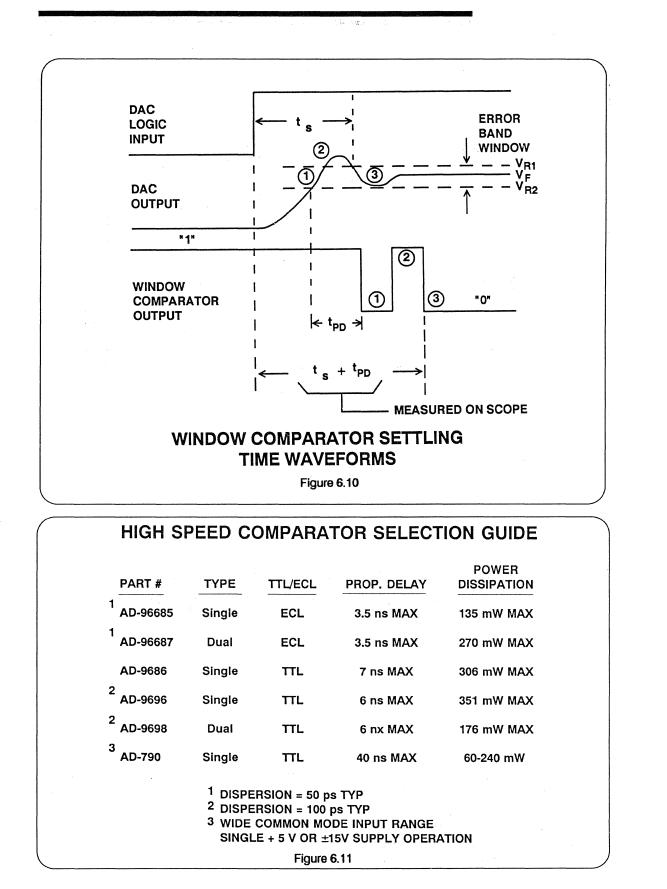

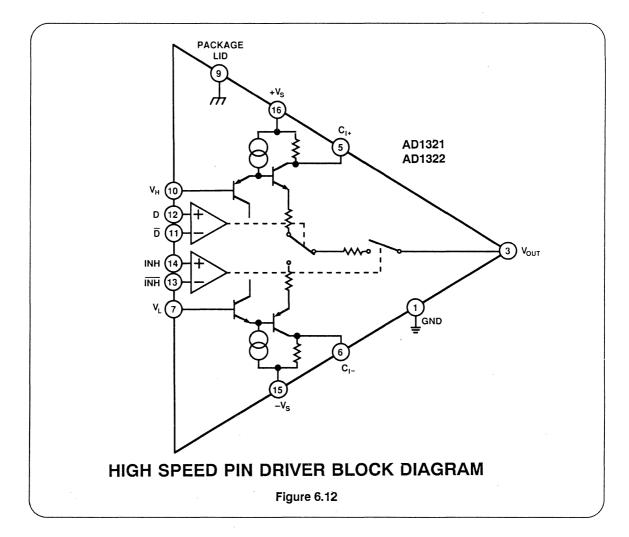

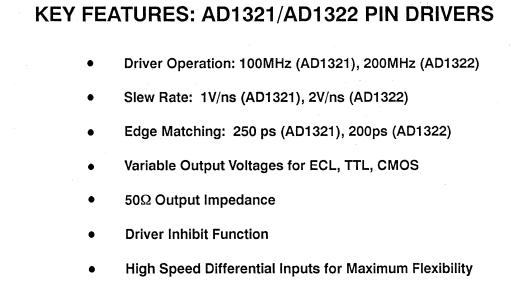

Comparator Operation Comparator Propagation Delay Dispersion Comparator Hysteresis Line Drivers and Receivers High Speed Window Comparator Circuit for Settling Time Measurements

**PIN Electronics for ATE**

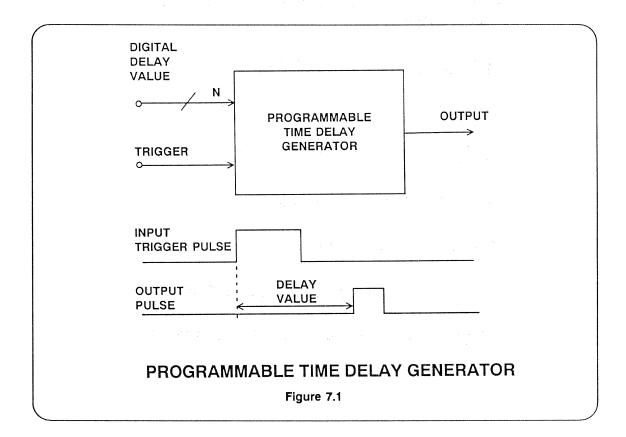

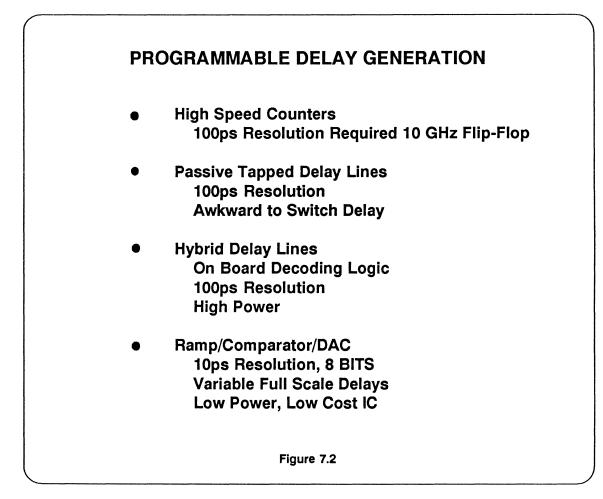

# SECTION VII TIME DOMAIN FUNCTIONS: TIME DELAY GENERATORS

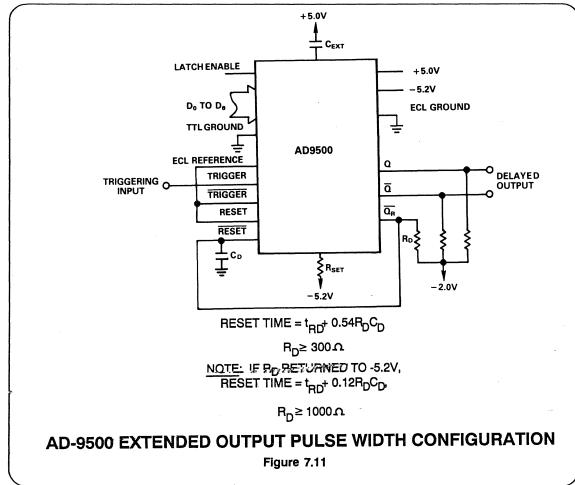

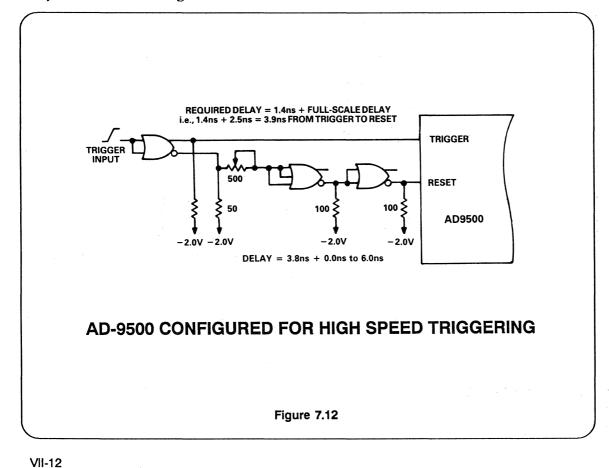

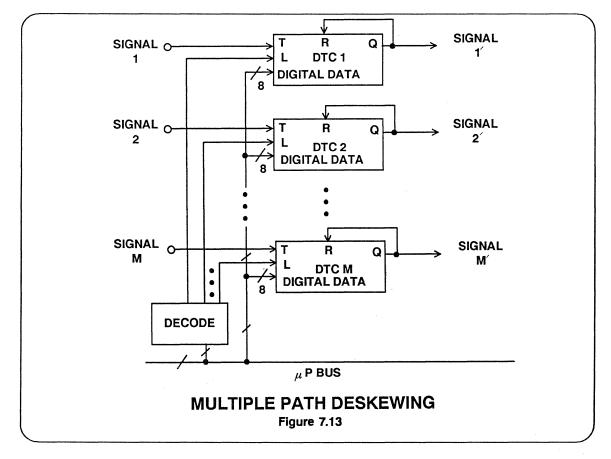

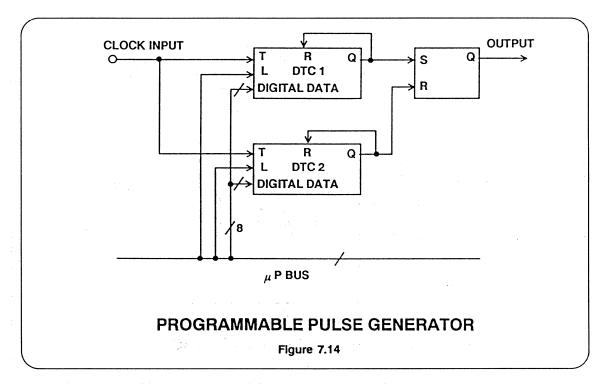

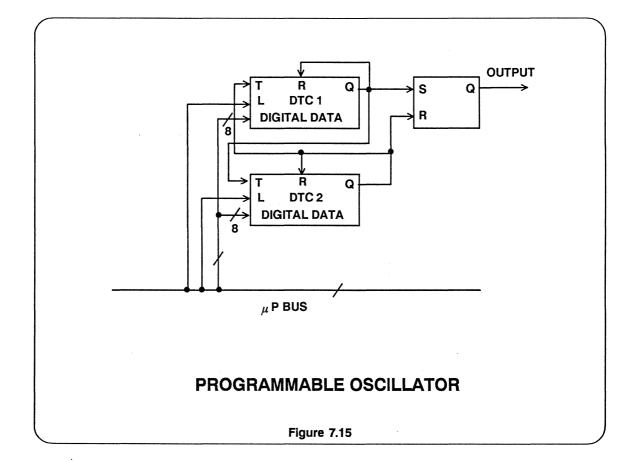

Programmable Time Delay Generation Techniques AD9500 Programmable Delay Generator AD9500 Minimum Output Pulse Width Configuration AD9500 Configured for Extended Output Pulse Widths AD9500 Configured for High Speed Triggering Multiple Path Deskewing Programmable Pulse Generator Programmable Oscillator

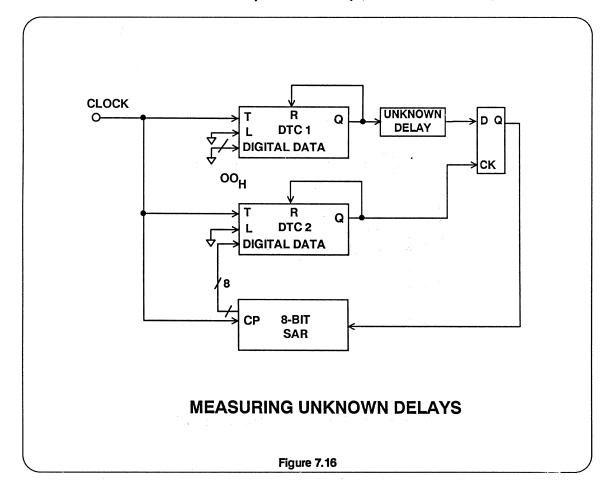

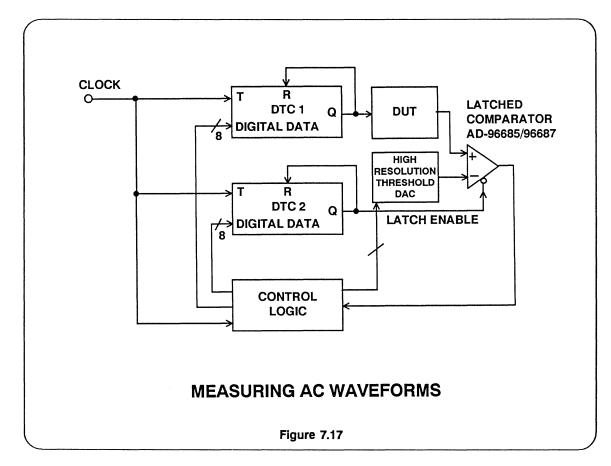

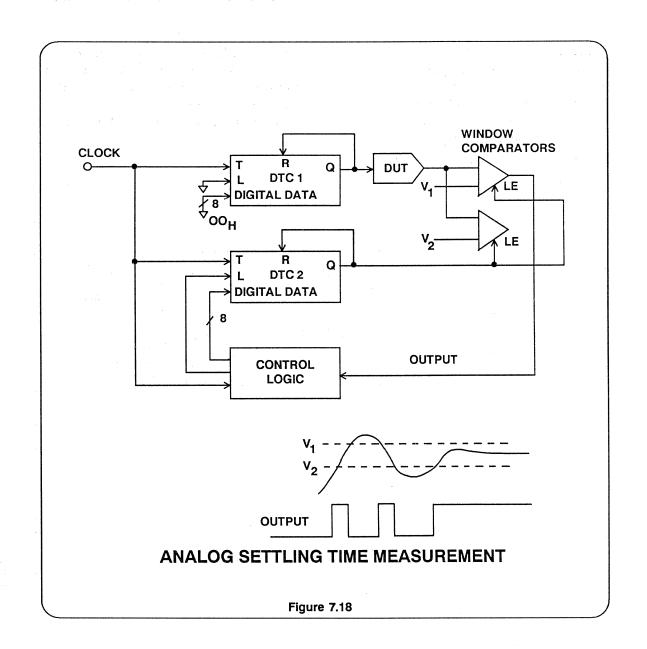

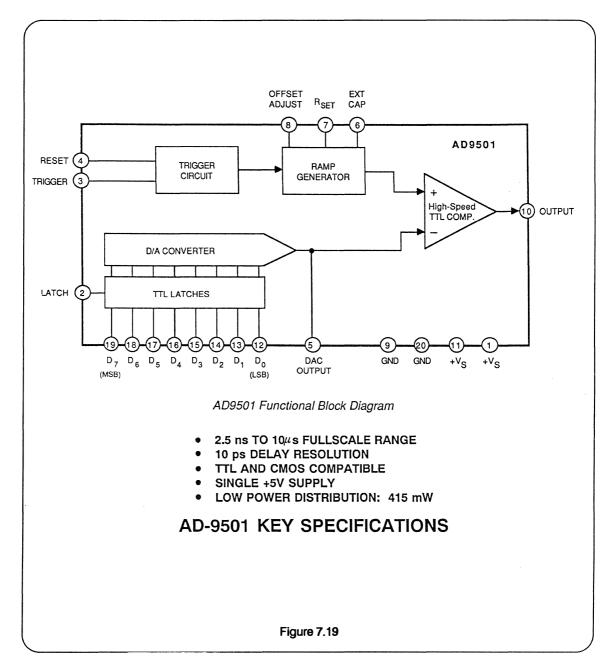

Digital Delay Detector Digitizing AC Waveforms Measuring Analog Settling Time AD9501 TTL Compatible Delay Generator

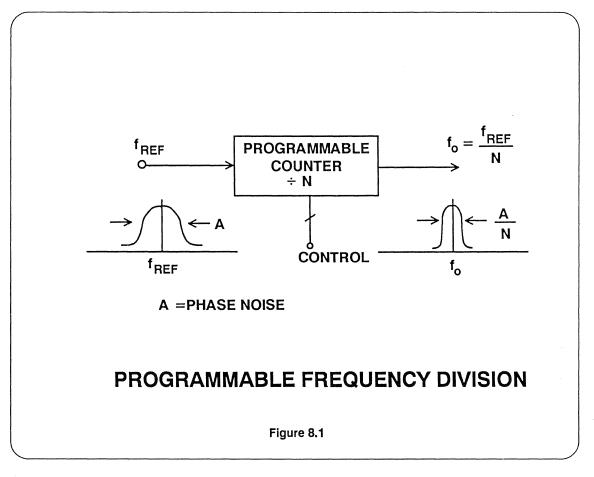

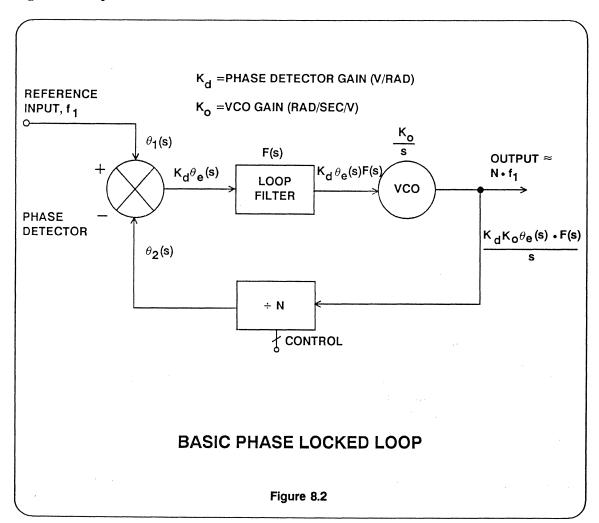

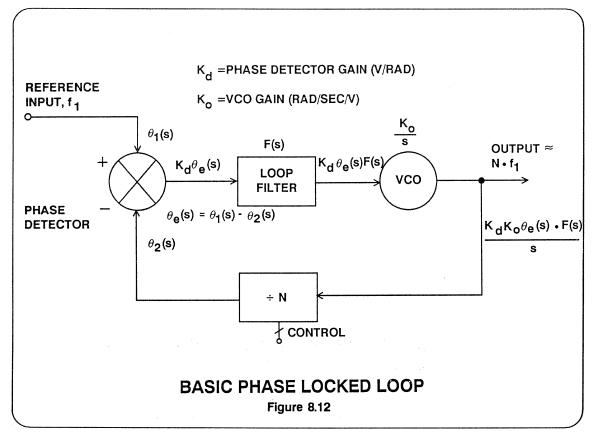

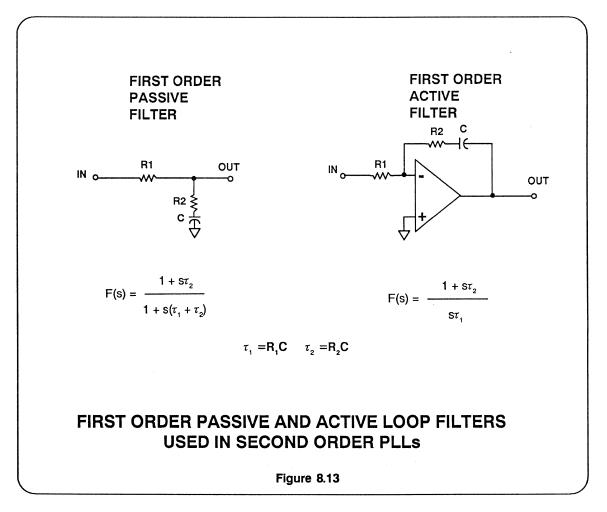

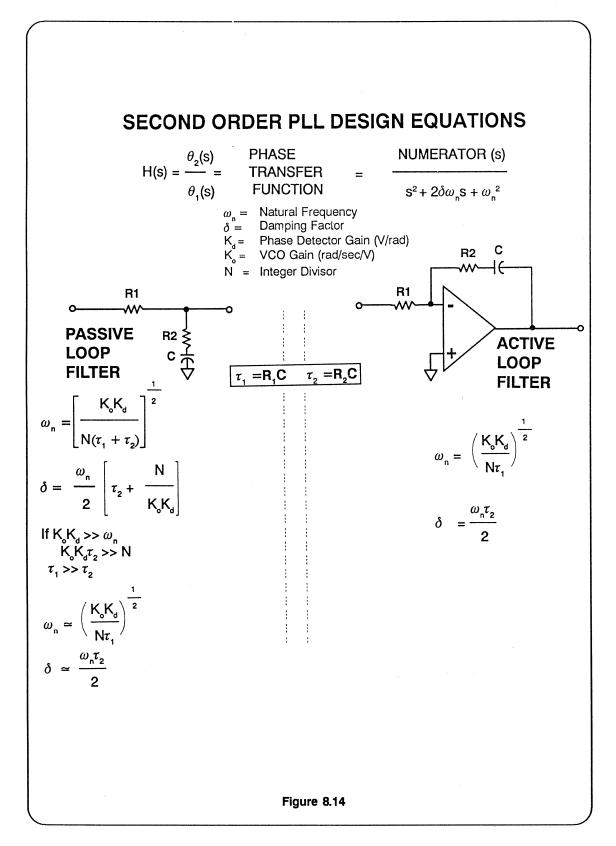

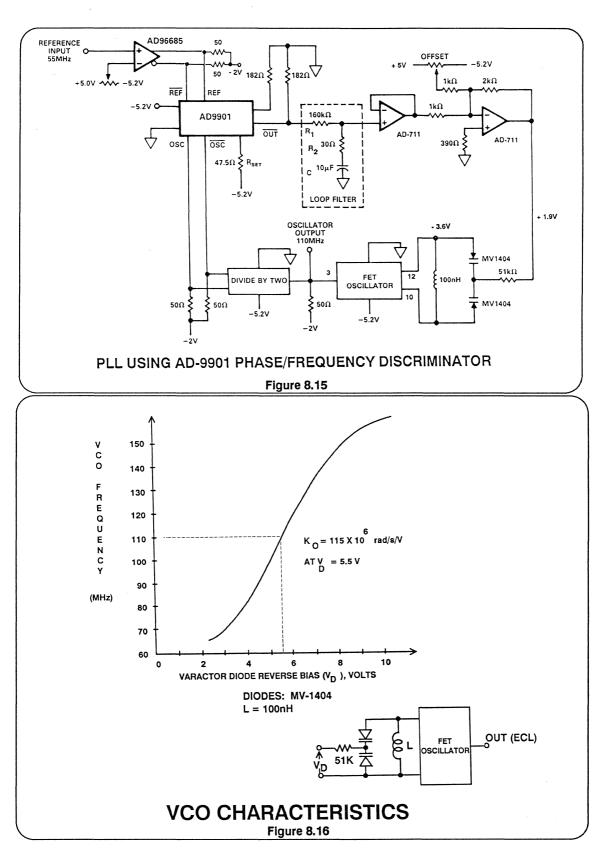

## SECTION VIII FREQUENCY DOMAIN FUNCTIONS: PHASE LOCKED LOOPS

Basic Phase Locked Loop

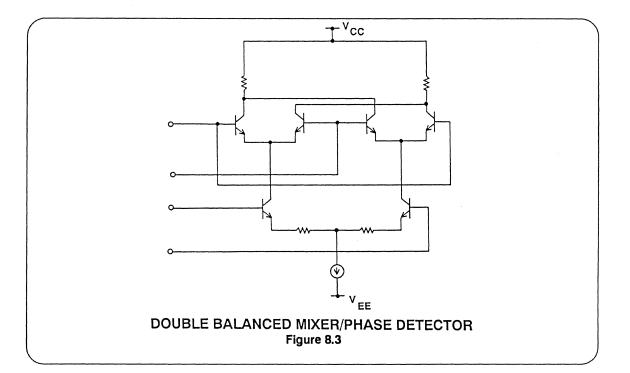

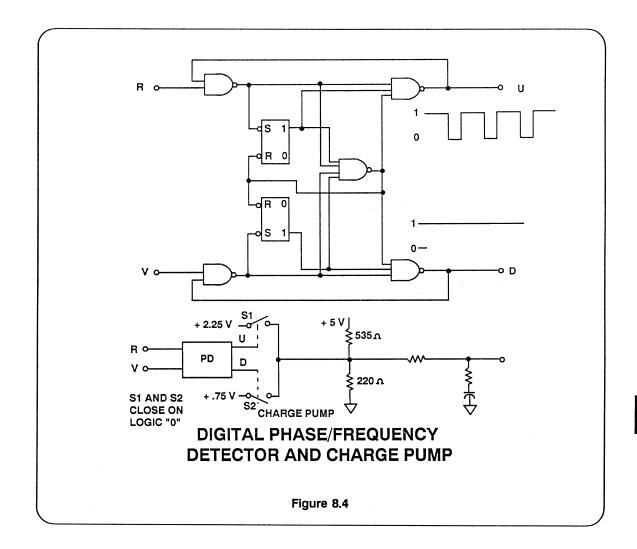

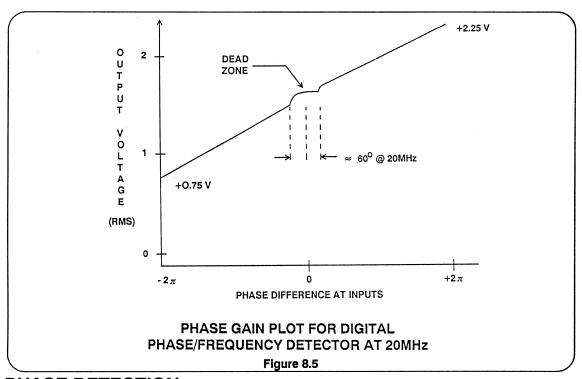

Phase Detectors: Analog Mixers, Digital Phase/Frequency Detector

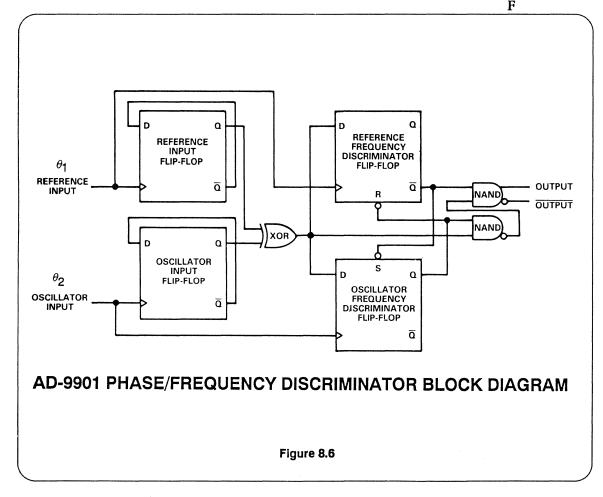

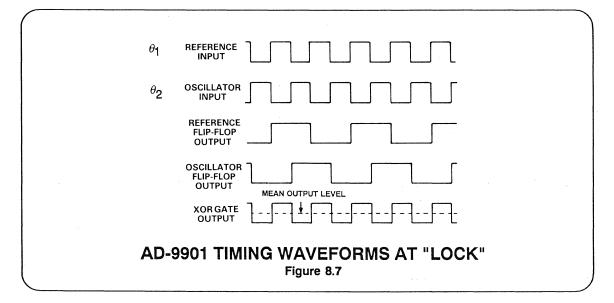

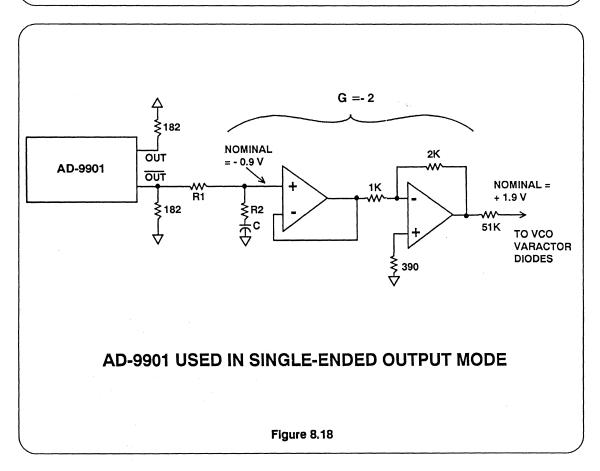

Phase Detection Using the AD9901 Phase/Frequency Discriminator

**PLL Mathematics and Design Basics**

Using the AD9901 in a PLL

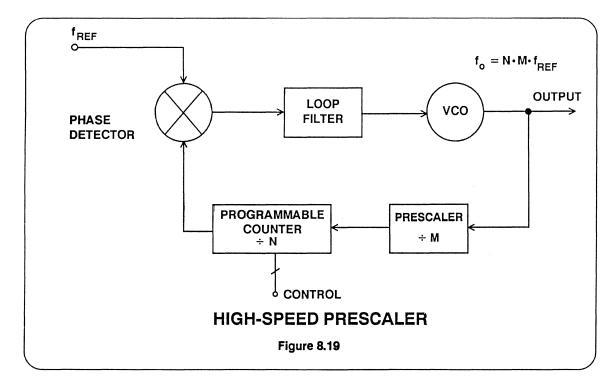

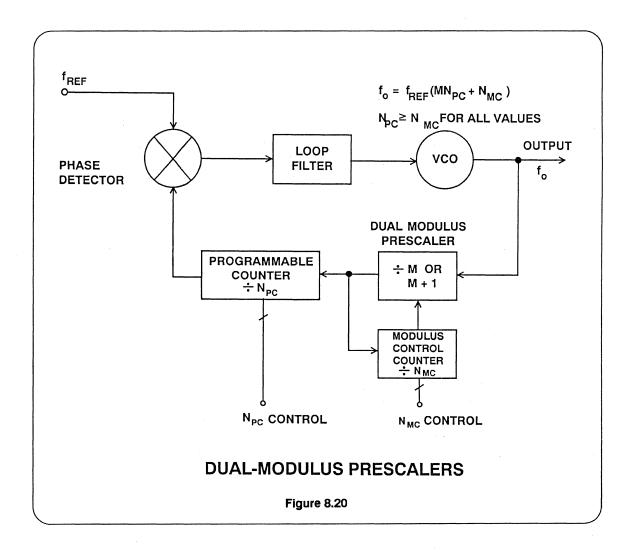

**Use of Dual Modulus Prescalers**

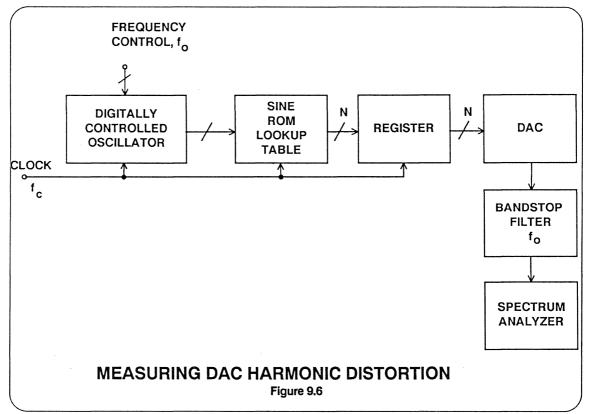

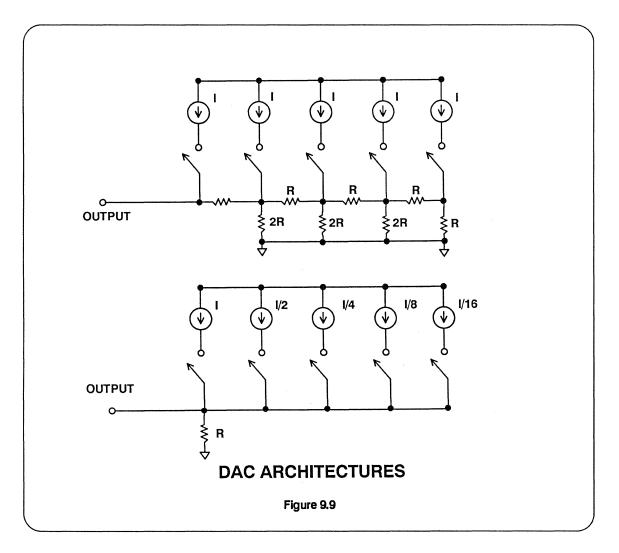

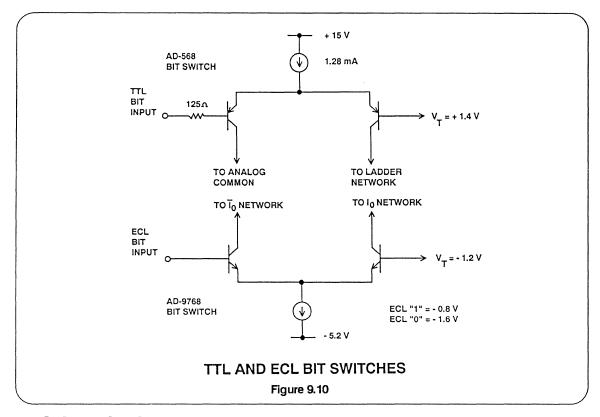

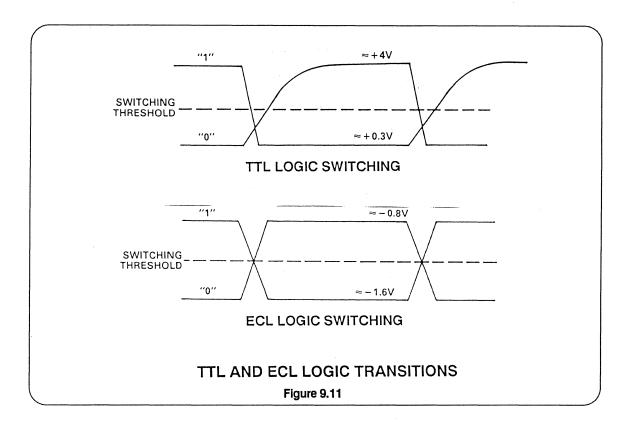

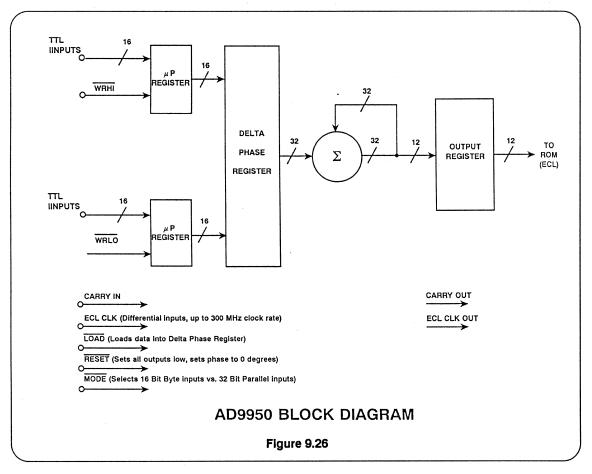

# SECTION IX FREQUENCY DOMAIN FUNCTIONS: D/A CONVERSION AND DIRECT DIGITAL SYNTHESIS

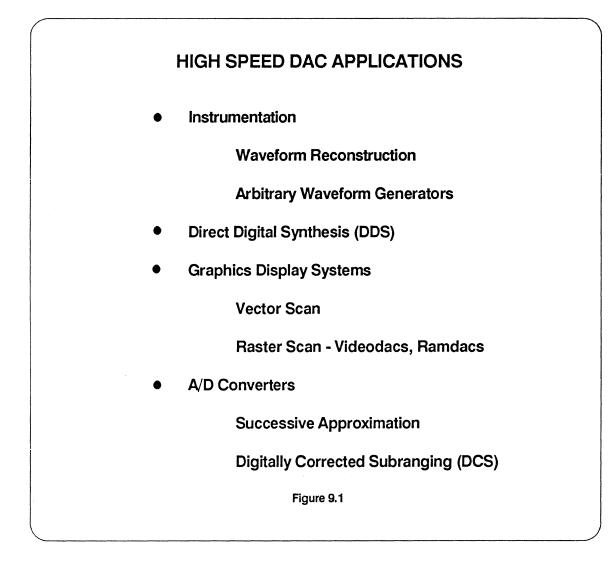

**Applications for High Speed DACs**

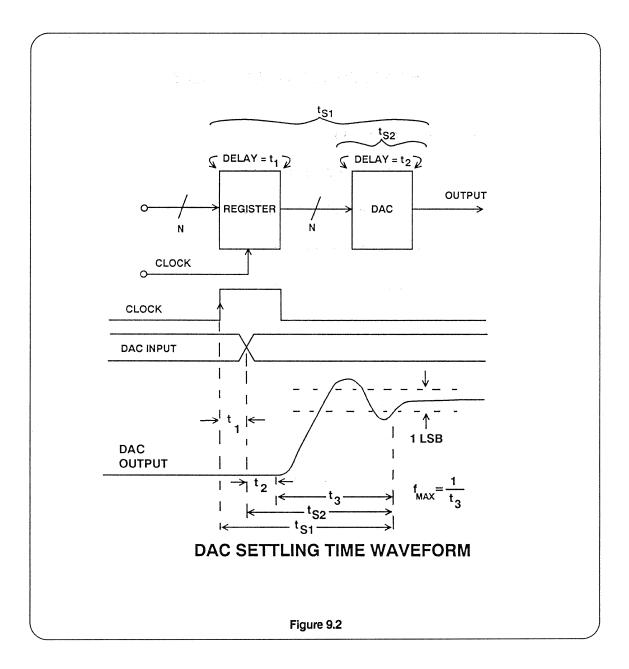

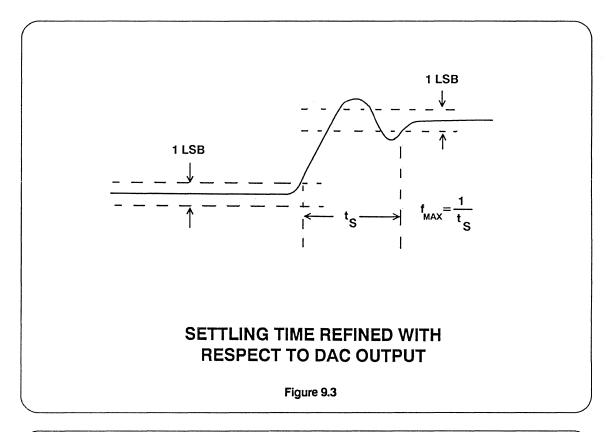

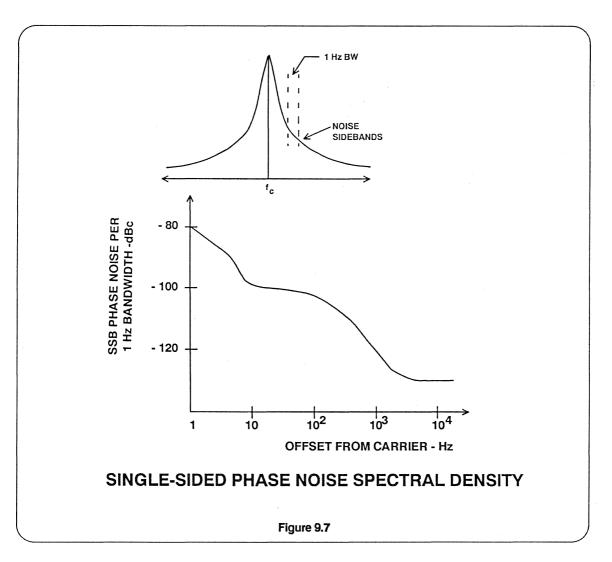

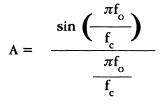

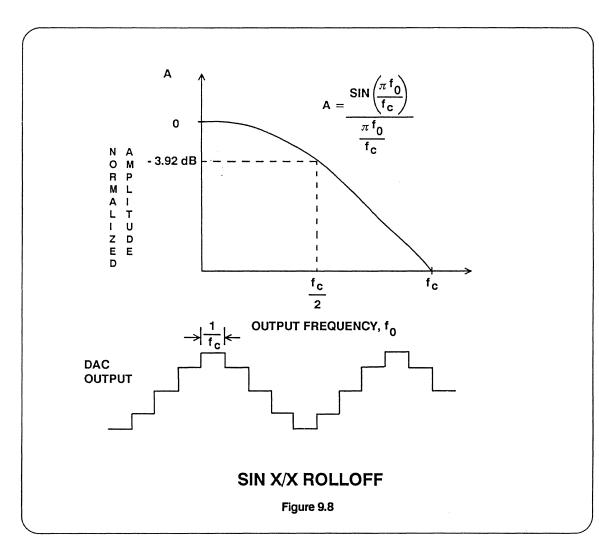

Dynamic Performance Considerations and Specifications for DACs:

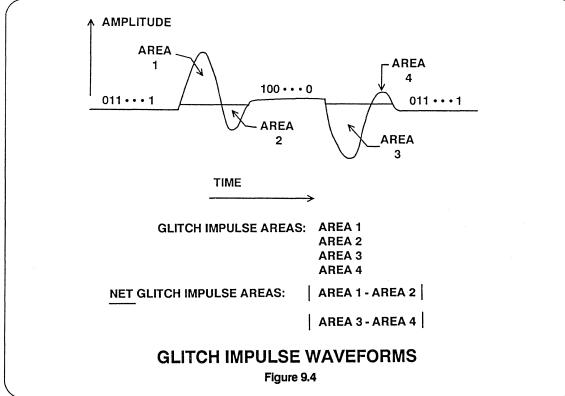

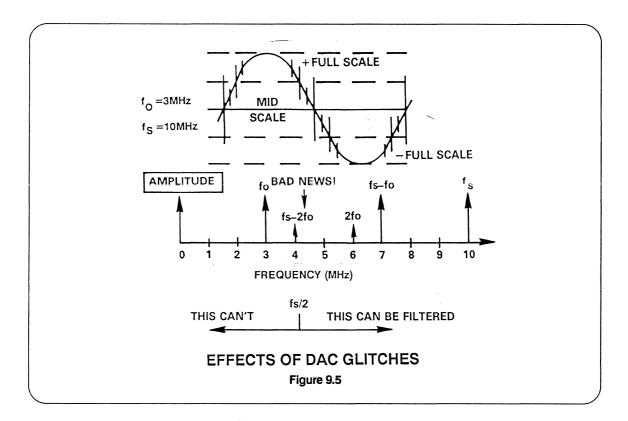

Settling Time, Update Rate, Glitch Impulse, Harmonic Distortion, Phase Noise

SIN X/X Rolloff Effect

**High Speed DAC Implementations**

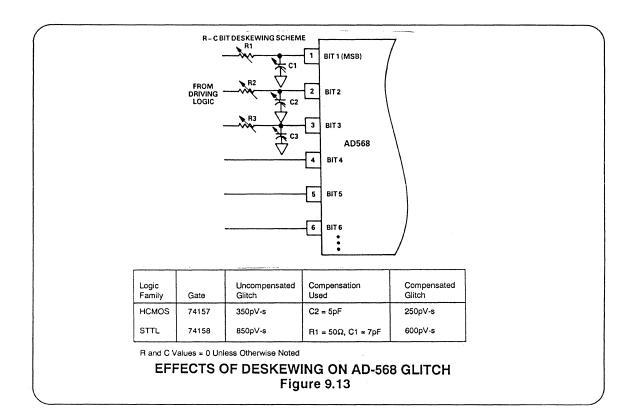

**Designing for Minimum Glitch Impulse**

**Glitch Reduction Using Segmentation**

**Deglitching Using SHAs**

**Direct Digital Synthesis Techniques**

**Frequency Synthesis Figures of Merit**

**Direct Digital Synthesis Applications**

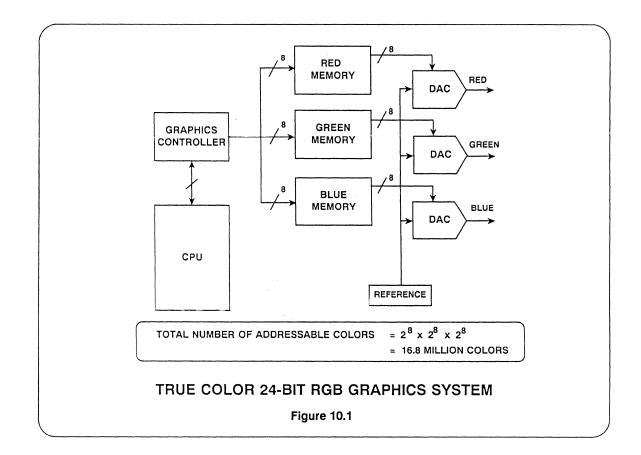

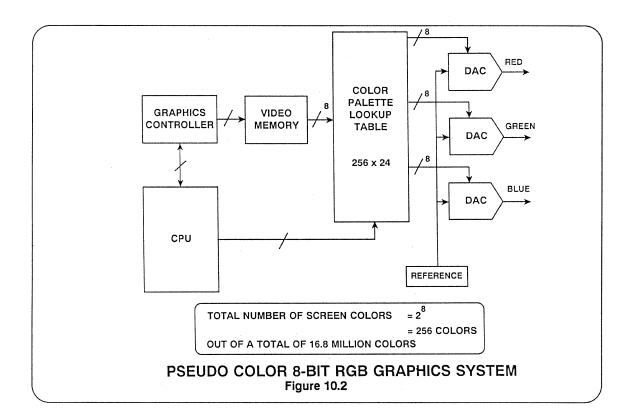

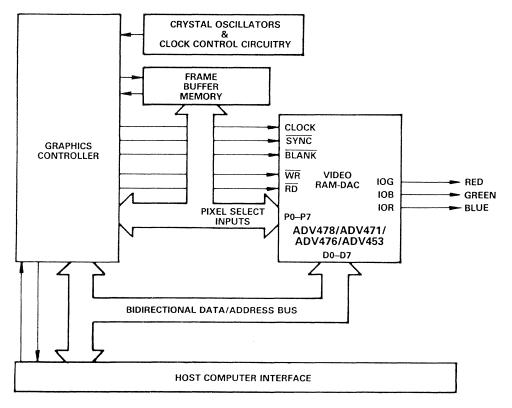

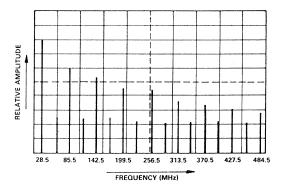

# SECTION X COMPUTER GRAPHICS AND RAM-DACs

Introduction

Computer Color Graphics Systems

Color Look-Up Tables

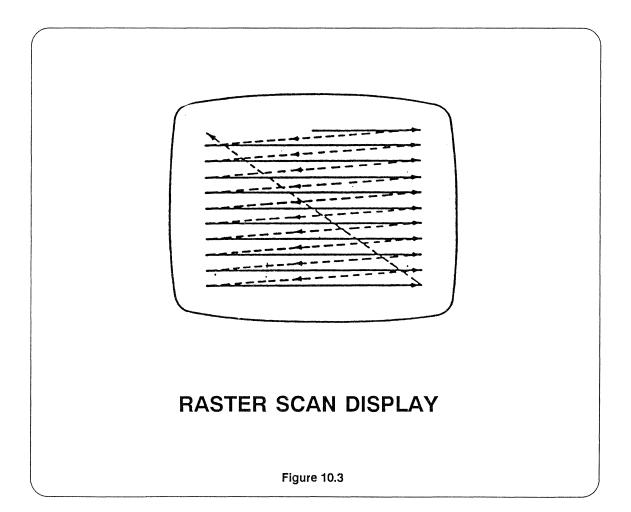

Video Formats

Specifications

**RAM-DACs**

**Using Overlay Palettes**

**Continuous Edge Graphics Digital Signal Processor**

Application Notes

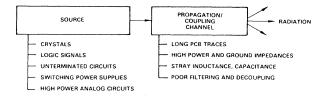

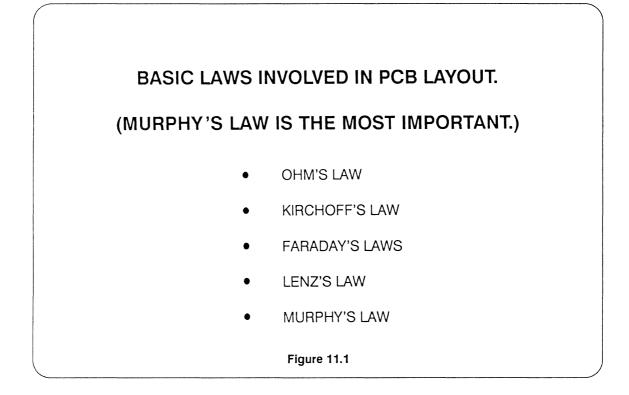

## SECTION XI: HIGH SPEED TECHNIQUES

#### Introduction

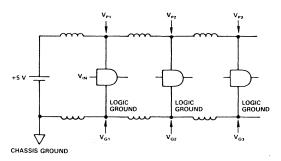

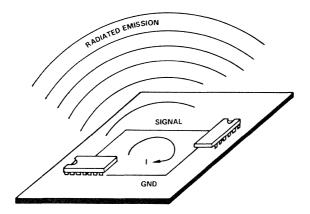

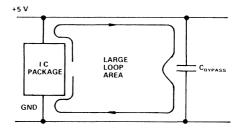

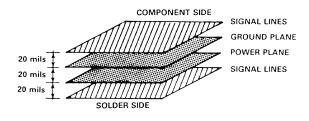

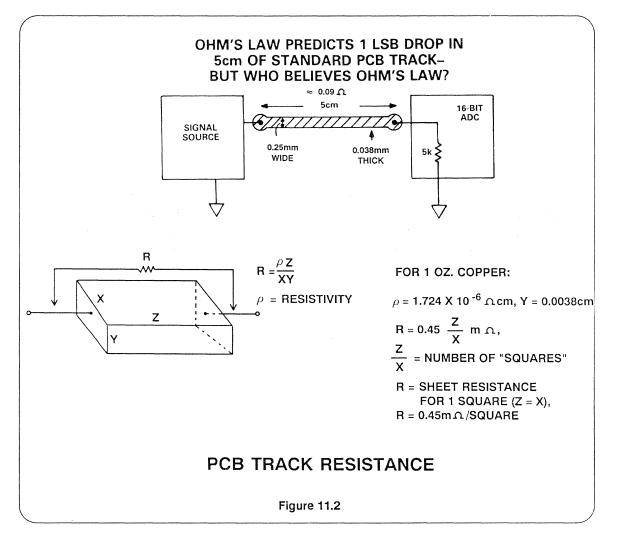

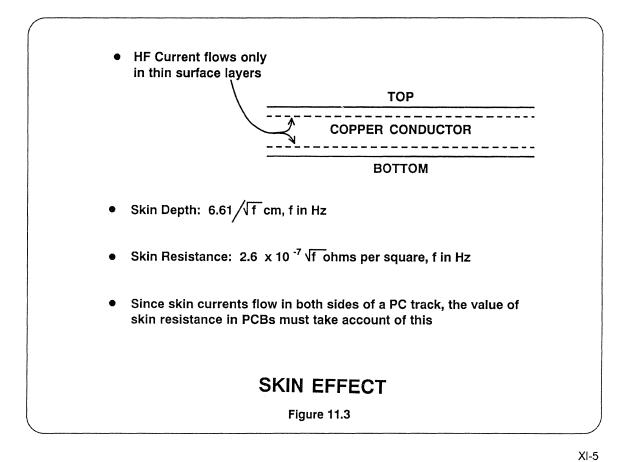

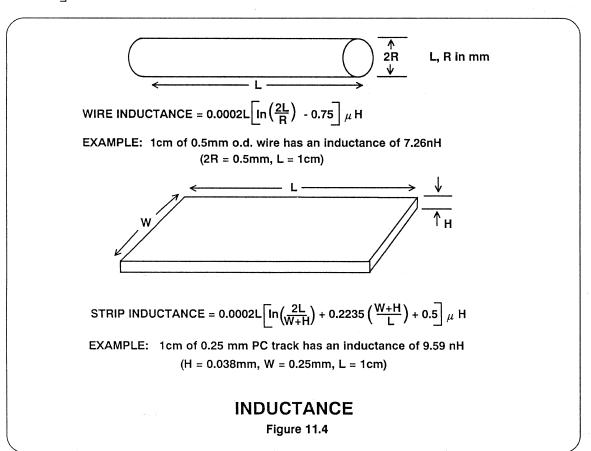

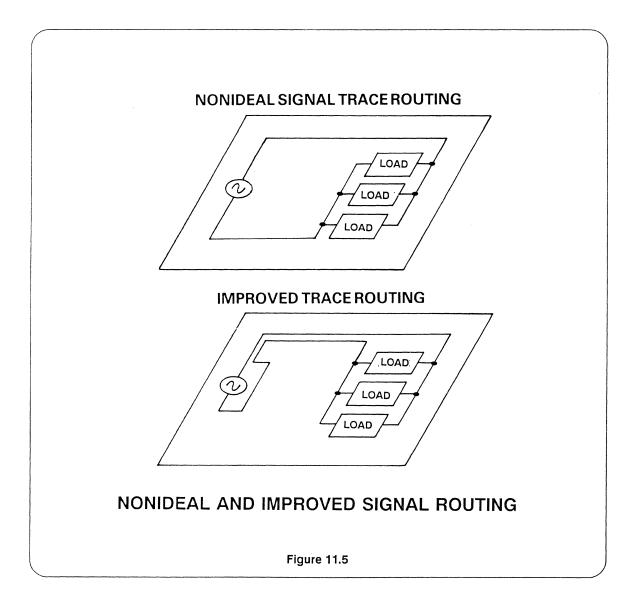

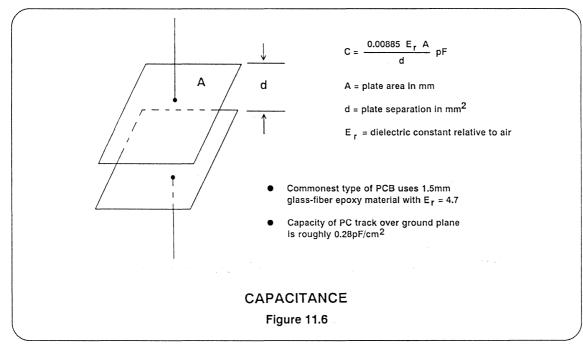

Impedance: Resistance, Inductance, Capacitance

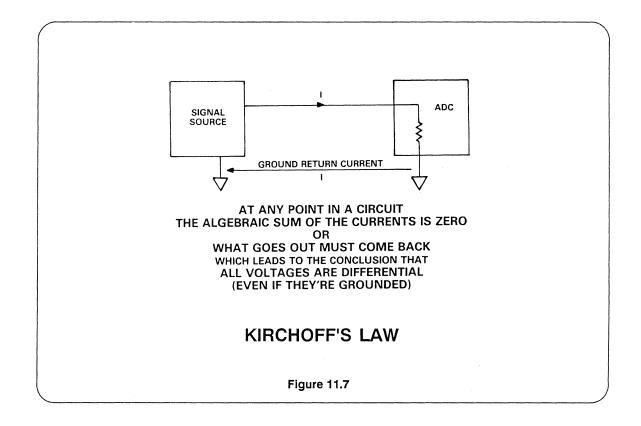

Grounds and Grounding: Kirchoff's Law, Ground Systems

#### Noise:

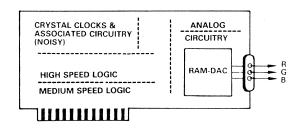

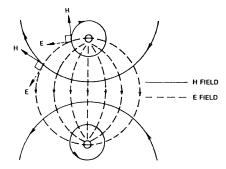

Conducted, Capacitive Coupling, Inductive Coupling, Electromagnetic Coupling, Overall Layout, Multiple Card Systems, Logic Types

**Construction - IC Sockets**

**Prototyping High Speed Circuits**

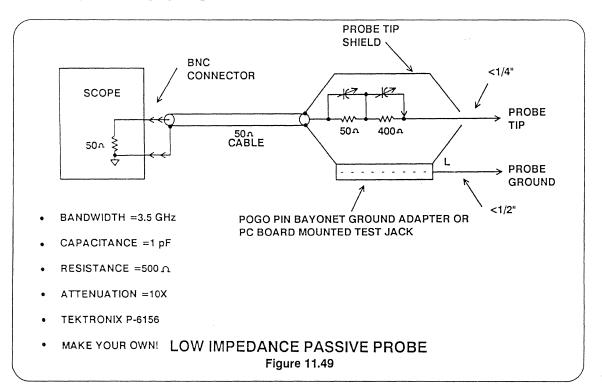

**High Speed Probing Techniques**

#### INDEX

v

and a substitution of the second state of the second state of the second state of the second state of the second

|  |  | 19 - 4 |  |

|--|--|--------|--|

|  |  |        |  |

# **SECTION I**

# HIGH SPEED A/D CONVERSION

$(x_1, x_2) = (x_1, x_2) + (x_2, x_3) + (x_3, x_4) + (x_4, x_4) + (x_$

.

# **HIGH SPEED A/D CONVERSION**

## HIGH SPEED A/D CONVERTER ARCHITECTURES

Flash

Successive Approximation

Subranging

**Digitally Corrected Subranging**

# A/D CONVERTER APPLICATIONS

Undersampling (Super-Nyquist)

Oversampling

Dithering

Multiplexing

# A/D CONVERTER DYNAMIC SPECIFICATIONS AND TESTING

**DSP** Testing

**Quantization Theory**

DFTs and FFTs

Signal to Noise Ratio

Effective Bits

Harmonic Distortion

Two-Tone Intermodulation Distortion

Spurious Free Dynamic Range

Coherent Sampling

Non-Coherent Sampling

Windowing

Sinewave Curve Fit

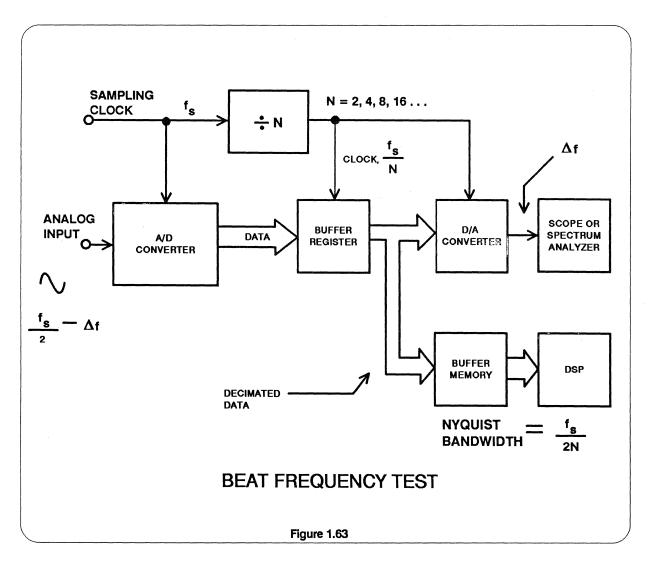

**Beat Frequency Tests**

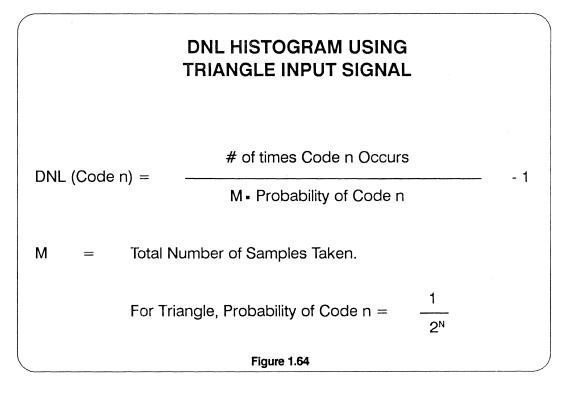

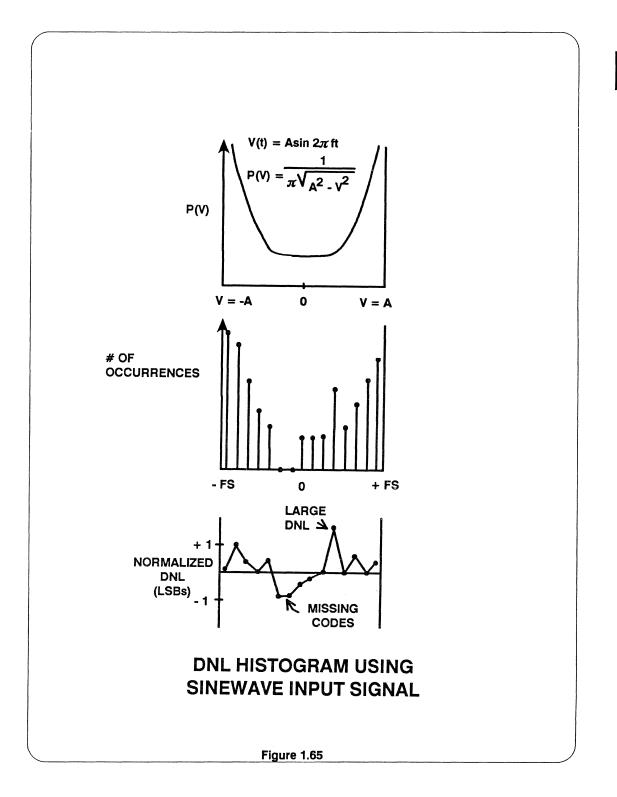

Histogram Tests

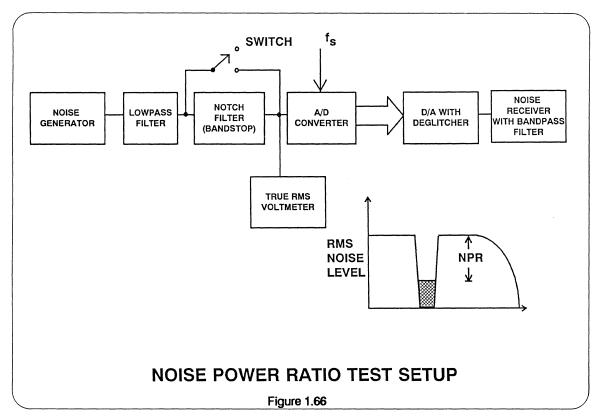

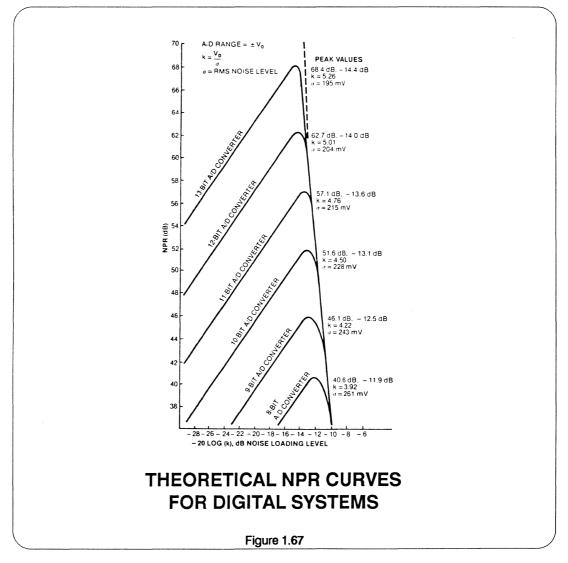

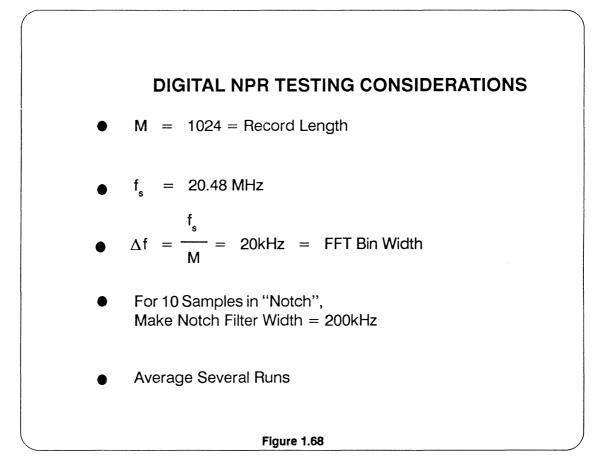

Noise Power Ratio

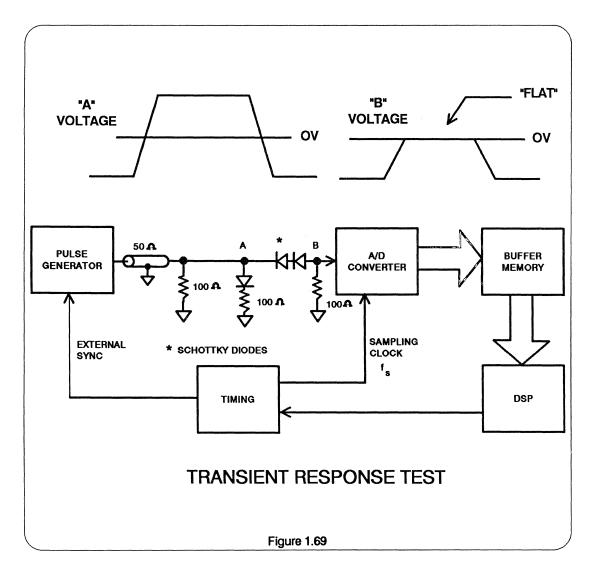

**Transient Response**

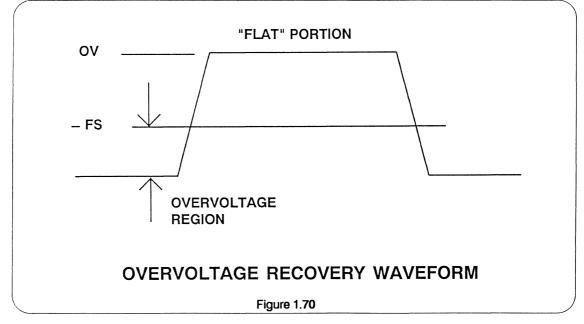

Overvoltage Recovery

**Aperture Time**

**Composite Video Tests**

**Error Rates**

#### REFERENCES

#### **TECHNICAL ARTICLE**

Multistage Error Correcting A/D Converters

# HIGH SPEED A/D<br/>CONVERTER ARCHITECTURESFlashSuccessive ApproximationSubrangingDigitally Corrected Subranging

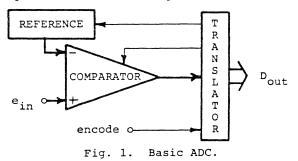

# FLASH CONVERTERS -Basic Operation

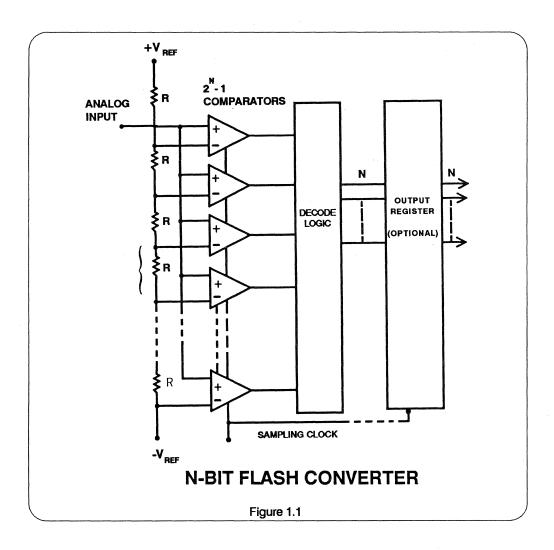

Recent advances in VLSI process technology and design techniques have made 4-10 bit flash A/D converters practical. This type of converter is characterized by high sampling rates and the ability to convert fast video input signals, usually without requiring a separate track-and-hold amplifier. The latter characteristic is limited, however, as we will discuss later. A block diagram of a typical flash converter is shown in Figure 1.1. The analog input signal to be digitized is applied simultaneously to  $2^{N}$ -1 latched comparators, where N is the number of bits. The reference voltage input for each comparator is derived from a resistive voltage divider. The reference voltage for each comparator is one least significant bit (LSB) higher than the comparator immediately below it.

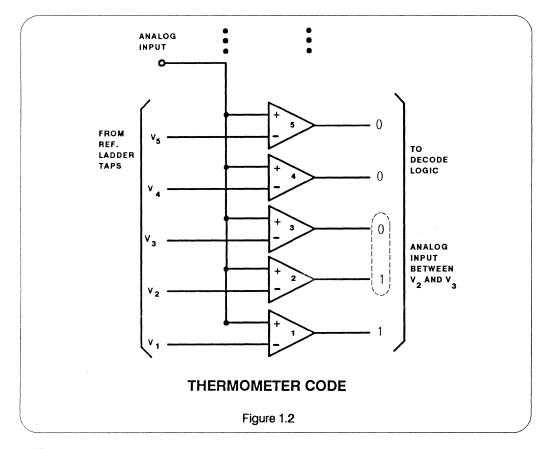

When an analog signal is present at the input of the comparator bank, all comparators which have a reference voltage below the level of the input signal will assume a logic "1" output. The comparators which have their reference voltage above the input signal will assume a logic "0" output. The result is often referred to as a "thermometer code" and is applied to a stage of decoding logic (See Figure 1.2). This decoding can be accomplished in a variety of ways (such as a simple priority encoder) and ultimately results in a binary digital output. The binary output of the decoding logic often drives an on-chip output latch.

## Flash Converters -Timing Considerations

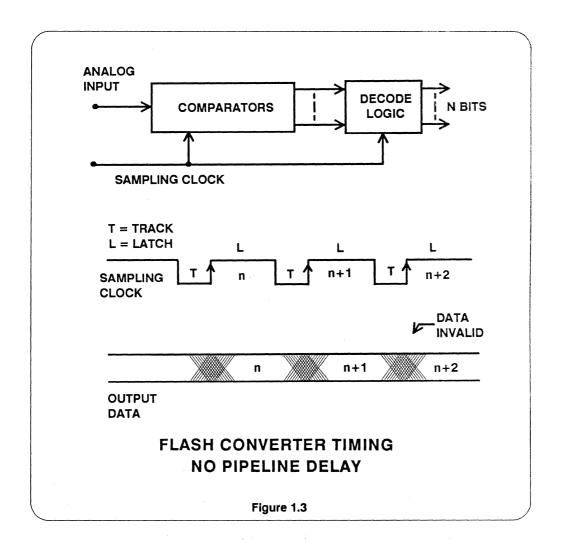

The comparator bank in a flash converter has two states. In the first state (controlled by the sampling clock), the comparators essentially "track" the analog input signal. In this state, the comparator outputs are changing, and the binary decoding logic output is invalid. When the sampling clock changes to the opposite logic level, the comparators are latched or "held", much the same as in a track-and-hold amplifier.

1-5

In a flash converter which has no output data latch (such as the AD-9688 or the AD-9000), the timing of the sampling clock with respect to the output binary data is shown in Figure 1.3. Note that the output data is invalid for a period roughly equal to the sampling clock pulse width. Since this pulse width must exceed some specified minimum value for proper operation of the comparators, it follows that at high sampling rates, the time during which the output data is invalid reduces the "data valid" time, thereby making it more difficult to strobe the flash converter output into an external register. For instance, if the flash converter is operated at a 100MHz sampling rate and the sampling clock is 5ns wide (50% duty cycle), the output data will be valid for only 5ns (neglecting the rise and fall time of the output binary bits).

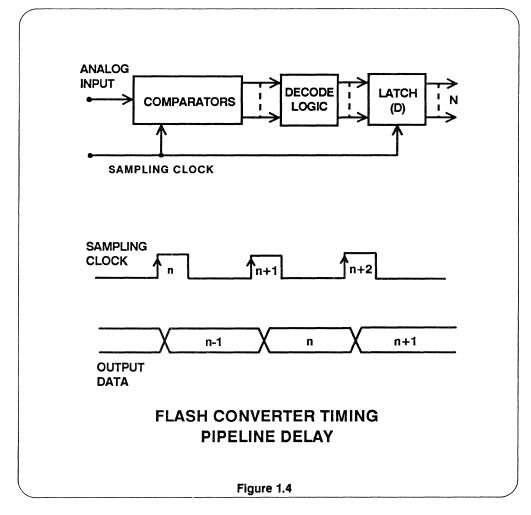

The addition of an internal latch after the decoding logic (such as the AD-9002, AD-9012, AD-9006, and the AD-9048) results in a timing diagram such as that shown in Figure 1.4. Note that the output data is now valid for approximately the entire clock cycle, and the flash converter

can be viewed as an edge-triggered device with an inherent one-cycle "pipeline" delay. The additional pipeline delay is not usually a problem in most systems applications, and the task of clocking the output data at the proper time is simplified.

# FLASH CONVERTER STATIC ERROR SOURCES

When a flash converter is digitizing a slowly changing or DC input voltage, the primary sources of integral and differen-

tial non-linearity are due to the matching of the reference ladder resistors, and the comparator input offset voltages and currents. Although not usually specified on the data sheet, most flash converters are somewhat sensitive to the duty cycle and frequency of the encode command pulse. This problem is manifested as a shift in differential and integral nonlinearity which is a function of clock duty cycle and frequency, especially when operating at or near the maximum specified sampling rate for the particular flash converter under consideration.

Another source of static flash converter errors, sometimes called "metastable state" errors, results from the finite probability that a comparator which is toggling between two logic levels (the analog input is equal to the comparator's

reference voltage input) may produce an erroneous binary code at the flash converter's final output. This metastable condition can result in a fullscale error if it occurs at the flash converter's mid-scale code (i.e., bits changing from 0111...1 to 1000...0). These erroneous error codes may show up as white dots or "sparkles" when digitizing television waveforms, hence the term "sparkle codes".Proper design of the comparators and/or use of additional logic algorithms in the decoding function can minimize these errors to an acceptable level for most applications. (See section on Dynamic Testing of A/D Converters for further discussion and how to measure this error.)

# FLASH CONVERTER STATIC ERROR SOURCES

- Reference Ladder Resistor Matching

- Comparator Offset Voltage Matching

- Comparator Bias/Offset Current

- Comparator Metastable Output States

- Reference Ladder Parasitic Resistance

Figure 1.5

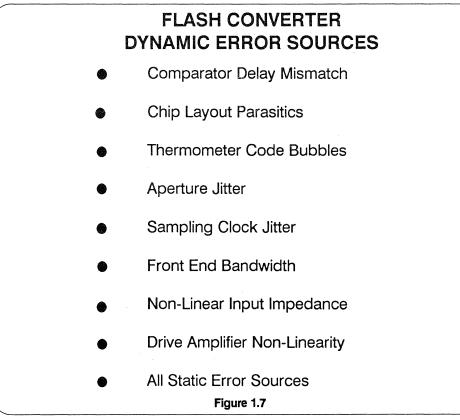

#### Flash Converter Dynamic Error Sources

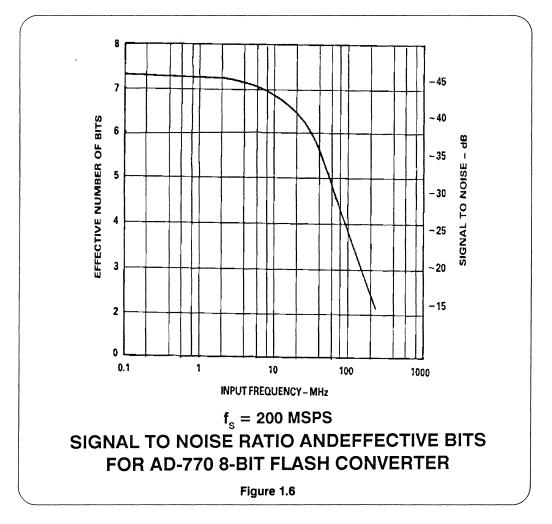

In the majority of video A/D converters (including flash converters), linearity (differential and integral) degrades as the analog input signal slew-rate increases. These errors manifest themselves as increased harmonic distortion, degradation in signal-to-noise ratio (SNR), missing codes, and spurious or "sparkle" codes. In a flash converter, these degradations occur primarily due to the relative delay mismatch between each comparator in the bank. This delay mismatch is a function of many design-related variables such as IC process variations, chip layout, comparator design, etc. A close to ideal converter would maintain its static performance specifications across the full Nyquist bandwidth (or higher for some applications). The theoretical RMS signal-to-noise ratio for an N-bit A/D converter is given by the well-known equation

SNR = 6.02N + 1.76dB. A typical plot of SNR versus input frequency for an 8-bit flash converter (AD-770) is shown in Figure 1.6 for a 200MHz sampling rate. The dynamic performance can also be evaluated in terms of Effective Number of Bits (ENOB) by solving the equation for N given the measured SNR. See the section on Dynamic Testing for a further discussion of this measurement.

Sample-to-sample variations in the effective sampling instant (aperture jitter) can also cause degradation in the overall SNR measurement for high slew-rate inputs. This jitter can be produced internally and/ or externally to the flash converter. Proper grounding techniques, power supply decoupling, PC board layout, and clean sampling clock pulses (both phase and frequency stable) are the best techniques to minimize externally produced jitter components.

Glitches or "sparkle codes" due to metastable comparator states as previously discussed, can also occur for high slewrate input signals.

In addition, high slew-rate inputs may produce what is called a "bubble" in the comparator bank thermometer code

output. Ideally, the comparator bank output should be a sequence of logic "1"s followed by a sequence of logic "0"s as shown in Figure 1.2. An out-of-sequence "1" or "0" may occur for high slew-rate inputs due to comparator delay mismatches. This creates a condition which looks like a "bubble" in the normal thermometer code. Depending upon where in the sequence it occurs, the "bubble" may cause the decoding logic to produce a large error code, or "sparkle" code. The probability of getting a "bubble" due to comparator mismatch can be reduced by proper comparator design. The magnitude of the binary error (sparkle code) produced by a "bubble" can be minimized by increasing the sophistication and complexity of the decoding logic.

# Flash Converter Full-Power Bandwidth

Flash converter "full power bandwidth" (FPBW) is a specification for which there is no currently accepted industry-wide definition. Users of flash converters should scrutinize the data sheet carefully and understand both the manufacturer's definition and test method.

In a traditional op-amp, FPBW typically is meant to be the maximum frequency at which the amplifier is capable of producing the maximum specified peak-to-peak output voltage at some level of distortion. Another commonly used definition is to calculate FPBW from the slew rate (SR) of the amplifier using the equation:

$$FPBW = \frac{SR}{2\pi V_{o}}$$

where the output voltage range of the amplifier is  $\pm V_0$ .

The problem in applying traditional "analog" bandwidth definitions to flash converters is that the results can be very misleading -- typically, the dynamic error sources previously discussed become dominant long before the true analog bandwidth of the comparator front end is approached.

If the FPBW is defined as the frequency at which the peak-to-peak "reconstructed"

sinewave output is reduced by 3dB for a fullscale input (a common definition), then the ENOBs or SNR at this input frequency may very well render the flash converter useless in a practical application. Thus, FPBW <u>and</u> ENOB or SNR must be considered together when evaluating flash converter performance. It is also important that the sampling rate be specified, since dynamic degradations are also more likely to worsen as the sampling rate is increased.

Another definition sometimes encountered for FPBW is the maximum fullscale input signal that can be processed by the flash converter at a specified sampling rate without missing any codes. Using this definition will always give the most pessimistic number of any definition previously discussed and, therefore, it appears on only a few A/D data sheets.

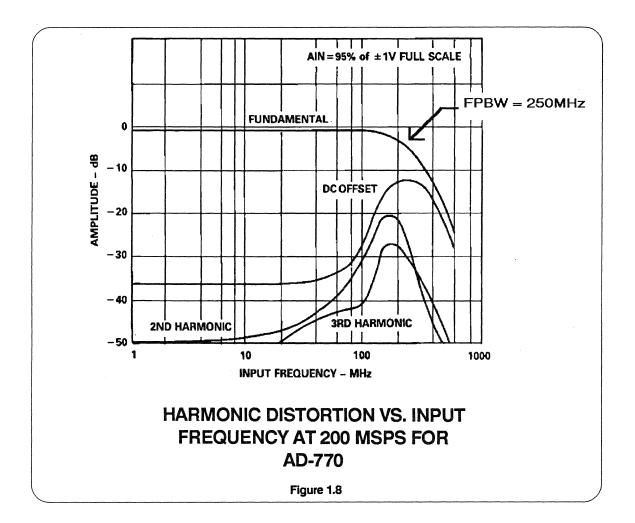

A recently proposed definition for FPBW (courtesy Chris Manglesdorf - Senior Scientist at Analog Devices) is that frequency at which the <u>fundamental</u> component of the reconstructed FFT output (neglecting harmonics) of the flash converter is reduced by 3dB from fullscale. Figure 1.8 shows an FFT plot for the AD-770 where the FPBW is measured to be 250MHz using this definition.

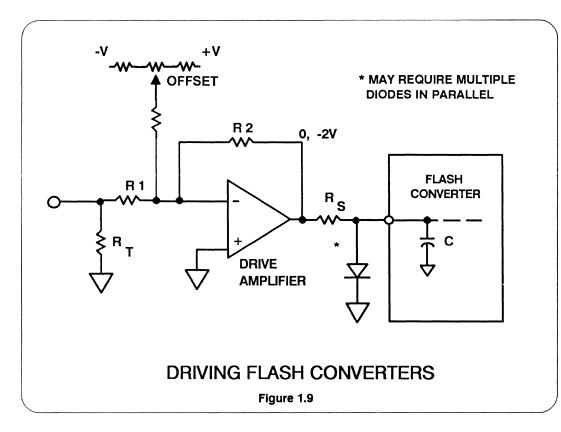

#### Driving Flash Converters

In a system application, the video signal to be digitized by the flash converter usually comes from a 50, 75 or 93 ohm source. This signal may be bipolar or unipolar. Obviously, if the input range of the flash converter is not compatible with the signal, a wideband amplifier will be required to produce the required gain and offset. (See Figure 1.9.)

In addition, the input capacitance of some flash converters may vary as a function of the analog input signal, thereby requiring a buffer amplifier for isolation to prevent the non-linear capacitance from producing undesirable harmonics in the digitized signal.

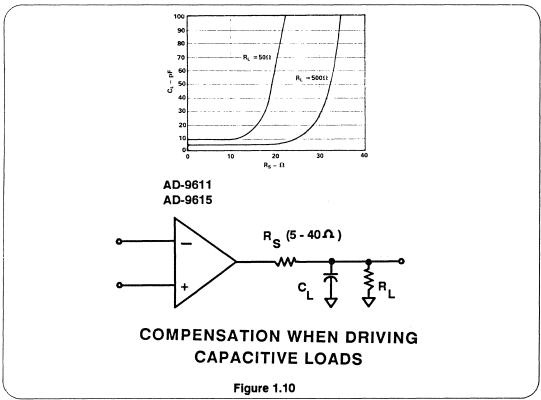

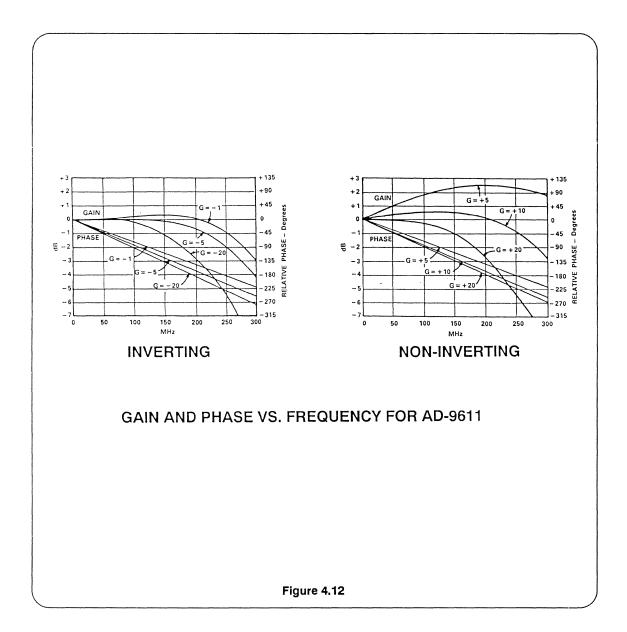

For some flash converters, the input capacitance is so high that a buffer amplifier is required to preserve the signal bandwidth. Figure 1.10 shows the appropriate series resistor value for various load conditions when using the AD-9611 current feedback amplifier as a driver.

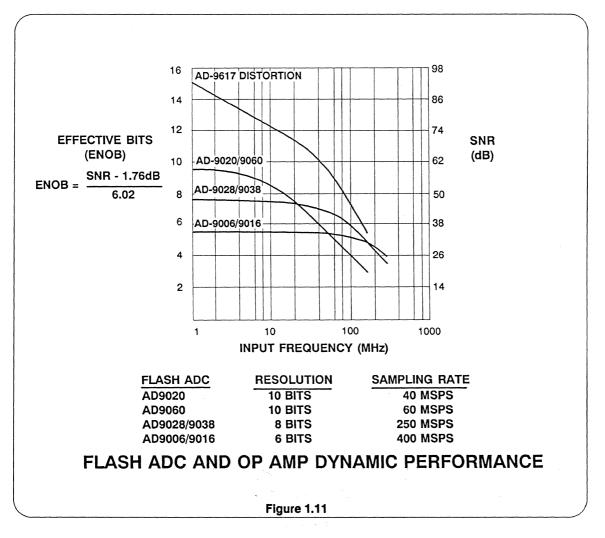

Since most applications do require a buffer amplifier ahead of the flash converter, the user must select it carefully. The primary consideration is to match the dynamic performance (harmonics, SNR, etc.) of the amplifier to that of the flash converter so that the inherent performance of the flash converter isn't degraded by the amplifier. Figure 1.11 shows the harmonic distortion of the AD-9617 monolithic current feedback amplifier plotted with the SNR for several flash converters. Fortunately (or unfortunately, depending on your perspective), the flash converter itself is usually the limiting factor to dynamic performance if the amplifier is properly selected. Pay particular attention to the flash converter data sheet, which should list recommended amplifiers and appropriate interface circuits.

Some flash converters have a unipolar negative input voltage range and can be damaged by positive input signals which forward bias the substrate diode. A schottkey diode offers effective protection, as shown in Figure 1.9.

I-14

The value of  $R_s$  should be chosen so that the drive amplifier current is limited to an appropriate value for positive output swings. Making the value of  $R_s$  too large, however, will reduce the bandwidth because of the input capacitance of the flash converter. Figure 1.12 lists a number of flash converters along with recommended drive amplifiers.

| FLASH CONVERTERS AND<br>RECOMMENDED DRIVE AMPLIFIERS |               |                       |         |                    |  |  |  |  |

|------------------------------------------------------|---------------|-----------------------|---------|--------------------|--|--|--|--|

| MODEL                                                | RESOLUTION    | MAX. SAMPLING<br>RATE | INPUT C | DRIVE<br>AMPLIFIER |  |  |  |  |

| AD9688                                               | 4-Bits        | 175 MSPS              | 10pF    | AD5539             |  |  |  |  |

| AD9000                                               | 6-Bits        | 75 MSPS               | 35pF    | AD844              |  |  |  |  |

| AD9006/16                                            | 6-Bits        | 500 MSPS              | 8.5pF   | AD9617             |  |  |  |  |

| AD9048                                               | 8-Bits        | 35 MSPS               | 16pF    | AD847              |  |  |  |  |

| AD9012                                               | 8-Bits        | 75 MSPS               | 16pF    | AD9617             |  |  |  |  |

| AD9002                                               | 8-Bits        | 125 MSPS              | 16pF    | AD9617             |  |  |  |  |

| AD770                                                | 8-Bits        | 200 MSPS              | 19pF    | AD9617             |  |  |  |  |

| AD9028/38                                            | 8-Bits        | 300 MSPS              | 17pF    | AD9617             |  |  |  |  |

| AD9020                                               | 10-Bits (TTL) | 60 MSPS               | 45pF    | AD9617             |  |  |  |  |

| AD9060                                               | 10-Bits (ECL) | 75 MSPS               | 45pF    | AD9617             |  |  |  |  |

| Figure 1.12                                          |               |                       |         |                    |  |  |  |  |

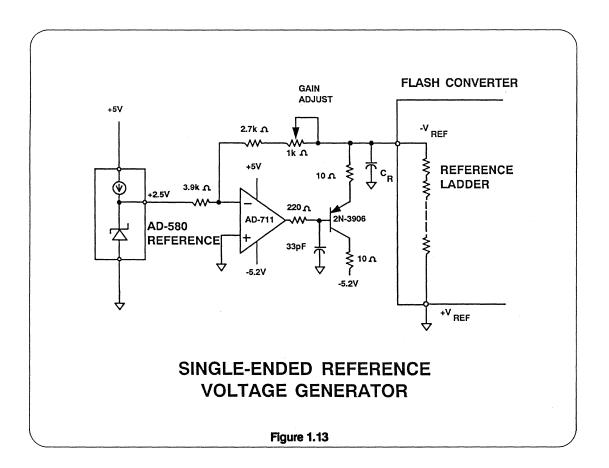

# Flash Converter Reference Voltage Generation

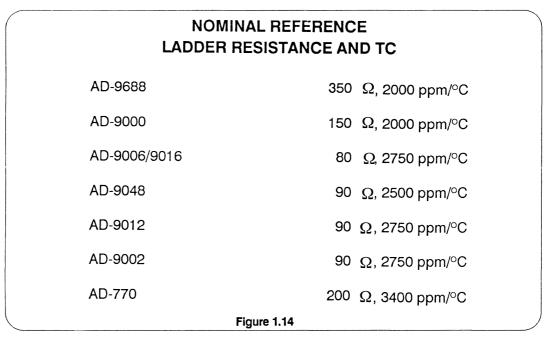

Since few flash converters contain an internal voltage reference, this must be supplied by the user. A typical reference voltage circuit for a flash converter requiring a single -2V reference is shown in Figure 1.13. A buffer transistor is required since the resistance of the ladder string is usually fairly low and, therefore, fairly large drive currents are required. Also, the reference ladder resistance of a flash converter is process dependent and may vary considerably from part to part. It may also have a large temperature coefficient (see Figure 1.14).

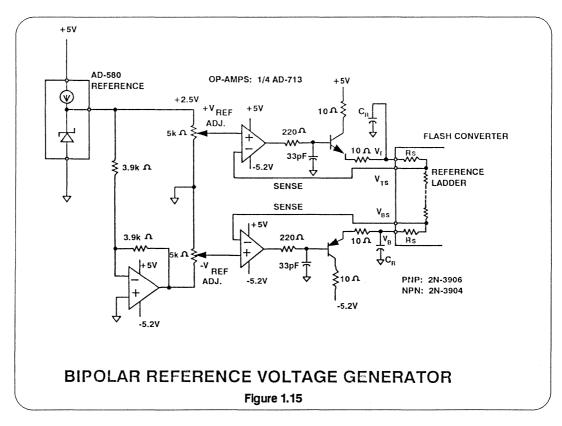

If the flash converter allows bipolar operation (such as the AD-770 and the AD-9000), two reference voltages must be generated. The circuit in Figure 1.15 operates on  $\pm 5V$  power supplies and allows great flexibility in setting the reference voltages for a bipolar flash converter.

Some flash converters have a "sense" pin for the voltage reference which can be used to compensate for the voltage drop due to the package pin and bond wire resistance. This feature is utilized in the circuit shown in Figure 1.15.

Flash converters may provide access to one or more taps along the internal reference ladder resistor string. These

#### taps can be driven from low impedance sources in order to achieve better integral linearity performance. Again, when in doubt, consult the data sheet! Bypass capacitors on the reference voltage inputs are particularly critical at sampling rates of 20MHz or greater. Ceramic chip capacitors are recommended $(0.1 \,\mu\text{F})$ and should be located as close to the pins as possible.

#### Hybrid Circuits Simplify Applications

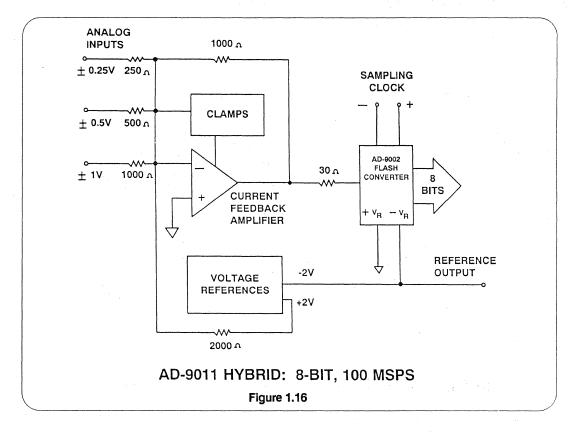

Several hybrid circuit manufacturers have recently introduced hybrid A/D converters which contain a drive amplifier and a reference voltage as well as the flash converter itself. A block diagram of the AD-9011 8-BIT, 100MSPS hybrid A/D converter is shown in Figure 1.16.

I-18

The current-feedback amplifier is designed to recover from an overvoltage condition within 20ns. Clamp limits are set to protect the flash converter input. The current feedback amplifier architecture insures that the bandwidth will remain relatively constant regardless of the gain chosen.

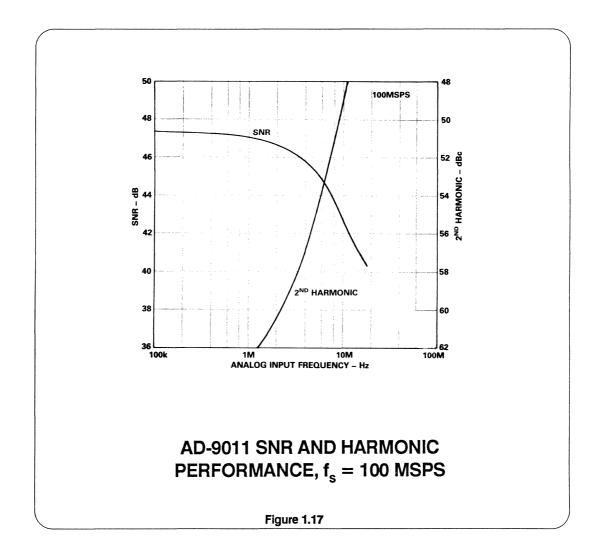

The SNR and harmonic distortion characteristics of the AD-9011 are shown in Figure 1.17.

## Capturing Flash Converter Output Data

At high data rates in excess of 200MHz, buffering flash converter output data can be a major challenge. It is always desirable to follow the flash converter with an appropriate buffer register located as close to the converter as possible.

If the digital outputs of a flash converter are routed directly to a backplane data

bus through a card edge connector, the overall SNR and harmonic performance of the flash converter may be severely degraded by the digital output signals coupling into the analog input.

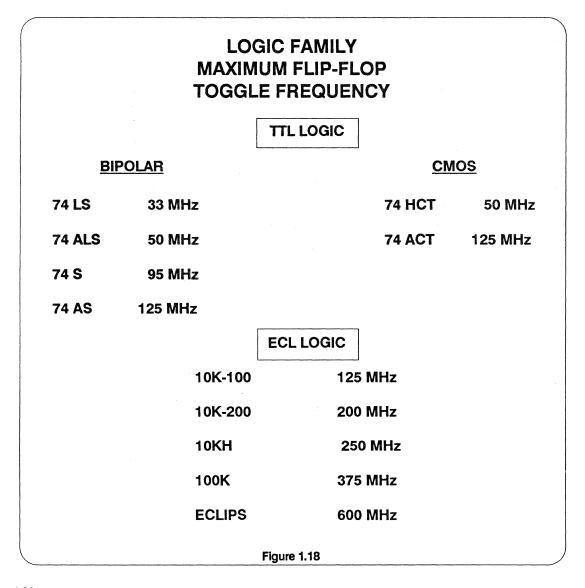

The appropriate logic family can be selected using the information in Figure 1.18.

Proper timing of the buffer register clock with respect to the flash converter sampling clock is best accomplished by following the recommendations on the data sheet. At high data rates, the setup time and hold time specifications on the selected buffer register become particularly important in optimizing the timing for reliable operation.

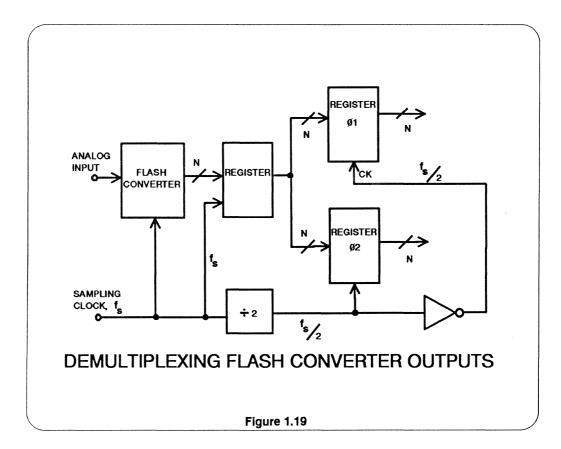

In most applications, flash converter output data is stored in a buffer memory of considerable length. Schemes such as that shown in Figure 1.19 are often used to de-multiplex the high-speed data stream down to frequencies which are appropriate for low cost efficient CMOS or TTL memories.

Some of the newer flash converters which operate at sampling rates greater than 200MHz (such as the AD-9006/9016) will have de-multiplexing on-board to minimize the problems associated with highspeed data storage.

## "Stacking" Flash Converters To Achieve Higher Resolutions

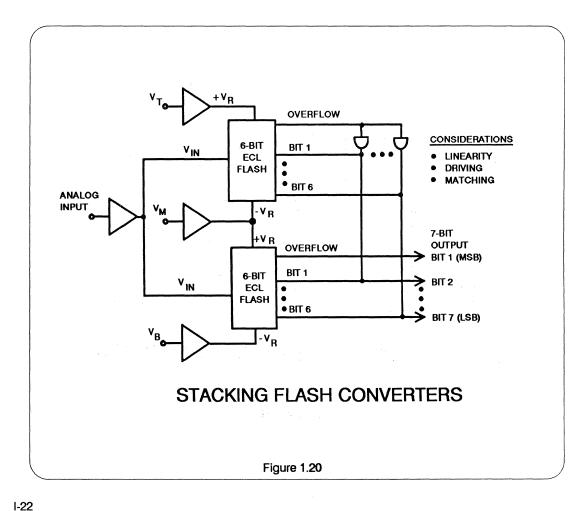

The concept of "stacking" flash converters originated in the late 1970's when the only commercially available flash converters that had sampling rates in excess of 50MHz were 4-or 6-bit devices such as the AMD-6688 (4-bit) and the Seimens SDA-6020 (6-bit). The technique is much less popular today because of the availability of 8-bit 100-200MHz flash converters such as the AD-9002 and the AD-770.

Figure 1.20 shows an application where two 6-bit AD-9000 flash converters have been connected to achieve 7-bit resolution. The six LSB's are obtained by wireoring the 6-bit ECL output of each flash converter -- the MSB is simply the "overflow" output of the bottom flash (the 64th comparator). The overflow output of the top flash converter must be used with additional logic to prevent the six LSB's from going to all zeros when the analog input signal goes out of range positive. Some flash converters have "overflow inhibit" logic which allows them to be used either stacked or unstacked without the need for additional external logic.

Several factors relating to the flash converter's performance must be considered when stacking flashes.

- The flash converter must have the additional "overflow" or 2<sup>Nth</sup> comparator output available.

- ECL output logic levels are desirable to simplify the external logic.

- The flash converter must have the required linearity when operating at the appropriate reference voltage. For instance, if a flash converter is specified as having ±1/2 LSB linearity for a 2-volt reference, it can be assumed that operating the converter at a 1-volt reference would yield ±1 LSB linearity and

produce missing codes. The linearity spec, therefore, needs to be  $\pm 1/4$  LSB for a 2-volt reference in order to consider stacking two converters and still maintain the overall 2-volt reference range.

In order to maintain dynamic performance, the two flash converters need to have well matched comparator delays. This may be difficult to insure since there is no guarantee that the two flash converters come from the same wafer or wafer lot.

In summary, stacking should be avoided except in applications where no other solution is available.

## Reducing Flash Converter Reference Voltage to Achieve Greater Dynamic Range

The effective "gain" of a flash converter can be increased by lowering the reference voltage. However, the same precaution referred to in "stacking" must be observed regarding the flash linearity specification at reduced reference voltages. At least  $\pm 1/2$  LSB linearity should be maintained at the lowest reference voltage. In addition, the maximum reference voltage must not exceed the data sheet spec.

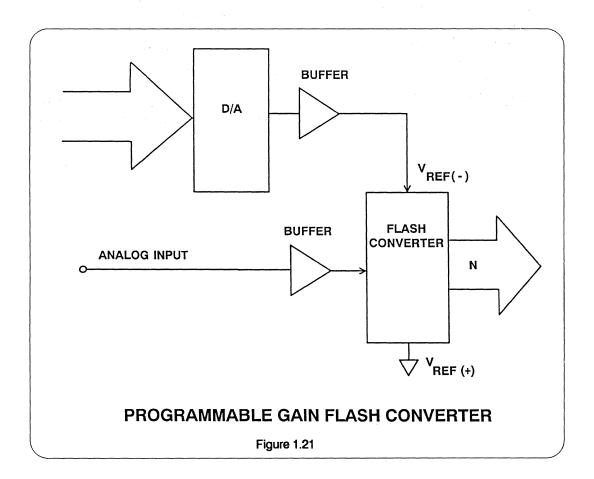

Operating within these constraints, a flash converter can be configured as a Program-

mable Gain A/D converter if the reference voltage is derived from a D/A converter. The gain switching speed can be fairly high since the flash converter reference voltage input bandwidth specification is typically 10MHz or higher. Reference input capacitances are typically less than 50pF and are, in general, slightly higher than the analog input capacitance. A diagram of a variable-gain flash converter circuit is shown in Figure 1.21.

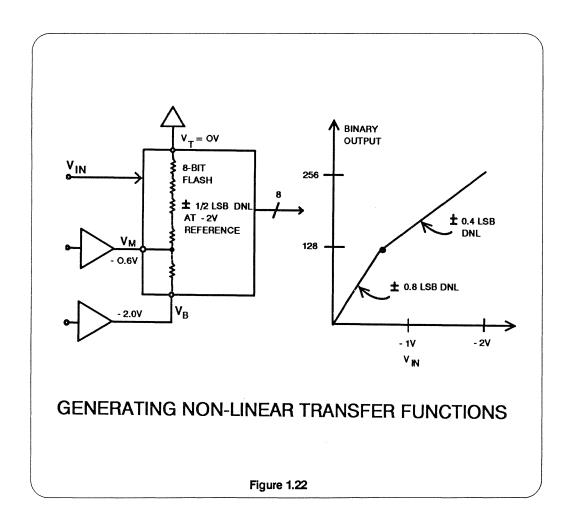

## Generation of Non-Linear Flash Converter Transfer Characteristics

If taps are available on the reference ladder string for a flash converter, a piecewise non-linear input/output transfer function can be generated. Figure 1.22 shows how the AD-9002 might be used in such an application to generate a two-piece transfer curve. In this application, the minimum reference voltage on a portion of the resistor string is that for which the  $\pm 1/2$  LSB linearity spec can still be maintained, and the maximum reference voltage for a portion of the string is governed by the data sheet spec on maximum allowable reference ladder voltage and current.

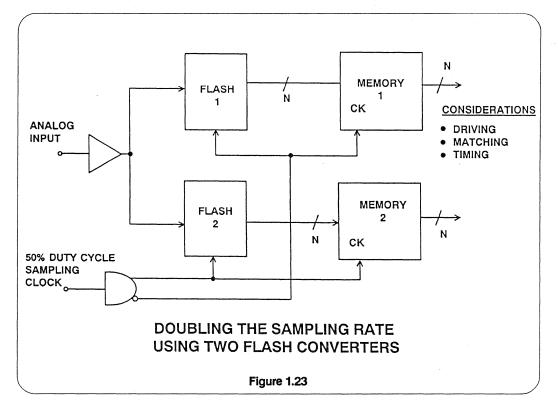

## Using Two Flash Converters With Common Inputs to Double the Sampling Rate

With certain limitations, it is possible to alternate (or "ping-pong") the encode command pulse between two flash converters and effectively double the sampling rate. Figure 1.23 shows such an application. Several factors should be considered in evaluating the merits of this scheme.

- The drive amplifier must be capable of driving the combined impedances of both flash converters to the required dynamic accuracy.

- Although the sampling rate can be doubled using this technique, the individual flash converters must maintain ENOB's, SNR, and harmonic performance at the higher analog input frequencies which will accompany the higher sampling rate. This implies that

each individual flash converter be specified for analog input frequencies which are above the Nyquist rate (super-Nyquist) and which approach the maximum sampling rate.

Delay and bandwidth mismatch between the two flash converters must not be so large as to degrade dynamic performance.  DC differential linearity, integral linearity, gain, and offset matching between the two flash converters should be better than ±1/2 LSB. In summary, it is difficult to use this approach and achieve anything close to Nyquist performance, but the technique may be useful for sub-Nyquist or oversampling applications.

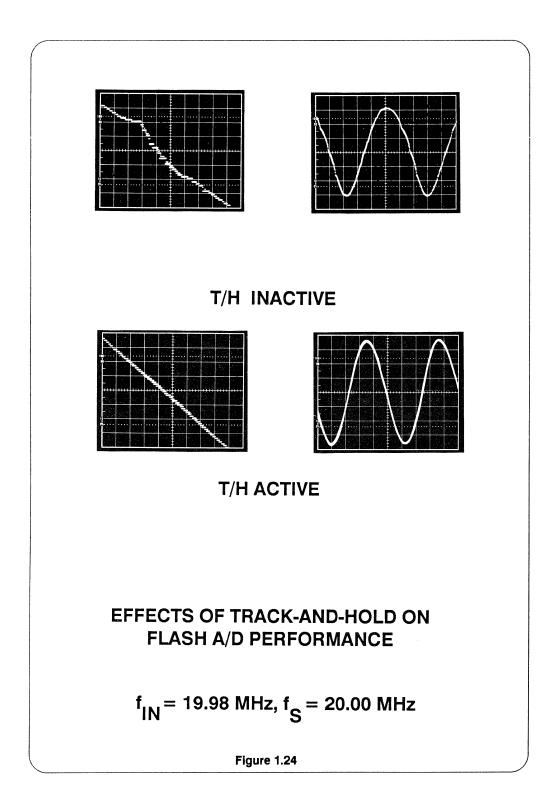

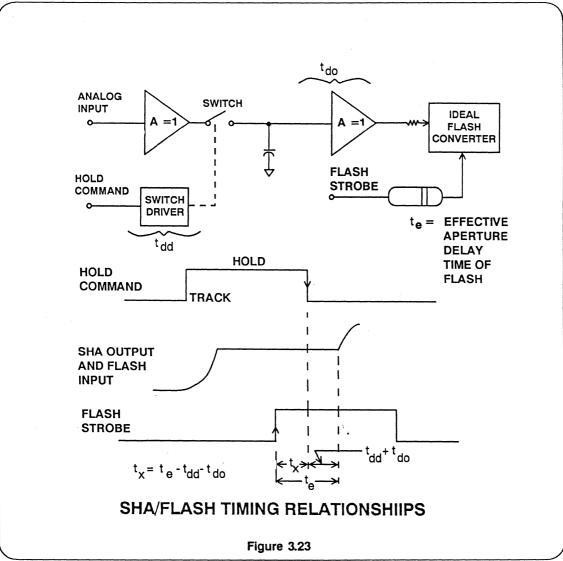

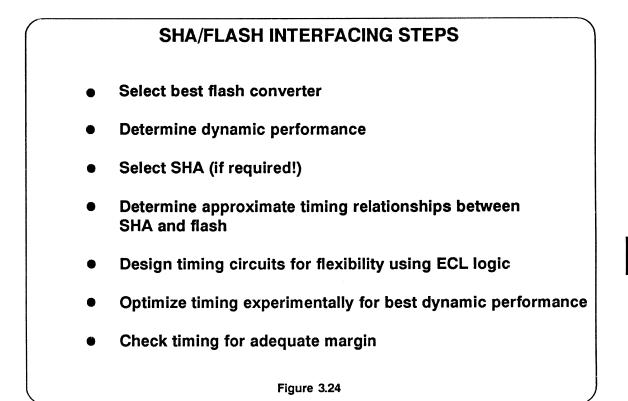

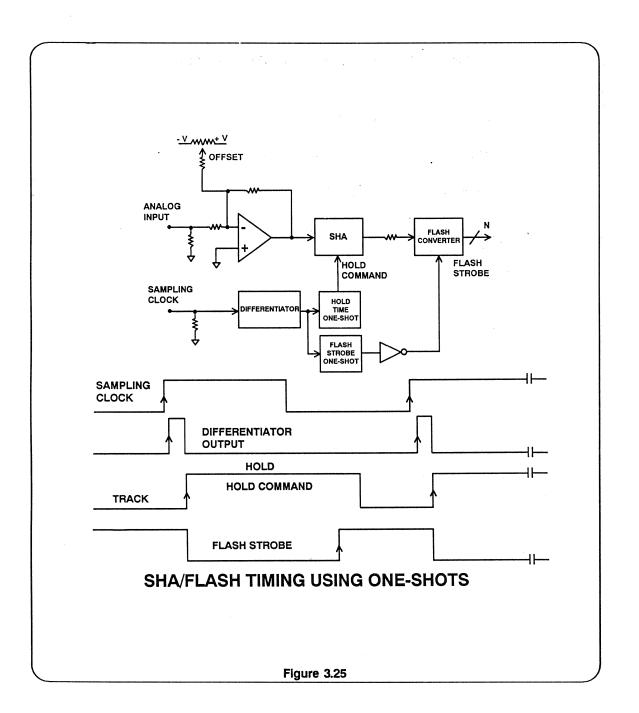

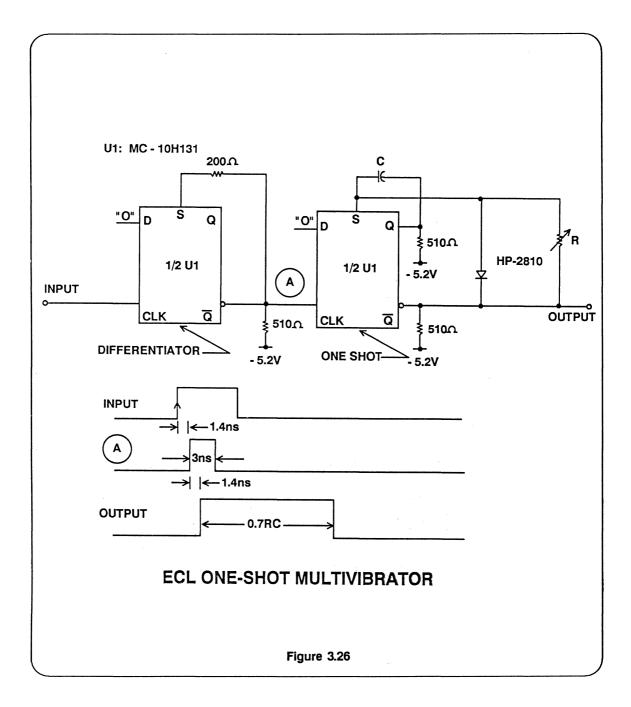

## Use Of Track-And-Hold To Improve Flash Converter Dynamic Performance

As has been previously discussed, the effective sample time delay variations among the latched comparators in a flash converter is a primary source of dynamic errors manifested as degradation in ENOB's, SNR, and harmonic performance. Individual comparators within an array can be visualized as having variable delay lines in series with their latch strobe inputs. To understand the effect of this delay on performance, consider an 8-bit, 100MHz flash converter which is digitizing a fullscale 50MHz sinewave input (Nyquist operation). The sinewave can be expressed as:

$$\mathbf{v}(\mathbf{t}) = \mathbf{V}_{\mathbf{p}} \sin 2 \,\pi \,\mathbf{f} \,\mathbf{t}.$$

The maximum rate-of-change of this signal occurs are the zero-crossing and is given by:

$$\frac{d\mathbf{v}}{dt}\Big|_{\max} = 2\pi \mathbf{f} \mathbf{V}_{\mathbf{p}} \approx \frac{\Delta \mathbf{v}}{\Delta t}\Big|_{\max}$$

Solving for  $\Delta t_{max}$ , we obtain

$$\Delta t_{\rm max} = \frac{\Delta v}{2\pi f V_{\rm p}}$$

If the input voltage range of the flash converter is 2 volts ( $V_p = 1V$ ), the LSB weight is 8mV for an 8-bit flash. For the flash converter error to be less than 1 LSB (8mV), the equation can be solved for  $\Delta t_{max}$ , and the result is

$$\Delta t_{max} = 25 \text{ps}$$

This says that the effective sample delay mismatch between comparators cannot exceed 25ps in order to ensure no missing codes when digitizing a 50MHz fullscale sinewave input.

Placing an ideal track-and-hold ahead of the flash converter would theoretically eliminate this problem since the flash converter would be basically digitizing a DC input (the "held" value of the trackand-hold output). In actual practice, track-and-holds are not ideal -- especially at high speeds. The result is that the signal actually presented to the flash converter is still changing, although at a slower rate. Even this "track-and-slowdown" approach can improve the flash converter performance at sampling rates up to about 25MHz. Above 25MHz sampling rates, the track-and-hold circuit needs to be mounted on the same substrate as the flash converter in a suitable hybrid package. Monolithic track-andholds have been successfully used in conjunction with 8-bit flash converters in hybrid packages to achieve 7 ENOBs at Nyquist inputs sampling at a rate of 250MHz. The penalty is cost and power (7 watts). (Tektronix Model TKAD20C).

Figure 1.24 shows the improvement in dynamic linearity which can be achieved by putting a hybrid track-and-hold (HTS-0025) ahead of an older flash converter (TDC-1007).

Nevertheless, the user should strive to select a flash converter which does not need a track-and-hold in order to achieve the desired dynamic performance required for the particular application. The performance of the track-and-hold/flash converter pair is almost impossible to determine from the separate data sheet specifications alone, and considerable experimentation may be required to achieve the desired results. The optimum timing relationship between the two devices will also be difficult to determine without considerable experimentation.

In the future, lower cost monolithic trackand-holds will be packaged with the flash converters in high performance hybrids, and be fully specified for dynamic characteristics. For most applications, however, improvements in flash converter designs and IC processes will probably eliminate the need for a separate track-and-hold except for the most exacting user.

-----

.

## FLASH CONVERTER SELECTION GUIDE

| RESOLUTION | MODEL       | MAXIMUM<br>SAMPLING RATE (MSPS) |

|------------|-------------|---------------------------------|

| 4-Bits     | AD9688      | 175 - ECL                       |

| 6-Bits     | AD9000      | 75 - ECL                        |

| 6-Bits     | AD9006/9016 | 500 - ECL                       |

| 8-Bits     | AD9048      | 35 - TTL                        |

| 8-Bits     | AD9012      | 75 - TTL                        |

| 8-Bits     | AD9002      | 125 - ECL                       |

| 8-Bits     | AD770       | 200 - ECL                       |

| 8-Bits     | AD9028/9038 | 300 - ECL                       |

| 8-Bits     | AD9011*     | 100 - ECL                       |

| 10-Bits    | AD9020      | 60 - TTL                        |

| 10-Bits    | AD9060      | 75 - ECL                        |

|            |             |                                 |

## \*HYBRID WITH INTERNAL AMP, REFERENCES

Figure 1.25

1-30

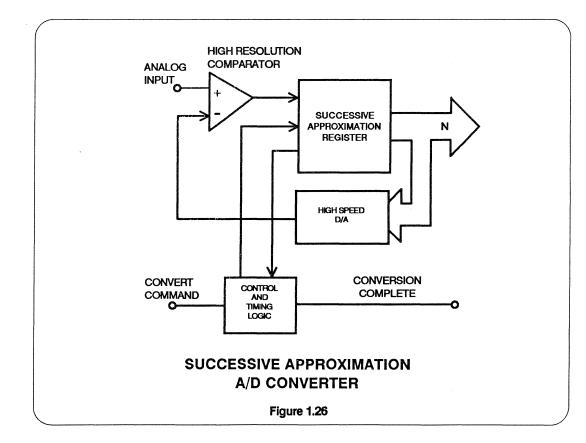

## SUCCESSIVE APPROXIMATION A/D CONVERTERS -Basic Operation

This A/D converter architecture has been the "workhorse" in the industry primarily because it combines relatively high resolution and speed with low cost. New IC process developments in CMOS allow 12-bit, 3  $\mu$ sec. converters to be achieved in monolithic form (AD-7672). In the past, this performance was only available from more expensive hybrid and modular products. A block diagram of a successive approximation A/D converter is shown in Figure 1.26. The building blocks consist of a comparator, D/A converter, and control logic (successive approximation register, or SAR). The overall static accuracy is primarily determined by the D/A converter.

The analog input drives one input of the comparator, while the D/A converter output is connected to the other input. The conversion technique consists of comparing the unknown input against a precise voltage or current generated by a D/A converter. The input of the D/A converter is the digital number at the A/D converter's output. The conversion process is strikingly similar to a weighing process using a chemist's balance, with a set of N binary weights (e.g., 1/2 lb, 1/4 lb, 1/16 lb (=1 oz), 1/2 oz, 1/4 oz, etc., for unknowns up to 1 lb.)

After the conversion command is applied, and the converter has been cleared, the D/A converter's MSB output (1/2 full scale) is compared with the input. If the input is greater than the MSB, it remains ON (i.e., "1" in the output register), and the next bit (1/4 FS) is tried. If the input is less than the MSB, it is turned OFF (i.e., "0" in the output register), and the next bit is tried. If the second bit doesn't add enough weight to exceed the input, it is left ON ("1") and the third bit is tried. If the second bit tips the scales too far, it is turned OFF ("0") and the third bit is tried. The process continues in order of descending bit weight until the last bit has been tried. The process completed, the conversion complete line changes state to indicate that the contents of the output register now constitute a valid conversion. The contents of the output

register form a binary digital code corresponding to the input signal's magnitude.

Each of the bit decisions requires a clock period. An N-bit converter will have N clock periods (plus an initialization period). Thus, the minimum conversion time of the A/D will be determined by the maximum allowable clock frequency. This frequency is limited by several factors: SAR clock-to-data-output delay, D/A settling time, comparator settling time, and SAR input data setup time. Hybrid 12-bit SAR A/D converters are available which have total conversion times approaching 1µsec.

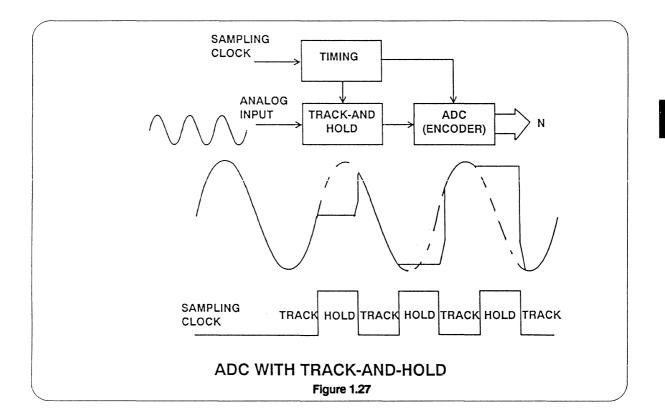

During the conversion time, it is important that the analog input signal be held constant. This requires that a SAR A/D converter be preceded with an appropriate track-and-hold if dynamic signals are to be digitized. Figure 1.27 shows a typical configuration. As has been previously discussed, it is difficult to determine the overall dynamic performance of this system by examining the separate data sheets for the track-and-hold and the SAR A/D (sometimes called the "encoder"). A more desirable solution is to purchase a "sampling" A/D converter where the track-and-hold, encoder, and appropriate timing circuits are contained in a single package which is fully specified for dynamic performance.

## SUCCESSIVE APPROXIMATION A/D CONVERTER SELECTION GUIDE

| ENCODERS (NO T/H)                  |            |                 |            |  |

|------------------------------------|------------|-----------------|------------|--|

| RESOLUTION                         | MODEL      | CONVERSION TIME | TECHNOLOGY |  |

| 12-Bits                            | AD-7572    | $5\mu$ sec      | IC-CMOS    |  |

| 12-Bits                            | AD-7672    | 3 µsec          | IC-CMOS    |  |

| 12-Bits                            | HAS-1202-A | 1.86 $\mu$ sec  | Hybrid     |  |

| 12-Bits                            | AD-1377    | 10 $\mu$ sec    | Hybrid     |  |

| SAMPLING A/D CONVERTERS (WITH T/H) |            |                 |            |  |

| RESOLUTION                         | MODEL      | SAMPLING RATE   | TECHNOLOGY |  |

| 12-Bits                            | HAS-1204   | 500 kHz         | Hybrid     |  |

| 12-Bits                            | AD-7878    | 100 kHz         | IC-CMOS    |  |

| 14-Bits                            | AD-7871    | 83 kHz          | IC-CMOS    |  |

| 16-Bits                            | AD-1380    | 50 kHz          | Hybrid     |  |

| Figure 1.28                        |            |                 |            |  |

diana.

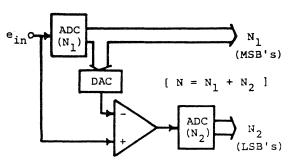

## SUBRANGING A/D CONVERTERS -Basic Operation

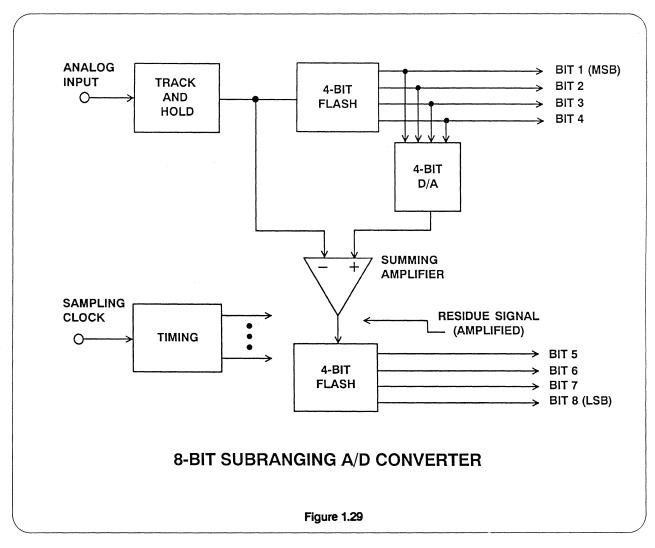

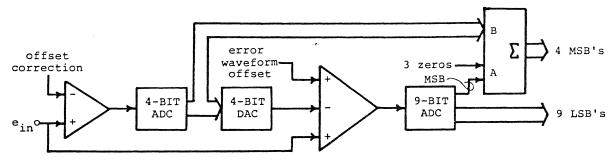

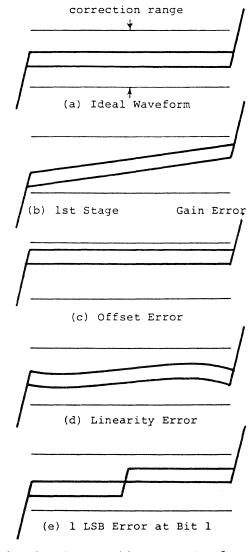

A block diagram of an 8-bit subranging A/D converter based upon two 4-bit flash converters is shown in Figure 1.29. The conversion process is done in two steps. The first four significant bits (MSBs) are digitized by the first flash (to better than 8-bits accuracy), and the 4-bit binary output is applied to a 4-bit D/A converter (better than 8-bit accurate). The D/A converter output is subtracted from the held analog input, and the resulting residue signal is amplified and applied to the second 4-bit flash converter by the summing amplifier. The outputs of the two 4-bit flash converters are then combined into a single 8-bit binary output word. If the amplified residue signal doesn't exactly fill the range of the second flash converter, non-linearities and missing codes will result.

1-34

## Subranging A/D Converters -Error Sources

The following sources can contribute to errors in the basic subranging A/D converters:

## SUBRANGING ERROR SOURCES

- First flash converter gain, offset, and linearity errors.

- D/A converter gain, offset, and linearity errors.

- D/A converter settling time.

- Summing amplifier gain, offset, and settling time errors.

- Second flash converter gain, offset, and linearity errors.

#### Figure 1.30

These errors are very troublesome at the "subranging" points and can contribute to non-linearities and missing codes in the overall A/C converter transfer func-

-----

tion. Modern subranging A/D converters use a technique called "digital correction" to eliminate most of these problems.

## DIGITALLY CORRECTED SUBRANGING (DCS) A/D CONVERTERS -Basic Operation

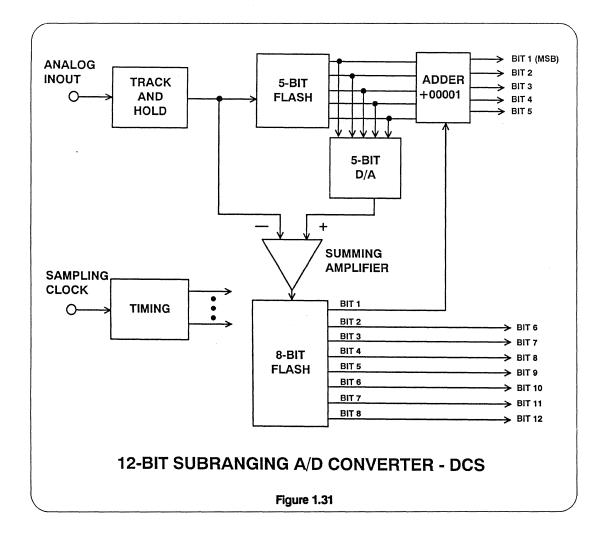

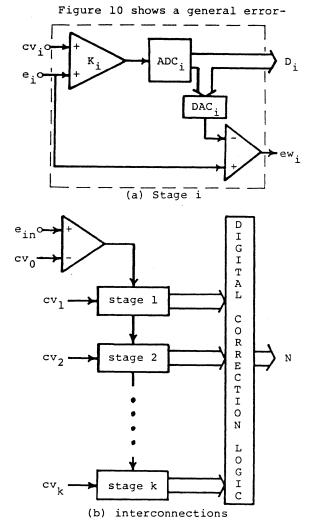

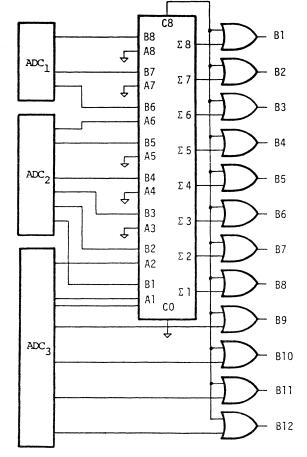

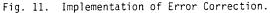

A block diagram of a 12-bit DCS A/D converter is shown in Figure 1.31. Note that a 5-bit and an 8-bit flash converter have been utilized to achieve a 12-bit DCS output. If there were no errors, the 5-bit "residue" signal applied to the 8-bit flash converter by the summing amplifier would never exceed one-half of the range of the 8-bit flash. The extra range in the second flash converter is used in conjunction with the error correction logic (usually just an adder) to correct the output data for most of the errors inherent in the traditional uncorrected subranging converter previously discussed. An in-depth treatment of DCS A/D converter operation and design is given in the article entitled "Multistage Error Correcting A/D Converters".

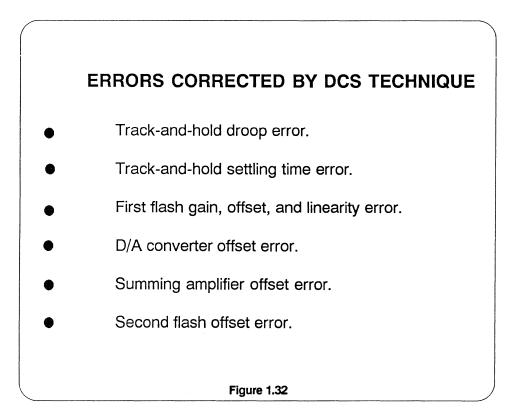

The following error sources can be corrected by proper use of this technique:

Proper use of the DCS technique will either correct for the above errors or translate them into either a gain and/or offset error in the transfer function of the overall A/D converters.

This technique is ideally suited to highspeed cost-effective A/D converters and

and the second

has been used successfully in card-level, hybrid, and monolithic A/D converters. These products have on-board track-andhold functions and are completely specified in terms of both static and dynamic performance characteristics.

| DCS A/D CON | VERTER |

|-------------|--------|

| SELECTION   | GUIDE  |

## SAMPLING A/Ds (WITH T/H)

| RESOLUTION        | MODEL      | SAMPLING RATE   | TECHNOLOGY |  |

|-------------------|------------|-----------------|------------|--|

| 10-Bits           | CAV1040    | 40 MHz          | PC Card    |  |

| 12-Bits           | AD1678/678 | 200 kHz         | IC         |  |

| 12-Bits           | AD9003     | 1 MHz           | Hybrid     |  |

| 12-Bits           | AD9005     | 10 MHz          | Hybrid     |  |

| 12-Bits           | CAV1220    | 20 MHz          | PC Card    |  |

| 14-Bits           | AD1679/679 | 100 kHz         | IC         |  |

| 14-Bits           | AD1779/779 | 100 kHz         | IC         |  |

| 14-Bits           | AD9014     | 10 MHz          | PC Card    |  |

| ENCODERS (NO T/H) |            |                 |            |  |

| RESOLUTION        | MODEL      | CONVERSION TIME | TECHNOLOGY |  |

| 12-Bits           | AD671      | 500 ns          | IC         |  |

|                   |            |                 |            |  |

|                   |            |                 |            |  |

| Figure 1.33       |            |                 |            |  |

I-38

# A/D CONVERTER APPLICATIONS

erstern Leistern aus

## UNDERSAMPLING, SUPER-NYQUIST, AND DOWN CONVERSION APPLICATIONS

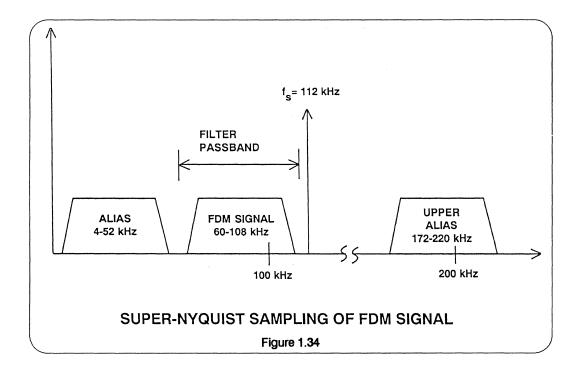

When the analog signal being digitized by an A/D converter exceeds one-half the sampling rate, the condition is often referred to as "super-Nyquist" or "undersampling". Nyquist's criterion state that the <u>bandwidth</u> (not the actual frequency) of the signal being digitized should not exceed one-half the sampling rate for all information to be preserved. As an example, consider a telecommunications transmultiplexer application where Frequency Division Multiplexed (FDM) data occupying the bandwidth of 60 to 108kHz is sampled at a frequency of 112kHz. Figure 1.34 shows the spectrum of the signal and the location of the "aliased" components. At the receiving end of the system, the filter which follows the reconstruction D/A converter is a bandpass rather than a lowpass and must filter out the "aliased" components falling between 4kHz and 52kHz as well as the component located at the sampling frequency of 112kHz.

Operation of an A/D converter in super-Nyquist applications obviously requires that the dynamic performance of the converter be known for input frequencies <u>above</u>  $f_g/2$ . The SNR, ENOB, and harmonic performance of an A/D converter typically degrades as the input frequency is increased and may render the converter useless for super-Nyquist applications. For example, it may be necessary to use a track-and-hold ahead of a flash converter in order to achieve acceptable dynamic performance.

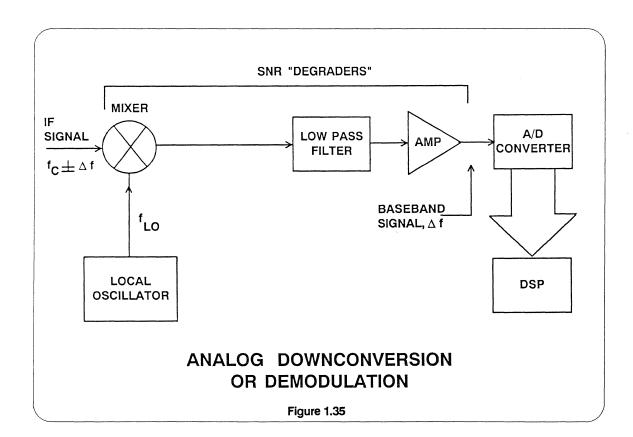

Another application for "super-Nyquist" operation is in the direct conversion of IF

signals to baseband. Most traditional communication and radar receivers employing A/D converters utilize a system in which the intermediate frequency (IF) from the front end of the receiver is down-converted to a baseband signal by a mixer (see Figure 1.35). This final IF stage uses a local oscillator which is phase coherent with the signal carrier frequency. The mixer output contains a baseband signal which is proportional to the phase difference between the two inputs. Following the mixer is a lowpass filter, DC amplifier, and an A/D converter.

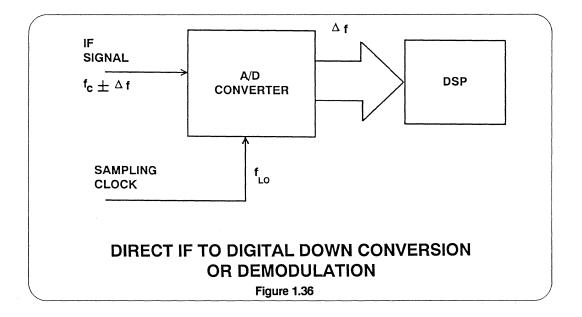

Typical mixers have a conversion loss ranging from 4 to 6dB. In cases when the signal-to-noise ratio is limited by the front end, elimination of the mixer will improve the overall noise figure of the receiver. This can be accomplished (as shown in Figure 1.36) if the IF signal is sampled at a rate which is equal to the local oscillator frequency. The A/D converter now looks like a demodulator. If the A/D converter samples an analog signal of the same frequency as the sampling frequency, the digitized output is a DC value. Any deviation in the analog signal from the sampling frequency looks like a "beat" frequency, and the demodulation process is thereby achieved.

The data from the A/D converter must be processed using an FFT which computes both the real and imaginary components of the digitized signal. This is necessary in order to preserve the phase information contained in the demodulated signal. The total bandwidth of the signal to be demodulated must be less than f/2 in order not to violate the Nyquist criterion.

## OVERSAMPLING APPLICATIONS

- 10 - A.W.

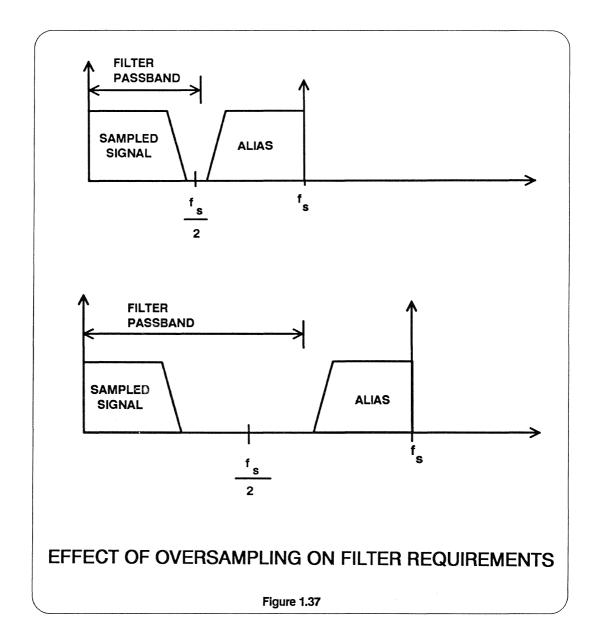

The technique of sampling a signal at greater than twice its maximum frequency (called "oversampling") has several advantages in A/D converter applications. Increasing the sampling rate beyond the Nyquist rate  $f_s/2$  makes the design of the anti-aliasing filter preceding the A/D converter much easier, as shown in Figure 1.37.

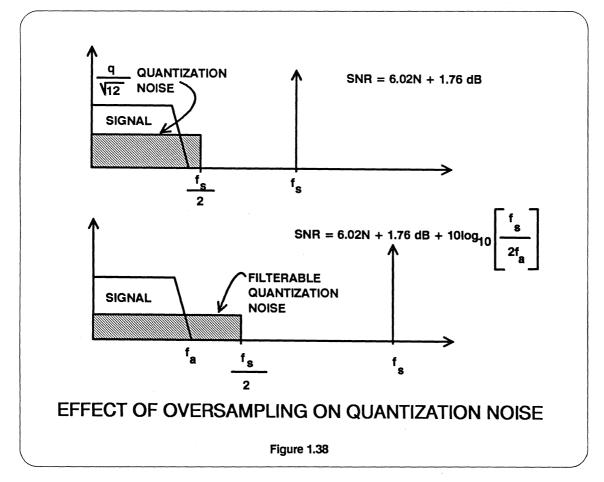

Also, the effective SNR can be improved by oversampling, as shown in Figure 1.38. For a given sampling rate  $f_s$ , the theoretical RMS quantization noise in the bandwidth f/2 is given by  $q \wedge 12$ , where q is the weight of the least significant bit. (See derivation given in Reference 15.) From this, the theoretical formula for the SNR of an N-bit A/D converter (SNR = 6.02N + 1.76dB) can be easily derived. If the signal bandwidth  $f_a$  is held constant, and the sampling rate is increased, the effect is to "spread" the quantization noise over a wider bandwidth, thereby reducing the RMS noise in the analog bandwidth,  $f_2$ . The exact expression for the fullscale sinewave SNR under these conditions is given by

$$SNR = 6.02N + 1.76dB + 10\log_{10} \left[\frac{f_s}{2f_a}\right]$$

where  $f_s$  is the sampling rate and  $f_a$  is the analog bandwidth of interest. It can be seen that doubling the sampling rate for a constant analog bandwidth has the effect of increasing the SNR by 3dB or increasing the ENOBs by 1/2 bit. Digital post processing of the quantized data in conjunction with a digital lowpass filter of bandwidth  $f_a$  is usually used to obtain this improvement. The noise power in the bandwidth  $f_a$  to  $f_s/2$  is removed by the digital filter. See pp. 15-22 of the February 1988 **Hewlett-Packard Journal** for further discussion of this topic.

1-44

#### Absolute Peak Detector

Sec. 1 Dela

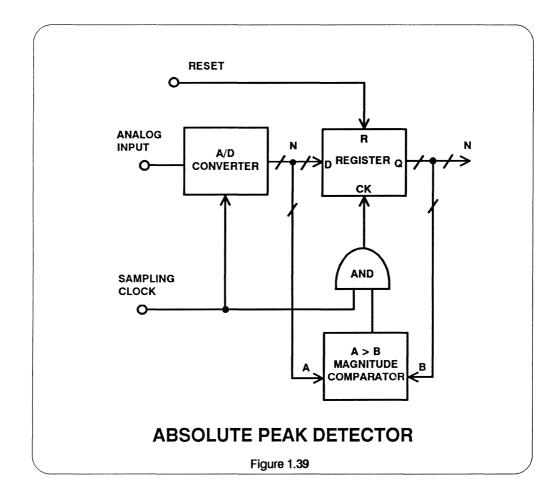

An absolute peak detector circuit is shown in Figure 1.39. A reset pulse is first applied to the register at the start of the time period. The A/D converter sampling clock is then initiated. The A/D converter output will only be clocked into the register if it is greater than the previous sample. In this way, the largest sample during the sampling window is always stored in the register. At the end of the period, the sampling clock is stopped, and the peak value is read. The sampling rate must be substantially higher than the analog input frequency in order to capture the peak of interest.

1-45

## APPLICATIONS OF DITHERING

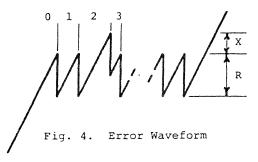

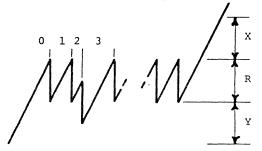

The assumption of a random quantization error signal which is independent of input signal allows an easy derivation of the familiar expression  $q/\sqrt{12}$  (q=1LSB) for the RMS quantization noise (within the Nyquist bandwidth) of an ideal A/D converter. For a sinusoidal input, however, the A/D converter output error is actually composed of a large number of harmonics of the input frequency. These harmonics (regardless of frequency) all appear within the Nyquist bandwidth (due to aliasing produced by the sampling process). If the power of all these harmonics is summed, the RMS quantization power is accurately given by  $q/\sqrt{12}$ .

Since the error waveform produced by the quantization of a periodic waveform is itself periodic, and appears as harmonic distortion of tones present at the A/D converter input, this situation is highly undesirable in spectral analysis applications. In receiver application especially, it is more desirable to have the quantization noise power spread uniformly over the Nyquist bandwidth rather than concentrated in a discrete set of spectral lines. Also, the harmonics present in the error waveform are coherently related to the A/D input waveform. This further complicates the task of processing the signal spectrum to differentiate between signals and system-induced spurious components, especially when "searching" the spectrum for the presence of low-level signals in the presence of large signals.

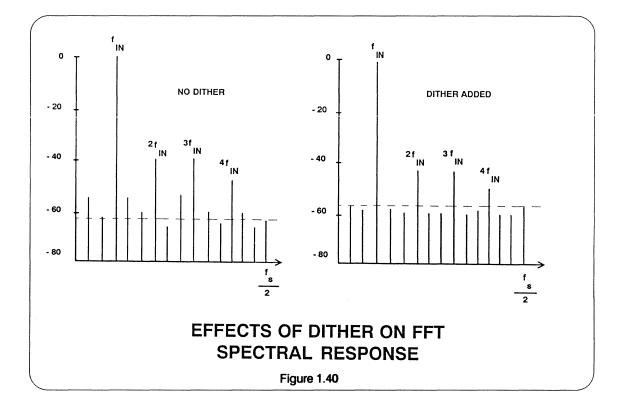

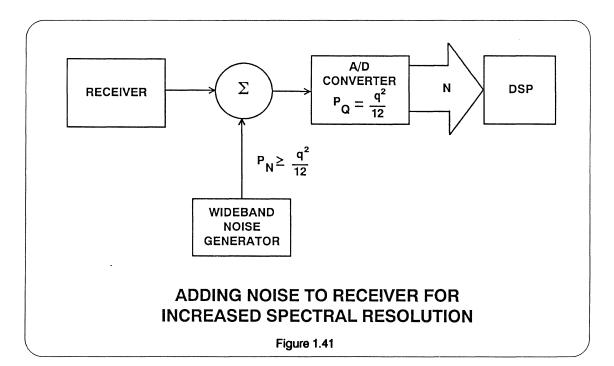

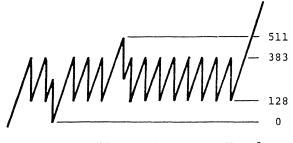

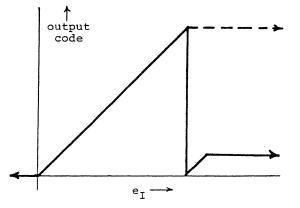

If random noise which has a flat spectrum over the Nyquist bandwidth (dither) is added to the A/D input signal, the effect is to randomize the quantization noise, provided the random noise voltage is at least  $q/\sqrt{12}$ . Obviously, this has the effect of degrading the overall SNR by 3dB, but also has the effect of destroying any statistical correlation between sample errors. The composite noise spectrum at the A/D converter output is thus made flat over the Nyquist bandwidth. The actual noise level which provides optimum performance is very A/D and application dependent, but typically is chosen to be several dB greater than  $q/\sqrt{12}$ . The effects of adding noise to a digitized sinewave is shown in Figure 1.40. The process of adding random noise to the input signal is referred to as *dithering*.

In a receiver application, the front-end gain can be adjusted so that the actual receiver noise present at the A/D input is at the correct level to randomize the quantization error as shown in Figure 1.41.

It should also be remembered that dither can be introduced into the system by phase jitter on either the sampling clock or the input sinewave. Either of these will have the effect of increasing the overall noise floor. See the section on Aperture Jitter for further discussion.

Sophisticated dithering signals (other than random noise) have been used in conjunction with digital filtering and processing to achieve improvements in A/D converter performance without degrading SNR performance. This is accomplished by adding the appropriate dither signal to the A/D input and then subtracting it from the A/D output. A detailed discussion of this technique is given on pp. 70-76 in the June 1988 Hewlett-Packard Journal.

an 1993 S. S. Stan. Security and Mathematical State

## MULTIPLEXING APPLICATIONS

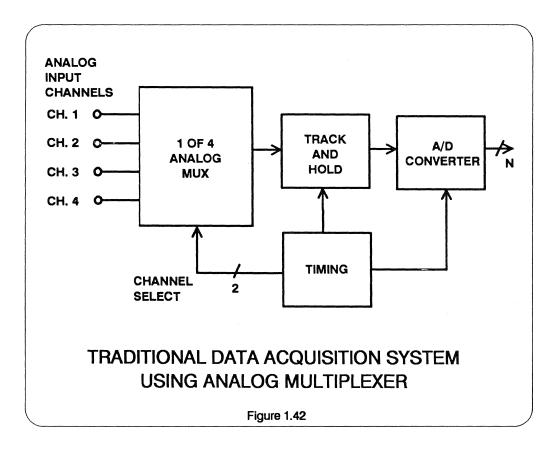

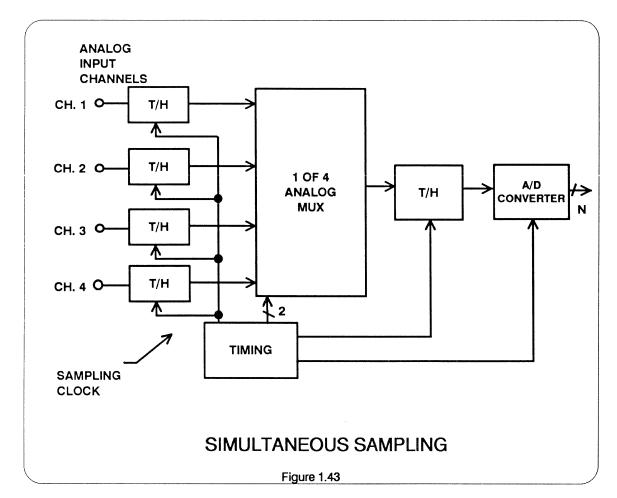

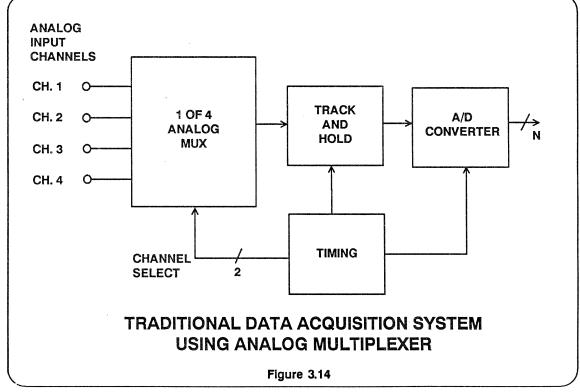

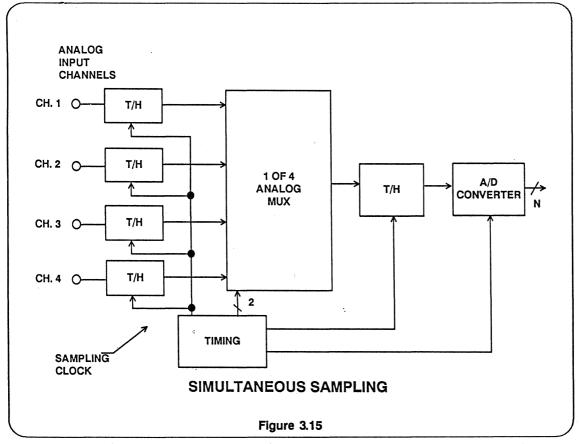

Multiplexing many channels of analog data into a single A/D converter is quite common in low-speed data acquisition systems, and a classical block diagram is shown in Figure 1.42. A variation on this scheme, called "simultaneous sampling" is shown in Figure 1.43, where track-andhold amplifiers are kept in the "hold" mode long enough for the multiplexer to sequence each channel into the A/D converter. These schemes have proven to offer a cost-effective solution to low speed multi-channel digitization, primarily because only one A/D converter (usually the most expensive part) is required.

With the advent of high-speed A/D converters and faster analog multiplexer/ switches, it is tempting to apply the same architecture to high-speed data acquisition systems. The user should be aware of several potential problems associated with using this approach at video speeds.

- There is no way to guarantee the per-channel dynamic performance (SNR, ENOB, etc.) based on the individual component specifications alone.

- Multiplexer settling time and A/D converter transient response become critical specifications.

Remember that the multiplexer output can present a fullscale

sample-to-sample change to the A/D converter analog input. If the multiplexer and A/D converters have not both settled to the required accuracy, DC channel-tochannel "crosstalk" will result.

• AC crosstalk between channels is much more of a problem when digitizing video speed signals.

In summary, the use of A/D converters on a per-channel basis is definitely the preferred solution for multichannel data acquisition systems at video speeds.

## A/D CONVERTER DYNAMIC SPECIFICATIONS AND TESTING

- DSP Testing

- Quantization Theory

- DFTs and FFTs

- Signal to Noise Ratio

- Harmonic Distortion

- Two Tone Intermodulation Distortion

- Spurious Free Dynamic Range

- Coherent Sampling

- Non-Coherent Sampling

- Windowing

- Sinewave Curve Fit

- Beat Frequency Tests

- Histogram Tests

- Noise Power Ratio

- Transient Response

- Overvoltage Recovery

- Aperture Time

- Composite Video Tests

- Error Rates

## DSP TESTING OF A/D CONVERTERS

With the advent of "sampling" A/D converters, much emphasis has been placed on the dynamic performance of the converter when digitizing rapidly changing signals. The particular dynamic specifications of interest may very widely with the application as shown in Figure 1.45.

## ANALOG-TO-DIGITAL DYNAMIC SPECIFICATIONS VS. APPLICATIONS

#### **SPECIFICATION**

Effective number of bits (ENOB)

Signal-to-noise ratio (SNR)

AC linearity

Noise power ratio (NPR)

Two-tone intermod distortion

Transient response

Overvoltage recovery

Aperture jitter

Differential gain and phase

**Error Rate**

Spurious free dynamic range (SFDR)

#### APPLICATION

All

Radar, communications, spectrum analysis

Radar, spectrum analysis

Communications

Radar, spectrum analysis

Transient analysis, radar, multiplexing

Radar

All

Television

Radar, transient analysis, communications

Communication receivers, spectrum analysis

Figure 1.45

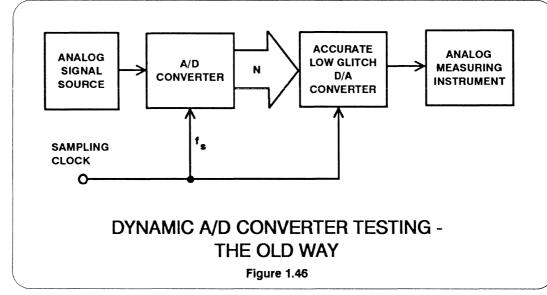

In the early days of video speed A/D converters, most dynamic testing was done in the analog realm using a high

performance D/A converter to reconstruct the output of the A/D converter, as shown in Figure 1.46.

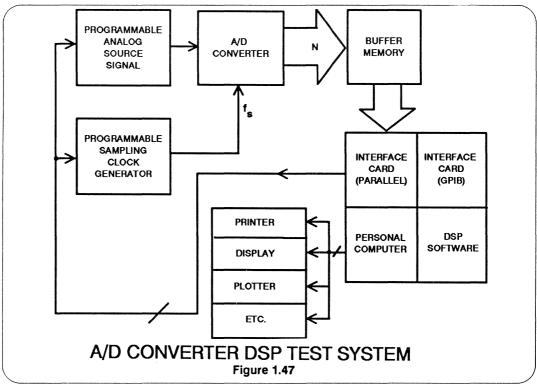

Today, it is possible to perform sophisticated DSP tests (such as FFTs, AC histograms, etc.), using test systems based upon user-friendly personal computers and standard software packages. The PCbased test system shown in Figure 1.47 is capable of performing a 1024-point FFT in less than one second.

I-53

Some key features of this system are shown in Figure 1.48. Specialized A/D converter DSP test systems are currently being offered by large ATE manufacturers such as Teradyne and LTX. These systems are well suited to large volume IC production applications, but are too costly for the end user. Other less expensive benchtop systems are now available from companies such as Tektronix and Hewlett-Packard which allow the end user to implement DSP testing of A/D converters not only at low cost but with a minimum of hardware and software development effort. Manufacturers of video speed A/D converters such as Analog Devices are supplying product-specific evaluation boards to allow customers to easily interface the A/D converter with their DSP test system. The evaluation boards contain reference voltages, power supply decoupling, timing circuits, output registers, connectors, etc., in order to make performance evaluations as easy as possible. In addition, the evaluation boards usually have a matching D/A converter which is useful in determining the overall functionality of the A/D converter.

| PC-BASED TEST SYSTEM |                                   |  |

|----------------------|-----------------------------------|--|

| Personal Computer:   | AT&T PC-6300                      |  |

| Co-Processor:        | 8087                              |  |

| Storage:             | 20 MByte Hard Disk Drive          |  |

| Interface Card:      | Metrobyte PIO-12, 24-bit Parallel |  |

| Operating Software:  | Microsoft "Quickbasic"            |  |

| FFT Software:        | Micro Way "87 FFT"                |  |

| Figure 1.48          |                                   |  |

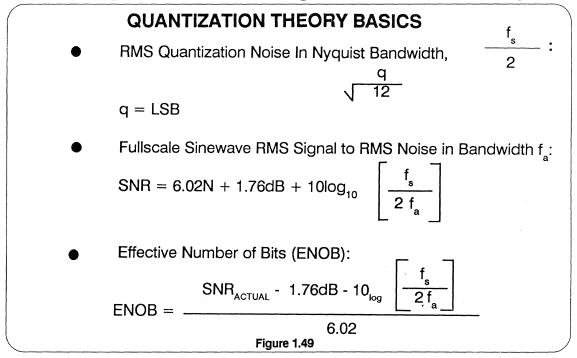

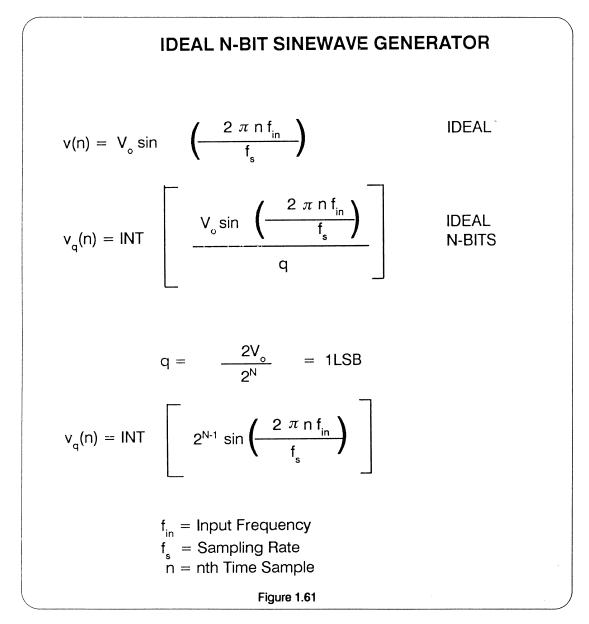

## QUANTIZATION THEORY

The RMS noise voltage measured within the Nyquist bandwidth for an ideal A/D converter is given by the familiar expression  $q^{\lambda}$  12, where q is the weight of the LSB. This value is also independent of input signal frequency and amplitude.

For a fullscale sinewave input, it can be shown that the theoretical RMS signal to quantification noise ratio is given by

$SNR = 6.02N + 1.76dB + 10\log_{10} \left[ \frac{I_s}{2f_a} \right]$

where N = number of bits,  $f_s$  = sampling rate, and  $f_a$  = analog bandwidth. The third term in the above equation represents the increase in SNR due to oversampling, as previously discussed. The classical deviation of these expressions can be found in the following reference:

> W.R. Bennett, "Spectra of Quantized Signals" <u>BSTJ</u> 27, pp. 446-472, July 1948.

-----

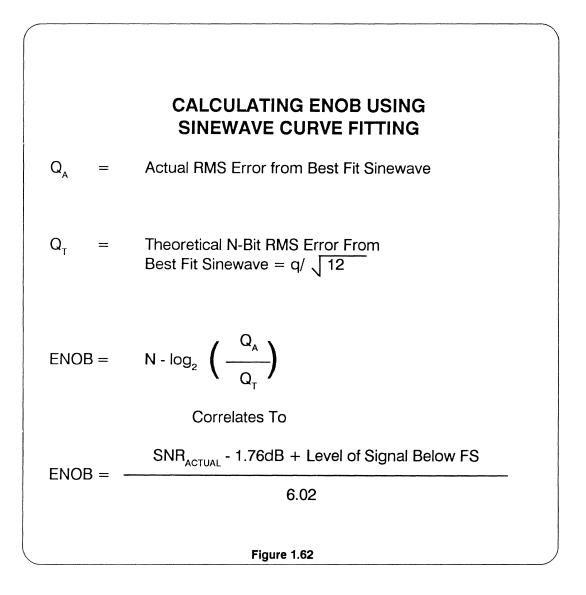

Practical A/D converters exhibit errors which are due to static and dynamic nonlinearities. These dynamic errors increase as input slew-rates become greater. The actual SNR measurement will, therefore, be less than theoretical, and it is useful to calculate the effective number of bits (ENOB) by solving the above equation for N:  $\begin{bmatrix} \mathbf{f}_s \end{bmatrix}$

$\text{ENOB} = \frac{5 \text{SNR}_{\text{ACTUAL}} - 1.76 \text{dB} - 10 \log_{10}}{6.02} = \frac{2 \text{f}_{a}}{6.02}$

Note that when the "noise" is calculated using DFT techniques, it includes not only quantization noise but also the harmonics of the input sinewave. Harmonics which fall outside the Nyquist bandwidth are "aliased" back into the Nyquist bandwidth because of the sampling process.

Sinewaves are the most popular signals for evaluating A/D converter dynamic performance because of their ease of generation and mathematical analysis.

1-55

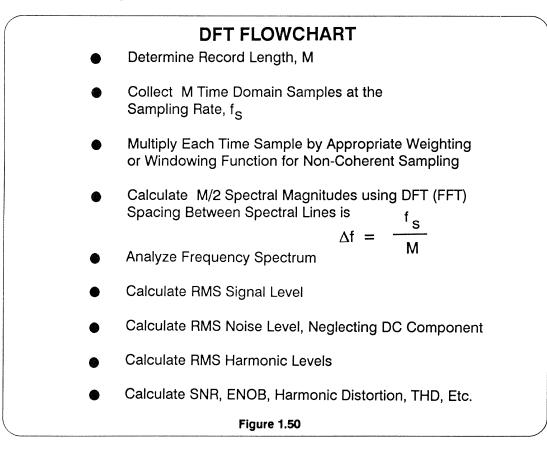

# DISCRETE AND FAST FOURIER TRANSFORMS

The discrete fourier transform (DFT) in the digital domain is analagous to spectrum analysis in the analog domain. The DFT is a mathematical operation which is performed on a finite record of contiguous discrete time samples to produce an equivalent number of frequency samples. Both signal level, noise levels, and harmonic content can then be calculated from the DFT output. The fast fourier transform (FFT) is simply an algorithm which is used to greatly reduce the number of mathematical calculations (and thereby the processing time) required to obtain the DFT output spectrum. An excellent in-depth treatment of DFT and FFT theory can be found in any number of references, particularly

> The FFT: Fundamentals and Concepts Robert W. Ramirez, Prentice Hall, 1985.

### Calculating the DFT

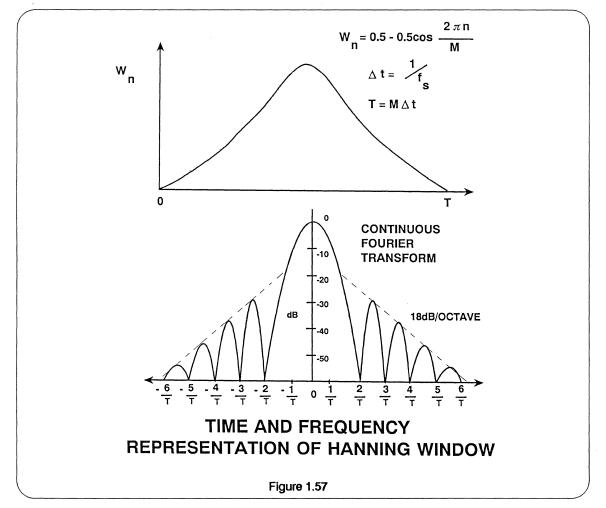

To calculate the DFT, a spectrally pure sinewave is applied to A/D converter, and a number of contiguous samples are stored in a buffer memory. Unless the record time contains an integer number of cycles of the sinewave, time-weighting of the samples is required to reduce frequency sidelobes. Without weighting, the discontinuity produced by not having an integer number of cycles will cause the main lobe energy to "leak" into many other frequency bins making accurate spectral measurements impossible. A popular weighting function is called the "Hanning" function and is given by

$$W_n D_n = D_n \left[ 0.5 - 0.5 \cos \left( \frac{2\pi n}{M} \right) \right]$$

where  $W_n D_n$  is the nth weighted data sample,  $D_n$  is the nth input data sample, and M is the total number of samples.

By using this weighting function, the leakage energy can be compressed into a small band of frequencies centered on the fundamental sinewave frequency. This eliminates contamination of a large portion of the overall spectrum.

Next the program must find the DFT of the sequence of weighted data samples for M/2 frequencies. To do that, the program must solve the following two equations for the Kth frequency:

$$A_{\rm K} = \frac{1}{M} \frac{M}{\sum_{n=1}^{M} W_n D_n \cos \left[ \frac{2\pi k(n-1)}{M} \right]}$$

$$\frac{1}{M} \frac{M}{\sum_{n=1}^{M} V_n D_n \cos \left[ \frac{2\pi k(n-1)}{M} \right]}$$

$$B_{K} = \frac{1}{M} \sum_{n=1}^{M} W_{n} D_{n} \sin \left[ \frac{2\pi k(n-1)}{M} \right]$$

where  $A_k$  and  $B_k$  represent the magnitudes of the cosine and sine parts of the Kth spectral line. The total magnitude of the Kth spectral line is then expressed by the equation:

$$MAG_{K} = \sqrt{A_{K}^{2} + B_{K}^{2}}$$

The results yield M/2 components which are the frequency domain representation of the M time samples. The resolution or spacing between the spectral lines is given by the equation  $\Delta \mathbf{f} = \frac{\mathbf{f}_{s}}{\mathbf{M}}$

where  $f_s$  is the sampling rate, and M is the total record length. The value,  $\Delta f_s$  is often referred to as the "bin" size.

# CALCULATING THE SIGNAL-TO-NOISE RATIO FROM THE FFT OUTPUT

Unless the sinewave frequency is chosen such that the record length M contains an integer number of cycles of the sinewave, the signal energy will be contained in several bins located around the fundamental. The RMS energy contained in the fundamental sinewave is computed by taking the square root of the sum of the squares of the appropriate number of samples (including the peak) located on either side of the peak. The number of samples to be included in this calculation can be determined by knowing the resolution of the A/D converter and the sidelobe roll-off characteristics of the particular weighting function being used.

The RMS energy in the remaining frequency bins represents the noise due to theoretical quantization, A/D harmonic distortion and excess noise, and FFT round-off error. This energy is calculated by taking the square root of the sum of the squares of the remaining samples (excluding the DC component).

The overall A/D converter SNR is then calculated by:

$SNR = 20\log_{10}$

RMS SIGNAL LEVEL

### I-57

# CALCULATING HARMONIC DISTORTION FROM THE FFT OUTPUT

Harmonic distortion is calculated in a similar manner. The program "searches" the FFT frequency spectrum for the proper location of the desired harmonic (bearing in mind that harmonics above  $f_s/2$  will be aliased into the baseband) and calculates the RMS energy in the harmonic. The RMS signal to RMS harmonic ratio is calculated as follows:

# TWO-TONE INTERMODULATION TESTS USING FFTs

It is often useful to measure the thirdorder intermodulation products for two sinewaves of frequency  $f_1$  and  $f_2$  which are HARMONIC DISTORTION =  $20\log_{10} \left[ \frac{\text{RMS SIGNAL LEVEL}}{\text{RMS HARMONIC LEVEL}} \right]$

Total harmonic distortion (THD) is often calculated by root-sum-squaring the first five harmonics of the fundamental sinewave and using the resulting number in the above formula for the RMS harmonic level.

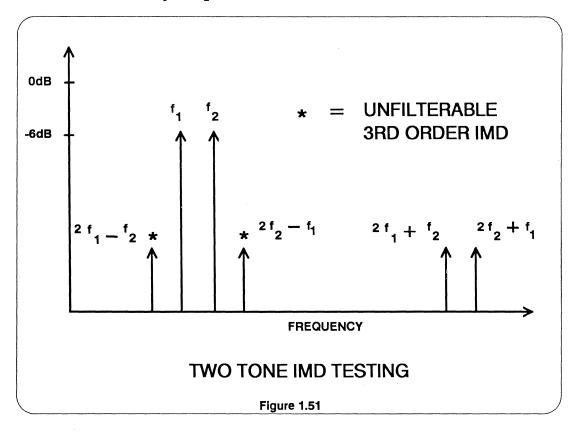

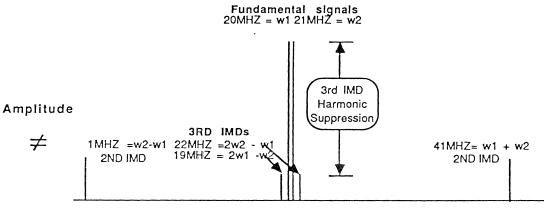

applied to an A/D converter (see Figure 1.51).

1-58

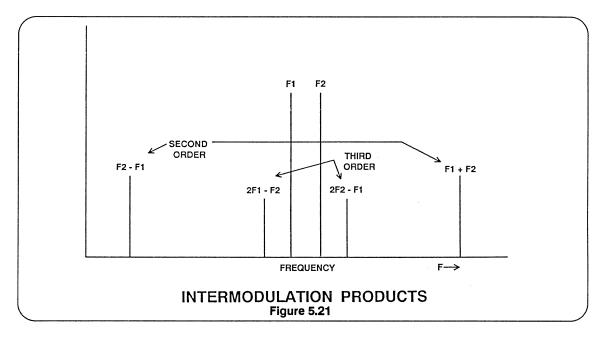

These products occur at frequencies:

$$\begin{array}{rcl} 2f_1 + f_2 & 2f_2 + f_1 \\ 2f_1 - f_2 & 2f_2 - f_1 \end{array}$$

Most IMD can be filtered out. However, if the two tones are of similar frequencies, the third order IMD  $(2f_1-f_2, 2f_2-f_1)$  will be very close to the fundamental frequencies and cannot be easily filtered. The level of these products is of most concern in narrow bandwidth applications.

The amplitudes of the individual tones should be at least 6dB below the fullscale of the A/D converter to avoid distortion due to clipping.

The frequency separation of the two tones should be consistent with the resolution of the FFT. As previously discussed, the spectral resolution of the FFT is a function of record length, M, coherence vs. non-coherence, and the properties of the particular windowing function chosen.

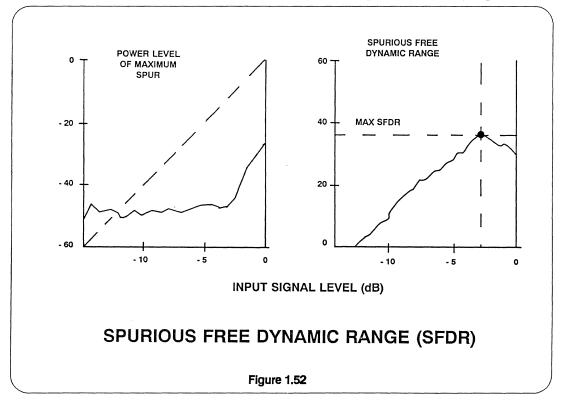

### SPURIOUS FREE DYNAMIC RANGE (SFDR)

In receiver applications, it is often desired to know the maximum ratio achievable between the amplitude of a single tone input signal and the amplitude of its maximum spur.

For an ideal A/D converter, this would occur for a fullscale input sinusoid. In a practical A/D, however, spurious content is a function of slew-rate and, therefore, the maximum spurious free dynamic range (SFDR) for a given input frequency usually occurs at a level somewhat below fullscale.

Figure 1.52 shows a typical plot of the maximum spur level vs. input power level.

This corresponding spurious free dynamic range plot is also shown in Figure 1.52. This plot shows that the maximum SFDR occurs for an input signal which is approximately 3dB below fullscale.

The SFDR is slew-rate dependent, and, therefore, a function of the input frequency as well as the amplitude.

The data needed to generate these plots is readily available from the family of FFTs calculated for the different input amplitudes.

By knowing the input signal level that gives the highest SFDR at frequencies close to Nyquist, the gain of the system can be set to take maximum advantage of the A/D converter's spectral characteristics.

#### Determining The Proper FFT Record Length

The first consideration in choosing the number of time-domain samples required or record length, N, is the required spectral resolution,  $\Delta f$ . Also, in order to perform the FFT computations, N must be equal to an integer which is a power of two. The FFT spectral resolution,  $\Delta f$ , is given by

$$\Delta f = \int_{s}^{s} M$$

where  $f_s$  is the sampling rate. This can also be expressed as

$$\Delta f = \frac{1}{M \cdot \Delta t} ,$$

where  $\Delta t$  is the sampling period,  $1/f_s$ .

Typically, M is selected to be between 256 and 4096 depending upon the desired resolution and the amount of buffer memory available. (See section on the selection of a windowing function for further discussion on the effects of windowing on spectral leakage).

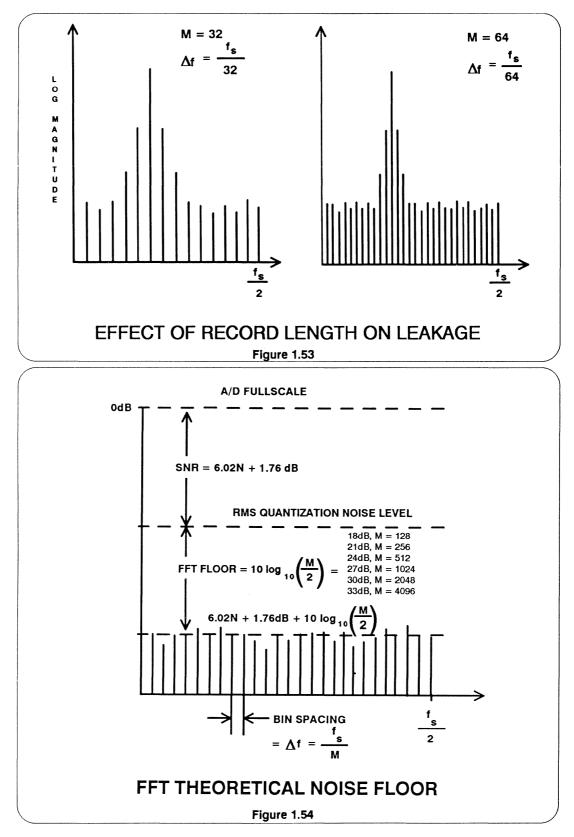

If windowing is used, the main lobe width and sidelobe rolloff (leakage) are measured in units of "bin width", f/M. This leakage can be "compressed" around the main lobe by using a larger record length, M, thereby leaving a larger percentage of the Nyquist spectrum uncontaminated, as shown in Figure 1.53.

For example, the Hanning weighting leakage is 10 bins around the fundamental for 68dB sidelobe suppression. If the record length is 256, then the smeared fundamental occupies 20/128, or 16% of the Nyquist bandwidth. For M = 1024, the percentage reduces to 20/512, or 4%.

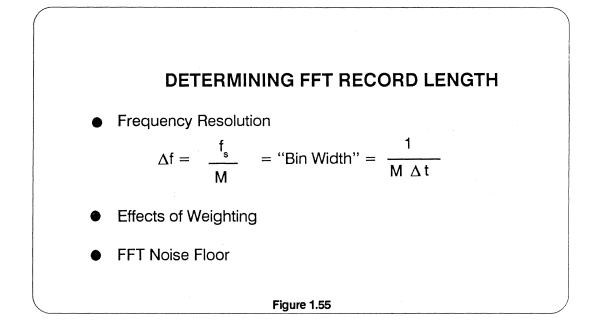

Another consideration in determining the proper record length is the FFT noise floor itself. Assuming the DSP noise contribution (due to roundoff error) is negligible, the RMS signal to RMS noise level in a <u>single</u> frequency bin of width  $\Delta f$  is given by the expression

$SNR_{FFT} = 6.02N + 1.76dB + 10log_{10}$

This represents the FFT noise floor. The value should be chosen such that any spurious components which need to be resolved lie at least 10dB above this floor. This is illustrated in Figure 1.54.

1-60

. . . . . <u>. . . . . . . . . .</u>

fs

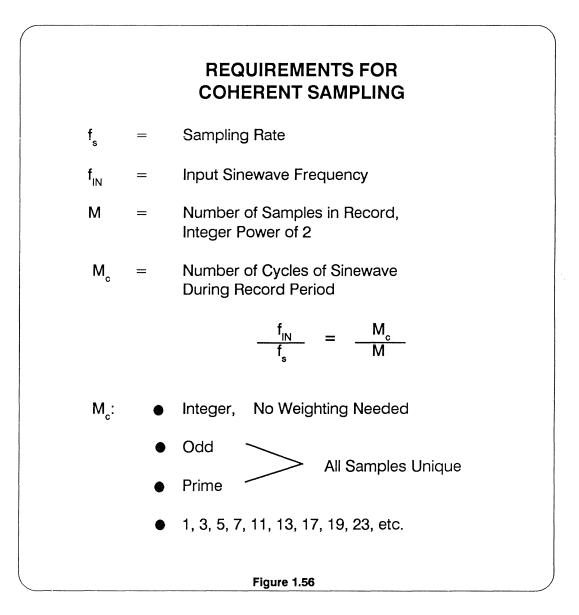

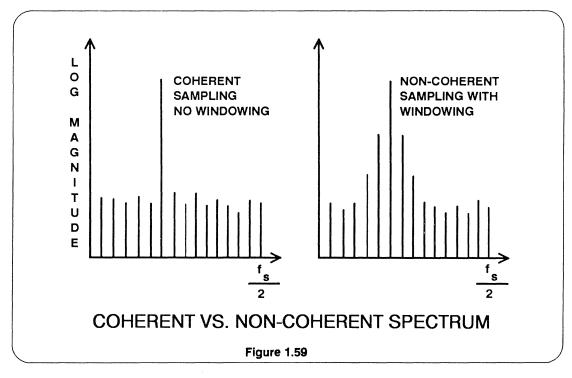

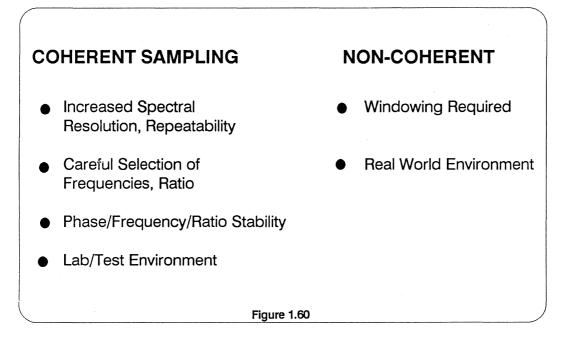

## DETERMINING SINEWAVE INPUT FREQUENCY FOR COHERENT SAMPLING

As has been previously discussed, the use of coherent sampling eliminates leakage and the requirement for windowing. There are, however, some requirements placed on the choice of the sampling rate and the sinewave frequency.

First, the following ratio must be observed:

$$\frac{f_{IN}}{f_s} = \frac{M_C}{M} \text{ where }$$

$M_c$  = Number of integer cycles of the sinewave during the record period.

M = Number of samples in record period.

$f_{IN}$  = Input sinewave frequency.

= Sampling rate.

For a whole number of cycles,  $M_c$  must be an integer. For non-repetitive data  $M_c$ should also be <u>odd</u> and <u>prime</u> - i.e., 1, 3, 5, 7, 11, 13, 17, etc. This insures that all samples during the record period will be unique.

When using coherent sampling, the ratio must be constant! This implies that the frequencies  $f_s$  and  $f_{in}$  be derived from sources that are locked to each other, such as two locked frequency synthesizers.

. 4585 ~

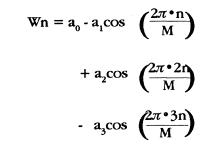

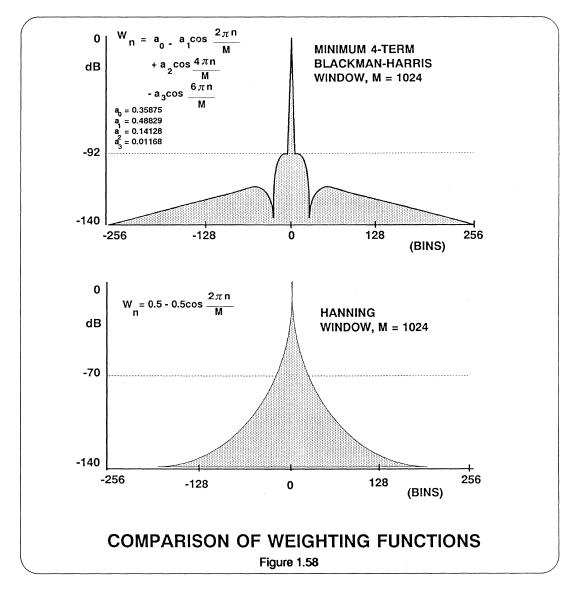

# CHOOSING THE WINDOWING FUNCTION FOR NON-COHERENT SAMPLING

If non-coherent sampling is chosen, fewer restrictions apply to the selection of the input frequency. However, integer submultiples of the sampling frequency should be avoided to prevent masking out harmonics of the fundamental. It is also desirable to make the input frequency an <u>odd</u> multiple of the FFT frequency bin size to ensure this condition does not occur.

The selection of the weighting function is primarily a tradeoff between main-lobe spreading and sidelobe rolloff. The following reference is highly recommended for an in-depth look at windows:

> Fredric J. Harris, "On The Use of Windows for Harmonic Analysis with the Discrete Fourier Transform," <u>IEEE Proceedings</u>, Vol. 66, No. 1, Jan. 1978, pp. 51-83.

The effects of "windowing" a sinewave are shown in Figure 1.57 for the popular "Hanning" window.

This window has the following characteristics:

- Highest Sidelobe Level: 32dB below fundamental

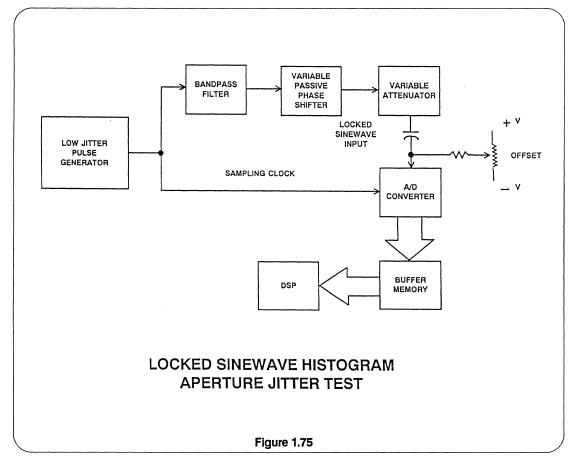

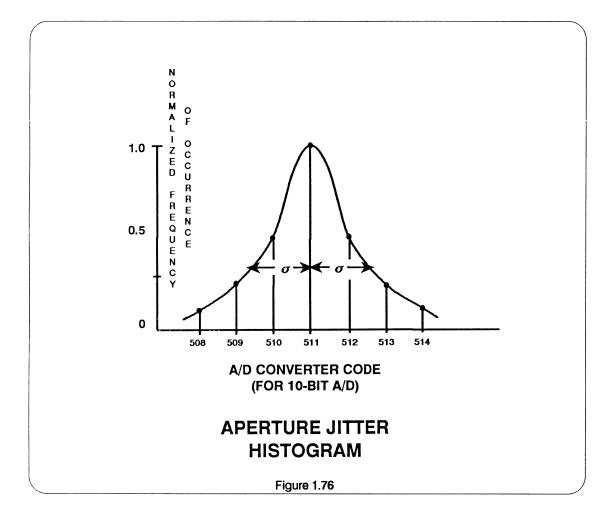

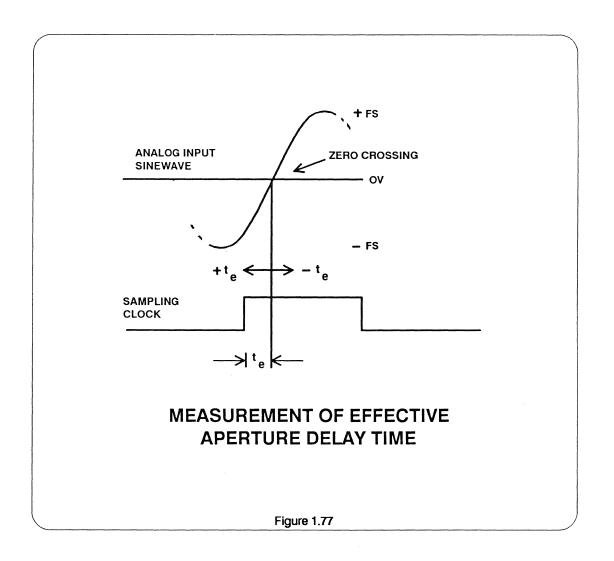

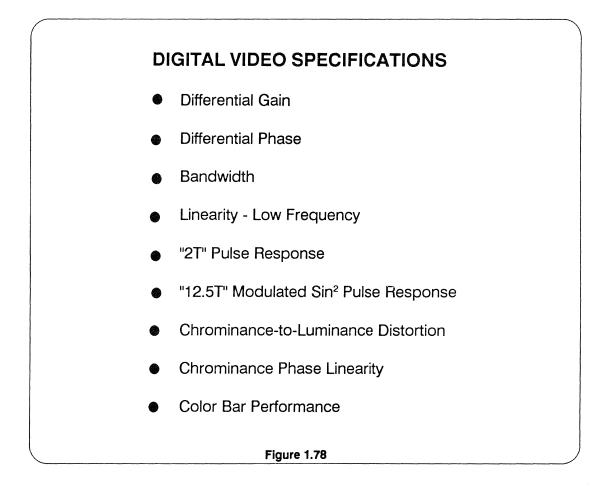

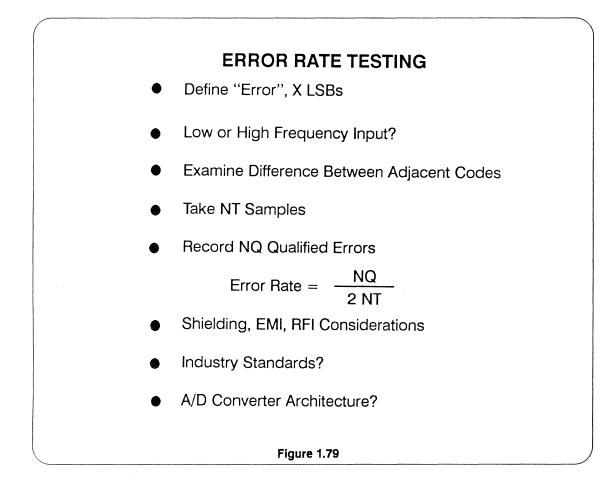

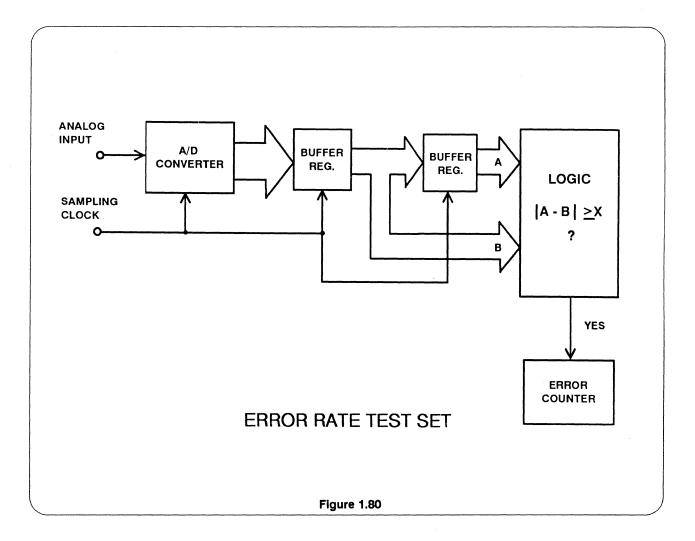

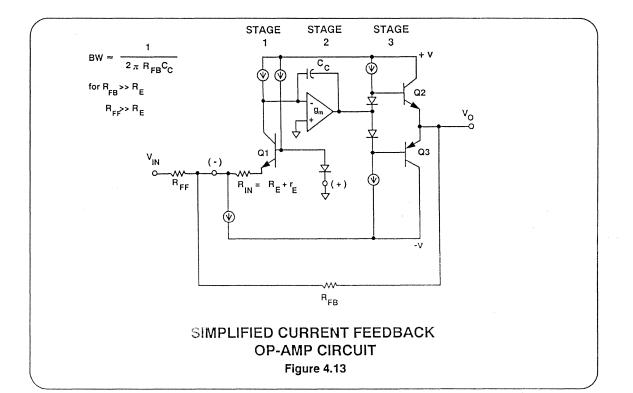

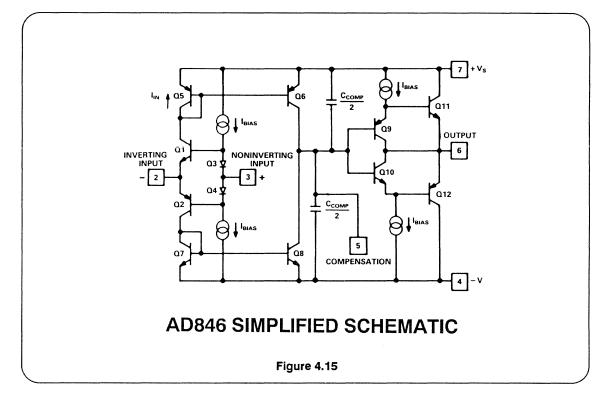

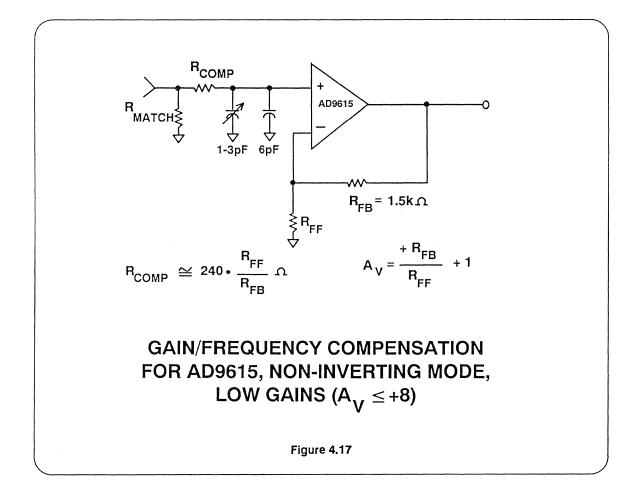

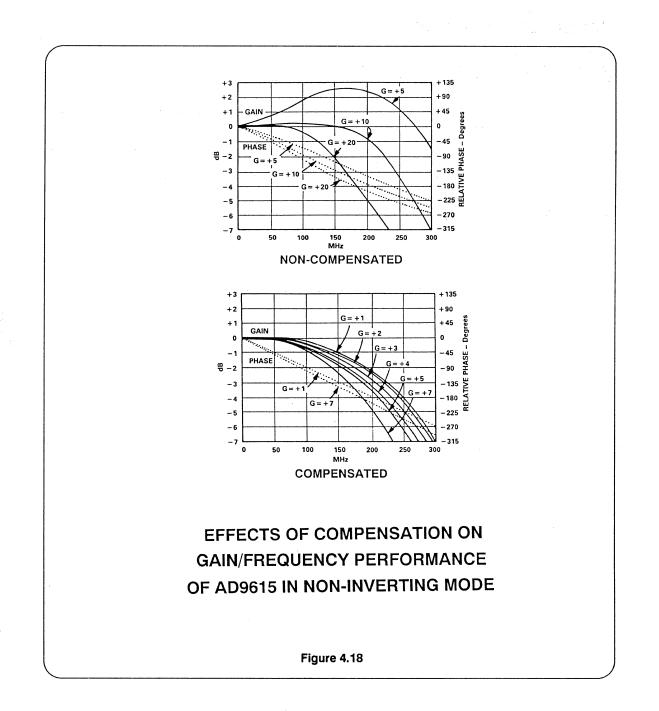

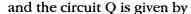

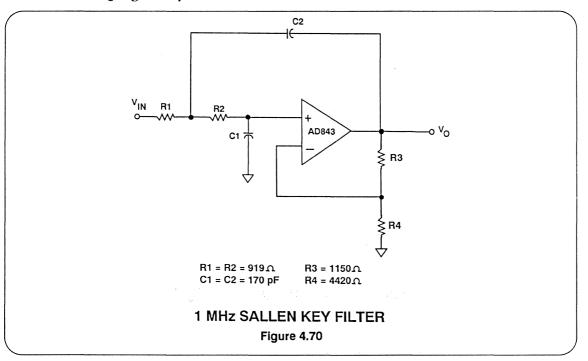

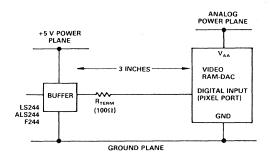

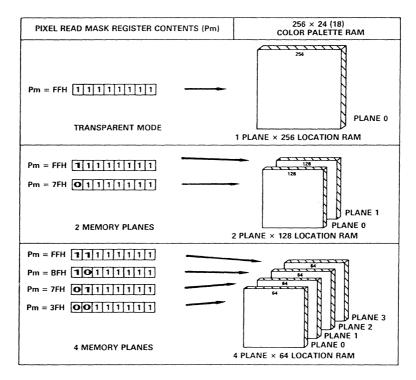

- 6dB point of main lobe: 2 bins wide