ANALOG

## ADSP-2100 FAMILY

Applications Handbook Volume 4 You may contact the Digital Signal Processing Division in the following ways.

- By contacting your local Analog Devices Sales Representative

- For Marketing information, call (617) 461-3881 in Norwood, Massachusetts, USA

- For Applications Engineering information, call (617) 461-3672 in Norwood, Massachusetts, USA

- The Norwood office Fax number is (617) 461-3010

- The Norwood office may also be reached by

- Telex: 924491

- TWX: 710/394-6577

- Cables: ANALOG NORWOODMASS

- The DSP Division runs a Bulletin Board Service that can be reached at 300, 1200 or 2400 baud, no parity, 8 bits data, 1 stop bit by dialing: (617) 461-4258

- By writing to:

Analog Devices DSP Division One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 USA

### **ADSP-2100 Family Applications Handbook, Volume 4**

© 1990 Analog Devices, Inc. ALL RIGHTS RESERVED

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices.

PRINTED IN U.S.A.

FIRST EDITION

# Literature

### **ADSP-2100 FAMILY MANUALS**

ADSP-2100 User's Manual/Architecture ADSP-2101 User's Manual/Architecture ADSP-2111 User's Manual/Architecture Complete descriptions of architecture and system interface.

ADSP-2100 Cross-Software Manual ADSP-2101 Cross-Software Manual Complete programmer's references, including optional C compiler.

ADSP-2100 Emulator Manual ADSP-2101 Emulator Manual ADSP-2101 EZ-ICE<sup>™</sup> Manual User's manuals for in-circuit Emulators.

**ADSP-2100A Evaluation Board Manual** A guide to the Evaluation Board including schematics for prototyping.

**ADSP-2101 EZ-LAB™ Manual** A guide to the EZ-LAB demonstration board and programs.

### **APPLICATIONS INFORMATION**

**Digital Signal Processing Applications Using the ADSP-2100 Family** (Formerly the *ADSP-2100 Family Applications Handbook, Volumes 1, 2 and 3.*) Topics include arithmetic, filters, FFTs, linear predictive coding, modem algorithms, graphics, pulse-code modulation, multirate filters, DTMF, multiprocessing, host interface and sonar.

**ADSP-2100 Family Applications Handbook, Volume 4** Topics include V.32 modem implementation, quadrature amplitude modulation (QAM), frequency shift keying (FSK) modulation, echo cancellation, and adaptive equalization.

### SPECIFICATIONS INFORMATION

ADSP-2100A/ADSP-2100 Data Sheet ADSP-2101 Data Sheet ADSP-2111 Data Sheet (preliminary) ADSP-2105 Data Sheet (preliminary)

### CHAPTER 1 INTRODUCTION

| 1.1 | OVERVIEW                       |  |

|-----|--------------------------------|--|

| 1.2 | ADSP-2100 FAMILY OF PROCESSORS |  |

| 1.3 | SUMMARY OF VOLUMES 1, 2 AND 3  |  |

| 1.4 | CONVENTIONS OF NOTATION        |  |

| 1.5 | PROGRAMS ON DISK               |  |

### CHAPTER 2 V.32 MODEMS

| 2.1     | OVERVIEW                              | 2–1  |

|---------|---------------------------------------|------|

| 2.2     | V.32 MODEM DEFINITION                 |      |

| 2.2.1   | Transmitter Algorithms                | 2–2  |

| 2.2.2   | Receiver Algorithms                   |      |

| 2.3     | SCRAMBLER                             | 2–5  |

| 2.4     | DESCRAMBLING                          |      |

| 2.4.1   | ADSP-2100 Family Implementation       | 2–8  |

| 2.4.2   | Scrambler/Descrambler Programs        | 2–9  |

| 2.5     | RAISED COSINE FILTER                  | 2–16 |

| 2.5.1   | ADSP-2100 Family Implementation       |      |

| 2.6     | TRELLIS ENCODING                      |      |

| 2.6.1   | ADSP-2100 Family Implementation       | 2–23 |

| 2.7     | VITERBI DECODING                      | 2–31 |

| 2.7.1   | Data Constellation                    | 2–34 |

| 2.7.2   | Viterbi Algorithm                     | 2–34 |

| 2.7.3   | ADSP-2100 Family Implementation       | 2–36 |

| 2.7.4   | Shortest Path Through Trellis Diagram | 2–37 |

| 2.7.5   | Viterbi Program                       | 2–39 |

| 2.7.5.1 | Initialization                        | 2–39 |

| 2.7.5.2 | Data Input and Euclidean Distance     | 2–39 |

| 2.7.5.3 | Shortest Path                         | 2–39 |

| 2.7.5.4 | Last Surviving Path                   | 2–39 |

|---------|---------------------------------------|------|

| 2.7.5.5 | Determination of Error Corrected Data |      |

| 2.8     | REFERENCES                            | 2–59 |

### CHAPTER 3 QUADRATURE AMPLITUDE MODULATION

| 3.1 | INTRODUCTION                    | 3–1 |

|-----|---------------------------------|-----|

| 3.2 | QAM METHODOLOGY                 | 3–1 |

| 3.3 | ADSP-2100 FAMILY IMPLEMENTATION | 3–4 |

| 3.4 | REFERENCES                      | 3–5 |

### CHAPTER 4 ECHO CANCELLATION

| 4.1   | INTRODUCTION                                         | 4–1  |

|-------|------------------------------------------------------|------|

| 4.2   | ECHO CANCELLATION ALGORITHM                          | 4–2  |

| 4.2.1 | ADSP-2100 Family Implementation of LMS Algorithm     | 4–4  |

| 4.3   | FREQUENCY OFFSET COMPENSATION                        | 4–8  |

| 4.3.1 | ADSP-2100 Family Implementation of Hilbert Transform | 4–11 |

| 4.4   | V.32 MODEM IMPLEMENTATION                            | 4–16 |

| 4.5   | REFERENCES                                           | 4–18 |

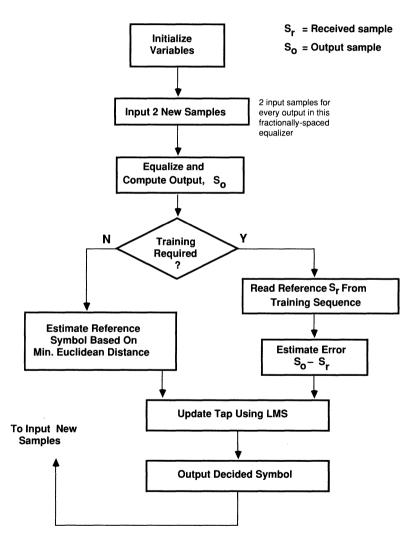

### CHAPTER 5 ADAPTIVE EQUALIZER

| INTRODUCTION                       | 5–1          |

|------------------------------------|--------------|

| HISTORY OF ADAPTIVE FILTERS        | 5–1          |

| APPLICATIONS OF ADAPTIVE FILTERS   | 5–2          |

| CHANNEL EQUALIZATION IN A MODEM    | 5–4          |

| Equalization                       | 5–5          |

| Performance Index                  | 5–8          |

| EQUALIZER ARCHITECTURES            | 5–8          |

| Real Or Complex                    | 5–9          |

| Sampling Rates                     | .5–10        |

| LEAST MEAN SQUARED (LMS) ALGORITHM | .5–12        |

| PROGRAM STRUCTURE                  | .5–15        |

| Input New Sample                   | .5–16        |

|                                    | INTRODUCTION |

| 5.7.2 | Filtering (Equalizing)          | .5–16 |

|-------|---------------------------------|-------|

| 5.7.3 | Training Sequence               | .5–17 |

| 5.7.4 | Decision-Directed Adaptation    | .5–18 |

| 5.7.5 | Tap Update (LMS Algorithm)      |       |

| 5.7.6 | Output                          | .5–21 |

| 5.8   | PRACTICAL CONSIDERATIONS        | .5–22 |

| 5.8.1 | Viterbi Decoder                 | .5–22 |

| 5.8.2 | Pseudo-Random Training Sequence | .5–22 |

| 5.8.3 | Delay Line Length               | .5–22 |

| 5.9   | REFERENCES                      |       |

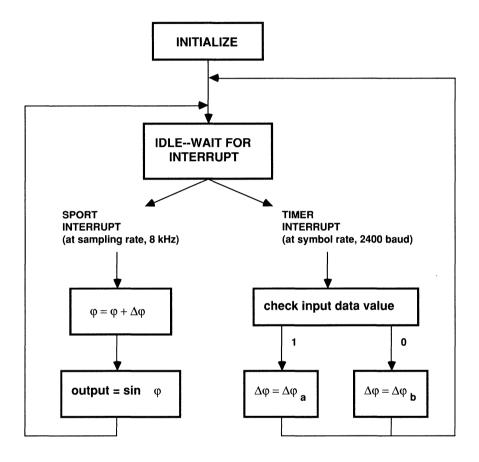

### CHAPTER 6 CONTINUOUS PHASE FREQUENCY-SHIFT KEYED MODULATION

| 6.1 | INTRODUCTION                    | 6–1 |

|-----|---------------------------------|-----|

| 6.2 | CPFSK METHODOLOGY               | 6–1 |

| 6.3 | ADSP-2100 FAMILY IMPLEMENTATION | 6–2 |

| 6.4 | REFERENCES                      | 6–6 |

### FIGURES

| Transmitter Block Diagram                    | 2–3                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Call Mode Scrambler                          |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Answer Mode Scrambler                        | 2–7                                                                                                                                                                                                                                                                                                                                                                                             |

| Call Mode Descrambler                        | 2–7                                                                                                                                                                                                                                                                                                                                                                                             |

| Answer Mode Descrambler                      | 2–7                                                                                                                                                                                                                                                                                                                                                                                             |

| Circular Buffer Implementation for Scrambler | 2–8                                                                                                                                                                                                                                                                                                                                                                                             |

| Raised Cosine Pulse Shaping Filter           | 2–18                                                                                                                                                                                                                                                                                                                                                                                            |

| Modem Transmitter                            |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Encoder Block Diagram                        | 2–22                                                                                                                                                                                                                                                                                                                                                                                            |

| V.32 Signal Constellation                    |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Convolutional Encoder Block Diagram          | 2–25                                                                                                                                                                                                                                                                                                                                                                                            |

| Trellis Diagram for Convolutional Encoding   | 2–33                                                                                                                                                                                                                                                                                                                                                                                            |

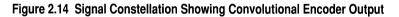

| Signal Constellation Showing Convolutional   |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Encoder Output                               | 2–35                                                                                                                                                                                                                                                                                                                                                                                            |

| Accumulated Distance Table Update Example    | 2–38                                                                                                                                                                                                                                                                                                                                                                                            |

|                                              | Answer Mode Scrambler<br>Call Mode Descrambler<br>Answer Mode Descrambler<br>Circular Buffer Implementation for Scrambler<br>Raised Cosine Pulse Shaping Filter<br>Modem Transmitter<br>Encoder Block Diagram<br>V.32 Signal Constellation<br>Convolutional Encoder Block Diagram<br>Trellis Diagram for Convolutional Encoding<br>Signal Constellation Showing Convolutional<br>Encoder Output |

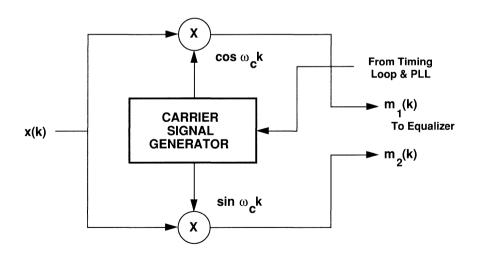

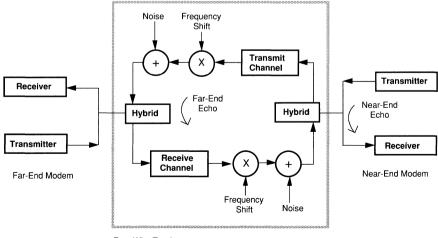

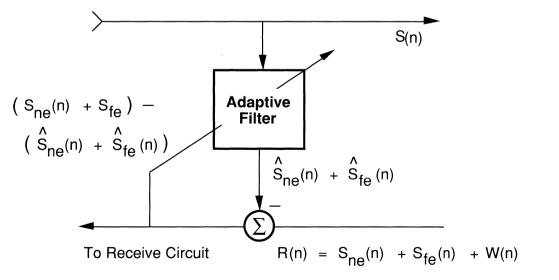

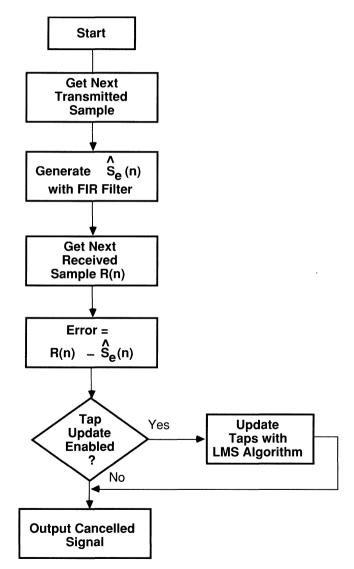

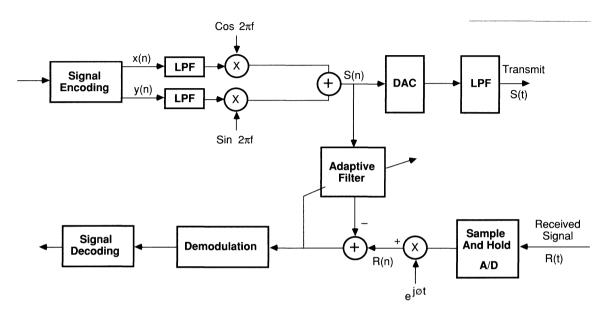

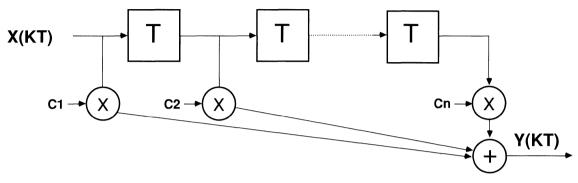

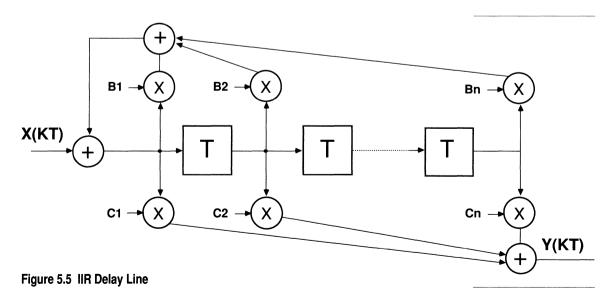

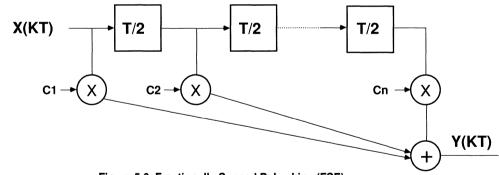

| Figure 3.2QAM Demodulator Block Diagram3-3Figure 4.1Telephone Channel Block Diagram4Figure 4.2Echo Canceller4Figure 4.3LMS Adaptive Filter4Figure 4.4Flowchart for LMS Stochastic Gradient Algorithm4Figure 4.5Block Diagram of Echo Canceller with Frequency Shift4Figure 4.6Block Diagram of Hilbert Transform41Figure 4.7Spectrum of Hilbert Frequency Shift41Figure 5.1Example Short Impulse Response5Figure 5.2Pure Delay Impulse Response5Figure 5.3Equalizer Impulse Response5Figure 5.4Transversal (FIR) Delay Line5Figure 5.5IIR Delay Line5Figure 5.6Fractionally Spaced Delay Line (FSE)510Figure 5.7Adaptive Equalizer Flowchart511Figure 5.7CPFSK Flow Diagram6 | Figure 3.1 | QAM Modulator Block Diagram                     |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|-----|

| Figure 4.2Echo Canceller4-4Figure 4.3LMS Adaptive Filter4-4Figure 4.4Flowchart for LMS Stochastic Gradient Algorithm4-4Figure 4.5Block Diagram of Echo Canceller with Frequency Shift4-4Figure 4.6Block Diagram of Hilbert Transform4-10Figure 4.7Spectrum of Hilbert Frequency Shift4-11Figure 4.8V.32 Modem Block Diagram4-11Figure 5.1Example Short Impulse Response5-4Figure 5.2Pure Delay Impulse Response5-4Figure 5.3Equalizer Impulse Response5-4Figure 5.4Transversal (FIR) Delay Line5-4Figure 5.5IIR Delay Line5-4Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-11                                                    | •          |                                                 |     |

| Figure 4.2Echo Canceller4-4Figure 4.3LMS Adaptive Filter4-4Figure 4.4Flowchart for LMS Stochastic Gradient Algorithm4-4Figure 4.5Block Diagram of Echo Canceller with Frequency Shift4-4Figure 4.6Block Diagram of Hilbert Transform4-10Figure 4.7Spectrum of Hilbert Frequency Shift4-11Figure 4.8V.32 Modem Block Diagram4-11Figure 5.1Example Short Impulse Response5-4Figure 5.2Pure Delay Impulse Response5-4Figure 5.3Equalizer Impulse Response5-4Figure 5.4Transversal (FIR) Delay Line5-4Figure 5.5IIR Delay Line5-4Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-11                                                    | Figure 4.1 | Telephone Channel Block Diagram                 | 4–1 |

| Figure 4.3LMS Adaptive Filter4-4Figure 4.4Flowchart for LMS Stochastic Gradient Algorithm4-4Figure 4.5Block Diagram of Echo Canceller with Frequency Shift4-4Figure 4.6Block Diagram of Hilbert Transform4-10Figure 4.7Spectrum of Hilbert Frequency Shift4-11Figure 4.8V.32 Modem Block Diagram4-17Figure 5.1Example Short Impulse Response5-4Figure 5.2Pure Delay Impulse Response5-4Figure 5.3Equalizer Impulse Response5-4Figure 5.4Transversal (FIR) Delay Line5-4Figure 5.5IIR Delay Line5-4Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-11                                                                               | Figure 4.2 | Echo Canceller                                  |     |

| Figure 4.5Block Diagram of Echo Canceller with Frequency Shift4-4Figure 4.6Block Diagram of Hilbert Transform4-10Figure 4.7Spectrum of Hilbert Frequency Shift4-11Figure 4.8V.32 Modem Block Diagram4-17Figure 5.1Example Short Impulse Response5-6Figure 5.2Pure Delay Impulse Response5-6Figure 5.3Equalizer Impulse Response5-6Figure 5.4Transversal (FIR) Delay Line5-6Figure 5.5IIR Delay Line5-6Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-10                                                                                                                                                                           | Figure 4.3 |                                                 |     |

| Figure 4.5Block Diagram of Echo Canceller with Frequency Shift4-4Figure 4.6Block Diagram of Hilbert Transform4-10Figure 4.7Spectrum of Hilbert Frequency Shift4-11Figure 4.8V.32 Modem Block Diagram4-17Figure 5.1Example Short Impulse Response5-6Figure 5.2Pure Delay Impulse Response5-6Figure 5.3Equalizer Impulse Response5-6Figure 5.4Transversal (FIR) Delay Line5-6Figure 5.5IIR Delay Line5-6Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-10                                                                                                                                                                           | Figure 4.4 | Flowchart for LMS Stochastic Gradient Algorithm |     |

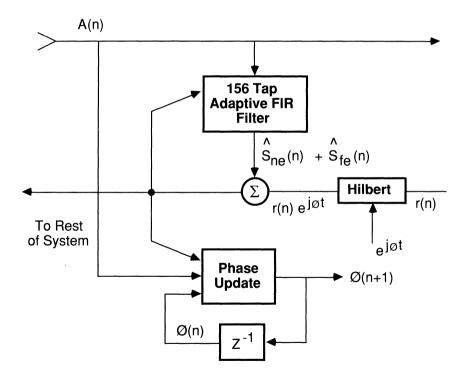

| Figure 4.6Block Diagram of Hilbert Transform4–10Figure 4.7Spectrum of Hilbert Frequency Shift4–11Figure 4.8V.32 Modem Block Diagram4–11Figure 5.1Example Short Impulse Response5–6Figure 5.2Pure Delay Impulse Response5–6Figure 5.3Equalizer Impulse Response5–6Figure 5.4Transversal (FIR) Delay Line5–6Figure 5.5IIR Delay Line5–6Figure 5.6Fractionally Spaced Delay Line (FSE)5–10Figure 5.7Adaptive Equalizer Flowchart5–11                                                                                                                                                                                                                                            | Figure 4.5 |                                                 |     |

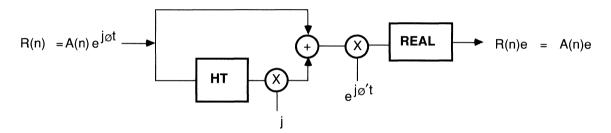

| Figure 4.7Spectrum of Hilbert Frequency Shift4–11Figure 4.8V.32 Modem Block Diagram4–11Figure 5.1Example Short Impulse Response5–4Figure 5.2Pure Delay Impulse Response5–4Figure 5.3Equalizer Impulse Response5–4Figure 5.4Transversal (FIR) Delay Line5–4Figure 5.5IIR Delay Line5–4Figure 5.6Fractionally Spaced Delay Line (FSE)5–14Figure 5.7Adaptive Equalizer Flowchart5–14                                                                                                                                                                                                                                                                                            | Figure 4.6 | •                                               |     |

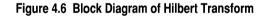

| Figure 4.8V.32 Modem Block Diagram4–17Figure 5.1Example Short Impulse Response5–4Figure 5.2Pure Delay Impulse Response5–4Figure 5.3Equalizer Impulse Response5–4Figure 5.4Transversal (FIR) Delay Line5–4Figure 5.5IIR Delay Line5–4Figure 5.6Fractionally Spaced Delay Line (FSE)5–14Figure 5.7Adaptive Equalizer Flowchart5–14                                                                                                                                                                                                                                                                                                                                             | Figure 4.7 |                                                 |     |

| Figure 5.2Pure Delay Impulse Response5-6Figure 5.3Equalizer Impulse Response5-6Figure 5.4Transversal (FIR) Delay Line5-6Figure 5.5IIR Delay Line5-6Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-10                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 4.8 |                                                 |     |

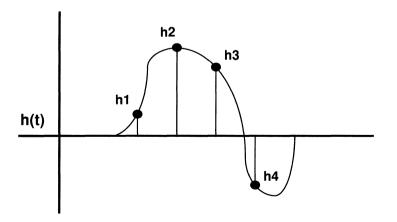

| Figure 5.2Pure Delay Impulse Response5-6Figure 5.3Equalizer Impulse Response5-6Figure 5.4Transversal (FIR) Delay Line5-6Figure 5.5IIR Delay Line5-6Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-10                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 5.1 | Example Short Impulse Response                  | 5–5 |

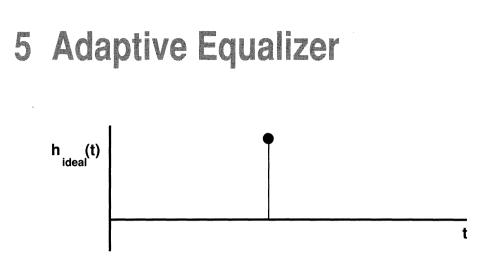

| Figure 5.3Equalizer Impulse Response5-4Figure 5.4Transversal (FIR) Delay Line5-4Figure 5.5IIR Delay Line5-4Figure 5.6Fractionally Spaced Delay Line (FSE)5-10Figure 5.7Adaptive Equalizer Flowchart5-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •          |                                                 |     |

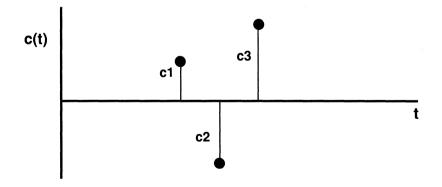

| Figure 5.4       Transversal (FIR) Delay Line       5-4         Figure 5.5       IIR Delay Line       5-4         Figure 5.6       Fractionally Spaced Delay Line (FSE)       5-10         Figure 5.7       Adaptive Equalizer Flowchart       5-11                                                                                                                                                                                                                                                                                                                                                                                                                          | •          |                                                 |     |

| Figure 5.5       IIR Delay Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0          |                                                 |     |

| Figure 5.6       Fractionally Spaced Delay Line (FSE)       5–10         Figure 5.7       Adaptive Equalizer Flowchart       5–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0          | IIR Delay Line                                  | 5–9 |

| Figure 5.7 Adaptive Equalizer Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •          |                                                 |     |

| Figure 6.1 CPFSK Flow Diagram6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •          |                                                 |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 6.1 | CPFSK Flow Diagram                              | 6–3 |

### LISTINGS

| Listing 2.1 | Call Mode Scrambler Main Routine       | 2–10 |

|-------------|----------------------------------------|------|

| Listing 2.2 | Call Mode Scrambler Scrambling Routine | 2–12 |

| Listing 2.3 | Call Mode Descrambler Routine          | 2–14 |

| Listing 2.4 | Raised Cosine Filter                   |      |

| Listing 2.5 | Trellis Encoder Program                | 2–26 |

| Listing 2.6 | Convolutional Encoder Routine          |      |

| Listing 2.7 | Signal Mapping Routine                 | 2–30 |

| Listing 2.8 | Viterbi Decoder                        | 2–40 |

| Listing 3.1 | Modulator Code                         | 3–4  |

| Listing 3.2 | Demodulator Code                       |      |

| Listing 4.1 | LMS Stochastic Gradient Implementation  | 4–6  |

|-------------|-----------------------------------------|------|

| Listing 4.2 | Hilbert Transform Implementation        | 4–13 |

| Listing 5.1 | Delay Line Routine, Complex Tap Weights | 5–11 |

| Listing 5.2 | LMS Routine                             | 5–14 |

| Listing 5.3 | Input Routine                           | 5–16 |

| Listing 5.4 | Filter Routine                          | 5–17 |

| Listing 5.5 | Training Sequence Routine               | 5–18 |

| Listing 5.6 | Decision-Directed Adaptation Routine    | 5–19 |

| Listing 5.7 | Tap Update Routine                      |      |

| Listing 5.8 | Output Routine                          |      |

| Listing 6.1 | CPFSK Program (ADSP-2101)               | 6–6  |

### TABLES

| Table 2.1 | Differential Encoder Lookup Table                 | 2–24 |

|-----------|---------------------------------------------------|------|

| Table 2.2 | State Table for Convolutional Encoder             |      |

| Table 2.3 | Lookup Table of X and Y Coordinates               |      |

| Table 4.1 | ADSP-2100 Family Benchmarks for Echo Cancellation | 4–17 |

### INDEX

# Introduction 🔲 1

### 1.1 OVERVIEW

This is Volume 4 of our Applications Handbooks for the ADSP-2100 family of DSP microprocessors. It presents a compilation of software for a variety of data communication applications, mostly related to the CCITT V.32 modem recommendation. These examples may be used as they are or they may serve as a starting point for the development of your particular application. Each application is prefaced by a brief discussion of the algorithm that underlies the code.

Along with the specific applications, the routines in this handbook demonstrate a variety of programming tactics. We believe that readers will want to scan every chapter, even if their application interests are confined to a single topic.

This handbook does not explain the architecture or instruction set of the ADSP-2100. Refer to the literature page at the front of this book for additional publications describing the processors in the ADSP-2100 family and their hardware and software development tools. Contact your local Analog Devices Sales Representative for these materials if you need them.

We do not attempt to explain the theory of any application area completely. We have assumed that our readers already understand the theory and practice of their own application areas. The references included in each chapter provide additional background.

### 1.2 ADSP-2100 FAMILY OF PROCESSORS

The processors in the ADSP-2100 family share the core architecture of the ADSP-2100 device. The ADSP-2100 contains three independent computational units—arithmetic/logic unit (ALU), multiplier/ accumulator (MAC) and barrel shifter—that operate on 16-bit fixed-point data. The ADSP-2100 supports a modified Harvard architecture in which

# 1 Introduction

data memory stores data and program memory stores both instructions and data. Its program sequencer and two address generators provide flexible addressing for performing DSP algorithms.

- The ADSP-2100A is a version of the ADSP-2100 fabricated in 1.0µm CMOS. It is pin- and code-compatible with the ADSP-2100. It is available (currently) in 10 MHz and 12.5 MHz versions, whereas the ADSP-2100 is offered in 6 MHz and 8 MHz versions.

- The ADSP-2101 is a programmable single-chip microcomputer based on the ADSP-2100. Like the ADSP-2100, the ADSP-2101 contains an ALU, a multiplier/accumulator, and a barrel shifter, as well as a program sequencer and dual address generators. Additionally, there are 1K words of data memory and 2K words of program memory on chip, two serial ports, a timer, boot circuitry (for loading on-chip program memory at reset), and enhanced interrupt capabilities.

- The ADSP-2102 is identical to the ADSP-2101 with program memory ROM instead of RAM.

- The ADSP-2105 is the same as the ADSP-2101 with half the on-chip memory (512 words of data memory and 1K words of program memory) and one serial port instead of two. It is pin- and code-compatible with the ADSP-2101.

- The ADSP-2111 contains all the features of the ADSP-2101 plus a host interface for direct connection (no glue logic) to a host processor. For example, the Motorola 68000, the Intel 8051, and the ADSP-2101 can all be connected easily to the ADSP-2111. The ADSP-2111 also provides additional flag outputs.

All references to the ADSP-2100 in this handbook apply to all members of the ADSP-2100 family of processors, unless otherwise indicated. Because the processors are code-compatible, the programs in this handbook can be executed on any member of the family (some modifications for interrupt vectors may be necessary), although a program may not take advantage of specific functions, such as the serial ports of the ADSP-2101.

# Introduction 1

### 1.3 SUMMARY OF VOLUMES 1, 2 AND 3

Volumes 1, 2 and 3 of the ADSP-2100 Family Applications Handbooks, formerly published as three separate books, are now available in a single book, *Digital Signal Processing Applications Using the ADSP-2100 Family*: This book presents information on the following topics:

- Fixed-point arithmetic operations

- Floating-point arithmetic operations

- Function approximations

- Digital filters

- Fast Fourier transforms (FFTs), both one- and two-dimensional

- Image processing

- Graphics

- Linear predictive speech coding (LPC)

- Pulse code modulation (PCM)

- Adaptive differential pulse code modulation (ADPCM)

- High-speed modem algorithms

- Dual-tone multifrequency (DTMF) coding and detection

- Sonar beamforming

- Memory interface

- Multiprocessing

- Host interface

### 1.4 CONVENTIONS OF NOTATION

The following conventions are used throughout this handbook:

- In listings, all keywords are uppercase; user-defined names (such as labels, variables, and data buffers) are lowercase. In text, keywords are uppercase and user-defined names are lowercase and italicized. Note that this convention is for readability only; the Cross-Software modules do not distinguish between uppercase and lowercase letters.

- In comments, register values are indicated by "=" if the register contains the value or "->" if the register points to the value in memory.

- All numbers are decimal unless otherwise specified. In listings, constant values are specified in binary, octal, decimal, or hexadecimal by the prefixes B#, O#, D#, and H#, respectively.

# **1** Introduction

### 1.5 PROGRAMS ON DISK

An IBM PC 5-1/4 inch diskette containing the source code in this book is available. Consult your local Analog Devices Sales Office for a copy. As with the printed routines, we cannot guarantee their suitability for your application.

### 2.1 OVERVIEW

The International Telegraph and Telephone Consultative Committee (CCITT), which determines protocols and standards for telephone and telegraph equipment, has authored a number of recommendations describing modem operation. This chapter surveys the fundamental algorithms of the V.32 modem recommendation, which describes the operation of a high-speed modem. Implementations of the algorithms on the ADSP-2100 family of DSP microprocessors are shown.

A modem is an electronic device that incorporates both a **mo**dulator and a **dem**odulator into a single piece of signal conversion equipment. Interfacing directly to the communication channel, modems establish communication links between various computer systems and terminal equipment. In most cases the communications channel is the general switched telephone network (GSTN) or a two- or four-wire leased circuit. The GSTN is, for the most part, a copper wire network. The bandwidth of this channel is limited to 200 Hz to 3400 Hz.

Traditionally, a modem was implemented using analog discrete components. Today, digital circuits centered around a high performance digital signal processor can meet the demands of modem algorithms without the difficulties associated with analog circuitry. A digital modem implementation offers programmability, temperature insensitivity, ease of design and often reduced cost when compared with analog implementations.

### 2.2 V.32 MODEM DEFINITION

The V.32 recommendation describes a full duplex synchronous modem that operates on the general switched telephone network (GSTN) as well as point-to-point leased circuits. The V.32 modem communicates at a rate of 9600 bits per second (with a 4800 bit per second slow down mode) utilizing quadrature amplitude modulation (QAM). (QAM is discussed in detail in Chapter 3.) Four-bit symbols (bauds) modulate a carrier frequency of 1800 Hz with a modulation rate of 2400 bauds per second. *The modulation of 4-bit symbols at a rate of 2400 symbols per second yields the 9600 bit per second specification.*

There are three signal coding modes to choose from in the V.32 recommendation.

- 9600 bit/second 16-point QAM. Four bits per symbol are transmitted.

- 9600 bit/second 32-point trellis-coded QAM. Transmitted symbols contain four information bits and an additional trellis encoded bit for error correction.

- 4800 bit/second 4-point QAM.

The second method, which produces a redundant bit for error correction, is the method used in the implementation described in this chapter.

Channel separation is achieved through echo cancellation. Echo cancellers are subject to CCITT specification G.165. An ADSP-2100 family implementation of an echo canceller is described in Chapter 4.

The V.32 modem transmits with a carrier frequency of  $1800 \pm 1$  Hz and must be able to operate with received carrier frequency offsets of  $\pm 7$  Hz. The V.32 recommendation also specifies the transmitted spectrum.

### 2.2.1 Transmitter Algorithms

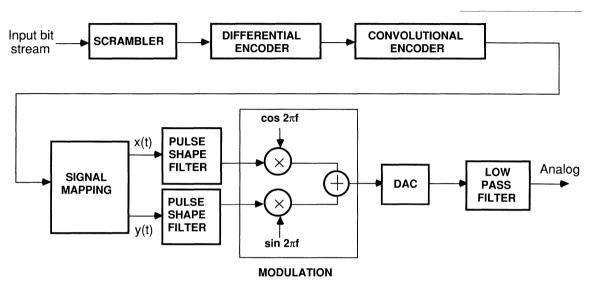

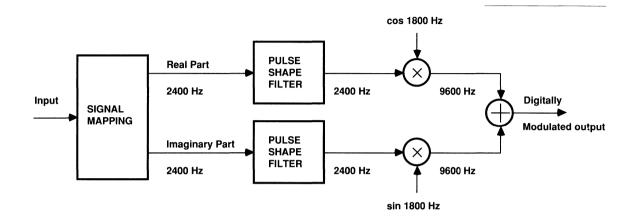

A block diagram of the transmitter section of the V.32 modem implemented in this chapter is shown in Figure 2.1. The input serial bit stream is subject to a number of algorithms prior to modulation and transmission. Each step is described briefly below and in greater detail in the following sections.

*Scrambler*. The input serial bit stream is first scrambled by a selfsynchronizing (requires no clock signal) scrambler. Scrambling takes the input serial bit stream and produces a pseudo-random sequence. The purpose of the scrambler is to whiten the spectrum of the transmitted data. Without the scrambler, a long series of identical symbols could cause the receiver to lose carrier lock. Scrambling makes the transmitted spectrum resemble white noise, to utilize the bandwidth of the channel more efficiently, makes carrier recovery and timing synchronization easy and makes adaptive equalization and echo cancellation possible.

*Encoders*. The scrambled bit stream is divided into groups of four bits. The first two bits of each 4-bit group are first differentially encoded and then convolutionally encoded. This produces a 5-bit symbol in which the first bit is a redundantly coded bit.

Figure 2.1 Transmitter Block Diagram

*Signal Mapping.* The 5-bit symbols are mapped into the signal space (defined in the V.32 recommendation) for modulation. The signal space mapping produces two coordinates, one for the real part of the QAM modulator and one for the imaginary part.

*Pulse Shape Filters*. The pulse shape filter is based on the impulse response of a raised cosine function. Used prior to modulation, these filters attenuate frequencies above the Nyquist frequency that are generated in the signal mapping process. The filters are designed to have zero crossings at the appropriate frequencies to cancel intersymbol interference.

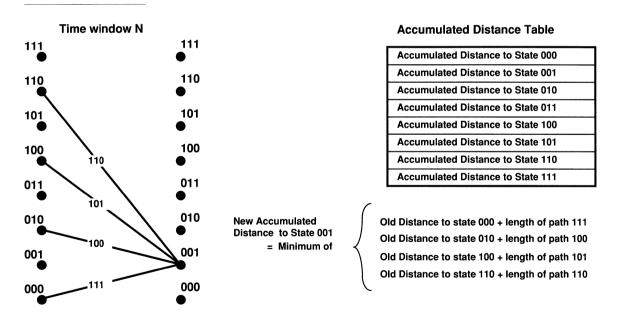

*Modulation*. The modulation for all coding schemes in the V.32 modem recommendation is quadrature amplitude modulation (QAM). A QAM implementation on the ADSP-2100 family is described in Chapter 3. The carrier frequency is 1800 Hz and the modulation rate is 2400 symbols/ second.

After modulation, the samples are converted to an analog signal. The analog output is filtered through a smoothing filter.

### 2.2.2 Receiver Algorithms

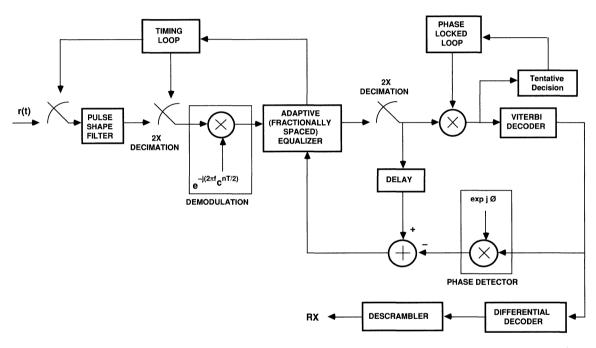

A block diagram of the receiver section of the V.32 modem described in this chapter is shown in Figure 2.2. Each step is described briefly below and in greater detail in the following sections.

### Figure 2.2 Receiver Block Diagram

*Input Filter*. The received analog signal is oversampled by a factor of 4 at 9600 samples per second. The sampled input is filtered with a raised cosine pulse shape filter. The output is then decimated by a factor of 2.

*Demodulation*. Multiplication by  $e^{-j(2\pi f}c^{nT/2)}$  demodulates the signal. QAM demodulation techniques are described in Chapter 3.

*Adaptive Equalizer*. An adaptive equalizer compensates for distortions introduced in the communications channel. A 64-tap fractionally spaced equalizer provides the performance necessary for V.32 applications. The

equalizer also feeds a timing loop which adjusts the 4X sampling input and the 2X sampling output of the input filter. An ADSP-2100 family implementation of an adaptive equalizer is described in Chapter 5.

*Viterbi Decoder*. The decoder takes as input a demodulated, pulse shaped, equalized signal. The Viterbi algorithm is employed as a decoder in order to determine the appropriate signal constellation point received. This algorithm is a soft-decision maximum likelihood sequence decoder. By keeping a past history of 20 or so baud, the decoder can determine the signal point received in noisy conditions. The phase detector and delay adjust the feedback from the Viterbi decoder to the equalizer, which is constantly adapting in response to the received data.

*Differential Decoder and Descrambler.* Once the amplitude and phase of the signal point received is known, the corresponding symbol must be backmapped to decode the encoded bits. The decoded 4-bit symbol is then descrambled utilizing the same generating polynomials as the scrambler.

### 2.3 SCRAMBLER

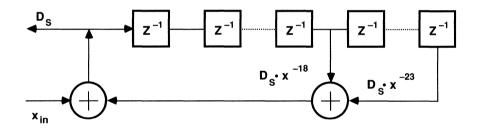

The V.32 modem recommendation calls for the use of a scrambler in the transmit section of the modem and descrambler in the receive section of the modem. The scrambler and descrambler are based on simple polynomials. Each transmission direction uses a different scrambler, i.e., a different generating polynomial, as specified in the V.32 specification. The calling or call mode modem uses the following generating polynomial (GPC):

$GPC = 1 + x^{-18} + x^{-23}$

where x is the input sample and the exponent on x indicates a time delay, e. g.,  $x^{-23}$  is the twenty-third previous sample. The answering or answer mode modem uses a similar scrambler with the following generating polynomial (GPA):

$GPA = 1 + x^{-5} + x^{-23}$

The additions are modulus 2 additions, that is, the bitwise exclusive-OR of the data values. The transmitting modem scrambles the input data sequence by dividing the message sequence by the generating polynomial. The receiving modem multiplies the scrambled sequence by the same polynomial to descramble and recover the original message sequence.

These polynomials can be thought of as digital filters. The scrambler has an all pole transfer function and the descrambler has an all zero transfer function.

The scrambler output is pseudo-random. For a repetitive input signal, the scrambler output is also repetitive with a maximum period of  $2^{k}-1$  samples, where k is the order of the generating polynomial (23 in the case of the V.32 scrambler). In order to maximize the period of the pseudo-random output patterns, the specified GPC and GPA are irreducible and primitive.

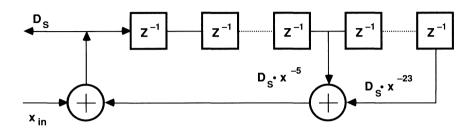

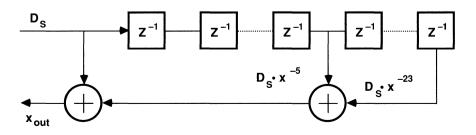

A block diagram of the call mode scrambler is shown in Figure 2.3;  $x_{in}$  is the serial bit input stream and  $D_s$  is the scrambled data bit stream. Each delay block corresponds to a serial port cycle and each addition block is an exclusive OR operation.

Figure 2.3 Call Mode Scrambler

The answer mode scrambler block diagram (Figure 2.4) is similar. The fifth delay line sample,  $x^{-5}$ , is used in the answer mode scrambler rather than the eighteenth delay line value as in the call mode scrambler.

### 2.4 DESCRAMBLING

The descrambler is implemented using a delay line, similar to the scrambler. The descrambler is the last functional block that the data passes through in the receiver. The data that is input to the descrambler is in effect multiplied by the appropriate generating polynomial. This multiplication performs the inverse operation of the scrambler.

Figure 2.4 Answer Mode Scrambler

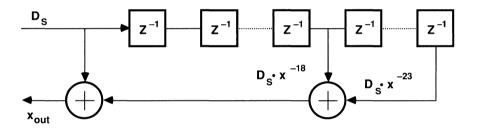

There are two versions of the descrambler, one for call mode and one for answer mode. Block diagrams for the call mode and answer mode descramblers are shown in Figures 2.5 and 2.6.

Figure 2.5 Call Mode Descrambler

Figure 2.6 Answer Mode Descrambler

### 2.4.1 ADSP-2100 Family Implementation

Fundamentally, the implementation of the generating polynomials for scrambling and descrambling is the management of a delay line. The scrambler generates its output from the current input bit and two delayed outputs. The call mode uses the eighteenth and twenty-third previous outputs, while the answer mode uses the fifth and twenty-third previous outputs.

The ADSP-2100 family processors have two key features to facilitate efficient delay line management. First, each of two independent data address generators (DAGs) has four independent data pointers. An index register pointer can be programmed to handle each of the delay values and can be separately updated. Second, the DAGs support circular buffers into which delay lines are easily mapped.

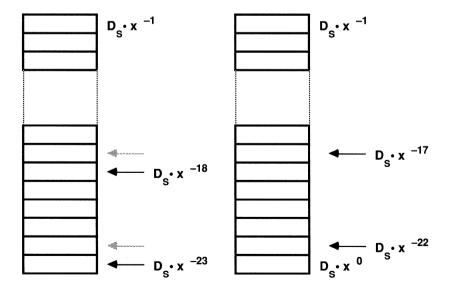

In either scrambler, the twenty-third value is the oldest value, and once used is no longer needed. Thus the newest value can be written over it, so the circular buffer always contains only the 23 most recent values. Figure 2.7 illustrates the circular buffer implementation and shows the appropriate pointers.

Figure 2.7 Circular Buffer Implementation for Scrambler

The value  $x^0$  is the current input value. This value is put into an ALU register. The delayed value,  $D_s \cdot x^{-18}$ , is read from the circular buffer using the address supplied by a pointer (represented in the above diagram with an arrow). Once the location is read, the pointer is decremented to the next location in the buffer, shown with the light arrow. The oldest value is then written to an ALU register; the pointer's address is not yet modified. The necessary XOR operations are performed and the result is output, as well as written to the last buffer location. This pointer is now decremented to the next value, now the oldest.

This process is repeated with each new input bit. When a pointer comes to the first location in the circular buffer and is decremented, it wraps around to the last location in the circular buffer. Eighteen and twentythree unit delays are maintained in the circular buffer, with no need to move data values, just pointer addresses.

The answer mode scrambler works similarly, except with a delay of five units instead of eighteen units. The descrambler, for both call and answer modes, also uses the same basic structure, but with a different flow of data to accomplish the inverse operation.

### 2.4.2 Scrambler/Descrambler Programs

The code in Listings 2.1 and 2.2 implements the V.32 scrambler (call mode) on the ADSP-2100 family processors. There are two modules, a main module and a scrambler module. The main module sets up interrupts, initializes the appropriate registers for interrupt control, initializes index registers for maintenance of the circular buffer, clears the circular buffer to zero and waits in an infinite loop for an interrupt. The only interrupt active in this program is IRQ3. This is the highest priority interrupt, and in this case it corresponds to a sampling interrupt. When a sample is ready to be scrambled, this interrupt is asserted.

The second program module is the actual scrambling routine. Included as part of this module is the *bits* subroutine, which takes 16-bit data values and strips off bits one at a time. The output of this subroutine is a string of simulated serial data values in the most significant bit position of 16-bit words. That is, a 16-bit word is input and 16 words (each of whose value is either H#8000 or H#0000) are output. These simulated serial bits are then passed to the scrambler. The scrambler output is in the AR register at the end of each pass and is written to the data memory location *dac*.

The descrambler program, in Listing 2.3, has the same fundamental structure as the scrambler program, performing the inverse operation of the scrambler.

.MODULE/RAM/ABS=0 cms main routine; This module initializes registers, clears a buffer} { { of length 23 for the call mode scrambler, sets IMASK} { and waits in a loop for sampling interrupt} initial, clear buffer} CALLS: { { INTERRUPTS: only interrupt 3 active} .CONST no bits per word=16; .VAR/DM/RAM/CIRC buffer[23], input buffer [no bits per word]; .GLOBAL input buffer; .PORT cntl port; .EXTERNAL start scramble; {interrupt jump table} RTI; {only INT3 is used} RTI; RTI; JUMP start scramble; {INT3 8 kHz from codec} {main routine} CALL initial; CALL clear buffer; IMASK=H#8; {enable interrupt 3} JUMP mainloop; {loop until interrupted} mainloop: {One time initialization subroutine, sets up registers} initial: IMASK=B#0000; {disable interrupts} ICNTL=H#F; {edge sensitive interrupts} SI=0;DM(cntl port)=SI; {load codec control register} L0=%buffer; {length registers} L1=%buffer; {circular buffer length 23} L2=%buffer; L3=0; {no other index circ buffer} L4=0; L5=0; L6=0; L7=0; {index registers} I0=^buffer; {ds(n-5)} Il=^buffer + 17; {ds(n-18)} I2=^buffer + 22; {ds(n-23)}

```

I3=0000;

I4=^input buffer + 15;

M0=0;

{modify registers}

M1 = -1;

M2=1;

M4 = -1;

M5=1;

SE=4;

{SE for nibble pack}

RTS;

{------CLEAR BUFFER SUBROUTINE-------}

{initialize scramble buffer to zero}

clear buffer: CNTR=%buffer;

DO clear UNTIL CE;

clear:

DM(I0,M1)=0;

RTS;

.ENDMOD;

```

### Listing 2.1 Call Mode Scrambler Main Routine

MODULE call mode scrambler; This module performs V.32 call mode scrambling } { { The generating polynomial is: xin + y(n-18) + y(n-23) } CALLS: bits} { input buffer; .EXTERNAL .CONST no bits per word = 16; .PORT codec; .PORT dac: .ENTRY start scramble; start scramble: AY0=DM(codec); {read from port} CALL bits; {show as serial stream} CNTR=no bits per word; {scramble 16 times} {once for every bit of input} DO scrambl UNTIL CE; AY0=DM(I4,M5); AX0=DM(I1,M1); {d(n-18)}  $AY1=DM(I2,M0); \{d(n-23)\}$ AR=AX0 XOR AY1;  $\{d(n-18) + d(n-23)\}$ AR=AR XOR AY0;  $\{d(n) + d(n-18) + d(n-23)\}$ DM(I2,M1)=AR; {store scramble in buffer} {write new value over oldest} DM(dac)=AR; {out to dac} MODIFY(I4,M4); {reset pointer to last buffer} {value for next input word} scrambl: NOP;

RTI;

AX0=AI0; {expanded Sutput Into ALO; SE=15; CNTR=no\_bits\_per\_word; AY0=H#8000; DO bit\_loop UNTIL CE; AR=AX0; SR=LSHIFT AR (LO); {shift so next bit is} {MSB in reg SR0}

AR=AR0 AND AY0; {mask out all except MS}

DM(I4,M4)=AR;

AY1=SE; {decrement SE for next}

AR=AY1-1;

SE=AR;

I4=^input\_buffer;

SE=4;

RTS;

bit loop:

.ENDMOD;

Listing 2.2 Call Mode Scrambler Scrambling Routine

.MODULE/RAM/ABS=0 main routine; Descrambling Routine } { Call Mode Functions implemented: } { d(n) = di(n) + d(n-18) + d(n-23)ł System file: fullpm.sys} { initial, clear buffer, output} ł CALLS: .VAR/DM/RAM/CIRC buffer[23]; . PORT codec: .PORT dac: .PORT cntl port; RTI; RTI; RTI; {int0-2 not used} JUMP start descramble; {INT3 8 kHz from codec} CALL initial; CALL clear buffer; IMASK=h#8; {enable interrupts} mainloop: JUMP mainloop; {loop until interrupted} {------ descramble subroutine -------} {addressing circular buffer with 2 pointers for modem scrambler} start descramble: AY0=DM(codec); {read from port}  $\{d(n-18)\}$ AX0=DM(I1,M1); AY1=DM(I2,M0);  $\{d(n-23)\}$ AR=AX0 XOR AY1;  $\{d(n-18) + d(n-23)\}$ AR=AR XOR AY0;  $\{d(n) + d(n-18) + d(n-23)\}$ DM(I2, M1) = AY0;{store scramble in buffer} {input stored... not output} CALL output; AR=0; {clear AR for next time} RTI; {initialize registers} initial: IMASK=B#0000; {disable interrupts} ICNTL=H#F; {edge level interrupts} SI=0; DM(cntl port)=SI; {load codec control reg} L0=%buffer; {circular buffer length 23} L1=%buffer;

```

L2=%buffer;

L3=0;

L4=0;

L5=0;

L6=0;

L7=0;

I0=^buffer;

I1=^{buffer} + 17;

I2=^{buffer} + 22;

M0=0;

M1 = -1;

SR0=0;

SR1=0;

SE=16;

RTS;

----- clear buffer subroutine ---

{----

--- }

{initialize buffer to zero}

clear buffer:

CNTR=%buffer;

DO clear UNTIL CE;

clear:

DM(I0, M1) = 0;

RTS;

{----- output routine packs serial into 16 bit words -----}

output:

SR=SR OR LSHIFT AR(LO);

AY0=SE;

AR=AY0 -1;

SE=AR;

IF EQ CALL out;

RTS;

out:

DM(dac)=SR1;

SR0=0;

SR1=0;

SE=16;

RTS;

```

.ENDMOD;

### Listing 2.3 Call Mode Descrambler Routine

### 2.5 RAISED COSINE FILTER

For the V.32 modem recommendation, 5-bit symbols are modulated by a carrier of 1800 Hz. This modulation is performed digitally. Coupled with the modulator and the demodulator are pulse shaping low pass filters. These digital filters eliminate intersymbol interference (ISI) on the bandlimited GSTN.

A brief development of the theory of pulse shaping filters follows. For a more complete theoretical discussion of pulse shaping filters, see "References" at the end of this chapter: Bingham, Lee and Messerschmitt, Proakis.

Low pass transmitted signals can be shown to have the form

$$\sum_{n=0}^{\infty} I_n g(t-nT)$$

where  $I_n$  is the discrete code word and g(t) is a pulse. For the bandlimited channel, we desire a transmitted pulse g(t) that produces no ISI. If the channel is ideally bandlimited, then an ideally bandlimited pulse can be used. In the frequency domain, this ideally bandlimited pulse can be described as:

G(f) = T for f < 1/2T0 for  $f \ge 1/2T$

This spectrum has an ideal rectangular shape.

In the time domain, this ideal spectrum shape is the sinc function:

$g(t) = \sin(\pi t/T)/(\pi t/T)$

The nulls (zero values of the pulse function) occur at multiples of T, the baud rate. Because of the placement of the nulls, there is no additive interference due to previous symbols; there is no ISI.

The ideal pulse shaping filter is not practical to implement. The ideally bandlimited frequency response has a corresponding infinite impulse response. Although the impulse response has a zero value at all multiples of T, any mistiming in the modem produces an infinite series of ISI terms.

A pulse shaping filter that is practical and widely used in digital communications is the raised cosine pulse shaping filter. The raised cosine pulse shaping filter is realizable, unlike the ideal pulse shaping filter. The raised cosine function has tails that decay proportional to  $1/t^3$ , whereas the ideal pulse tails off proportional to 1/t. Mistiming errors in sampling in the modem therefore have a much less dramatic effect on the amount of ISI in the raised cosine pulse filter.

A generic formula for the impulse response of the raised cosine filter, p(t), is shown below. *T* is the symbol rate in Hz, *t* is the sampling rate in Hz, and  $\alpha$  is the rolloff factor.

$p(t) = \frac{\sin (\pi t/T) \bullet \cos (\alpha \pi t/T)}{(\pi t/T) \bullet (1 - (2\alpha \pi t/T)^2)}$

The rolloff factor,  $\alpha$ , represents the amount of excess bandwidth required. A raised cosine with a rolloff factor of 0 needs the least excess bandwidth. As  $\alpha$  varies from 0 to 1, the amount of excess bandwidth required increases from 0 to 100%. For purposes of this implementation, a common rolloff factor of 0.25 is used. For the V.32 modem, the symbol rate, T, is specified at 2400 symbols per second. The sampling rate, t, is usually 9600 Hz. The frequency response of the raised cosine pulse shaping filter with these parameter values is shown in Figure 2.8, on the following page.

The pulse shaping filter usually spans four baud intervals. For a sampling rate of 9600 Hz and a symbol rate of 2400 Hz, a 17-tap FIR filter can be used.

### 2.5.1 ADSP-2100 Family Implementation

The raised cosine pulse shaping filter can be implemented in the modem as a simple FIR filter. Implementation of FIR filters on the ADSP-2100 family is straightforward. The dual DAGs with circular buffering and the on-chip Harvard architecture allows for efficient realization of FIR filter structures. A complete description of FIR filters as well as other fixedcoefficient filters can be found in *Digital Signal Processing Applications Using the ADSP-2100 Family*, Chapter 5 (see "Literature" at the beginning of this book).

Filter coefficients are arrived at using the formula above, generated with a C program. The coefficients are scaled to provide a filter with 0 dB gain.

# Impulse response

Figure 2.8 Raised Cosine Pulse Shaping Filter,  $\alpha$ =0.25

The coefficients represent a rolloff factor of 0.25, and the generated impulse response spans four baud intervals.

For the V.32 modem, the filter input is a digitally modulated value (1800 Hz carrier). Samples are processed at the baud rate (2400 baud) and are interpolated, zero-filled, to provide filter input at a rate of 9600 Hz. Samples are processed in quadrature. Figure 2.9 shows the relationship of the filter to the digital modulator and the data rates.

Listing 2.4 contains the ADSP-2100 family code for implementation of the raised cosine filter. The coefficients can be found in the data file *coef.dat*.

### Figure 2.9 Modem Transmitter

```

.MODULE/boot=0

fir sub;

Ł

Pulse Shape filter routine for V.32

ICASSP DEMO

Rev History

2/8/90 take APP VOL I FIR routine

adapt for V.32

}

.ENTRY

pulse shape;

.CONST

PSF length = 89;

.EXTERNAL

Real_PSF_delay_line, Imag_PSF_delay_line, Pulse_Shape_Coeff;

real_PSF_i0, imag_PSF_i0;

.EXTERNAL

.VAR/DM

psf save I0;

.VAR/DM

psf save L0;

psf save I4;

.VAR/DM

.VAR/DM

psf save L4;

.VAR/DM

test psf1;

.VAR/DM

test psf2;

```

### (listing continues on next page)

pulse shape: DM(psf save I0) = I0; DM(psf save L0) = L0; {save I0,L0,I4,L4} DM(psf save I4) = I4; DM(psf save L4) = L4;IO = DM(real PSF iO);I4 = ^Pulse Shape Coeff; L0 = psf length; L4 = psf length; {--- Do real part of the filter. ax0 contains the x value from the signal map module. } DM(I0, M2) = AX0;{dump new vals into delay line} CNTR = PSF Length - 1; MR=0, MX0=DM(I0,M2), MY0=PM(I4,M5); MR=MR+MX0\*MY0(SS), MX0=DM(I0,M2), MY0=PM(I4,M5); sop: IF NOT CE JUMP sop; MR=MR+MX0\*MY0(RND); IF MV SAT MR; AX0 = MR1;{filtered X in ax0} DM(real PSF i0) = I0;{--- Do the imaginary part of the Pulse Shape filter. ax1 contains the imaginary part of the point from the signal map module. } IO = DM(imag PSF iO);DM(I0, M2) = AX1;{dump new vals into delay line} CNTR = PSF Length - 1; MR=0, MX0=DM(I0,M2), MY0=PM(I4,M5); MR=MR+MX0\*MY0(SS), MX0=DM(I0,M2), MY0=PM(I4,M5); imag sop: IF NOT CE JUMP imag sop; MR=MR+MX0\*MY0(RND); IF MV SAT MR; AX1 = MR1;{filtered Y in ax1} DM(imag PSF i0) = I0; IO = DM(psf save IO); LO = DM(psf save LO);I4 = DM(psf save I4); L4 = DM(psf save L4);RTS; .ENDMOD;

Listing 2.4 Raised Cosine Filter

### 2.6 TRELLIS ENCODING

The GSTN was intended for voiceband transmission and is bandlimited 200 Hz to 3400 Hz. Data rates in excess of the upper band limit can be realized only by the transmission of multiple bits per symbol interval. Data rates of 9.6 Kbits per second can be achieved on unconditioned circuits and data rates of up to 16.8 Kbits per second can be realized on conditioned leased lines using the technique known as trellis coded modulation (TCM).

The V.32 modem recommendation specifies trellis encoding as an option. Four-bit symbols are encoded into 5-bit symbols that are made up of four information bits and a redundant bit. These 5-bit symbols are used with a 32 carrier state QAM modulator. A 2400 baud rate is used and 9600 information bits per second are transmitted. A trellis encoded scheme offers much better performance than a non-encoded scheme. It results in a much higher immunity to noise for a given error rate and can reduce the block error rate by three orders of magnitude for a given signal-to-noise ratio.

There are two fundamental types of codes used in channel encoding. Linear block codes include Hamming codes, BCH (Bose-Chadhuri-Hocquenghem) codes, Reed-Solomon codes, Galay codes and many others. The convolutional code, which is specified for V.32 modems can be implemented using a shift register and can be described using a diagram called a trellis diagram.

Suppose we can achieve a certain  $P_e$  (probability of error) in an uncoded system operating on a bandlimited channel. We can attempt to improve system performance by coding. If we add a single redundant bit to a binary symbol with *k* bits, we increase the number of waveforms that the modulator must produce from 2<sup>k</sup> to 2<sup>k+1</sup>. An increase in alphabet size on the same bandwidth requires a 3 dB increase in the signal to noise ratio to achieve the same  $P_{e^*}$ . That is, coding alone decreases the performance of the system.

Trellis coded modulation employs signal set partitioning in addition to redundant coding in order to increase the system performance. In the case of the V.32 modem, there are 32 modulator states. Of the four input bits to the encoder, only two are encoded. Two bits pass through uncoded and two bits are encoded into three output bits. The three bits provide a mechanism for dividing the 32 modulator states into 8 subsets of 4 modulator carrier states. The coded bits identify the subset of the 32

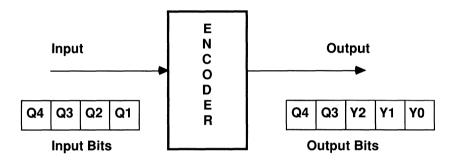

modulator states and the uncoded bits select a point within the subset. Figure 2.10 shows the input and output bits of the trellis encoder. Bits Q1 through Q4 are the input bits. Bits Q3 and Q4 pass through the encoder unchanged. Bits Q1 and Q2 are encoded to give Y1, Y2 and the redundant error correcting bit Y0. Bits Y0, Y1, Y2 identify the subset while the bits Q3 and Q4 identify the point within the subset.

Figure 2.10 Encoder Block Diagram

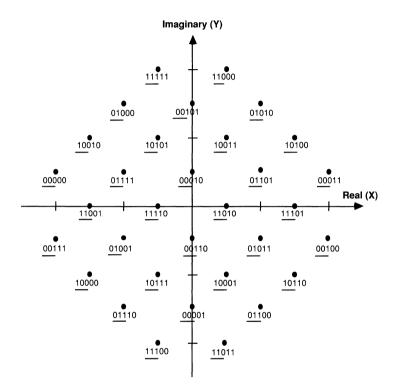

The signal set for the V.32 modem (and other TCM schemes) has been designed so that there is a large distance between the members of each subset. The 32-state signal constellation for the V.32 modem is shown in Figure 2.11. Bits are ordered on this diagram left to right, most significant to least significant: Y0 Y1 Y2 Q3 Q4. The signal space mapping for the redundant coding is from Figure 3/V.32 of the V.32 recommendation.

The signal set is located on a quadratic grid known as a  $Z_2$  lattice and the signal set type is known as 32 CROSS. In order to transmit *m* bits per signalling interval,  $2^{m+1}$  signals are needed. The coding gain (performance of the coded signals versus uncoded signals) is approximately 4 dB for any *m*. The closest distance between any two points on the signal set is  $\Delta_0$ . The closest distance between any two points in a subset (i.e., points that have the same Y0, Y1 and Y2 bits) is  $\sqrt{8} \Delta_0$  for the 32 CROSS signal set.

All bit patterns that begin with the same three bits are spread out on the signal constellation. This signal set partitioning along with the redundant coding are the fundamentals of TCM.

Figure 2.11 V.32 Signal Constellation

### 2.6.1 ADSP-2100 Family Implementation

Trellis encoding for the V.32 modem consists of two encoding operations: a differential encoder, implemented as a lookup table and a convolutional encoder, performed using a shift register and Boolean logic. Together, these two encoders generate a 5-bit symbol from a 4-bit input word.

The serial input bits to the encoder are Q1, Q2, Q3 and Q4 (Q1 first, Q4 last). Three of the output bits are Y0, Y1 and Y2, and the other two output

bits are Q3 and Q4, unchanged from the input. Y1 and Y2 are generated in the differential encoder. Y0, the redundant bit for error correction, is generated in the convolutional encoder.

The differential encoder takes as input the first two bits, Q1 and Q2, and produces two output bits, Y1 and Y2. Previous output bits, Y1(n–1) and Y2(n–1) are also used in the differential encoder. The encoder is easily implemented on the ADSP-2100 family as a lookup table. The input bits and the previous output bits are combined to a 4-bit value that serves as a pointer into the lookup table. For example, assume that the current input bits are Q1=1, Q2=0, Y1(n–1)=0 and Y2(n–1)=1, for a 4-bit value of 1001. This corresponds to the 1001 (ninth) entry in the lookup table, from which the current Y1 and Y2 outputs are read. Table 2.1 shows the lookup table for differential encoding.

| Inputs |    | Previous | Outputs | Outputs |    |

|--------|----|----------|---------|---------|----|

| Q1     | Q2 | Y1(n-1)  | Y2(n-1) | Y1      | Y2 |

| 0      | 0  | 0        | 0       | 0       | 0  |

| 0      | 0  | 0        | 1       | 0       | 1  |

| 0      | 0  | 1        | 0       | 1       | 0  |

| 0      | 0  | 1        | 1       | 1       | 1  |

| 0      | 1  | 0        | 0       | 0       | 1  |

| 0      | 1  | 0        | 1       | 0       | 0  |

| 0      | 1  | 1        | 0       | 1       | 1  |

| 0      | 1  | 1        | 1       | 1       | 0  |

| 1      | 0  | 0        | 0       | 1       | 0  |

| 1      | 0  | 0        | 1       | 1       | 1  |

| 1      | 0  | 1        | 0       | 0       | 1  |

| 1      | 0  | 1        | 1       | 0       | 0  |

| 1      | 1  | 0        | 0       | 1       | 1  |

| 1      | 1  | 0        | 1       | 1       | 0  |

| 1      | 1  | 1        | 0       | 0       | 0  |

| 1      | 1  | 1        | 1       | 0       | 1  |

Table 2.1 Differential Encoder Lookup Table

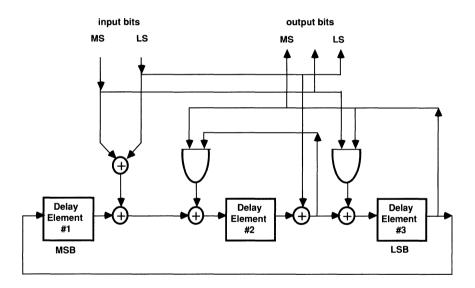

The convolutional encoder (Figure 2.12) uses a shift register structure to examine the four incoming bits (the output of the differential encoder) and build a 5-bit symbol. The five output bits of the convolutional encoder consist of the four input bits plus an additional redundantly coded fifth bit. This additional bit increases the complexity of the signal set, but limits the number of possible transitions between bit patterns. For any given 5-bit convolutionally encoded word, only half of the signal states can follow. In other words, the process of convolutional encoding prohibits transitions from any particular signal state to only half of the possibilities. This property is exploited in the Viterbi decoder in the receiver.

Figure 2.12 Convolutional Encoder Block Diagram

Listing 2.5 contains a ADSP-2100 family subroutine that provides both the differential encoder and the convolutional encoder. The input is assumed to be a single bit residing in the most significant bit position of a 16-bit word. Listing 2.6 shows the convolutional encoder routine that is called by the program in Listing 2.5, and Listing 2.7 contains the routine that performs signal mapping on the encoded data.

```

.MODULE/RAM

trellis;

.VAR/DM/RAM

t table[16];

.VAR/DM/RAM

last ys;

.VAR/DM/RAM

bit count;

diff out;

.VAR/DM/RAM

.VAR/DM/RAM

delay_val_1;

.VAR/DM/RAM

delay_val_2;

.VAR/DM/RAM

delay val 3;

.VAR/DM/RAM

Y1;

.VAR/DM/RAM

Y2:

.INIT

t table: 0,1,2,3,1,0,3,2,2,3,1,0,3,2,0,1;

.ENTRY

trellis encode;

.PORT

dac;

.PORT

adc;

.GLOBAL

t table, bit count, last ys;

{--bit count is intially 4---}

trellis encode: SE=DM(bit count);

SI=DM(adc); {take in new 8000 or 0000}

SR=SR OR LSHIFT SI (LO); {count up 4 bits,}

Q1Q2 pack:

AY0=SE;

{shift into SR register}

AR=AY0 -1;

SE=AR;

DM(bit count)=SE; {store decremented count}

IF EQ JUMP packed;

RTI;

packed:

AX0=SR1;

{stored as 4 bits}

AX1=4;

\{Q1 \ Q2 \ Q3 \ Q4\}

DM(bit count)=AX1;

SR0=0;

SR1=0;

CALL d encode;

RTI;

```

{input: AX0 -> 0 0 0 X where X -> bits 0 0 0 0 01020304} d encode: I3=^t table; {mask to keep Q1 Q2} AY0=h#000C; AR=AX0 AND AY0; AY1=DM(last\_ys); {last\_output Y1 Y2} AR=AR XOR AY1; {AR is Q1 Q2 Y1 Y2} M3=AR; {address in lookup} MODIFY(I3,M3); {for new Y1 Y2} SI=DM(I3,M0); DM(last ys)=SI; {AY0 ->encoded Y1 Y2} AY1=3; AF=AX0 AND AY1; {keep Q3 Q4} SR=LSHIFT SI BY 2(LO); AR=SR0+AF; {AR ->Y1 Y2 Q3 Q4} DM(diff out)=AR; {store output of diff encode} DM(dac)=AR; CALL c encode; {call convolutional encode} RTS;

.ENDMOD;

Listing 2.5 Trellis Encoder Program

.MODULE/RAM conv encode; { Trellis Encoder for V.32 Modem Implements convolutional encoder Four bit symbols, output of the differential encoder Input: Output: Five bit symbol in the LSB positions} diff\_out; conv\_out; .VAR/DM/RAM {differential encode output} .VAR/DM/RAM {convolutional encode output} {01020304 as 4 LSBs} .VAR/DM/RAM packed 4 bits; delay val 1; {conv. enc delay element} .VAR/DM/RAM .VAR/DM/RAM delay\_val\_2; {conv. enc delay element} .VAR/DM/RAM delay val 3; {conv. enc delay element} .VAR/DM/RAM intermed 1: intermed 2; .VAR/DM/RAM .VAR/DM/RAM Y0: {output bit Y0} .VAR/DM/RAM Y1; {output bit Y1} .VAR/DM/RAM Y2: {output bit Y2} .GLOBAL conv out; .GLOBAL delay val 1, delay val 2, delay val 3; .GLOBAL intermed 1, intermed 2, packed 4 bits; c encode; .ENTRY .EXTERNAL sig map, dac; { \_\_\_\_\_\_ CONVOLUTIONAL ENCODE \_\_\_\_\_\_} {Input is Y1Y2Q3Q4 located in "diff out" 4 LSBs} {Output is 3 encoded bits in data mem locations Y0 Y1 Y2} {calls "pack up 5 bits" for output to dac} c encode: SR0=0;{clear shift result} SR1=0; SI=DM(diff out); {get input from diff encoder} SE = -3;SR=LSHIFT SI BY -3(HI); {put Y1 in LSB position} AY0=1; AR=SR1 AND AY0; {separate Y1} DM(Y1) = AR;AX0=AR; SR=LSHIFT SI BY -2(HI); AR=SR1 AND AY0; {separate Y2 and store} DM(Y2) = AR;AY0=AR;

AR=AX0 XOR AY0; {op #1} AY1=DM(delay val 3); AR=AR XOR AY1; {op #2} DM(intermed 1)=AR; AX0=DM(delay val 1); AR=AX0 XOR AY0; {delay val 1 XOR Y2 op #5} DM(intermed 2)=AR; AY0=DM(delay val 2); DM(delay val 3)=AY0; {update delay val 3} AR=AR AND AYO;  $\{and 1\}$ AY1=DM(intermed 1); AR=AR XOR AY1; DM(delay\_val\_1)=AR; {update delay\_val\_1} AX1=DM(Y1);AR=AX1 AND AY0; {and 2} AY0=DM(intermed 2); AR=AR XOR AY0; DM(delay val 2)=AR; {update delay val 2} DM(Y0) = AR;CALL pack up 5 bits; RTS; {Packs up convolutional bits as 5 LSBs Y0 Y1 Y2 Q3 Q4} {Outputs to DAC} pack up 5 bits: SR0=0; {pack up bits as Y0Y1Y2Q3Q4} SR1=0; {clear SR} SR1=DM(diff out); SI=DM(Y0); SR=SR OR LSHIFT SI BY 4 (HI); DM(conv out)=SR1; DM(dac) = SR1;SR0=0; SR1=0; CALL sig map; RTS;

.ENDMOD;

#### Listing 2.6 Convolutional Encoder Routine

.MODULE signal\_map;

{ This module takes the output of the convolutional encoder, that is, a five bit code residing in the LSBs of the data memory location "conv\_out", and looks up the x and y coordinates as defined by the CCITT spec for the V.32 modem.

The coordinates are given in the CCITT spec as whole integers. They are represented in a 16-bit fixed format as follows:

|                    | 0<br>1<br>2<br>3<br>4<br>-1<br>-2<br>-3 |                  | 0000<br>2000<br>4000<br>6000<br>7FFF<br>E000<br>C000<br>A000 | exadecima                     | al                                                               |                               |                               |                               |

|--------------------|-----------------------------------------|------------------|--------------------------------------------------------------|-------------------------------|------------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|

| Registe<br>}       | ers                                     | used:            |                                                              |                               |                                                                  |                               |                               |                               |

| .VAR/DM<br>.VAR/DM |                                         | x_tabl<br>y_tabl |                                                              |                               |                                                                  |                               |                               |                               |

| .INIT              |                                         |                  | H#0000,<br>H#4000,<br>H#2000,<br>H#E000,                     | H#0000,<br>H#4000,<br>H#A000, | 00, H#000<br>H#8000,<br>H#4000,<br>H#2000,<br>H#A000,<br>H#A000; | H#C000,<br>H#C000,<br>H#6000, | H#C000,<br>H#C000,<br>H#E000, | H#4000,<br>H#A000,<br>H#6000, |

| .INIT              |                                         |                  | H#6000,<br>H#E000,<br>H#C000,<br>H#C000,                     | H#E000,<br>H#A000,<br>H#4000, | 00, H#200<br>H#E000,<br>H#2000,<br>H#4000,<br>H#0000,<br>H#7FFF; | H#6000,<br>H#A000,<br>H#4000, | H#E000,<br>H#2000,<br>H#4000, | Н#6000,<br>Н#С000,<br>Н#С000, |

```

.EXTERNAL conv out, dac;

sig map;

.ENTRY

sig map:

I1=^x table;

I2=^y table;

M0 = 0;

M1=DM(conv out);

MODIFY(I1,M1);

MODIFY(I2,M1);

AX0=DM(I1,M0); {x value in ax0}

AX1=DM(I2,M0); {y value in ax1}

DM(dac) = ax0;

DM(dac) = ax1;

RTS:

.ENDMOD;

```

#### Listing 2.7 Signal Mapping Routine

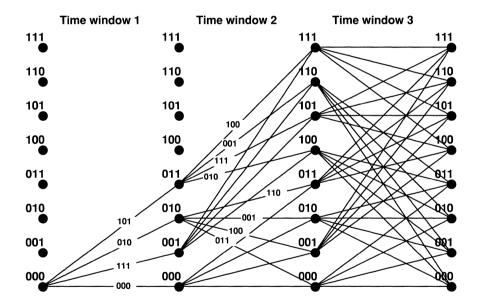

### 2.7 VITERBI DECODING

The V.32 recommendation specifies a trellis or convolutional encoding of data before transmission. The most common technique used for decoding received data is Viterbi decoding. The Viterbi algorithm is a general purpose technique for making an error-corrected decision. Viterbi decoding provides a certain degree of error correction by determining from the received bit pattern the value that was the most likely to have been transmitted. The Viterbi algorithm can be used for many applications where error correcting is required. Its application in the V.32 modem is similar to that used in other digital data communication schemes, such as digital telephones.

In order for the Viterbi algorithm to decode received data properly, the model for encoding the transmitted data must be known. In trellis encoding, it is assumed that the three delay elements of the encoder contain zeros initially. At each time period, a new 2-bit input is presented. The contents of the delay elements are changed accordingly and a 3-bit output is produced. If the three delay elements are treated as a 3-bit word, where delay element 1 is the most significant bit and delay element 3 is

the least significant bit, then the state of the delay elements collectively can be represented by that 3-bit value.

It is possible to derive a state diagram or table from this specification. The three delay elements in the encoder are labelled from left to right as element 1, 2 and 3, respectively, in Figure 2.12 (on page 2-25). At any moment, each delay element has stored in it a 1 or a 0. The possible combinations of bits in the three delay elements or the possible states is eight. The state table shows the eight possible states of these three storage elements. It also shows that for any 2-bit input to the encoder, the three delay elements go to some new state and the encoder also produces an output. The state table showing the state transitions with the encoder inputs and outputs is shown in Table 2.2.

| Beginnin | g     |        | End   | Beginnir | ıg    |        | End   |

|----------|-------|--------|-------|----------|-------|--------|-------|

| State    | Input | Output | State | State    | Input | Output | State |

| 000      | 00    | 000    | 000   | 100      | OÓ    | 000    | 010   |

| 000      | 01    | 101    | 011   | 100      | 01    | 101    | 001   |

| 000      | 10    | 010    | 010   | 100      | 10    | 010    | 000   |

| 000      | 11    | 111    | 001   | 100      | 11    | 111    | 011   |

|          |       |        |       |          |       |        |       |