E

# **Advanced Micro Devices**

# AmZ8000 Family Data Book

Copyright © 1980 by Advanced Micro Devices, Inc.

Portions of the information in this book were originated by Zilog, Inc. and are used here with their permission.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 453, Sunnyvale, California 94086 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

> > AM-PUB098

.

.

### PREFACE

The present state of MOS LSI semiconductor technology has permitted powerful and complex generalpurpose processors to be economically incorporated into single silicon chips. This capability ushers in a new era of system design, where for the first time low cost tools are available for solving many complex problems. Significant levels of computing power are now available inexpensively and can be used both to lower the cost of high performance systems and to improve the efficiency of programmers in their increasingly more complex tasks.

The AmZ8000 Family is the first integrated processor family to fully exploit this new era, breaking tradition with the legacy of compromised performance dictated by past manufacturing technologies. The two processors in the family incorporate many of the features heuristically evolved from both minicomputer and main-frame systems. This gives the applications programmer, the systems programmer and the system designer the power and flexibility required for today's complex systems.

This Data Book is one of a series of documents that support the AmZ8000 Family. The AmZ8000 Processor Instruction Set book (AM-PUB086) provides a complete, detailed description of all the processor instructions; the AmZ8000 Interface Manual (AM-PUB089) provides a detailed discussion of the CPU interface and its use with several support devices; AmZ8010 Memory Management introduction (AM-PUB093). Additional information is currently being prepared for publication.

### TABLE OF CONTENTS

| 1. | Introduction to AmZ8000 Family                                      | . 1-1 |

|----|---------------------------------------------------------------------|-------|

| 2. | Processor Architectural Overview                                    | . 2-1 |

| 3. | System Architecture Overview                                        | . 3-1 |

|    | Component Data Sheets                                               |       |

|    | Analog Interface Components                                         |       |

|    | Memory Components                                                   |       |

|    | AmSYS <sup>™8</sup> Development System, Software and Board Products |       |

| Ap | pendices                                                            |       |

| •  | - Advanced Commitment to Excellence (ACE)                           | . A-1 |

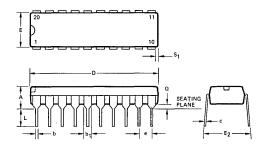

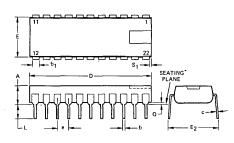

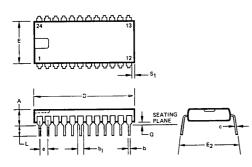

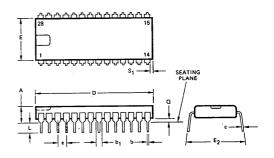

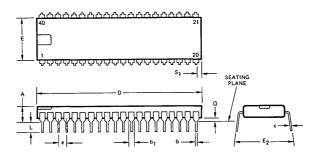

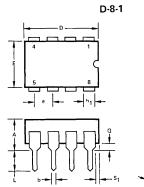

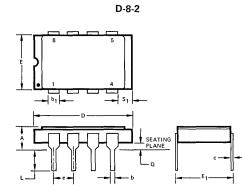

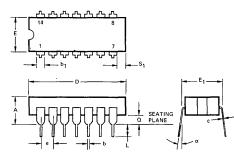

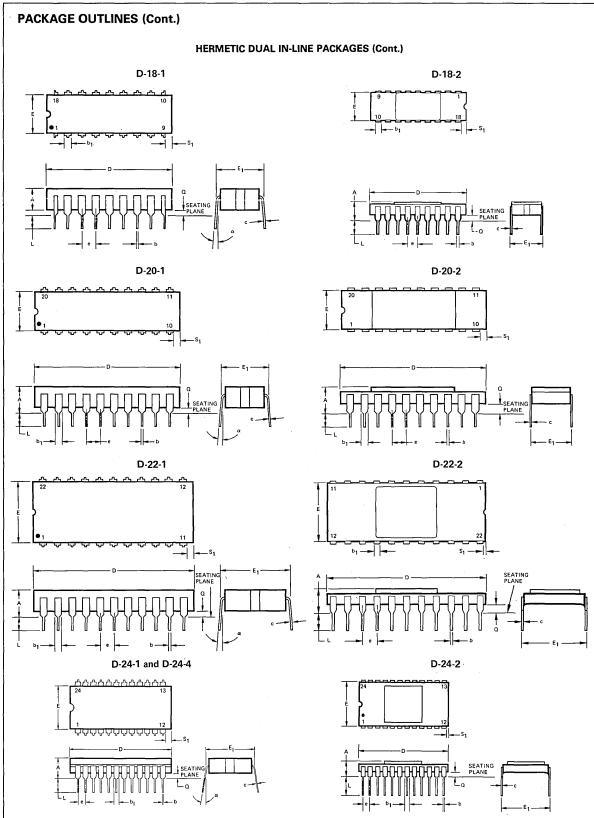

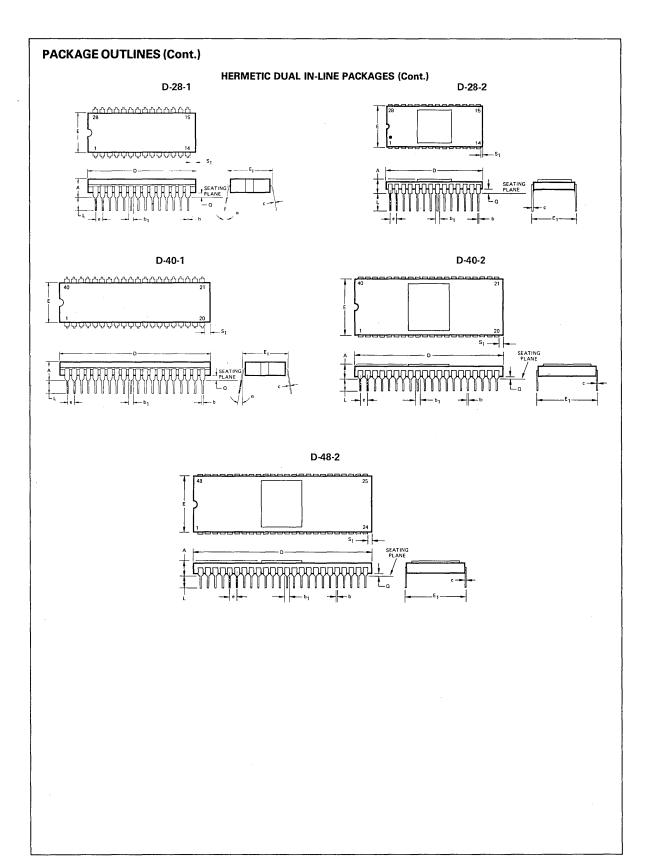

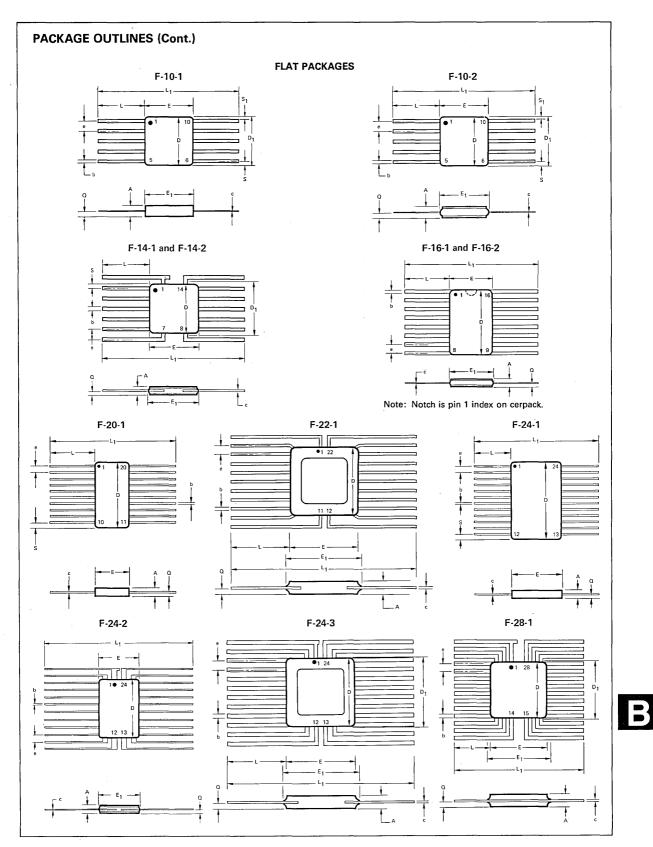

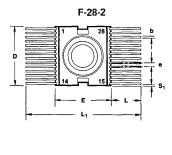

|    | - Package Dimensions                                                | . B-1 |

|    | - MIL-STD-883/MIL-M-38510                                           | . C-1 |

### AmZ8000 Literature

### Processor Instruction Set

Defines the exact form and function of each CPU instruction. AM-PUB086

**Processor Interface Manual** Describes hardware interconnections between CPU and peripherals. Describes interrupt daisy chain and multimicroprocessor systems. AM-PUB089

Memory Management An introduction to memory management concepts and the AmZ8010 MMU device. AM-PUB093

### COMPONENT PART NUMBER INDEX

| AmZ8000 Proces                        | SSOIS                                                                              |

|---------------------------------------|------------------------------------------------------------------------------------|

| AmZ8001                               | Segmented 16-Bit Microprocessor 4-1                                                |

| AmZ8002                               | Non-Segmented 16-Bit Microprocessor 4-22                                           |

| AmZ8000 Family                        |                                                                                    |

| ۔<br>AmZ8010                          | Memory Management Unit 4-42                                                        |

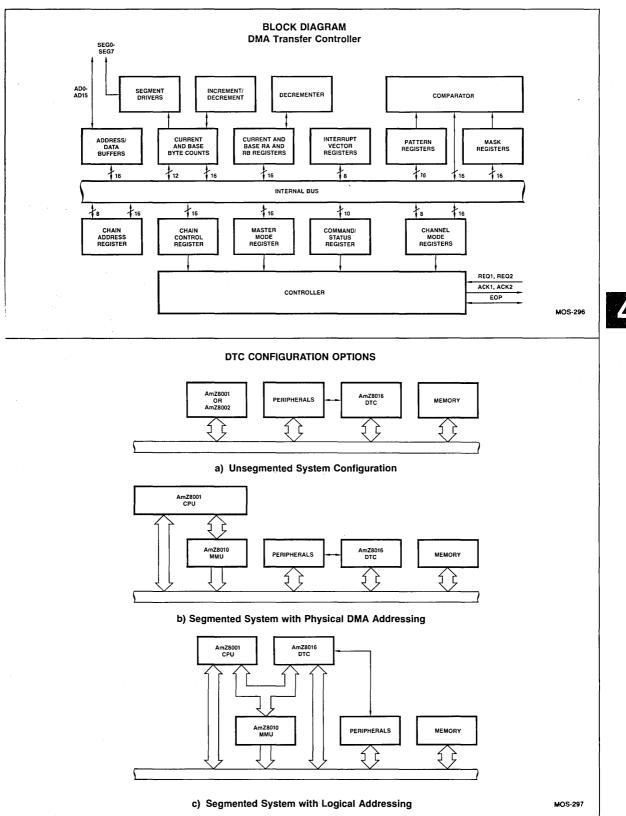

| AmZ8016                               | Direct Memory Access Transfer Controller                                           |

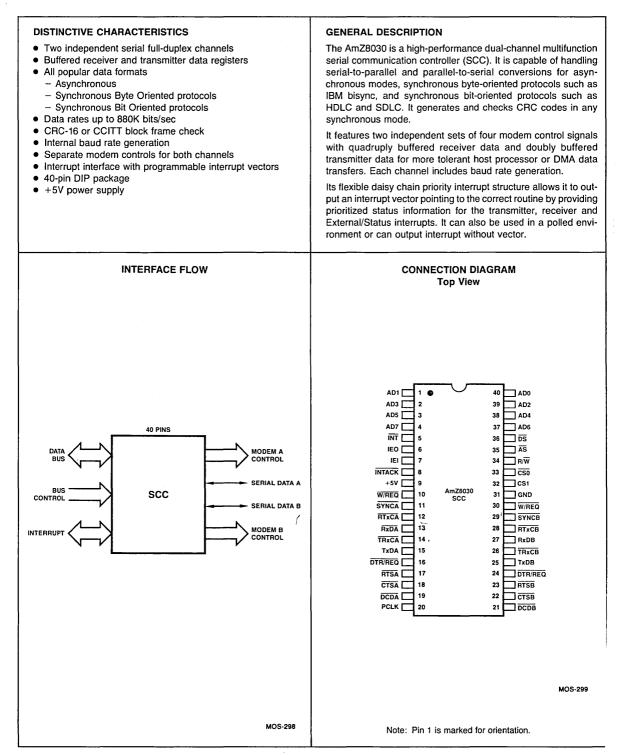

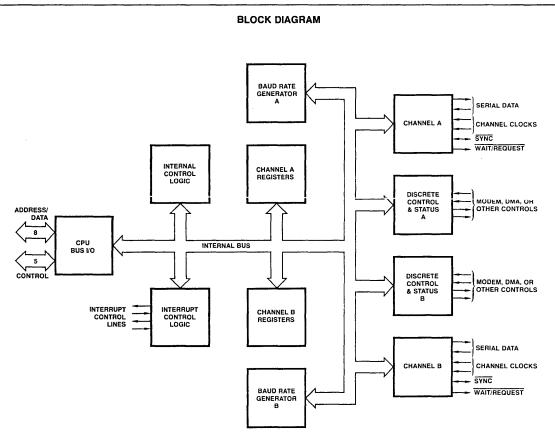

| AmZ8030                               | Serial Communication Controller                                                    |

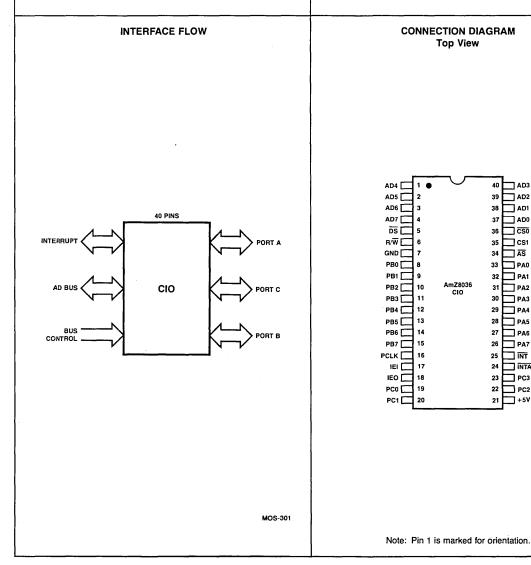

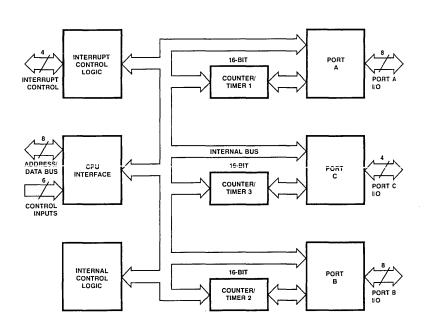

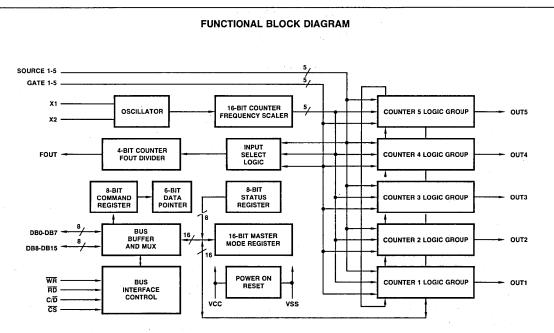

| AmZ8036                               | Counter, Parallel I/O Interface                                                    |

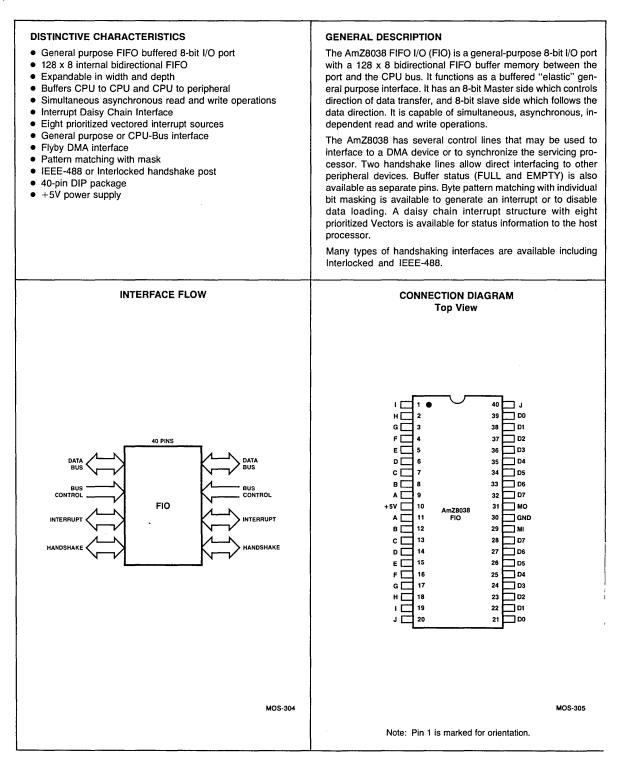

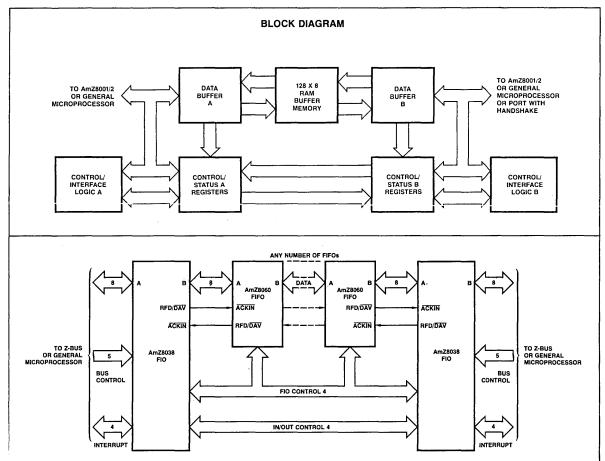

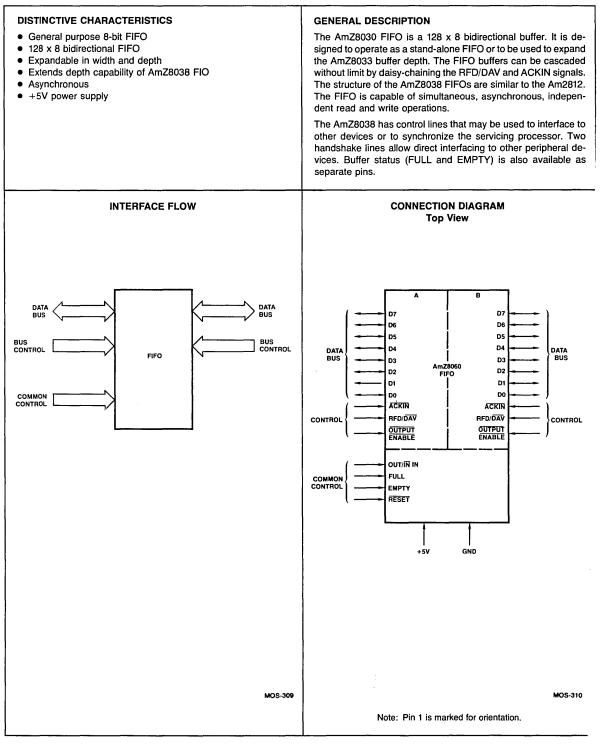

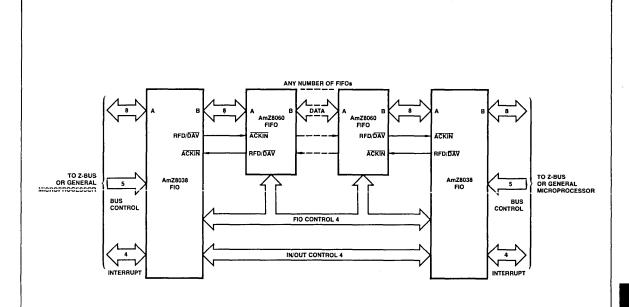

| AmZ8038                               | FIFO Buffered Parallel I/O Interface                                               |

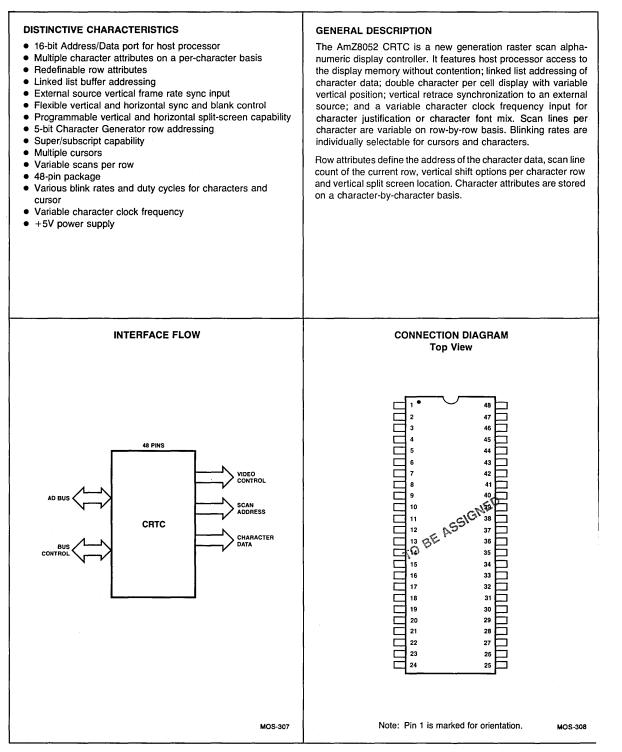

| AmZ8052                               | CRT Controller                                                                     |

| AmZ8060                               | FIFO Buffer Unit and FIO Expander                                                  |

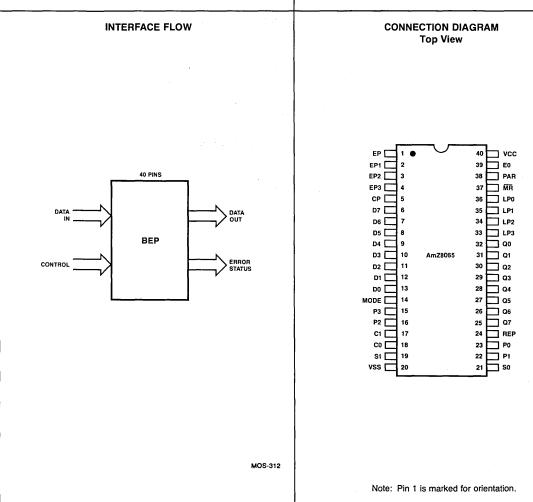

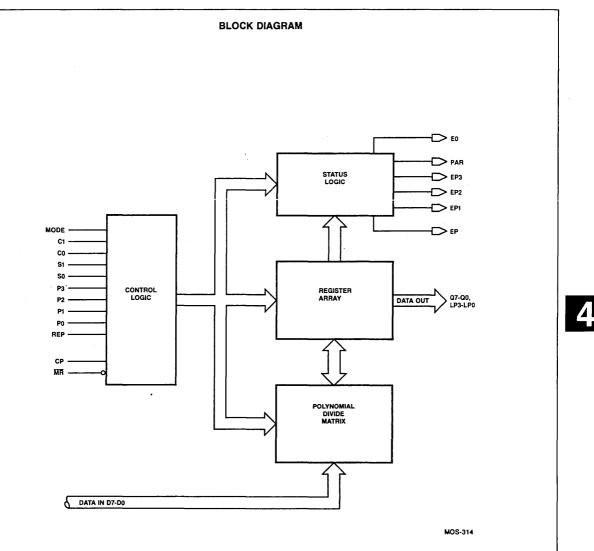

| AmZ8065                               | Burst Error Processor                                                              |

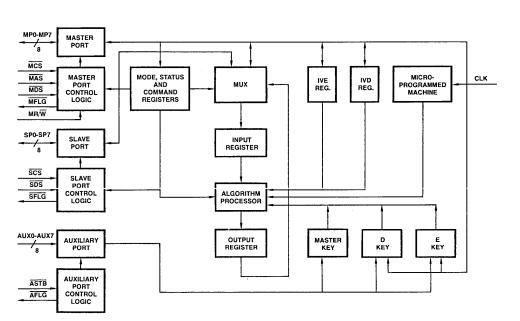

| AmZ8068                               | Data Ciphering Processor                                                           |

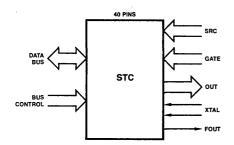

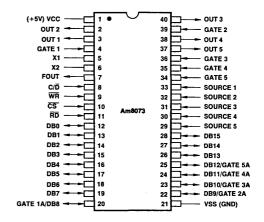

| AmZ8073                               | System Timing Controller                                                           |

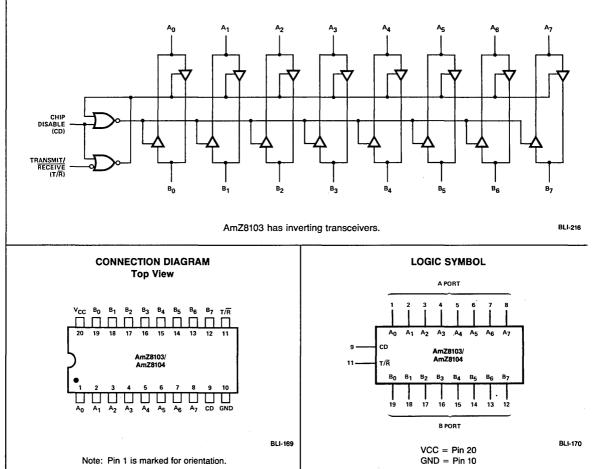

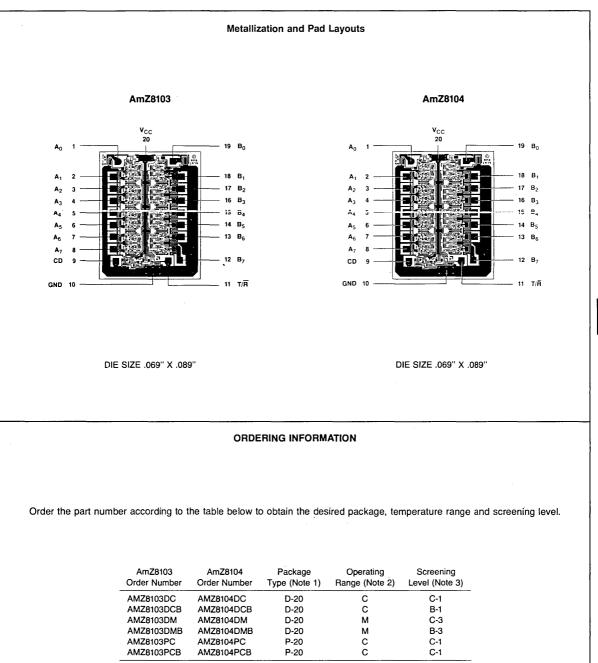

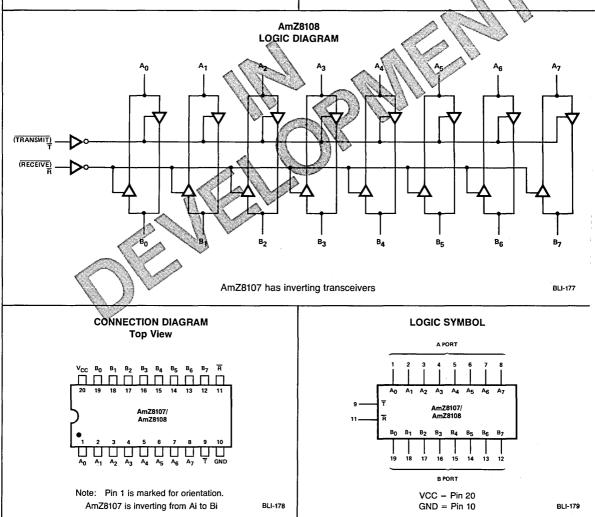

| AmZ8103/4/7/8                         | Octal Bidirectional Buffers                                                        |

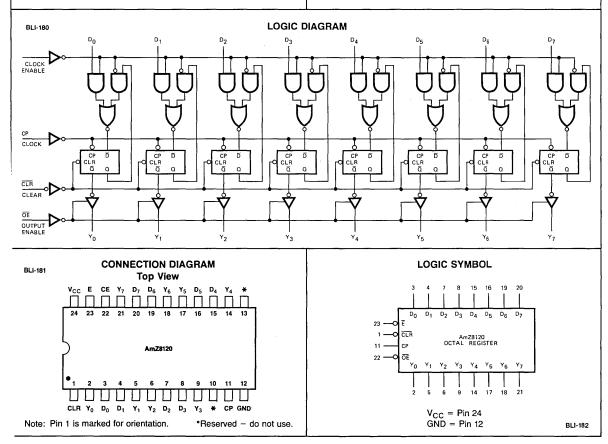

| AmZ8120                               | Octal D-Type Flip-Flop                                                             |

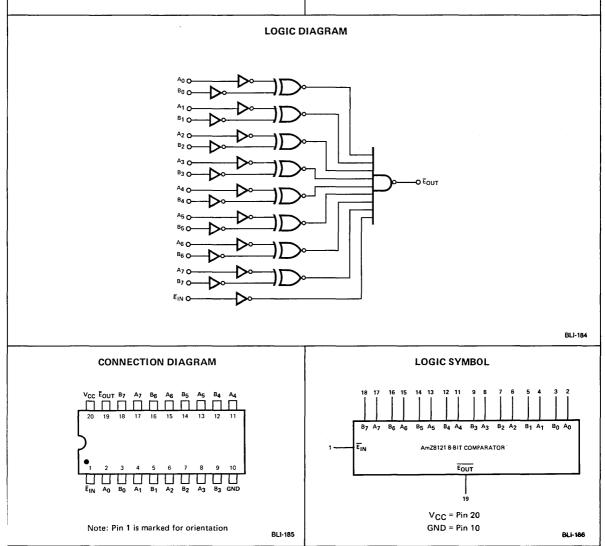

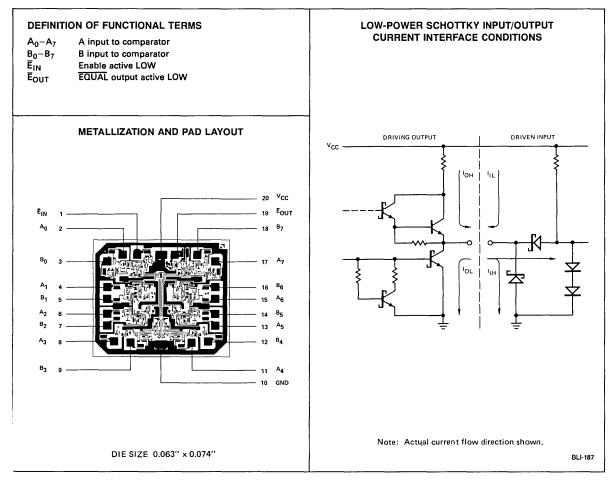

| AmZ8121                               | 8-Bit Comparator                                                                   |

| AmZ8127                               | System Clock Generator and Controller                                              |

| AmZ8133                               | Octal 3-State Latches                                                              |

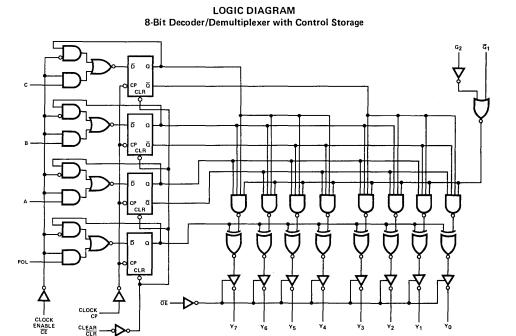

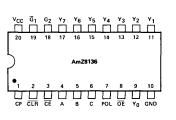

| AmZ8136                               | 8-Bit Decoder with Control Storage                                                 |

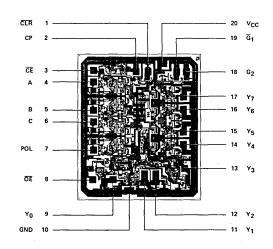

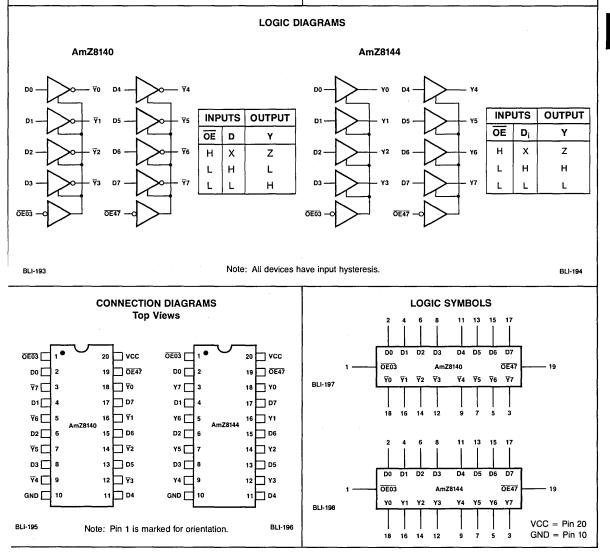

| AmZ8140/44                            | Octal 3-State Buffers                                                              |

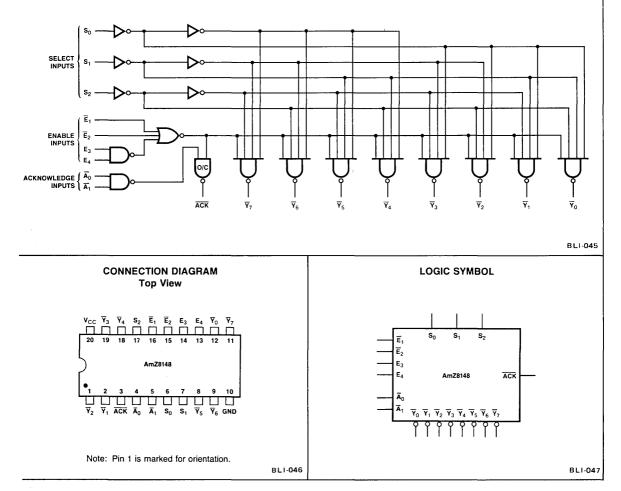

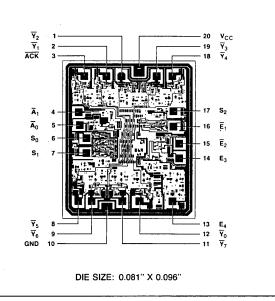

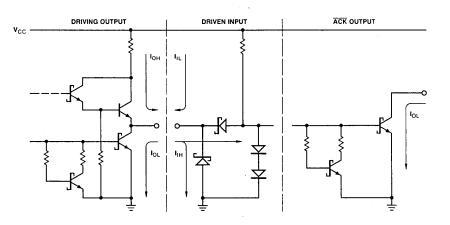

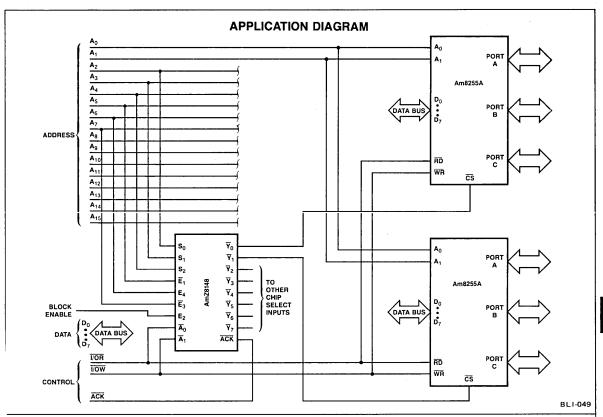

| AmZ8148                               | 3-to-8 Decoder with Acknowledge                                                    |

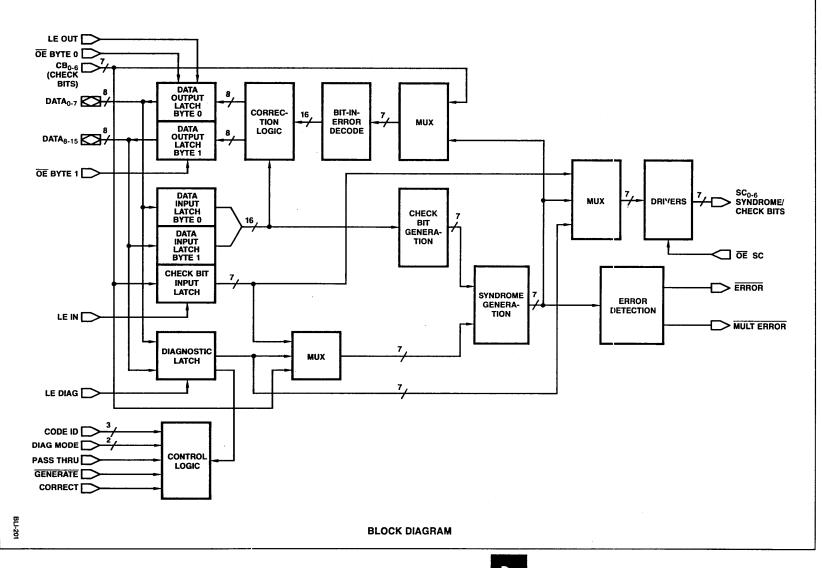

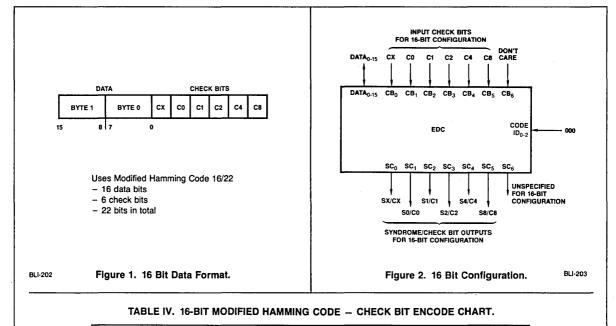

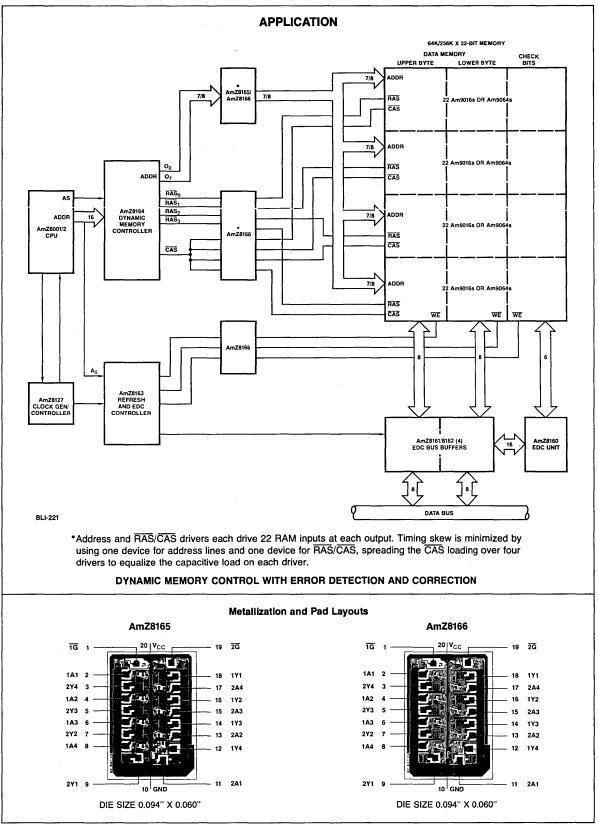

| AmZ8160                               | Error Detection and Correction Unit                                                |

| AmZ8161/62                            | Multiple Bus Buffers                                                               |

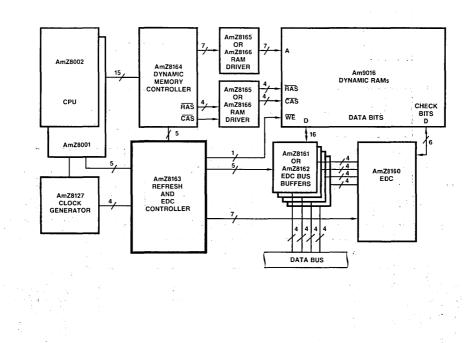

| AmZ8163                               | Timing, Refresh and EDC Controller                                                 |

| AmZ8164                               | Dynamic Memory Controller                                                          |

| AmZ8165/66                            | Octal Memory Driver                                                                |

| AmZ8173                               | Octal 3-State Latches                                                              |

| LSI System Com                        | iponents                                                                           |

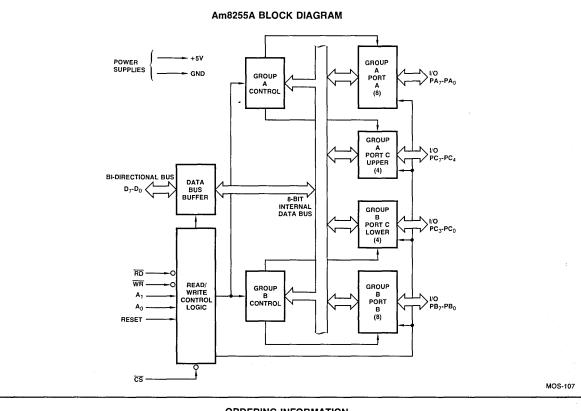

| Am8255A                               | Programmable Peripheral Interface                                                  |

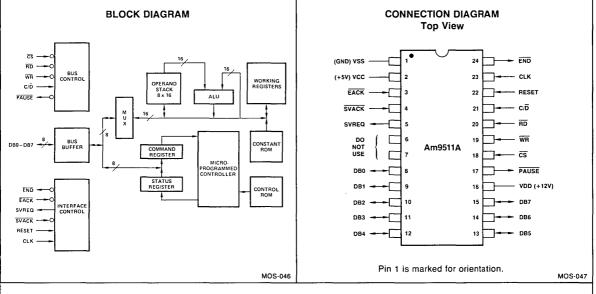

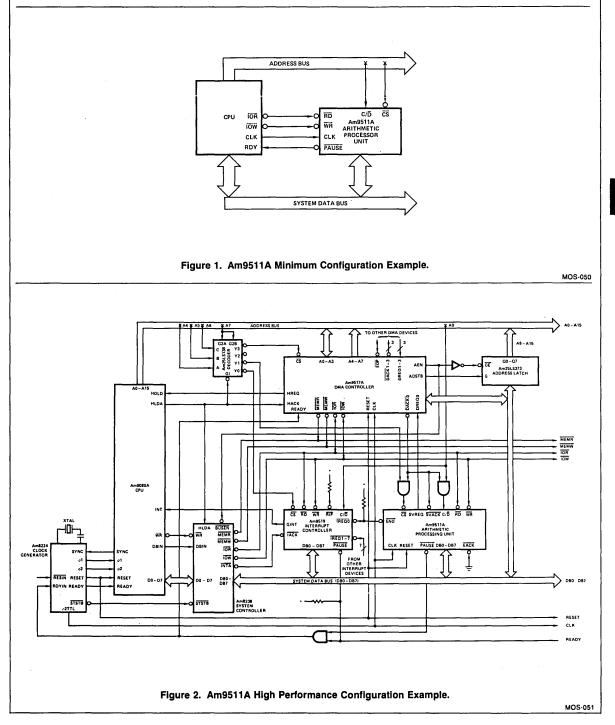

| Am9511A                               | Arithmetic Processor Unit                                                          |

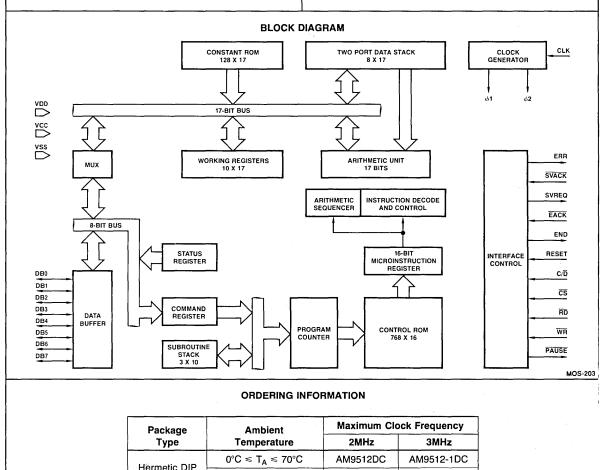

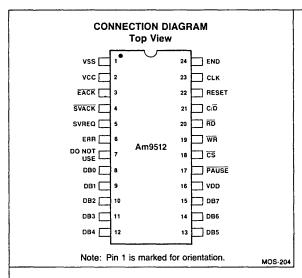

| Am9512                                | Floating-Point Processor                                                           |

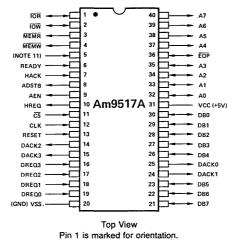

| Am9517A                               | Multimode DMA Controller                                                           |

| Am9519                                | Universal Interrupt Controller                                                     |

| Analog Interface                      |                                                                                    |

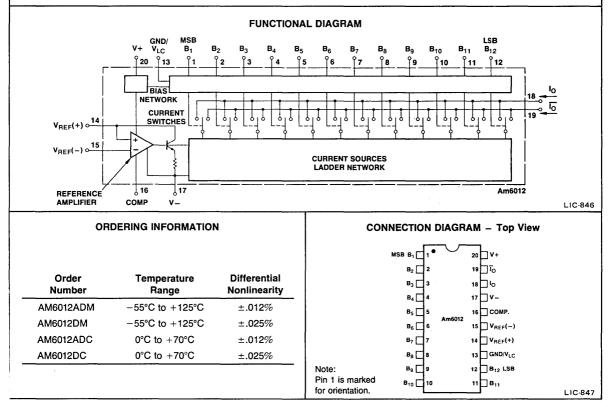

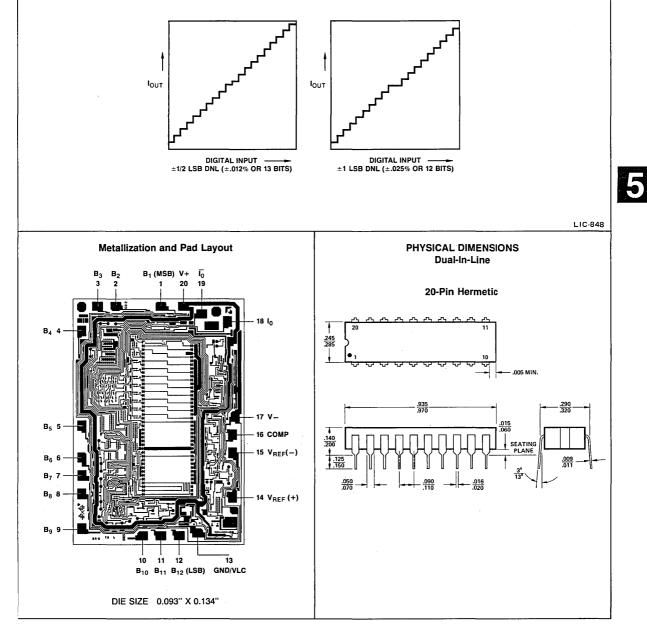

| Am6012                                | 12-Bit Multiplying D/A Converter                                                   |

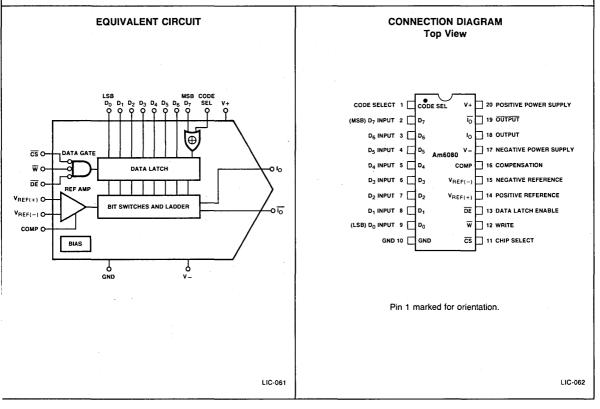

| Am6080                                | Microprocessor System Compatible 8-Bit High-Speed Multiplying D/A Converter 5-9    |

| Am6081                                | Microprocessor System Compatible 8-Bit High-Speed Multiplying D/A Converter . 5-11 |

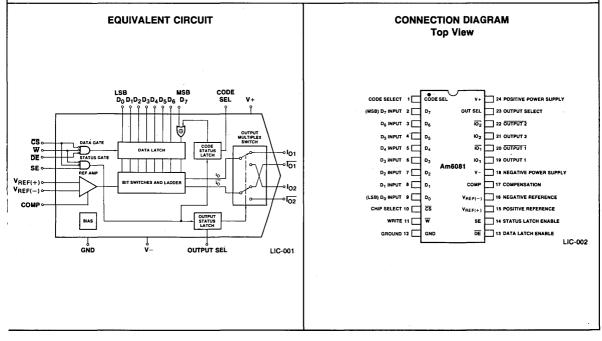

| Am6108                                | Microprocessor System Compatible A/D Converter                                     |

| Memory Compo                          |                                                                                    |

|                                       |                                                                                    |

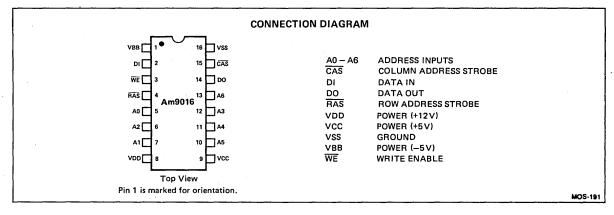

| Am9016                                | 16K x 1 Dynamic RAM                                                                |

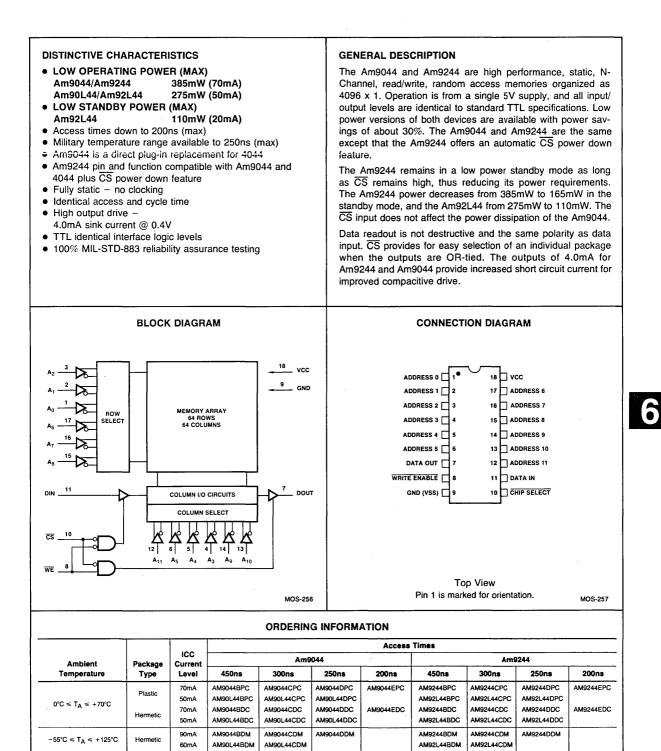

| Am9044/9244                           | 4K x 1 Static RAM                                                                  |

| Am9114/9124                           | 1K x 4 Static RAM                                                                  |

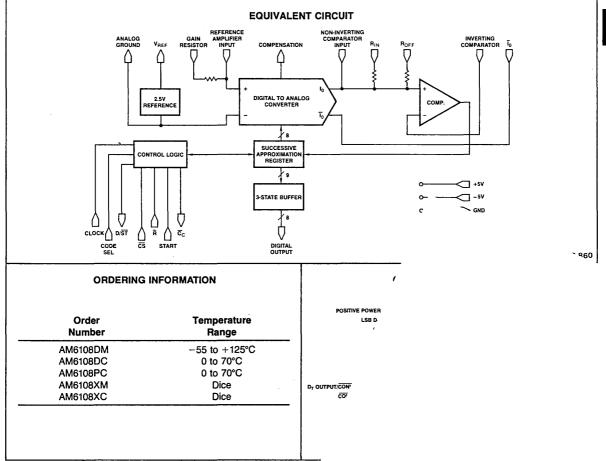

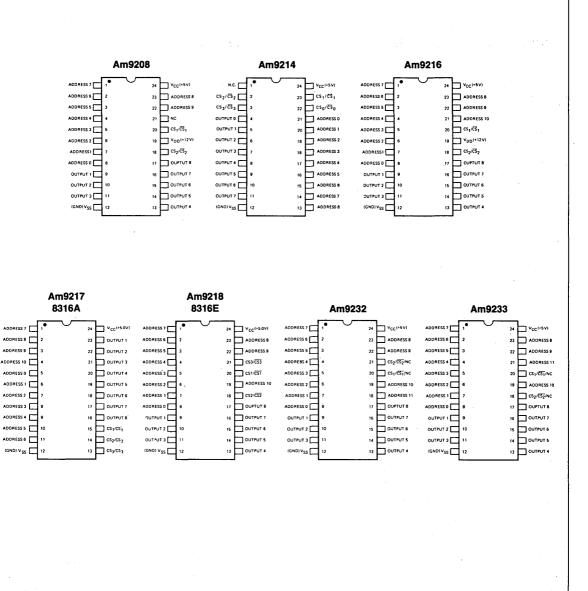

| Am2716<br>Am9218                      | 2K x 8 Erasable PROM                                                               |

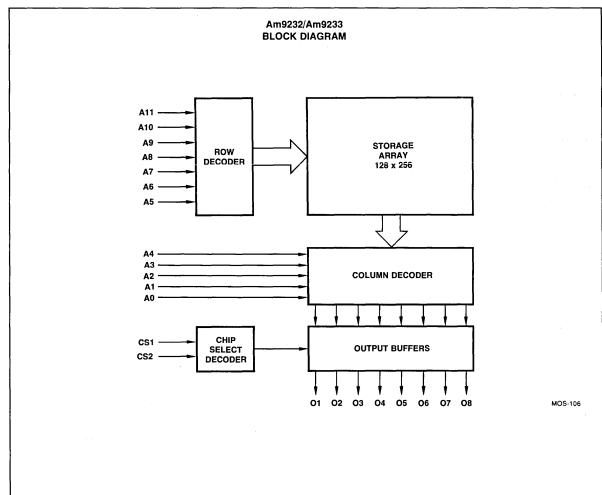

| Am9218<br>Am9232/33                   | 2K x 8 ROM                                                                         |

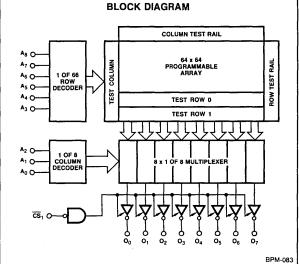

| Am27S28/29                            | 4K X 8 ROM                                                                         |

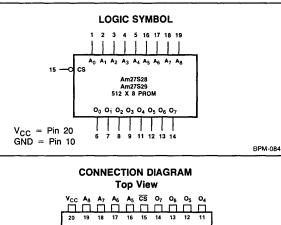

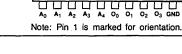

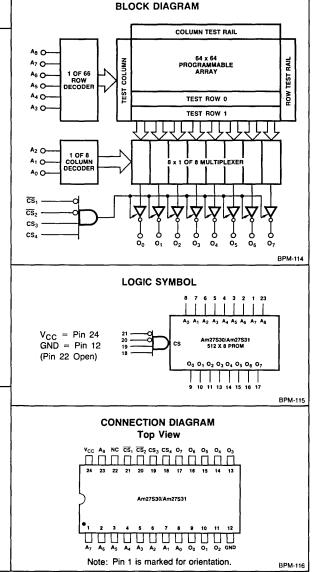

| Am27528/29<br>Am27530/31              | 512 x 8 PROM                                                                       |

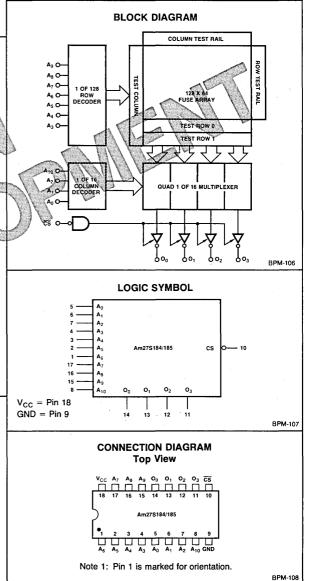

| Am27S180/181                          | 1K x 8 PROM                                                                        |

| Am27S184/185                          | 2K x 8 PROM                                                                        |

| , , , , , , , , , , , , , , , , , , , |                                                                                    |

### AmZ8000 Microprocessor Family

# CHAPTER 1

# ntroduction

Ā Am 28000 15 better THE 1897 A 1888

### INTRODUCTION

Advanced Micro Devices has undertaken a significant commitment to the world of 16-bit fixed-instruction-set processors. AMD is bringing to the market:

- A new, advanced processor architecture,

- A complete family of LSI peripheral circuits,

- A complete family of system support circuits,

- A complete family of memories and memory support circuits,

- Complete technical documentation,

- Effective development system products,

- Extensive support software.

This book describes all of these items in as much detail as is available at press time. Future editions will be propagated as new information is generated. Some of the data included here is preliminary and is intended to aid long-term planning. The factory should be contacted for the latest technical data on specific products and for the latest product availability information.

A large majority of future microprocessor applications will be serviced by a combination of single-chip microcomputer products such as the Am8048 series and by 16-bit microprocessors such as the AmZ8000. Where applications are simple enough, the 8-bit microcomputer chips will tend to be used. Increasing software costs and throughput requirements will cause the 16-bit CPUs to dominate the balance of the designs because they can answer these problems more efficiently. Conventional 8-bit microprocessors will serve a shrinking share of new designs.

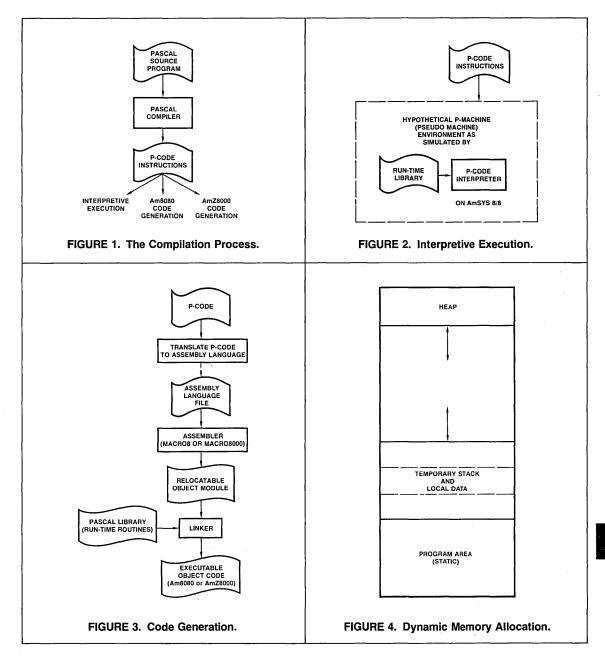

In addition to significant increases in throughput that flow directly from the 16-bit structures, improved technology and more sophisticated architectures add even more performance. Software cost savings are being realized due to more powerful instruction sets, and in conjunction with sophisticated high-level languages such as PASCAL. Language compilers allow the programmers to write, debug and document programs in a shorter time span. This is vitally important for such a labor-intensive activity where costs are rapidly rising. The declining costs of technology-intensive LSI hardware can be used to improve software costs.

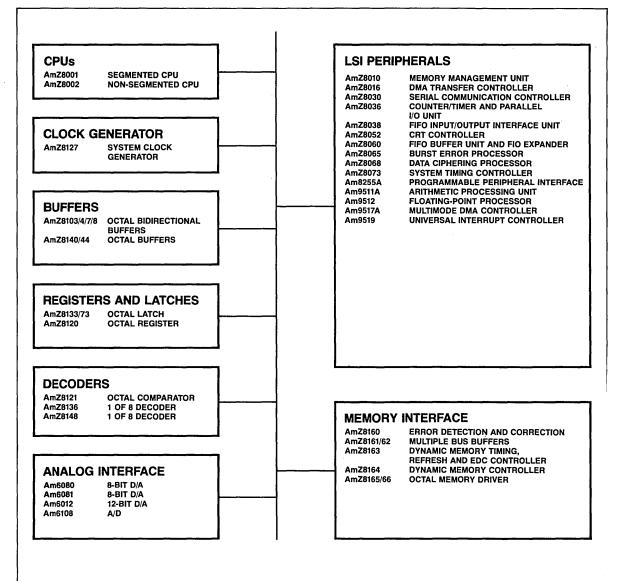

The AmZ8000 processors, in terms of resources, system features, instructions, interface and architecture, represents a major advance in microprocessor sophistication and system-level performance. The processors form the heart of a large family of components, systems, software, documentation and support. In addition to existing peripheral chips, a variety of new advanced peripherals has been designed to support the AmZ8001 and AmZ8002 processors. Figure 1 shows these new MOS/LSI components. Several types of products are available for buffering, driving, latching, decoding and control functions. These are useful within the system as well as for external interface and for implementing memory subsystems. Additional specialized components have been designed for control of specific memory subsystem functions such as refreshing and error correction.

A wide variety of memory devices are available to support the AmZ8000 Family. Advanced Micro Devices manufactures many types of RAMs, ROMs, PROMs, EPROMs and FIFOs. Memories, of course, are essential elements in any processor design. Indeed, processors can be considered as tools for converting logic gates and algorithms into memory cells, thus providing user access to the excellent levels of technology available via memories.

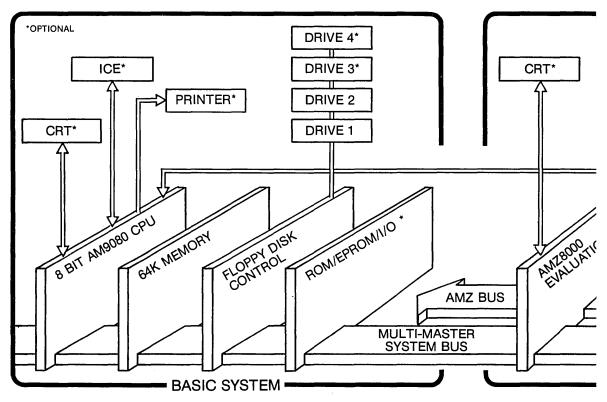

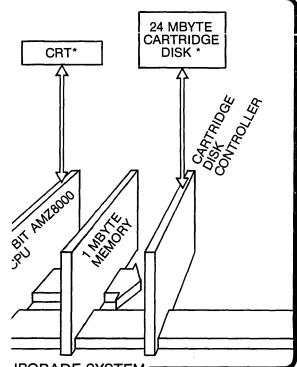

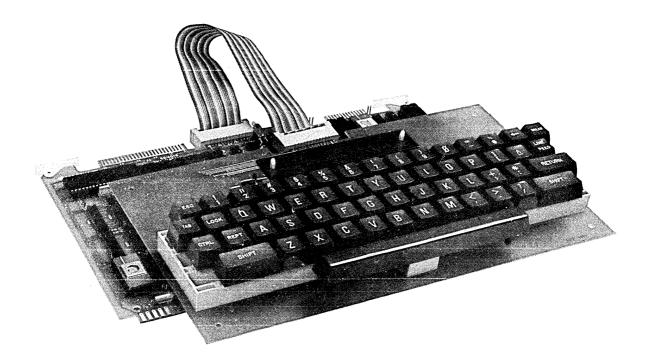

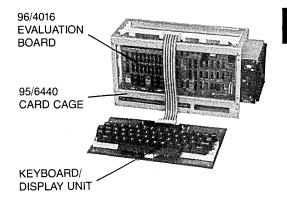

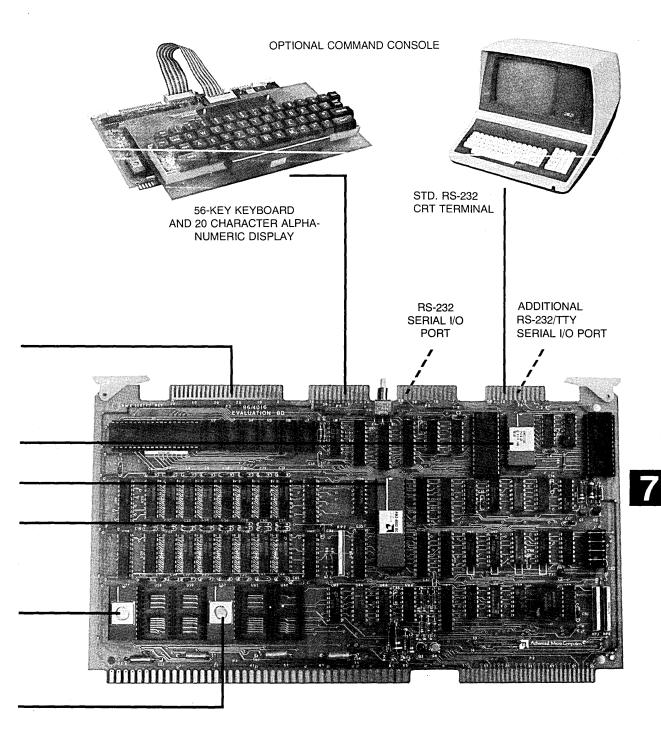

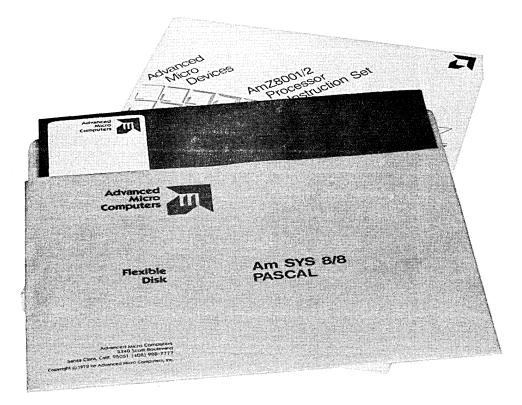

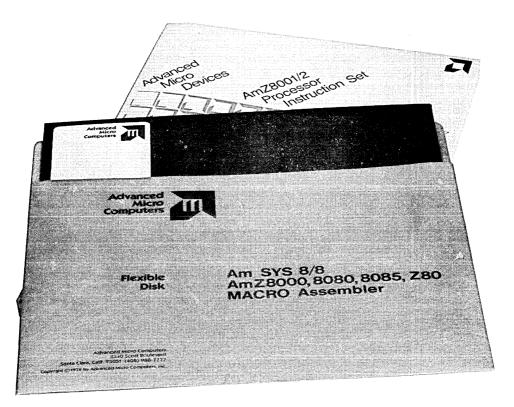

An AmZ8000 Evaluation Board is available from Advanced Micro Computers for quick hands-on experience with the AmZ8000. It is a complete small computer with RAM, ROM and several I/O ports. Available software includes a resident monitor and a simple line-by-line assembler. The AmSYS™8/8 Microcomputer Development System supports the AmZ8000 Family as well as other microprocessors such as the Am8080, Am8085 and Z80. The system includes RAM, dual 8 inch Floppy Disk drives and several serial and parallel interfaces.

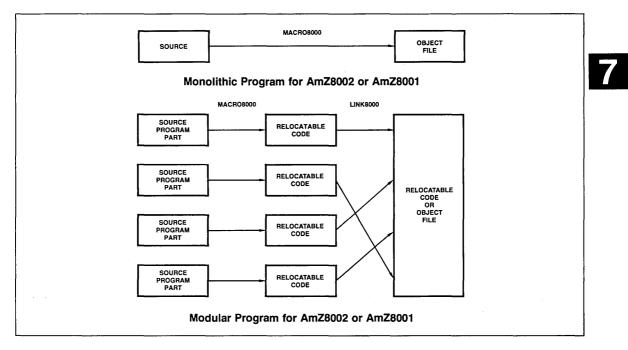

A powerful set of development software is available with the AmSYS /8 to make the complex process of product development easier and faster. The software includes a sophisticated Disk Operating System, Macro Assemblers, a linking loader, a powerful editor and debugger and a PASCAL compiler.

Advanced Micro Devices has an educational department which offers courses on the AmZ8000 microprocessor family, Am2900 bit-slice family and on related topics. Check with your AMD sales office for course outlines and schedules.

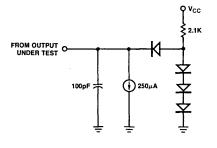

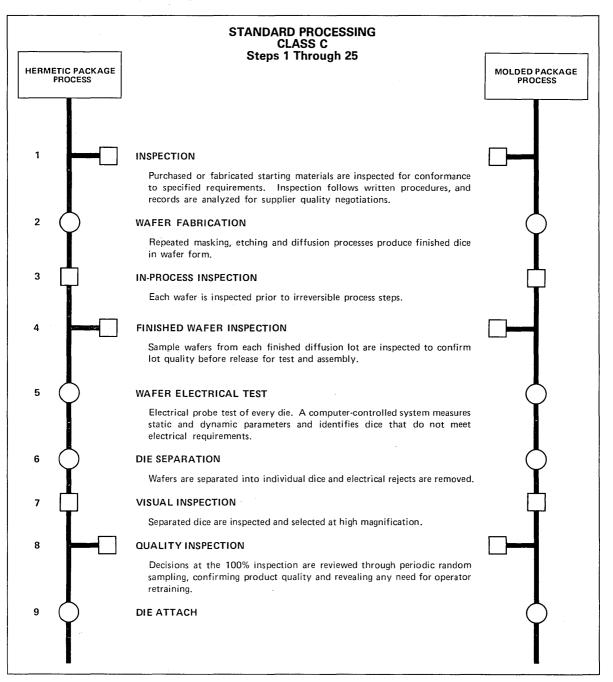

Advanced Micro Devices was conceived on the premise that there was a place in the semiconductor community for a manufacturer dedicated to excellence. This attitude is manifested in many ways throughout the structure of the company and has been maintained consistently throughout the life of AMD. In product assurance procedures, Advanced Micro Devices is unique. Only AMD processes all integrated circuits, commercial as well as military, to the demanding requirements of MIL-STD-883. The AmZ8000 microprocessors and its family of support devices are no exception; every component is 100% screened to MIL-STD-883, Method 5004, Class C.

### Introduction

### AmZ8000 Microprocessor Family

CHAPTER

## **Processor Architecture**

2

4\_0

1.0

1

*d*...

A. U

d.,

2

d.

### PROCESSOR ARCHITECTURAL OVERVIEW

### INTRODUCTION

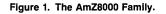

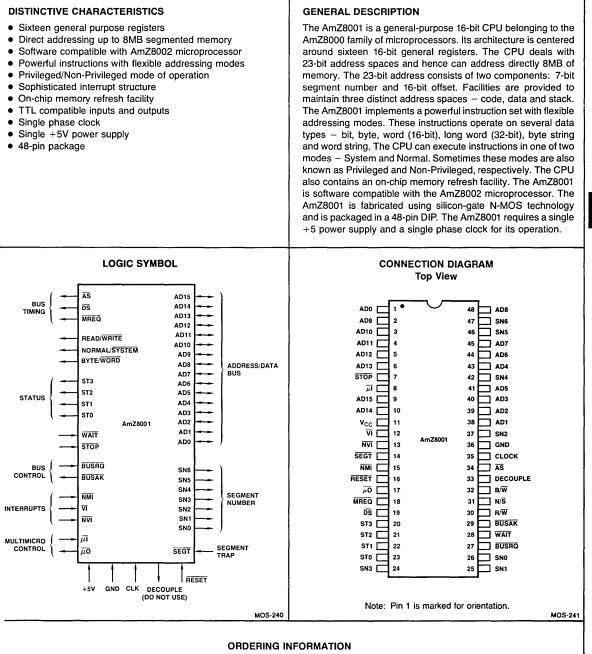

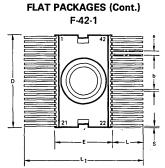

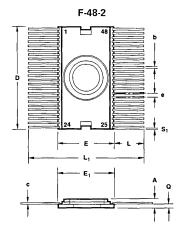

The AmZ8000 is an advanced high-end 16-bit microprocessor designed to span a wide variety of applications. Its features allow it to be used effectively in complex, high-throughput systems, yet it remains efficient for simpler systems as well. The AmZ8000 is available in two versions: the AmZ8001 48-pin segmented CPU and the AmZ8002 40-pin non-segmented CPU. The difference between the two devices is the addressing range: the AmZ8001 can directly address eight megabytes of memory per memory space and the AmZ8002 can directly address 65 kilobytes of memory per memory space. To meet the requirements of complex, memory intensive applications, the AmZ8010 Memory Management Unit offers logical-to-physical address translation and several memory protection features.

The AmZ8000 has abundant CPU resources that include numerous registers, many data element types, a large instruction set and several addressing modes. Not only are the CPU resources abundant, but they exhibit a consistency and regularity not found in previous microprocessor architectures. Regularity of register organization, data types, instructions and addressing modes greatly simplifies the programming process and reduces program length.

Compiler, compiler-produced, and operating system code all run efficiently on the AmZ8000. The AmZ8000 supports compilers with features such as a consistent instruction set, large address space, relocation, multiple stacks and some specific instructions (Push, Pop, Increment, Test).

Operating systems are supported by features such as system and normal modes, system and normal stacks, specific instructions (System Call, Load Program Status and privileged instructions), and by a sophisticated interrupt and trap structure. This structure includes three types of interrupts (non-maskable, nonvectored and vectored) and four types of traps (system calls, illegal instructions, privileged instructions and segment errors).

Multi-microprocessor systems are supported in software by exclusion and synchronization instructions and in hardware by the Micro In and Micro Out interface lines.

### **CPU RESOURCES**

Not only must the address space of an advanced architecture by large, but its CPU resources must be abundant enough for the solution of large problems.

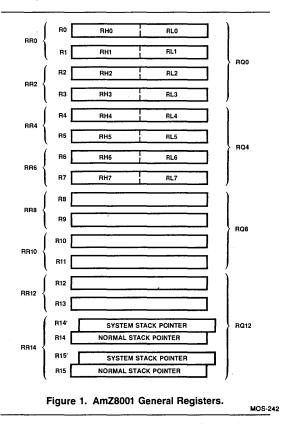

### Registers

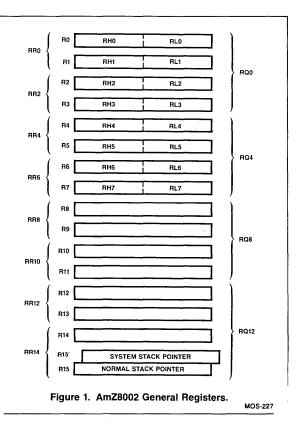

The AmZ8000 offers sixteen 16-bit general-purpose registers in addition to special system registers. All 16 general-purpose registers may be used as accumulators and all but R0 as index registers and stack pointers. The first eight registers (R0-R7) can be used as sixteen 8-bit byte registers. For operations requiring long words (32 bits), the general purpose registers are grouped in pairs (RR0-RR14). For certain 64-bit operands (i.e., multiplication and division with long words), the register set is grouped in quadruples (RQ0-RQ12) to form 64-bit registers.

The CPU instruction set supports seven main data types: bits, BCD digits, bytes, words (16 bits), long words (32 bits) byte strings and word strings. Additionally, many other data elements such as memory addresses, I/O addresses, segment table entries and program status words may also be manipulated.

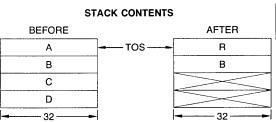

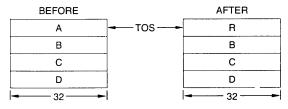

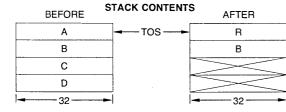

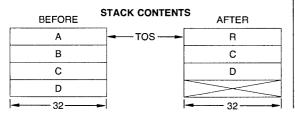

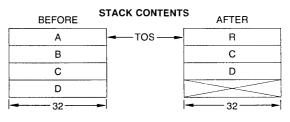

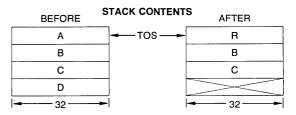

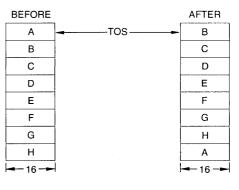

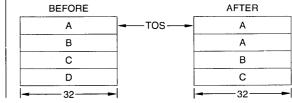

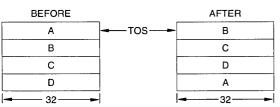

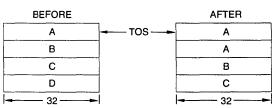

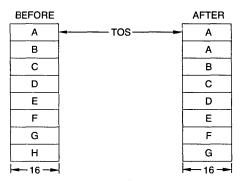

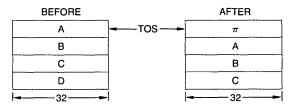

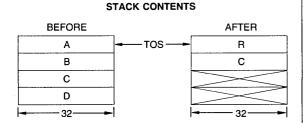

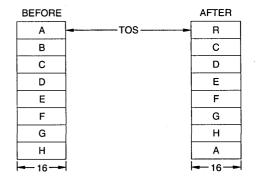

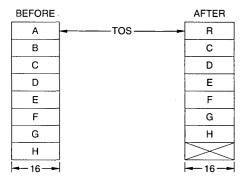

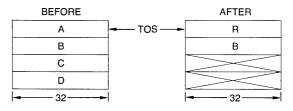

#### Stacks

The AmZ8000 allows data stacks to be located anywhere in memory. Push and Pop instructions allow any register (except RR0 (AmZ8001) and R0 (AmZ8002)) to be designated as data stack pointers. Call and Return instructions, as well as interrupts and traps use the (implied) linkage stack pointers. For the AmZ8001, the register pair RR14 (R14 and R15) is the linkage stack pointer, while for the AmZ8002 register R15 is the linkage stack pointer.

The CPUs operate in one of two selectable modes: System and Normal. The System mode is sometimes called a Supervisor or Privileged mode and the Normal mode is sometimes known as User or Task or Nonprivileged mode. Separation from system information is provided by a dual set of linkage stack pointers. In the AmZ8001, the register pair R14' and R15' will be used in the System mode as the implied stack pointer, while the AmZ8002 will use the R15' register. Because the implied stack pointers are part of the general-purpose register group, the user can manipulate the stack pointers with any of the instructions available for register operation.

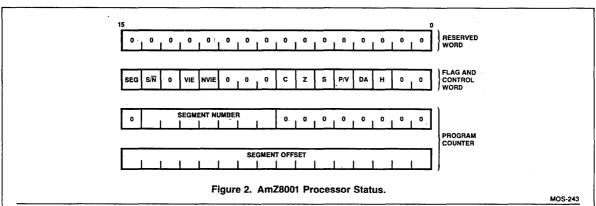

### **Program Status Information**

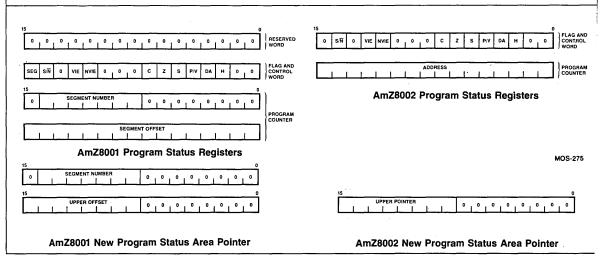

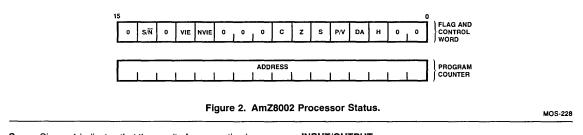

This group of status registers contains the program counter (PC), the flag and control word (FCW) and the new program status area

pointer (NPSAP). When an interrupt or trap occurs, the Program Status registers (PC and FCW) are saved on the system stack. An Identifier that describes the reason for interruption is also saved. The NPSAP provides the memory location for loading new information into the PC and FCW registers.

The CPU Control bits occupy the upper byte of the Flag and Control Word. The bits may be read and loaded by the privileged LDCTL instruction. The Control bits are:

- SEG Segmented Mode Enable

- S/N System or Normal Mode

- VIE Vectored Interrupt Enable

- NVIE Non-Vectored Interrupt Enable

The SEG bit indicates segmented operation in the AmZ8001 if set to 1. When the SEG bit is 0, the AmZ8001 is forced into non-segmented operation and will interpret all programs as non-segmented. In this mode, the AmZ8001 executes AmZ8002 nonsegmented code. The AmZ8002 SEG bit is always set to 0 and cannot be altered by the programmer.

The CPU Flags occupy the lower byte of the Flag and Control Word. The privileged instructions LDCTLB, RESFLG and SETFLG are used to load, read, set and clear the flags. The Flag bits are:

- C Carry Result

- Z Zero Result

- S Sign Result

- P/V Even Parity or Overflow

- DA Decimal Adjust

- H Half Carry

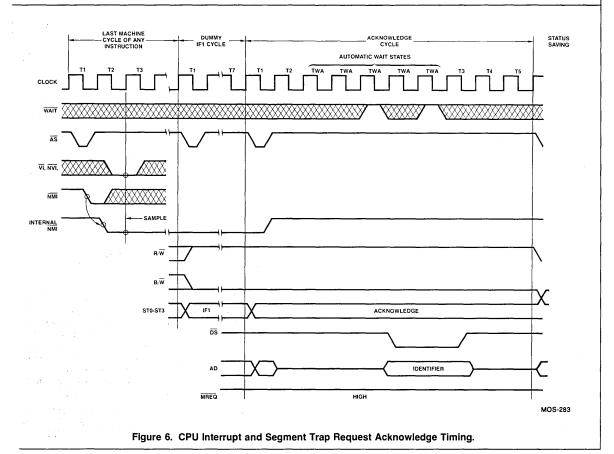

### Interrupt and Trap Structure

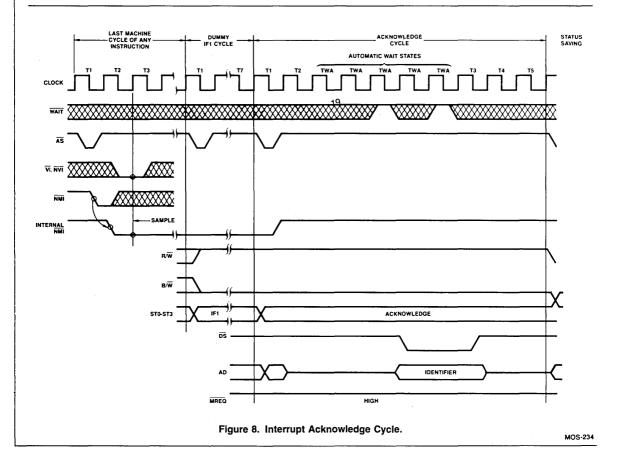

The AmZ8000 provides a flexible and powerful interrupt and trap structure. Interrupts are asynchronous events triggered by an external device requesting service, while traps are synchronous events occurring upon the execution of certain instructions. The AmZ8000 supports three types of interrupts (non-maskable, vectored and non-vectored) and four traps (system call, unimplemented instruction, privileged instructions and segmentation trap). The vectored and non-vectored interrupts are maskable. When an interrupt or trap occurs, a 16-bit identifier (in addition to the PC and FCW registers) is pushed onto the system stack.

The identifier contains the reason for the trap or interrupt. For internal traps, the identifier is the first word of the trapped instruction. For external traps or interrupts, the identifier is placed on the data bus by the interrupting or trapping peripheral.

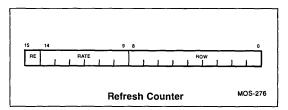

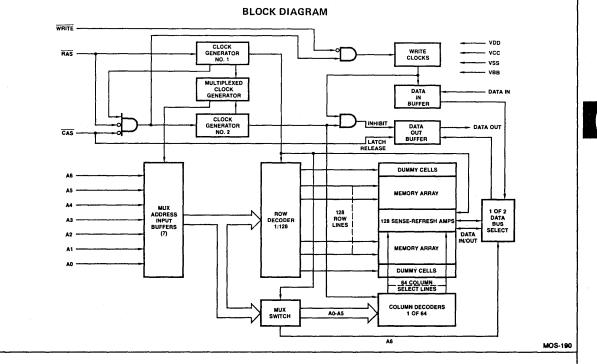

#### **Memory Refresh**

The AmZ8000 CPUs contain a refresh counter for automatically refreshing dynamic memory. A 9-bit row counter can address up to 256 rows and thereby assures compatibility with the latest 64K dynamic memories. It is incremented by two each time the rate counter reaches end-of-count. The rate counter determines the time between successive refreshes and can be programmed from 1 to 64 $\mu$ sec assuming a 4MHz CPU clock. The refresh mechanism can be disabled under software control.

#### Large Addressing Space

High-level languages, sophisticated operating systems, large data bases, large programs and decreasing memory prices are all accelerating the trend toward larger memories. The AmZ8000 processors can directly address up to eight megabytes of memory per address space. Four convenient, separate address spaces exist in both versions of the AmZ8000 processors: code and data for both the system mode and the normal mode.

Each space is addressed by a 16-bit or 23-bit address. Thus the total system addressing for a user is 32M bytes for the AmZ8001 and 256K bytes for the AmZ8002. Instructions are always addressed on word boundaries (even-numbered addresses) while data is addressed by byte, word, long word, or quadruple word addresses. A specific bit can also be addressed within a byte or word address.

The AmZ8000 also has a 16-bit I/O addressing space which is separate from the memory address space. An attractive complement of single element I/O and block I/O instructions exist for bytes and words.

Additionally, many useful memory management features, are provided by the AmZ8010 Memory Management Unit when used as a companion to the AmZ8001. These features will extend the life of the architecture by avoiding memory address limitations that have hampered microprocessors in the past.

The only drawback of the long addresses required by the large addressing space is the larger size of the instructions and the need for register pairs for some addressing modes. This problem is minimized by segmented addressing features, the use of short addresses in many situations, relative addressing ability and by the availability of a large number of general-purpose registers.

#### Memory Management

AmZ8001 programs can directly access the entire address space. A full address mode is available where 23 bits are set aside within the instruction for the address. The AmZ8001 also offers a mode called short offset mode in which the same address can be expressed by 16 bits in many situations where the higherorder offset bits are zeros.

Alternative methods commonly employ fixed internal registers that contain address extensions. Although these methods may use shorter instruction addresses, the byte savings are lost because many instructions are required to explicitly manage the contents of the registers. The AmZ8001 can use variations of these methods; however, it also provides direct addressing that removes the necessity for those extra instructions and unburdens the programmer from managing the register contents.

Another important feature provided to the system designer is the ability to distinguish externally between System code and Normal code, and in both cases, to distinguish between instruction space and data space. If this feature is utilized, the AmZ8001 can address up to 32 megabytes of memory. Aided by system programs, the memory management unit can help manage the large address space on behalf of the user.

Segmentation is the mechanism provided to address the large amount of memory addressable by the AmZ8001. A segmented address is made of two parts: a segment number and an offset value. The AmZ6001 can designate up to 128 cogments that reference areas of memory variable in size from 256 bytes to 64 kilobytes, in increments of 256 bytes.

The only difference between running segmented or non-segmented code is the number of bytes per address and the number of registers used for full addresses. Code written for the nonsegmented AmZ8002 can run in one segment of the segmented AmZ8001. Thus, full compatibility exists between the two versions.

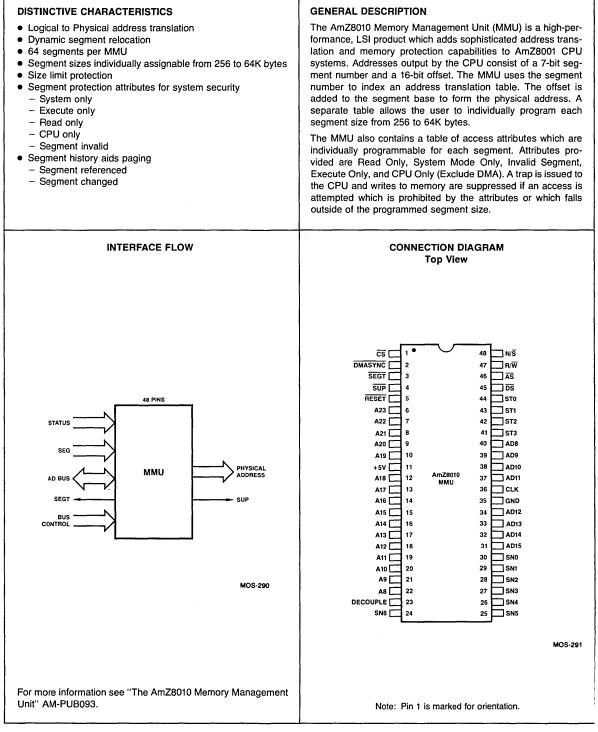

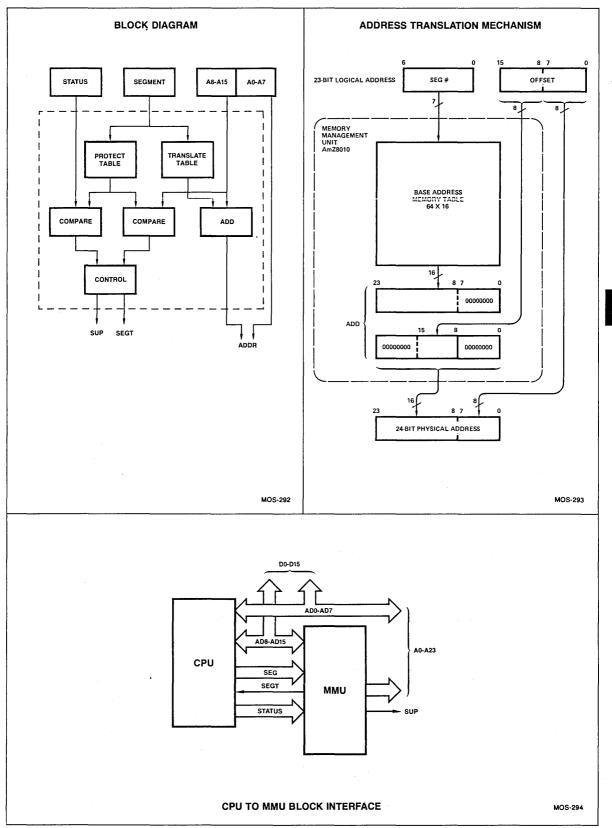

The AmZ8010 Memory Management Unit essentially doubles the silicon area available for the processor function (and adds pins as well). Hence, it also doubles the hardware available to the designer for implementing more high-end features than otherwise would have been possible. Some of these features include variable sized segments, more sophisticated dynamic memory relocation and several types of memory protection attributes.

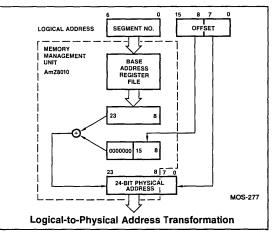

Addresses manipulated by the programmer are called logical addresses. The MMU translates these logical addresses to physical addresses required for accessing the memory. This address transformation makes user software addresses independent of the actual physical memory thus freeing the user from specifying where information is actually located in memory. The translation table in the Memory Management Unit associates the 7-bit segment number with the base address of the physical memory segment. The 16-bit offset portion of the logical address from the CPU is added to the physical base address to obtain the actual physical address. The system may dynamically reload translation tables as tasks are created, suspended, or changed. Memory protection features prevent illegal uses of segment, such as writing into a write-protected zone. Several Memory Management Units may be used with a single CPU.

### Instructions

Compared to other microprocessors or to 16-bit minicomputers, the number and power of individual instructions has been greatly increased. Over 110 distinct instruction types are available with the AmZ8000. Byte, word and long-word data elements can be processed by all the core instructions. Each instruction, with few exceptions, can use most of the addressing modes. Over 410 meaningful combinations of instruction types, data elements and addressing modes are available.

The instruction set provides nine basic instruction groups: Load and Exchange, Arithmetic, Logical, Program Control, Bit Manipulation, Shift and Rotate, String Manipulation, CPU Control, and Input/Output. Instructions vary in length from one to five words depending on the operation and addressing mode. String and block move instructions are interruptable to enhance response time. Also provided are signed-multiply and signed-divide instructions implemented in hardware for both 16-bit and 32-bit values.

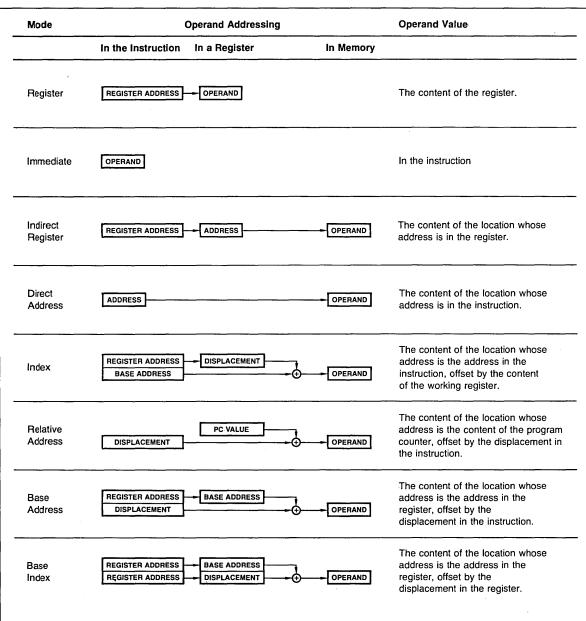

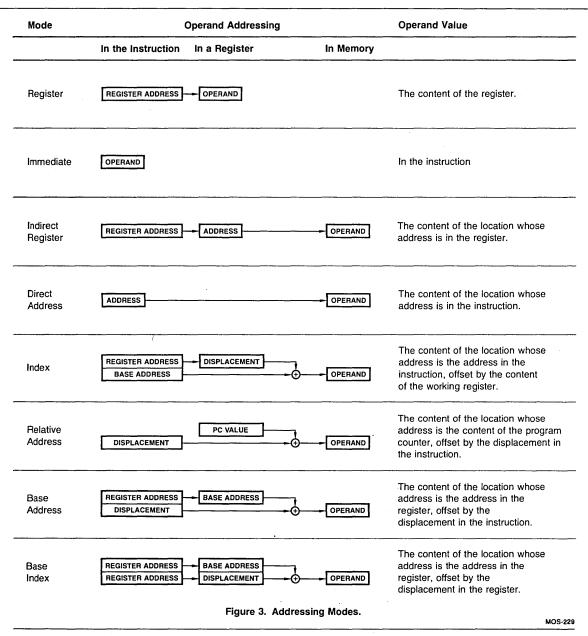

The instruction set provides several user-selectable addressing modes including five main modes: Register (R), Indirect Register (IR), Direct Address (DA), Indexed (X) and Immediate (IM). For certain instructions, there are other modes: Base Address (BA), Base indexed (BX), Relative Address (RA), Autoincrement and Autodecrement.

### **Code Density**

For a given hardware technology, microprocessor speed is largely dependent on the number of executed instruction words needed for a particular function. Therefore, code density becomes an important issue in high-performance systems. The AmZ8000 offers several advantages in this respect.

The number of words required to specify frequently executed instructions has been minimized. A special group of high frequency instructions has been designed into single words. This not only improves speed, but increases code density as well.

A short offset mechanism is also designed to allow certain 23-bit addresses to be reduced to a single word. It can be automatically invoked by assemblers and compilers.

Additional large improvements in program size and speed result from the consistent and regular architecture, and the greater power of the instruction set. These factors allow fewer instructions to accomplish a given task.

### **Compiler Efficiency**

It is tempting to adapt a computer architecture that efficiently executes a particular high-level language. Any special-purpose match between an architecture and a language is efficient for that language, but most likely inefficient for unrelated languages. Since the AmZ8000 is a general-purpose microprocessor, general language support has been provided through the inclusion of features that ease typical compilation and code-generation problems for all high-level languages.

Among these features is the regularity of the AmZ8000 addressing modes, registers and data element types. In addition, any

register can be used as a data stack pointer with the Push and Pop instructions. Segmentation and relocation are useful features for high-level language procedure implementation. Procedure parameter passing is aided by these features as well as by special increment and decrement instructions which are useful in stack frame allocation and de-allocation. Base Address and Base Indexed addressing modes are also useful for stack frames. Useful testing and comparison of data, logical evaluation and initialization are made very efficient by several special instruction types. Compilers and assemblers handle character blocks quite frequently and the string manipulation instructions provide unusual efficiency compared to software simulations of these important tasks.

### **Operating System Support**

Interrupt and task-switching features are included to improve operating system implementations. The memory-management and compiler-support features also contribute effectiveness in this environment.

The interrupt structure has three levels: non-maskable, nonvectored and vectored. When an interrupt occurs, the program status is saved on the stack with an indication of the reason for this state switching. A new program status is then loaded from memory and execution proceeds using the new Program Counter. In the case of a vectored interrupt, each vector points to a unique new Program Counter, providing direct access to particular service routines.

The System/Normal partition improves operating system integrity and organization. In the System mode, all operations are allowed; in the Normal mode, certain system instructions are prohibited. The System Call instruction allows a controlled switch of mode, and the implementation of traps enforces these restrictions. Dual linkage stack pointers also support the System/Normal partition.

Traps result in the same type of program status saving as interrupts; in both cases, the information saved is pushed on the system linkage stack and keeps the normal stack undisturbed. The Load Multiple instruction allows the contents of any group of the general registers to be saved and restored efficiently in memory. Running system programs can cause selective or general program status changes under direct software control. Finally, exclusion and serialization can be achieved with the "atomic" Test and Set instruction that synchronizes cooperating processes.

### Multiprocessor Support

The AmZ8000 exclusion/serialization mechanism is designed for multimicroprocessor systems. Any CPU in a multiprocessor system can exclude all other asynchronous CPUs from any critical shared resource by using the Micro In ( $\mu$ I) input and Micro Out ( $\mu$ O) output in conjunction with several coordinating instructions.

In addition, the large address space of the AmZ8000 proves to be a beneficial feature in most multiprocessor systems.

### AmZ8000 **Microprocessor =**amily

<u>a</u>

4.0

A

a c

3

, A

Ă

£.,8 á.

cuits

A wide variety

peripheral ci basy to use u

### CHAPTER 3

### **System Architecture**

### SYSTEM ARCHITECTURE OVERVIEW

### INTRODUCTION

The AmZ8000 CPU and peripheral device family support a variety of interface exchanges. The AmZ8000 processors are designed to handle five basic types of transfers: memory operations, I/O operations, resource request daisy chain, bus request daisy chain and interrupt request daisy chain. These interface exchanges share most of a common set of control signals. Most of the AmZ8000 peripherals use a similar control structure and some subset of the five basic transfer types. Some of the features of the system structure are:

- Juxtaposition and coordination of five different buses.

- Transparent bus for asynchronous peripheral operations.

- Multiplexed I/O and memory operations.

- Multiplexed Address and Data transfers.

- Full parallel 23-bit addresses.

- Preemptive interrupt daisy chains.

- Interrupt protocol allows vectors for peripheral identification.

- Resource allocation uses exclude/grant daisy chain.

- Bus requests use daisy chain for contention resolution.

#### **Memory Operations**

The AmZ8000 CPU offers a powerful combination of memory access techniques to a word organized memory. The CPU distinguishes between instructions, data and stack entries in both System and Normal modes and outputs a combination of status and bus timing signals. The status lines consist of four outputs which indicate the type of bus access; a Normal/System line to aid in selecting system or user memory space; a Byte/Word output line to allow addressing of an individual byte or a 16-bit word; and the Read/Write output indicating the direction of data flow.

Both versions of the AmZ8000 exhibit the identical set of status lines thereby allowing convenient access to separate 64K byte address spaces: system code, normal code, system data, normal data. The AmZ8001, through its additional seven segment number outputs allows extension of its address spaces to 8M bytes each. The AmZ8010 Memory Management Unit can further enhance memory space usage and allocation in the AmZ8001. The MMU offers the capability of generating a 24-bit physical address from the 23-bit logical address any 8M bytes within a 16M byte physical memory. Furthermore, memory address seg-

| Status | Line | Codes |

|--------|------|-------|

|--------|------|-------|

| ST3-ST0 | Definition                         |

|---------|------------------------------------|

| 0000    | Internal operation                 |

| 0001    | Memory refresh                     |

| 0010    | I/O reference                      |

| 0011    | Special I/O reference              |

| 0100    | Segment trap acknowledge           |

| 0101    | Non-maskable interrupt acknowledge |

| 0110    | Non-vectored interrupt acknowledge |

| 0111    | Vectored interrupt acknowledge     |

| 1000    | Data memory request                |

| 1001    | Stack memory request               |

| 1100    | Program reference, nth word        |

| 1101    | Instruction fetch, first word      |

ments can be of any size that is a multiple of 256 bytes and may overlap. Each Memory Management Unit may translate up to 64 address segments. If more segments are required, several Memory Management Units may simply be paralleled.

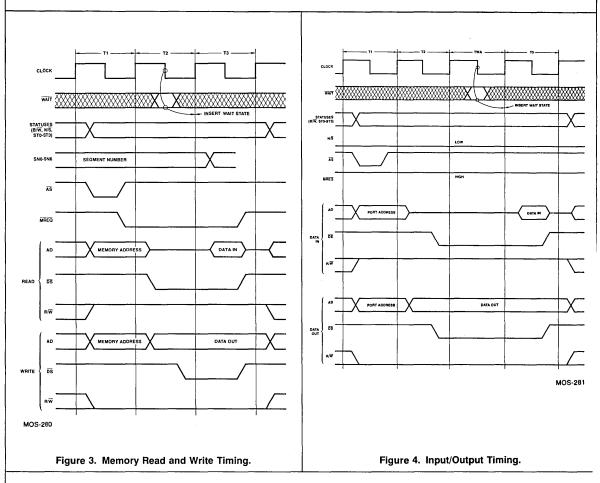

The AmZ8000 bus timing signals consisting of three signals: MREQ whose level indicates a memory or I/O type transfer; AS which is an address strobe (an address is indicated valid by its rising edge); and DS which is the data strobe (data read or written is also indicated valid by the rising edge of DS). A typical memory fetch cycle occurs within three CPU clock cycles thereby allowing the usage of moderate access time memories for price/performance enhancement. A WAIT bus control input is also available on the CPU thus allowing even slower memory operation.

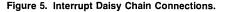

### I/O Operations

I/O operations between the AmZ8000 CPU and its peripherals are transacted on the same multiplexed address/data bus lines and are distinguished only by status outputs. (MREQ HIGH specifies an I/O operation while status lines ST0-ST3 specify either a standard I/O address space or a special I/O address space: for example, an AmZ8010 MMU.) The I/O address space can, therefore, be two separate 16-bit address spaces, in addition to the memory space, if the status lines are decoded in conjunction with MREQ signal. The large I/O address space allows great

versatility for accessing intensive register oriented peripherals: AmZ8000 peripherals typically follow the philosophy of allowing read and write operations to all their internal registers.

I/O mapped 8-bit peripherals can be located on either the upper or lower half of the address/data bus for data transfers; the AmZ8000 CPU duplicates a data byte on both halves of the bus when executing a byte write I/O operation.

A byte read I/O operation follows the same principle as byte read memory operations: Odd addresses refer to the low-order byte (AD0-AD7 bus) and even addresses to the high-order byte (AD8-AD15 bus).

Eight and 16-bit wide peripherals can be intermixed on the same bus, as the AmZ8000 provides both byte and word I/O oriented instructions, as well as Block I/O instructions for rapid data transfers (i.e., I/O peripheral register initialization).

AmZ8000 peripherals are not required to be synchronous with the CPU, because no clock is transmitted. AS and DS strobe signals provide the timing. In addition, the CPU inserts an automatic wait state whenever an I/O operation is performed. Additional wait states can be inserted by a slow peripheral by activating the AmZ8000 CPU wait status input.

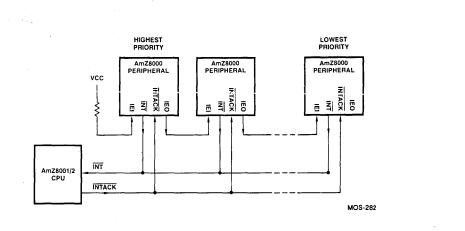

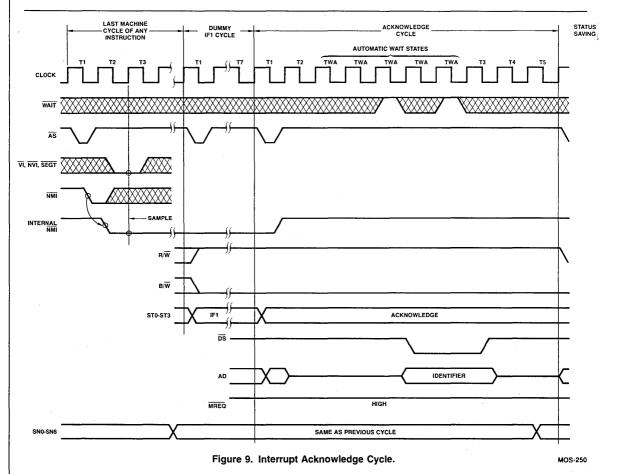

#### Interrupt Daisy Chain Protocol

An interrupt daisy chain protocol enables peripherals to act as slaves to the CPU. In contrast to I/O transactions which occur on the data bus in an orderly fashion; each peripheral, with interrupt capability, may attempt to use it simultaneously with another interrupting device. A daisy chain link between peripherals implements a distributed arbitration policy between interrupt requests to achieve an orderly, prioritized sharing of the CPU's resources.

The majority of the AmZ8000 family peripherals have the ability to request interrupts due to several internal reasons (for example, the AmZ8036 CIO can have three reasons to interrupt and the AmZ8030 SCC, eight). The peripheral itself contains an internal

interrupt structure for prioritizing its internal interrupt request sources; for requesting service according to its priority status among other peripherals sharing the system bus; for outputting a proper vector identification, with or without additional status bits, when acknowledged by the CPU. The 8-bit vector allows efficient program transfers to the appropriate service routine without additional polling of the peripheral by the CPU. The peripheral selfvectoring and daisy chain prioritizing precludes the requirement for an additional interrupt controller device in the system.

The AmZ8000 CPU recognizes three interrupt inputs (non-maskable, vectored, and non-vectored), and a segmentation trap input (normally intended to be generated by an AmZ8010 MMU). Interrupt inputs are asynchronous, and the interrupt acknowledge is decodable from the ST0-ST3 status lines for each interrupt type. An explicit completion code must be emitted by the CPU to terminate some peripheral's interrupt service. An appropriate I/O instruction easily accomplishes it. To ensure data integrity and proper settling of IEO signals in the daisy chain link, the AmZ8000 CPU automatically inserts five wait states following interrupt acknowledge and before asynchronously strobing in the peripheral's identification vector ("Identifier"). The peripheral may activate the CPU's WAIT line and cause additional wait cycles, if required.

3-3

#### Peripheral Internal Interrupt Protocol

In general, AmZ8000 family peripherals have three bits for control and status of the internal interrupt logic: an Interrupt Pending bit, an Interrupt Under Service bit and an Interrupt Enable bit. For a multisourced internal interrupt structure, the three above bits are duplicated for each interrupt source, and the interrupt sources are internally prioritized. Lower priority peripherals in the daisy chain link are disabled by the status of another internal list: Disable Lower Chain bit. The peripheral will output a vector for interrupt source identification, when acknowledged by the CPU, according to the status of its No Vector bit. The 8-bit vector (usually defined by an internally programmed register) may include status information as specified by the Vector Include Status bit.

#### **Resource Request Chain Protocol**

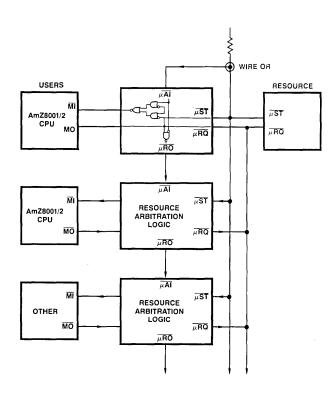

Multimicroprocessor systems are well supported in hardware and software. Resources, like buses with their associated peripherals or common memories, are easily shared in an orderly and expedient fashion by several CPUs in a system. In general, the resource user need not be a CPU (i.e., it could be an I/O Channel Processor, an Arithmetic Processor, etc.) as long as it can implement a meaningful resource sharing protocol. This is in contrast to a bus request chain (i.e., DMA operations) in which system exists a default master and a defined bus with a tailored protocol. The AmZ8000 CPU supports resource protocol with two hardware pins: the MultiMicro Out ( $\mu$ O) to issue requests for the resource. Four special instructions allow the CPU to test and request a resource, and to exclude or allow other users to the resource. These functions are particularly interesting with the

eight megabyte AmZ8001 CPU address space capability for multiple microprocessor systems with large shared memory requirements.

A resource request protocol is easily implemented in hardware through simple SSI logic where each resource user is connected to the resource-sharing system by four unidirectional lines.

Unlike an interrupt or bus request chain no user is a default master and no user can therefore be preempted. The resource request protocol uses the request algorithm described below:

- A user process checks the status of the μST (resource status) line to see if the resource is busy. (The AmZ8000 CPU would look at its μl input pin via the privileged MBIT instruction.)

- If the µST line is active, then another user is either using the resource or is in the process of requesting it. In both cases, the resource request is terminated with the indication of a busy resource via internal flag. This implements the policy of no preemption.

- 3. If the  $\mu$ ST line is not active, then the user:

- a. Activates its  $\mu$ RQ line ( $\mu$ O output on the AmZ8000) and,

- b. Waits for a finite delay (the AmZ8000 CPU MREQ instruction computes the delay by decrementing a 16-bit register). The delay is required in the case of several users requesting access to a particular resource. In this case, the daisy chain link lines ( $\mu$ AI,  $\mu$ AO) in the resource arbitration logic resolves the conflict by granting the resource to the highest priority requestor.

- c. Tests the μAI if active, then the resource is granted (the AmZ8000 again sets an internal flag); otherwise, the request is terminated.

Figure 7. Multimicro Resource Daisy Sharing Chain Link.

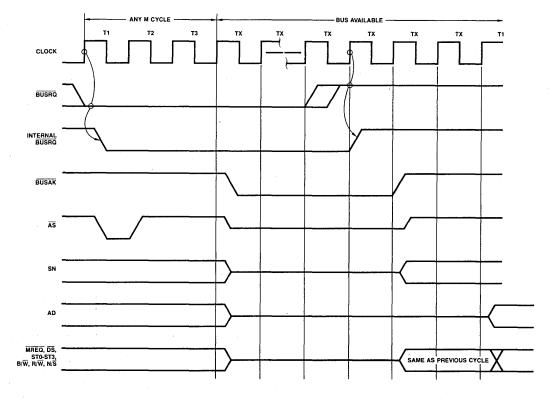

#### **Bus Request Chain Protocol**

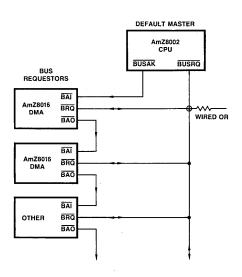

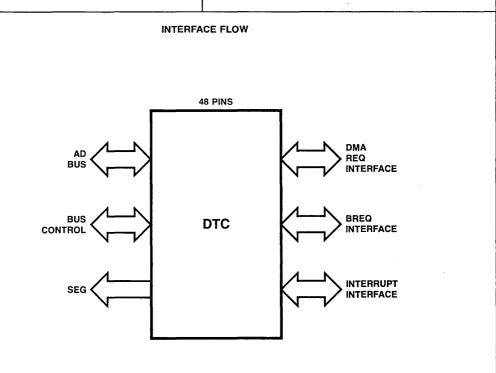

Typical data bus transactions follow a master/slave protocol between the AmZ8000 CPU and its peripherals. The CPU is the default bus master and does not require arbitration to access the bus. Some complex peripherals, like the AmZ8016 DMA, may require to obtain bus mastership in order to perform more complex bus transactions than the typical peripheral.

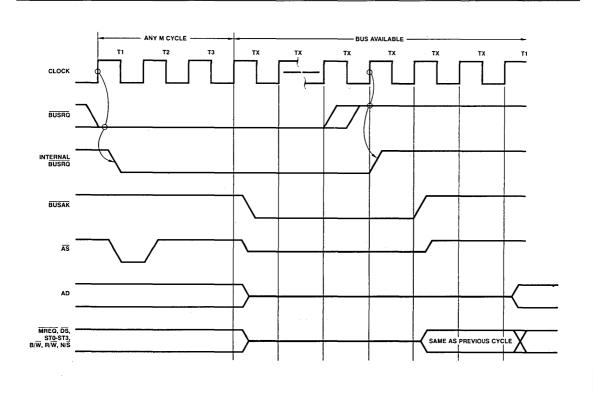

A Bus Request protocol is easily implemented to orderly request the AmZ8000 CPU to grant its bus mastership to one of several peripherals capable of commanding the bus. A daisy chain link priority resolution among bus requestors, along with a bus request protocol, forms an efficient bus mastership transfer. As common to most microcomputers, the AmZ8000 CPU recognizes asynchronous bus requests on its BUSRQ input pin, and grants it upon completion of the current machine cycle by causing its address/data, control and status outputs to go to high impedance and its BUSAK output pin to become active.

The algorithm for bus priority and request for bus requestors is as follows:

- 1. The requestor looks at its BRQ line to see if it is active. The BRQ line is bidirectional.

- If the BRQ line is active, then the requestor waits. This implements the policy of non-preemption, since another peripheral could be in process of using or requesting the bus.

- If the BRQ line is inactive, then the requestor activates its BRQ output and waits for its BAI input to go active. Upon BAI active, the requestor deactivates its BAO output (as opposed to letting the BAI input to ripple-thru to the BAO output), and takes control of the bus.

It is easy to see how the daisy chain link among peripherals is implemented to determine peripheral bus mastership priority.

#### **Typical System Structures**

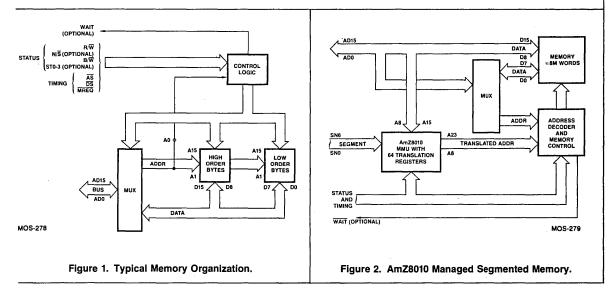

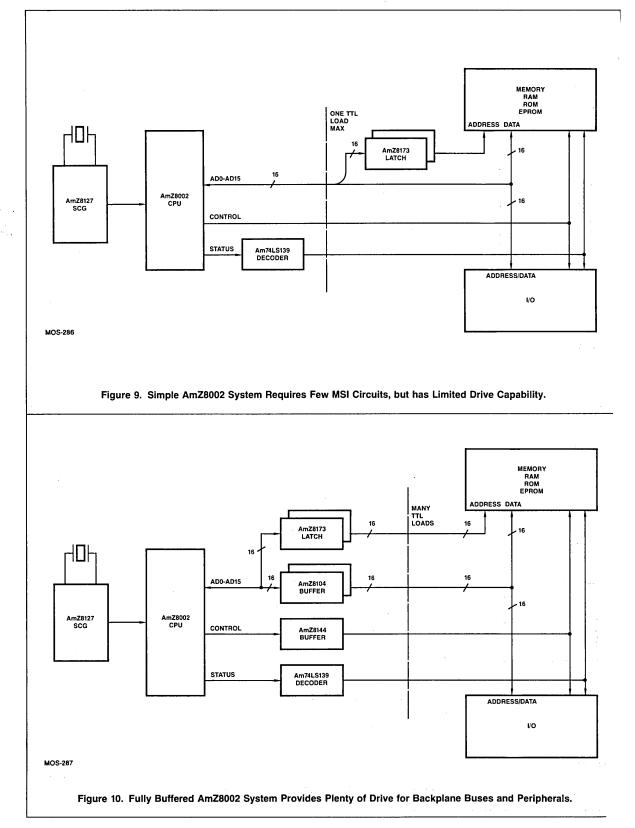

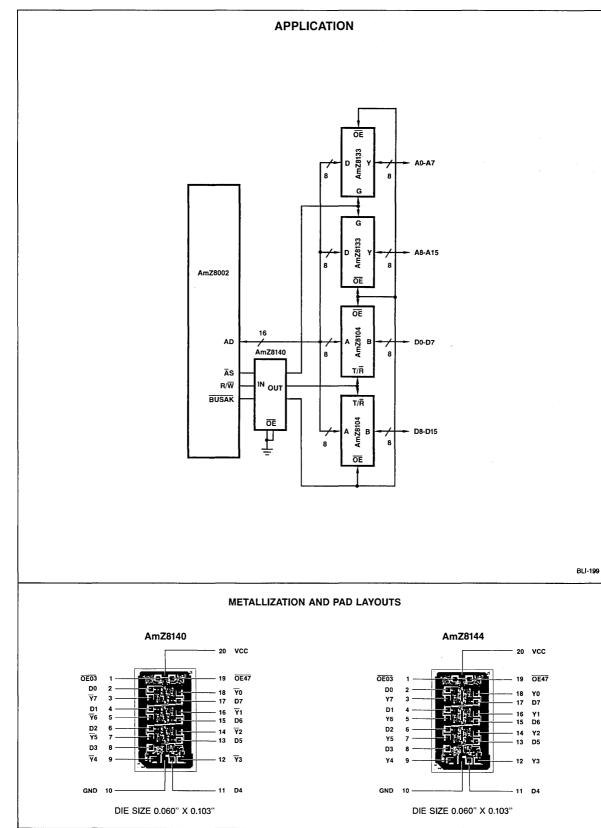

The complexity of an AmZ8000 system mainly depends on the application and the needs of the user. Interface peripheral and memory devices can vary widely upon this complexity. At various stages of complexity, different types of system interface logic must be used depending on the loading requirements. A minimum AmZ8002 system is shown in Figure 9. The AmZ8002 CPU can drive one standard TTL load. An AmZ8127 clock generator is used to provide the system clock. Since the address and data are multiplexed together, an AmZ8173 octal latch is used to latch the addresses. Status is decoded by a Am74LS139 decoder. If loading exceeds one TTL load, buffers should be used as in Figure 10. On the data bus, two AmZ8104s are used to provide 16 bidirectional data lines. While an AmZ8144 buffer is used to give extra fan-out to the control signals. Direct addressing is available up to 64K bytes.

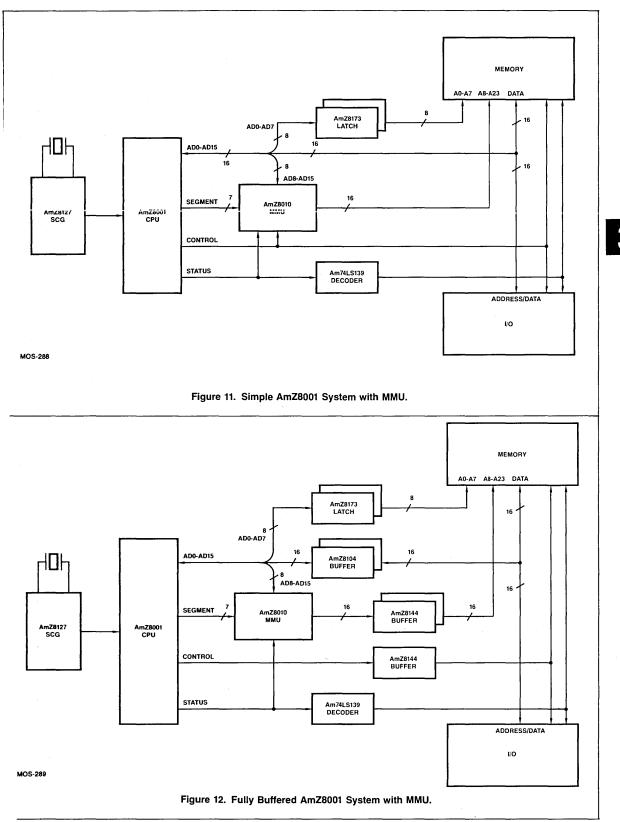

In Figure 11, an AmZ8001 segmented CPU is shown with the AmZ8010 Memory Management Unit. The AmZ8010 extends the memory into 64 segments where each segment can vary between 256 to 64K bytes. Without the AmZ8010, the AmZ8001 CPU can only access 8M bytes directly. This example can drive only TTL load. More drive capability could be added as in Figure 12. The buffering example is the same as Figure 11 with the exception of the AmZ8010 and the AmZ8144 to buffer the segment addresses.

Figure 8. Bus Request Chain Link.

### System Architecture

3-7

. . .

.

. .

.

1

.

. .

• •

.

### AmZ8000 Vicroprocessor Family

# CHAPTER 4

## components

69 69 69 69 69 69 6-9 6-9 AU 10 6.8 1 4.1 1 -4 o i) . <u>ال</u> Å. d.U N AU A U 1 đ.

### AmZ8001 16-Bit Microprocessor

### PRELIMINARY DATA

| Package      | Ambient                                  | Maximum Clock Frequency |  |

|--------------|------------------------------------------|-------------------------|--|

| Type         | Temperature                              | 4MHz                    |  |

| Hermetic DIP | $0^{\circ}C \leq T_{A} \leq 70^{\circ}C$ | AmZ8001DC               |  |

4

### INTERFACE SIGNAL DESCRIPTION

V<sub>CC</sub>: +5V Power Supply V<sub>SS</sub>: Ground

### AD0-AD15: Address/Data Bus (Bidirectional, 3-State)

This 16-bit multiplexed address/data bus is used for all I/O and memory transactions. HIGH on the bus corresponds to 1 and LOW corresponds to 0. AD0 is the least significant bit position with AD15 is most significant. The  $\overline{AS}$  output and  $\overline{DS}$  output will indicate whether the bus is used for address offset or data. The status output lines ST0-ST3 will indicate the type of transaction; memory or I/O.

### AS: Address Strobe (Output, 3-State)

LOW on this output indicates that the AD0-AD15 bus contains address information. The address information is stable by the time of the LOW-to-HIGH transition of the AS output (see timing diagrams). The status outputs ST0-ST3 indicate whether the bus contains a memory address or I/O address.

### DS: Data Strobe (Output, 3-State)

LOW on this output indicates that the AD0-AD15 bus is being used for data transfer. The  $R/\overline{W}$  output indicates the direction of data transfer – read (or in) means data into the CPU and write (or out) means data from the CPU. During a read operation, data can be gated on to the bus when DS goes LOW. A LOW-to-HIGH transition on the DS output indicates that the CPU has accepted the data (see timing diagram). During a write operation, LOW on the DS output indicates that data is setup on the bus. Data will be removed sometime after the LOW-to-HIGH transition of the DS output (see timing diagram).

### R/W: Read/Write (Output, 3-State)

This output indicates the direction of data flow on the AD0-AD15 bus. HIGH indicates a read operation, i.e., data into the CPU and LOW indicates a write operation, i.e., data from the CPU. This output is activated at the same time as  $\overline{AS}$  going LOW and remains stable for the duration of the whole transaction (see timing diagram).

### B/W: Byte/Word (Output, 3-State)

This output indicates the type of data transferred on the AD0-AD15 bus. HIGH indicates byte (8-bit) and LOW indicates word (16-bit) transfer. This output is activated at the same stage as AS going LOW and remains valid for the duration of the whole transaction (see timing diagram). The address generated by the CPU is always a byte address. However, the memory is organized as 16-bit words. All instructions and word operands are word aligned and are addressed by even addresses. Thus, for all word transactions with the memory the least significant address bit will be zero. When addressing the memory for byte transactions, the least significant address bit determines which byte of the memory word is needed; even address specifies the most significant byte and odd address specifies the least significant byte. In the case of I/O transactions, the address information on the AD0-AD15 bus refers to an I/O port and B/W determines whether a data word or data byte will be transacted. During I/O byte transactions, the least significant address bit A0 determines which half of the AD0-AD15 bus will be used for the I/O transactions. The ST0-ST3 outputs will indicate whether the current transaction is for memory, normal I/O or special I/O.

### ST0-ST3: Status (Outputs, 3-State)

These four outputs contain information regarding the current transaction in a coded form. The status line codes are shown in the following table:

| ST2 | ST1                                                                     | ST0                                                  |                                                                                                                        |

|-----|-------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| L   | Ļ                                                                       | L                                                    | Internal Operation                                                                                                     |

| L   | Ļ                                                                       | н                                                    | Memory Refresh                                                                                                         |

| L   | н                                                                       | L                                                    | Normal I/O Transaction                                                                                                 |

| L   | н                                                                       | н                                                    | Special I/O Transaction                                                                                                |

| н   | L                                                                       | L.                                                   | Segment Trap Acknowledge                                                                                               |

| н   | L.                                                                      | н                                                    | Non-Maskable Interrupt Acknowledge                                                                                     |

| н   | н                                                                       | L                                                    | Non-Vectored Interrupt Acknowledge                                                                                     |

| Н   | Н                                                                       | н                                                    | Vectored Interrupt Acknowledge                                                                                         |

| L   | L                                                                       | L                                                    | Memory Transaction for Operand                                                                                         |

| L   | L                                                                       | н                                                    | Memory Transaction for Stack                                                                                           |

| L   | н                                                                       | L                                                    | Reserved                                                                                                               |

| L   | н                                                                       | н                                                    | Reserved                                                                                                               |

| н   | L                                                                       | L                                                    | Memory Transaction for Instruction<br>Fetch (Subsequent Word)                                                          |

| н   | L                                                                       | н                                                    | Memory Transaction for Instruction<br>Fetch (First Word)                                                               |

| н   | н                                                                       | L                                                    | Reserved                                                                                                               |

| н   | н                                                                       | н                                                    | Reserved                                                                                                               |

|     | L<br>L<br>L<br>H<br>H<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>H<br>H<br>H | L L<br>L H<br>L H<br>H L<br>H L<br>H L<br>L L<br>L L | L L L<br>L L H<br>L H L<br>H L<br>H L<br>H L H<br>H L H<br>H H H<br>L L<br>L H<br>L L<br>H L<br>L H<br>L L<br>H L<br>H |

### WAIT: Wait (Input)

LOW on this input indicates to the CPU that memory or I/O is not ready for the data transfer and hence the current transaction should be stretched. The WAIT input is sampled by the CPU at certain instances during the transaction (see timing diagram). If WAIT input is LOW at these instances, the CPU will go into wait state to prolong the transaction. The wait state will repeat until the WAIT input is HIGH at the sampling instant.

### N/S: Normal/System Mode (Output, 3-State)

HIGH on this output indicates that the CPU is operating in Normal Mode and LOW indicates operation in System Mode. This output is derived from the Flag Control Word (FCW) register. The FCW register is described under the program status information section of this document.

### MREQ: Memory Request (Output, 3-State)

LOW on this output indicates that a CPU transaction with memory is taking place.

### **BUSRQ:** Bus Request (Input)

LOW on this input indicates to the CPU that another device (such as DMA) is requesting to take control of the bus. The BUSRQ input can be driven LOW anytime. The CPU synchronizes this input internally. The CPU responds by activating BUSAK output LOW to indicate that the bus has been relinquished. Relinquishing the bus means that the AD0-AD15, AS, DS, B/W, R/W, N/S, ST0-ST3, SN0-SN6 and MREQ outputs will be in the high impedance state. The requesting device should control these lines in an identical fashion to the CPU to accomplish transactions. The BUSRQ input must remain LOW as long as needed to perform all the transactions and the CPU will keep the BUSAK output LOW. After completing the transactions, the device must disable the AD0-AD15, AS, DS, B/W, R/W, N/S, ST0-ST3, SN0-SN6 and MREQ into the high impedance state and stop driving the BUSRQ input LOW. The CPU will make BUSAK output HIGH sometime later and take back the bus control.

### BUSAK: Bus Acknowledge (Output)

LOW on this output indicates that the CPU has relinquished the bus in response to a bus request.

### NMI: Non-Maskable Interrupt (Input)

HIGH to LOW transition on this input constitutes non-maskable interrupt request. The CPU will respond with the Non-maskable Interrupt Acknowledge on the ST0-ST3 outputs and will enter an interrupt sequence. The transition on the NMI can occur anytime. Of the three kinds of interrupts available, the non-maskable interrupt has the highest priority.

### VI: Vectored Interrupt (Input)

LOW on this input constitutes vectored interrupt request. Vectored interrupt is next lower to the non-maskable interrupt in priority. The VIE bit in the Flag and Control Word register must be 1 for the vectored interrupt to be honored. The CPU will respond with Vectored Interrupt Acknowledge code on the ST0-ST3 outputs and will begin the interrupt sequence. The  $\overline{VI}$  input can be driven LOW anytime and should be held LOW until acknowledged.

### **NVI:** Non-Vectored Interrupt (Input)

LOW on this input constitutes non-vectored interrupt request. Non-vectored has the lowest priority of the three types of interrupts. The NVIE bit in the Flag and Control Word register must be 1 for this request to be honored. The CPU will respond with Non-Vectored Interrupt Acknowledge code on the ST0<u>-ST</u>3 outputs and will begin the interrupt sequence. The NVI input can be driven LOW anytime and should be held LOW until acknowledged.

### μl: Micro-In (Input)

This input participates in the resource request daisy chain. See the section on multimicroprocessor support facilities in this document.

### $\overline{\mu O}$ : Micro-Out (Output)

This output participates in the resource request daisy chain. See the section on multimicroprocessor support facilities in this document.

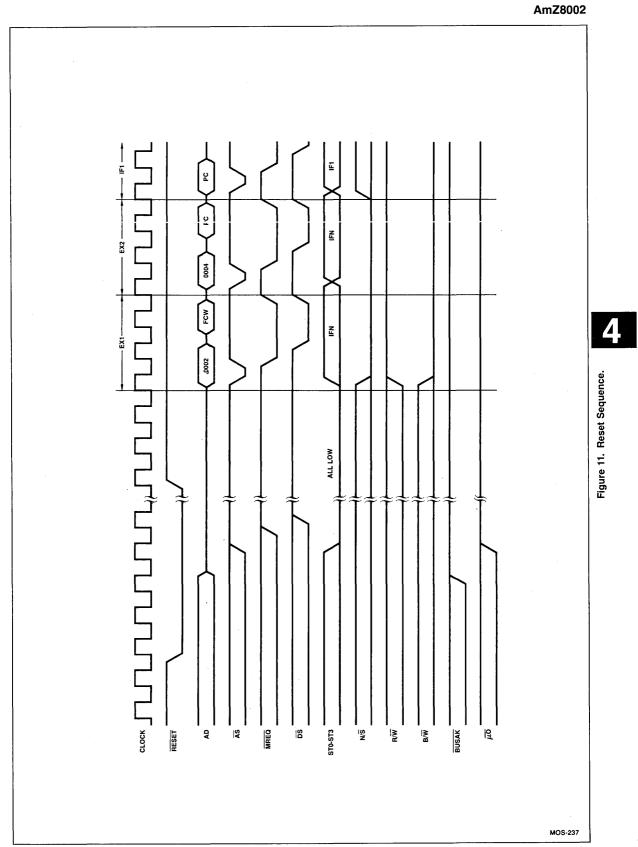

### RESET: Reset (Input)

LOW on this input initiates a reset sequence in the CPU. See the section on Initialization for details on reset sequence.

### CLK: Clock (Input)

All CPU operations are controlled from the signal fed into this input. See DC characteristics for clock voltage level requirements.

### **DECOUPLE: (Output)**

Output from the on-chip substrate bias generator. Do not use.

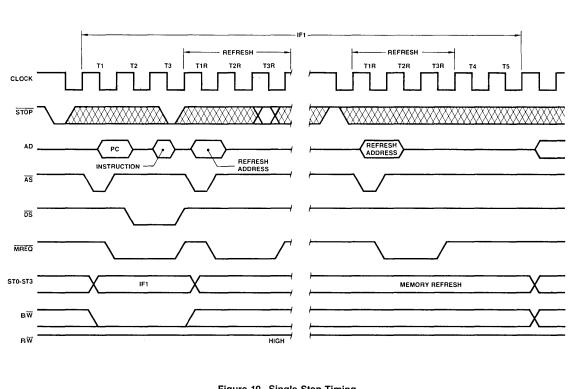

### STOP: Stop (Input)

This active LOW input facilitates one instruction at a time operation. See the section on single stepping.

### SN0-SN6: Segment Number (Outputs, 3-State)

These seven outputs contain the segment number part of a memory address. A HIGH on the output corresponds to 1 and a LOW corresponds to 0. SN0 is the least significant bit position and SN6 is the most significant bit position.

### SEGT: Segment Trap (Input)

LOW on this input constitutes a segment trap request. If the line is driven LOW, the CPU will respond with the Segment Trap Acknowledge code on the Status lines, and commence a trap sequence. The SEGT input may be driven LOW at any time and is customarily held LOW until acknowledged. This input has priority over the interrupts.

### PROCESSOR ORGANIZATION

The following is a brief discussion of the AmZ8001 CPU. For detailed information, see the AmZ8001/AmZ8002 Processor Instruction Set Manual (Publication No. AM-PUB086).

### GENERAL PURPOSE REGISTERS

The CPU is organized around sixteen 16-bit general purpose registers R0 through R15 as shown in Figure 1. For byte operations, the first eight registers (R0 through R7) can also be addressed as sixteen 8-bit registers designated as RL0, RH0 and so on to RL7 and RH7. The sixteen registers can also be grouped in pairs RR0, RR2 and so on to RR14 to form eight long word (32-bit) registers. Similarly, the sixteen registers can be grouped in quadruples RQ0, RQ4, RQ8 and RQ12 to form four 64-bit registers.

### STACK POINTER

The AmZ8001 architecture allows stacks to be maintained in memory. Any general-purpose register pair except RR0 can be used as a stack pointer in stack manipulating instructions such as PUSH and POP. The designated register pair holds a 23-bit segmented address. Certain instructions (such as subroutine call and return) make implicit use of the register pair RR14 as the stack pointer. Two implicit stacks are allowed – normal stack using RR14 as the stack pointer (see Figure 1). If the CPU is operating in the Normal Mode, RR14 is active, and if the CPU is in System Mode, RR14' will be used instead of RR14. The implied stack pointer is a part of the general registers and hence can be manipulated using the instructions available for register operations.

4

### **PROCESSOR STATUS**

The CPU status consists of the 16-bit flag and control word (FCW) register, and the 23-bit program counter (see Figure 2). A reserved word is also included for future expansion. The following is a brief description of the FCW bits.

- SEG: Segmented/Non-Segmented Bit. Indicates whether the AmZ8001 is running in segmented or non-segmented mode. 1 indicates segmented, 0 indicates non-segmented. See the section on non-segmented mode, elsewhere in this document.

- S/N: System/Normal 1 indicates System Mode and 0 indicates Normal Mode.

- VIE: Vectored Interrupt Enable 1 indicates that Vectored Interrupt requests will be honored.

- NVIE: Non-Vectored Interrupt Enable 1 indicates that Nonvectored interrupt requests will be honored.

- C: Carry 1 indicates that a carry has occurred from the most significant bit position when performing arithmetic operations.

- **Z**: Zero 1 indicates that the result of an operation is zero.

- S: Sign 1 indicates that the result of an operation is negative i.e., most significant bit is one.

- **P/V:** Parity/Overflow 1 indicates that there was an overflow during arithmetic operations. For byte logical operations this bit indicates parity of the result.

- DA: Decimal Adjust Records byte arithmetic operations.

- H: Half Carry 1 indicates that there was a carry from the most significant bit of the lower digit during byte arithmetic.

### DATA TYPES

The AmZ8001 instructions operate on bits, digits (4 bits), bytes (8 bits), words (16 bits), long words (32 bits), byte strings and word strings type operands. Bits can be set, reset or tested. Digits are used to facilitate BCD arithmetic operations. Bytes are used for characters and small integers. Words are used for large integer values and addresses while long words are used for large integer values and addresses. All operands except strings can reside either in memory or general registers. Strings can reside in memory only.

### INTERRUPT AND TRAP STRUCTURE

Interrupt is defined as an external asynchronous event requiring program interruption. For example, interruption is caused by a peripheral needing service. Traps are synchronous events resulting from execution of certain instructions under some defined circumstances. Both interrupts and traps are handled in a similar manner by the AmZ8001.

The AmZ8001 supports three types of interrupts in order of descending priority - non-maskable, vectored and non-vectored.

The vectored and non-vectored interrupts can be disabled by appropriate control bits in the FCW. The AmZ8001 has four traps – system call, segment trap, unimplemented opcode and privileged instruction. The traps have higher priority than interrupts.

When an interrupt or trap occurs, the current program status is automatically pushed on to the system stack. The program status consists of processor status (i.e., PC and FCW) plus a 16-bit identifier. The identifier contains the reason, source and other coded information relating to the interrupt or trap.

After saving the current program status, the new processor status is automatically loaded from the new program status area located in the memory. This area is designated by the New Program Status Area Pointer (NPSAP) register. See AM-PUB086 publication for further details.

### SEGMENTED ADDRESSING

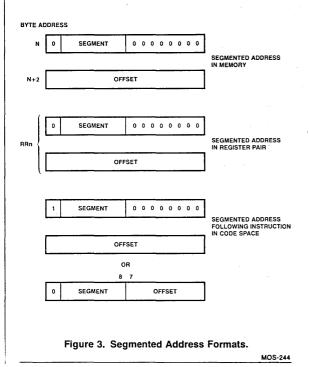

The AmZ8001 can directly address up to 8MB of memory space, using a 23-bit segmented address. The memory space is divided up into 128 segments, each up to 64KB in size. The upper seven bits of address designate the segment number, and are available on the SN0-SN6 outputs during a memory transaction. See the section on memory transactions for details.

The lower sixteen bits of address designate an offset within the segment, relative to the start of the segment, and are available on AD0-AD15 during part of the memory transaction. See the section on memory transactions for details.

The segmented address may be stored as a long word in memory, or in a register pair. The segment number and offset can be manipulated separately or together, by suitable use of the instruction set.

When the segmented address is contained in code space, a short offset format may be adopted. The segmented address is stored as one word, seven bits of segment number and eight bits of offset. Figure 3 shows the format for segmented addresses.

### ADDRESSING MODES

Information contained in the AmZ8001 instructions consists of the operation to be performed, the operand type and the location of the operands. Operand locations are designated by general register addresses, memory addresses or I/O addresses. The addressing mode of a given instruction defines the address space referenced and the method to compute the operand address. Addressing modes are explicitly specified or implied in an instruction. Figure 4 illustrates the eight explicit addressing modes: Register (R), Immediate (IM), Indirect Register (IR), Direct Address (DA), Indexed (X), Relative Address (RA), Base Address (BA) and Base Indexed (BX).

When an effective segmented address is being computed according to the designated addressing mode, the segment number is not affected by any carry from the 16-bit offset.

#### NON-SEGMENTED MODE ON THE AmZ8001

The AmZ8001 can execute code designed to run on the nonsegmented AmZ8002. This is achieved by changing the mode of execution of the AmZ8001 from segmented to non-segmented by writing a 0 to the SEG bit in the FCW. (See the section on processor status.) The change to non-segmented mode sets up a suitable environment for running non-segmented code. However, this environment only exists within the code segment that caused the change of mode from segmented to non-segmented.

SN0-SN6 will continue to indicate the code segment until a reset, interruption or return to segmented mode is encountered.

The effects of the non-segmented mode of operation on the AmZ8001 are described below.

- a) The AmZ8001 will interpret instruction length as if it was a non-segmented AmZ8002.

- b) The AmZ8001 will implement address computation in an identical manner to the AmZ8002.

Other CPU functions, such as interrupt and trap handling, reset and stack pointer manipulation are unaltered. These functions are characterized by the type of CPU, not by the state of the SEG bit in the FCW.

#### INPUT/OUTPUT

A set of I/O instructions are provided to accomplish byte or word transfers between the AmZ8001 and I/O devices. I/O devices are addressed using 16-bit I/O port addresses and I/O address space is not a part of the memory address space. Two types of I/O instructions are provided; each with its own 16-bit address space. I/O instructions include a comprehensive set of In, Out and Block transfers.

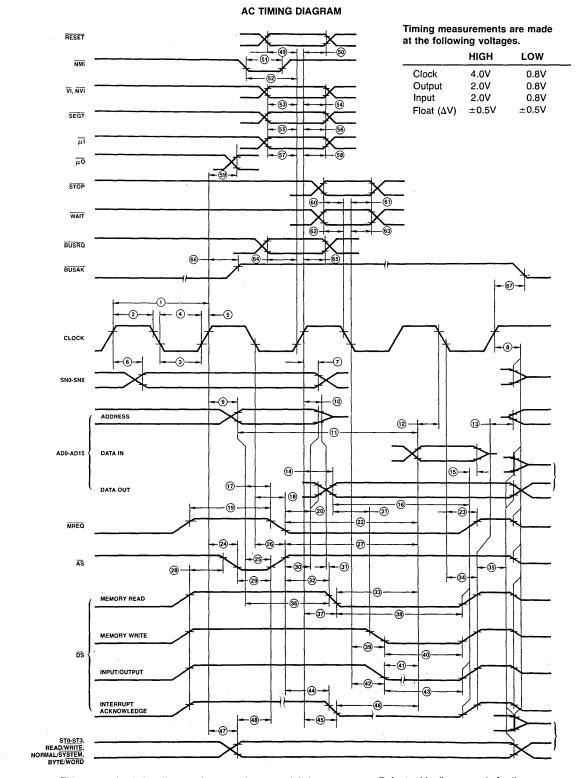

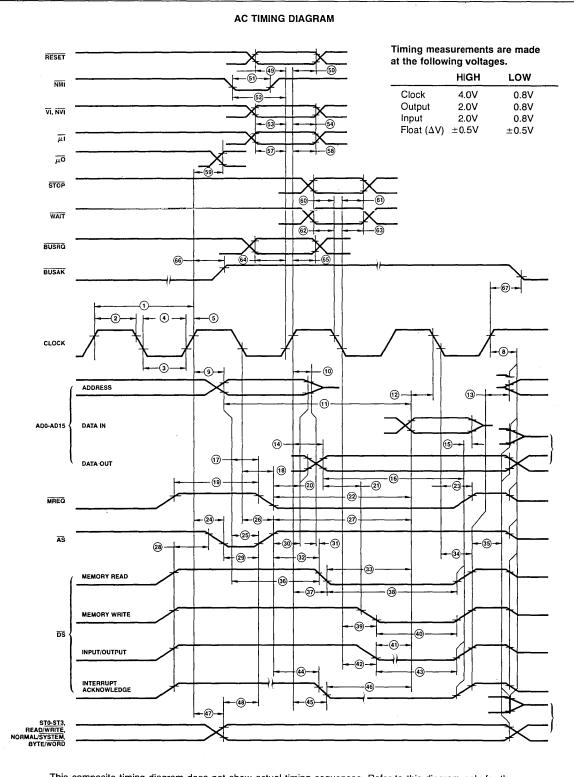

#### **CPU TIMING**

The AmZ8001 accomplishes instruction execution by stepping through a pre-determined sequence of machine cycles, such as memory read, memory write, etc. Each machine cycle requires between three and ten clock cycles. Bus Requests by DMA devices are granted at machine cycle boundaries. No machine cycle is longer than ten clock cycles; thus assuring fast response to a Bus Request (assuming no extra wait states). The start of a machine cycle is always marked by a LOW pulse on the  $\overline{\rm AS}$  output. The status output lines ST0-ST3 indicate the nature of the current cycle in a coded form.

#### STATUS LINE CODES

Status line coding was listed in the table shown under ST0-ST3 outputs in the Interface Signal Description. The following is a detailed description of the status codes.

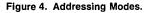

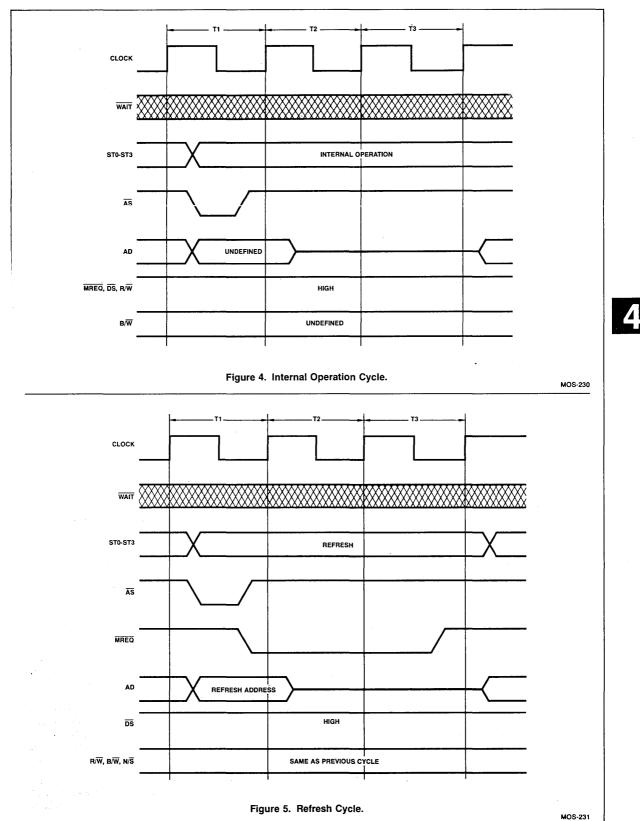

#### Internal Operation:

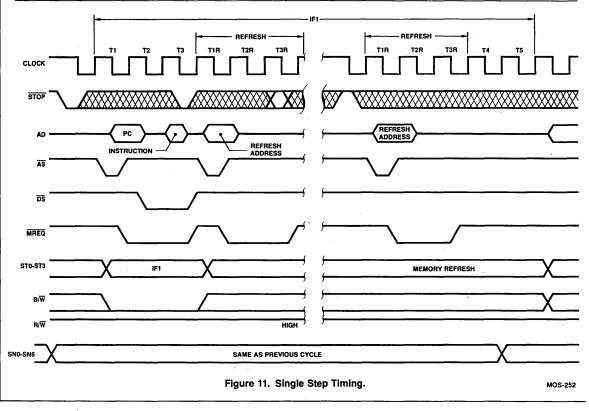

This status code indicates that the AmZ6001 is going through a machine cycle for its internal operation. Figure 5 depicts an internal operation cycle. It consists of three clock periods identified as T1, T2 and T3. The  $\overline{AS}$  output will be activated with a LOW pulse by the AmZ8001 to mark the start of a machine cycle. The ST0-ST3 will reflect the code for the internal operation. The  $\overline{MREQ}$ ,  $\overline{DS}$  and R/W outputs will be HIGH. The N/S and SN0-SN6 outputs will remain at the same level as in the previous machine cycle. The AmZ8001 will ignore the  $\overline{WAIT}$  input during the internal operation cycle. The CPU will drive the AD0-AD15 bus with unspecified information during T1. However, the bus will go into high impedance during T2 and remain in that state for the CPU with unspecified information.

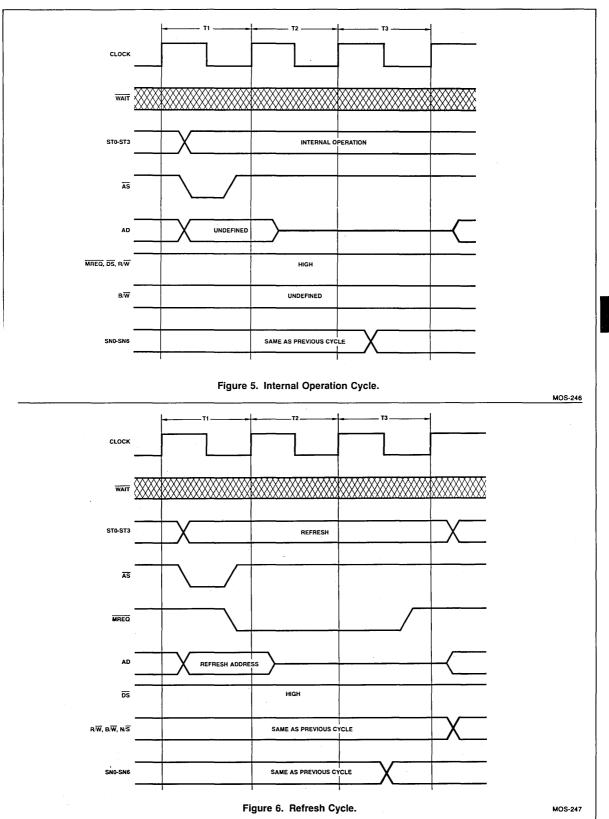

#### Memory Refresh:

This status code indicates that AmZ8001 is accessing the memory to refresh. The refresh cycle consists of three clock periods as depicted in Figure 6. The CPU will activate the AS output with a LOW pulse to mark the beginning of a machine cycle and ST0-ST3 outputs will reflect the refresh cycle code. The least significant 9 lines of the AD0-AD15 bus contain the refresh address. Because the memory is word organized, the AD0 will always be LOW. The most significant 7 bus lines are not specified. The DS output will remain HIGH for the entire cycle while R/W, B/W, SN0-SN6 and N/S outputs will remain at the same level as in the machine cycle prior to refresh. The AD0-AD15 bus will go into high impedance state during T2 period and remain there for the remainder of the cycle. The AmZ8001 will activate the MREQ output LOW during the refresh cycle. It should be noted that WAIT input is ignored by the CPU for refresh operations.

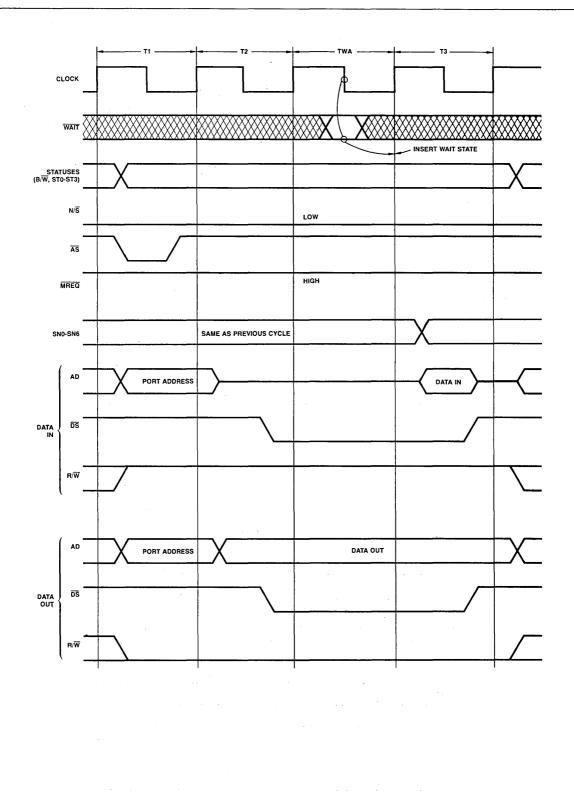

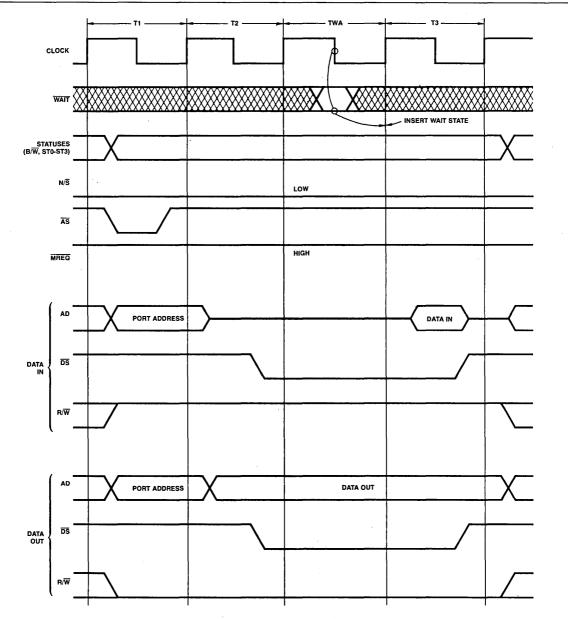

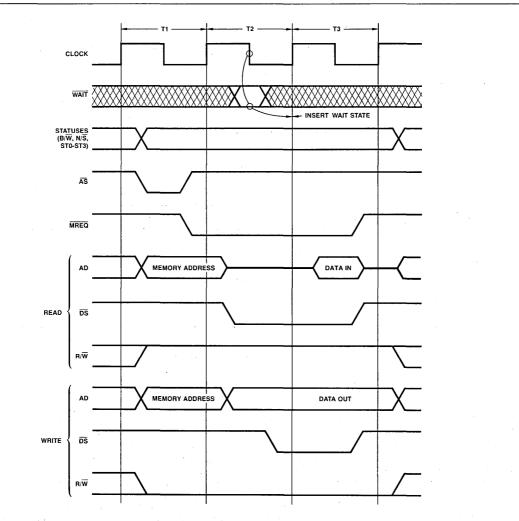

#### I/O Transactions:

There are two status line codes used for I/O transaction cycles. The AmZ8001 provides two separate I/O spaces and two types of instructions called Normal I/O and Special I/O. Each I/O space is addressed by a 16-bit address called port address. The timing for both types of I/O transactions is essentially identical. A typical I/O cycle consists of four clock periods T1, T2, TWA and T3 as shown in Figure 7. The TWA is the wait state; insertion of one wait state for an I/O cycle is always automatic. Additional wait cycles can be inserted by LOW on the WAIT input. The WAIT input is sampled during every TW state. If this input is LOW, one more wait state will be inserted. Insertion of wait states continues until WAIT input is HIGH. T3 state will follow the last wait state to complete the I/O cycle.

During I/O cycles the ST0-ST3 outputs will reflect appropriate code depending on the type of instruction being executed (Normal I/O or Special I/O). As output will be pulsed LOW to mark the beginning of the cycle. The CPU drives the AD0-AD15 bus with the 16-bit port address specified by the current instruction. The N/S output will be LOW indicating that CPU is operating in the system mode. It should be recalled that the N/S output is derived from the appropriate bit in the FCW register. All I/O instructions are privileged instructions and will be allowed to execute only if the FCW specifies system mode operation. The MREQ output will be HIGH. The AmZ8001 I/O instructions provide both word or byte transactions. The B/W output will be HIGH or LOW depending whether the instruction specifies a

byte or word transfer. The SN0-SN6 output will remain at the same level as in the machine cycle prior to the I/O cycle.

Two kinds of I/O transfers should be considered: Data In means reading from the device and Data Out means writing into the device. For In operations, the  $R\overline{W}$  output will be HIGH. The AD0-AD15 bus will go into high impedance state during T2. During byte input instructions, the CPU reads either the even or odd half of the Data Bus dependent upon the port address. If the port address is even, the most significant half of the Data Bus is read. If the port address is odd, the least significant half of the Data Bus is read. During word input instructions, the CPU reads all 16 bits of the Data Bus. The AmZ8001 will drive the  $\overline{DS}$

#### MOS-245

Figure 7. AmZ8001 I/O Cycle.

output LOW to signal to the device that data can be gated on to the bus. The CPU will accept the data during T3 and  $\overline{\rm DS}$  output will go HIGH signalling the end of an I/O transaction.

For Data Out, the R/W output will be LOW. The AmZ8001 will provide data on the AD0-AD15 bus and activates the  $\overline{DS}$  output LOW during T2. During byte output instructions, the CPU duplicates the byte data onto both the high and low halves of the Data Bus and external logic, using A0, enables the appropriate byte port. During word output instructions the CPU outputs data onto all 16 bits of the Data Bus. The  $\overline{DS}$  output goes HIGH during T3 and the cycle is complete.

#### **Memory Transactions:**

There are four status line codes that indicate a memory transaction:

- a) Memory transaction to read or write an operand

- b) Memory transaction to read from or write into the stack

- c) Memory transaction to fetch the first word of an instruction (sometimes called IF1)

- d) Memory transaction to fetch the subsequent word of an instruction (sometimes called IFN).

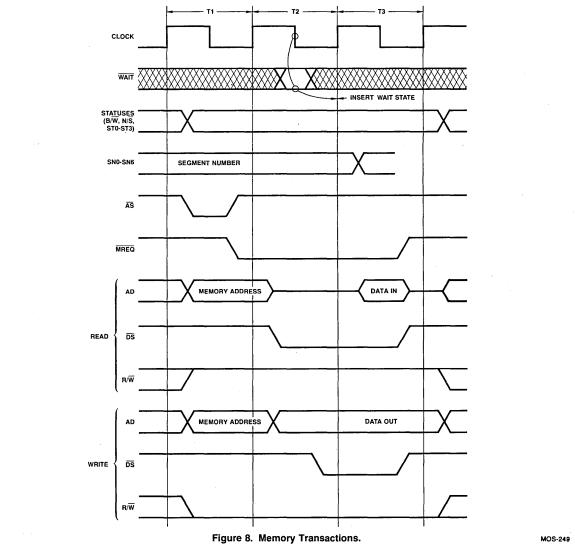

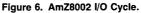

It can be appreciated that all the above transactions essentially fall into two categories: memory read and memory write. In the case of IF1 and IFN cycles, the memory will be read at the address supplied by the program counter. All AmZ8001 instructions are multiples of 16-bit words. Words are always addressed by an even address. Thus IF1 and IFN cycles involve performing a memory read for words. On the other hand, a memory transaction for operand and stack operation could be a read or write. Moreover, an operand could be a word or a byte. For stack operation involving the implied stack pointer the address will be supplied by the RR14 (or RR14'). For operand transactions, the memory address will come from several sources depending on the instruction and the addressing mode. Memory transaction cycle timing is shown in Figure 8. It typically consists of three clock periods T1, T2 and T3. Wait states (TW) can be inserted

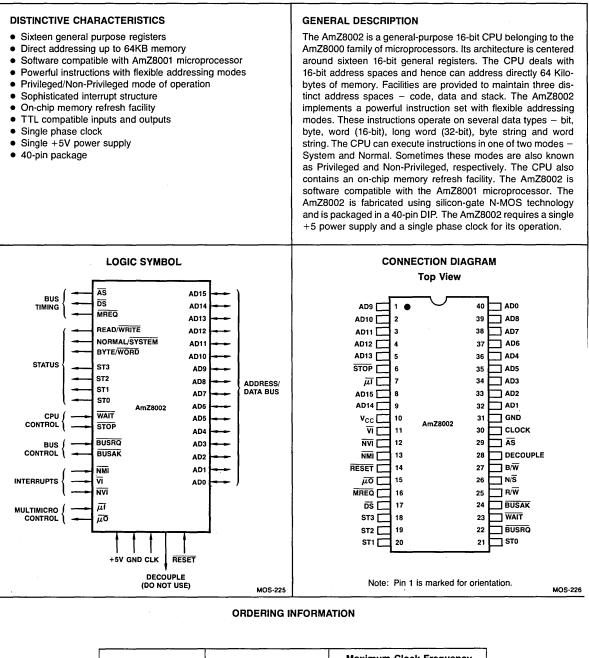

between T2 and T3 by activating the WAIT input LOW. The WAIT input will be sampled during T2 and during every subsequent TW. The ST0-ST3 outputs will reflect the appropriate code for the current cycle early in T1 and the AS output will be pulsed LOW to mark the beginning of the cycle. The N/S output will indicate whether the normal or system address space will be used for the current cycle. As shown in the figure the MREQ output will go LOW during T1 to indicate a memory operation.