# **Advanced Micro Devices**

# AmZ8000 Family Reference Manual

# Principles of Operation AmZ8001/2 Processor Instruction Set

Copyright © 1979 by Advanced Micro Devices, Inc.

Material in this document has been generated from information supplied by Zilog, Inc. Advanced Micro Devices, Inc. reserves the right to modify information contained in this document without notice.

AM-PUB086

## PREFACE

The present state of MOS LSI semiconductor technology has permitted very powerful and complex general purpose processors to be economically incorporated into a single silicon chip. This capability ushers in a new era of system design, where for the first time low cost tools are available for solving many complex problems. Significant levels of computing power are now available inexpensively and can be used both to lower the cost of high performance systems and to improve the efficiency of programmers in their increasingly more complex tasks.

The AmZ8000 family is the first processor family to fully exploit this new era, breaking tradition with the legacy of compromised performance dictated by past manufacturing technologies. The two processors in the family incorporate many of the features heuristically evolved from both minicomputer and main frame systems. This gives the applications programmer, the systems programmer and the system designer the power and flexibility required for today's complex systems.

This document describes the Processor Instruction Set in detail. The descriptions have been arranged with one instruction per page for completeness and for easy reference. This approach has been found to be suitable for both hardware designers and for programmers. There is no intention to be concise, but instead to provide users with complete, detailed, easy-to-understand descriptions of all the processor instructions.

The information in this document will later be updated and incorporated as the Instruction Chapter in a forthcoming AmZ8000 family reference manual. This document is one of several in support of the AmZ8000 family.

## CONTENTS

## PROCESSOR ORGANIZATION

| Introduction                      | 1 |

|-----------------------------------|---|

| Register Structure                | ļ |

| Stack Pointer                     | 6 |

| Program Counter                   | 7 |

| Processor Status Information      | 9 |

| New Program Status Area Pointer   | 2 |

| Refresh Counter                   | 2 |

| Addressing Modes                  | 6 |

| Operand Addressing                | 0 |

| Memory Addressing                 | 0 |

| Interrupts and Traps              | 5 |

| Instruction Format 4              | 0 |

| Input/Output                      | 3 |

| Condition Codes                   | 3 |

| Instruction Set                   | 6 |

| Instructions Arranged by Mnemonic | 1 |

### PROCESSOR ORGANIZATION

## Introduction

The AmZ8001 and AmZ8002 are initial members of the AmZ8000 sixteen bit microprocessor family. These central processing units (CPUs) are software compatible and hence, unless otherwise indicated, information contained in this document applies to both. The AmZ8001 handles 23-bit addresses giving it 8 Megabyte (8,388,608 bytes) addressing capability. Memory associated with the AmZ8001 system is considered to consist of 128 segments with 64 Kilobytes (65,536 bytes) per segment. Thus, the AmZ8001 is also known as the segmented version. On the other hand, the AmZ8002 has 16-bit (64 Kilobyte) addressing capability and is also known as the non-segmented version.

## **Register Structure**

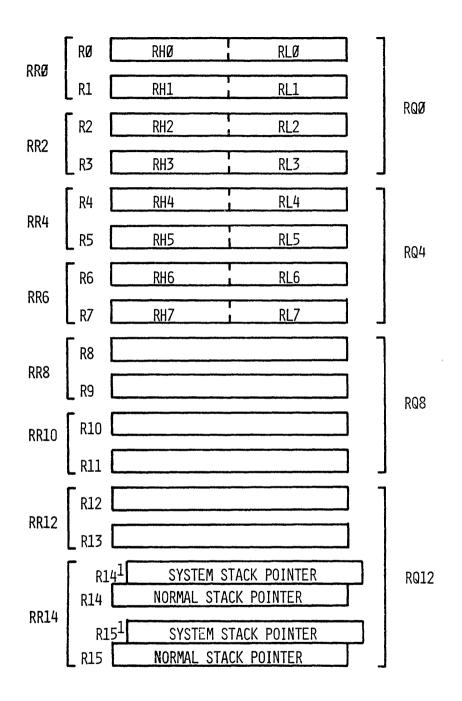

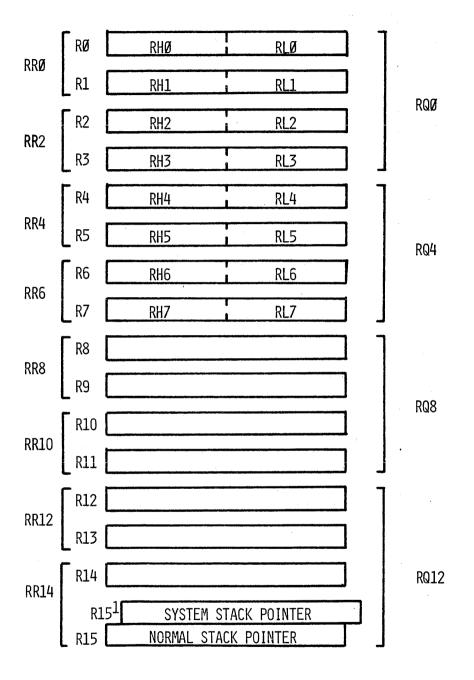

The CPUs are centered around sixteen 16-bit general purpose registers identified as RØ through R15. The desired register is usually designated by a four bit field in an instruction. In general, the instructions operate on byte (8-bit), word (16-bit), or long word (32-bit) operands. For byte operations, the first eight general purpose registers (RØ through R7) are treated as sixteen 8-bit registers identified as RLØ, RHØ, RL1 and so on to RL7 and RH7. A four bit field in an instruction designates the desired byte register. For operations requiring long-words, the 16-bit general purpose registers are grouped in pairs. For example, the RØ, R1 pair is identified as RRØ, the R2, R3 pair as RR2 and so on to the R14, R15 pair as RR14. Thus, the general purpose registers can also be treated as eight 32-bit registers. The three most significant bits of a 4-bit field in an instruction designate the desired register pair and the fourth bit should be zero. For certain 64-bit operands, the general purpose registers can also be grouped in quads. For example, the RØ, R1, R2 and R3 group is identified as ROØ, the R4, R5, R6 and R7 group as RO4 and so on to the R12, R13, R14 and R15 group as RQ12. The two most significant bits of a four bit field in an instruction designate the desired quad register and the remaining two bits should be zero. Figure 1 depicts the AmZ8001 register structure and Figure 2 shows the AmZ8002 register structure. Table 1 is a summary of register addressing in byte mode and Table 2 is a summary for 16-bit, 32-bit and 64-bit modes.

FIGURE 1 AMZ8001 REGISTERS

| Des | ignati | 8-Bit<br>Mode |   |      |

|-----|--------|---------------|---|------|

| ø   | Ø      | RHØ           |   |      |

| ø   | ø      | ø             | 1 | RH 1 |

| ø   | ø      | 1             | ø | RH2  |

| ø   | ø      | 1             | 1 | RH3  |

| ø   | 1      | ø             | ø | RH4  |

| ø   | 1      | ø             | 1 | RH5  |

| ø   | 1      | 1             | ø | RH6  |

| ø   | 1      | 1             | 1 | RH7  |

| 1   | ø      | ø             | ø | RLØ  |

| 1   | ø      | ø             | 1 | RL1  |

| 1   | ø      | 1             | ø | RL2  |

| 1   | ø      | 1             | 1 | RL3  |

| 1   | 1      | ø             | ø | RL4  |

| 1   | 1      | ø             | 1 | RL5  |

| 1   | 1      | 1             | ø | RL6  |

| 1   | 1      | 1             | 1 | RL7  |

Table 1. Byte Mode Register Addressing

| 64-BIT<br>Mode | 32-BIT<br>Mode | 16-BIT<br>Mode | Designation Field |     |   |   |  |

|----------------|----------------|----------------|-------------------|-----|---|---|--|

|                | RRO            | RO             | 0                 | 0   | 0 | 0 |  |

| RQO            | ĸĸu            | Rl             | 1                 | 0   | 0 | 0 |  |

| RUU            | RR2            | R2             | 0                 | 1   | 0 | 0 |  |

|                | KKZ            | R3             | 1                 | 1   | 0 |   |  |

| RQ4            | RR4            | R4             | 0                 | 0   | 1 | 0 |  |

|                | KK4            | R5             | ]                 | 0   | 1 | 0 |  |

|                | rr6            | R6             | 0                 | 1   | 1 | 0 |  |

|                | KKO            | R7             | 1                 | 1   | 1 | 0 |  |

|                | rr8            | R8             | 0                 | 0   | 0 | 1 |  |

| RQ <b>8</b>    | KKO            | R9             | 1                 | 0   | 0 | 1 |  |

| RUO            | RR10           | R10            | 0                 | 1   | 0 | 1 |  |

|                | KKIU           | R11            | 1                 | 1   | 0 | 1 |  |

|                | RR12           | R12            | 0                 | 0   | 1 | 1 |  |

| 0.12           | KK I Z         | R13            | 1                 | 0   | 1 | 1 |  |

| RQ12           | RR 14          | R14            | 0                 | 1   | 1 | 1 |  |

|                | KK 14          | R15            | 1                 | 1 1 |   | 1 |  |

Table 2. Register Addressing

The registers may contain operands or address information. When a register pair contains a long-word operand, the even numbered register of the pair holds the most significant 16-bit while the odd numbered register of the pair holds the least significant 16-bits. When a register quad is specified for 64-bit data, the first register holds the most significant 16-bits and the last register of the quad holds the least significant 16-bits. For example, RØ is the first register and R3 is the last register of the quad RQØ, R4 is the first and R7 is the last of the quad RQ4 and so on.

In AmZ8001 a register pair will be needed to specify the required 23-bit address. The 7-bit segment number is always specified in the even numbered register and 16-bit offset is specified in the odd numbered register of the pair.

### Stack Pointer

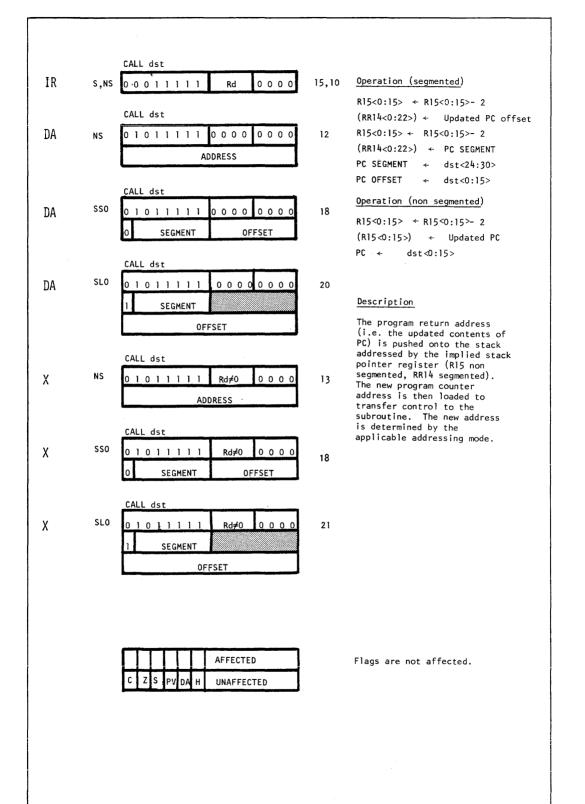

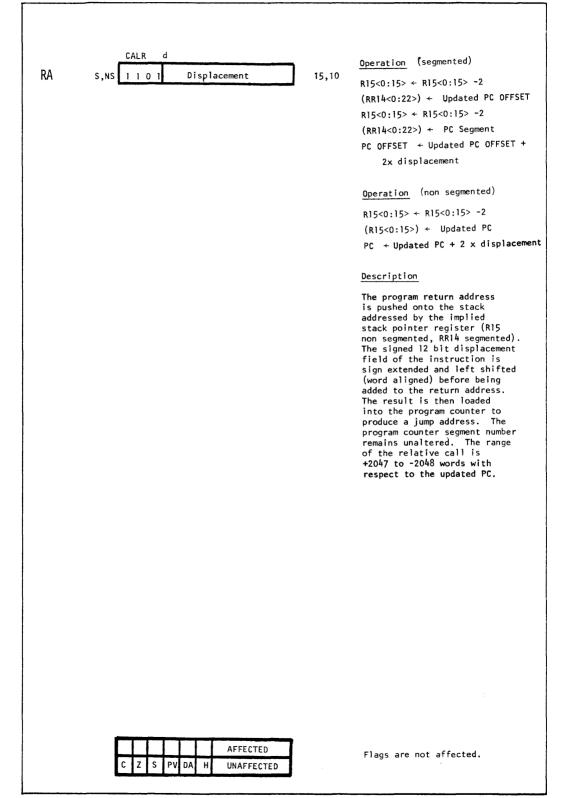

The architecture allows the creation and maintenance of stacks in the memory. Any of the general purpose registers (except RRØ in AmZ8001 and RØ in AmZ8002) can be designated as a stack pointer in the PUSH and POP instructions. However, for the CALL and RETURN instructions, specific general purpose registers are implied as stack pointers.

In the AmZ8001, the general purpose register pair RR14 is the implied stack pointer. The seven bit segment number is contained in R14 and R15 contains the 16-bit offset value. The segment number together with the offset value forms a 23-bit segmented address. For the AmZ8002, the general purpose register R15 is the implied stack pointer and contains the required 16-bit address. It should be remembered that the implied stack pointers are still general purpose registers. In other words, certain implied general purpose registers are given stack pointer attributes in addition to their normal general purpose characteristics.

The processors can operate in one of two selectable modes: SYSTEM and NORMAL. The SYSTEM mode is sometimes called supervisor or privileged

mode and the NORMAL mode is sometimes known as problem or non-privileged mode. Separation of system and normal stacks is a desirable in order to facilitate sophisticated system designs. This is accomplished by providing SYSTEM STACK POINTER in addition to NORMAL STACK POINTER.

In the AmZ8001 two additional registers R14<sup>1</sup> and R15<sup>1</sup> are provided corresponding to R14 and R15. When AmZ8001 is operating in the SYSTEM mode, R14<sup>1</sup> will be used as the general purpose register whenever R14 is specified. Similarly R15<sup>1</sup> will be used instead of R15 in the SYSTEM mode for both AmZ8001 and AmZ8002. Thus, the register pair R14<sup>1</sup>, R15<sup>1</sup> (identified as RR14<sup>1</sup>) is the implied SYSTEM STACK POINTER for the AmZ8001 and R15<sup>1</sup> is the implied SYSTEM mode, instructions are provided such that these two general purpose registers can be accessed without actually switching the operating mode. The SYSTEM STACK POINTER will be used during program interruptions to save the pre-interrupt status irrespective of the selected operating mode.

## Program Counter

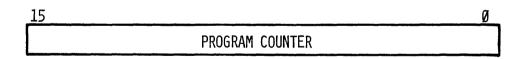

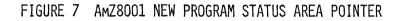

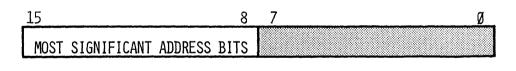

The CPU operation is controlled by instructions fetched from the memory. The address for instruction fetch is supplied by the PROGRAM COUNTER (PC). Figure 3 shows the AmZ8001 program counter. It consists of two words, seven bits of the first word are used to specify the segment number and 16-bit offset is specified in the second word. The segment number designates one of 128 segments and the 16-bit offset designates a memory location in that segment. The instructions are always word aligned and the PC is incremented by multiples of 2 to fetch instructions from sequential memory locations. It should be noted that incrementing the offset cannot affect the segment number. In other words, carry from offset will not propagate into the segment number of the PC; instead the offset counter will simply wrap around. Figure 4 shows the AmZ8002 PC format consisting of 16 bits. Except for the absence of the segment number portion PC operation of the AmZ8001 and AmZ8002 are identical. When reset, the AmZ8001 PC SEG will be automatically loaded from memory address 4 and PC OFFSET will be automatically loaded from address 6. AmZ8002 PC will be automatically loaded from memory address 2 upon reset. All these memory addresses are located in segment Ø.

| 15 | Ø        |

|----|----------|

| PC | C OFFSET |

|    |          |

FIGURE 3 AMZ8001 PROGRAM COUNTER

FIGURE 4 AMZ8002 PROGRAM COUNTER

### Processor Status Information

The contents of the program counter and FLAG AND CONTROL WORD (FCW) are collectively called the Processor Status Information. The FCW of the AmZ8001 is shown in Figure 5. The most significant byte contains five control bits - Segmentation Enable (SEG), Normal/System (N/S), Stop Enable (SE), Vectored Interrupt Enable (VIE) and Non-Vectored Interrupt Enable (NVIE). The least significant byte contains six CPU flag bits -Carry (C), Zero (Z), Sign (S), Parity/Overflow (P/V), Decimal Adjust (DA), and Half Carry (H). The remaining bits are reserved for future expansion. The FCW for the AmZ8002 is shown in Figure 6. It is identical to Figure 5 except that the SEG bit is not available in the AmZ8002.

The flag portion of the FCW contains processor flags necessary to characterize the results from data manipulation operations. The half carry (H) flag is affected during arithmetic operations involving byte operands. A byte consists of two 4-bit digits. The H flag is used to indicate occurrence of a carry from the least significant digit into the most significant digit.

The Decimal Adjust (DA) flag is provided to facilitate conversion operations required to accomplish BCD arithmetic. The Parity/Overflow (P/V) is used to indicate parity of the result following certain non-arithmetic operations and occurrence of overflow condition following arithmetic operations. If both operands participating in an add operation have the same sign and the result has the opposite sign, an overflow has occurred. Subtraction is addition with the 2's complement of the subtrahend.

The CPU uses two's complement representation of numbers and hence the most significant bit is considered to be the sign bit. A "one" in the most significant bit position represents a negative number. The Sign reflects the state of the most significant bit position of a result after an arithmetic or logic instruction.

The Zero (Z) flag when set to 1 indicates that all bits (including sign) of a result are zero. In general, this flag is affected for both arithmetic and logic instructions.

#### 12 11 10 9 8 15 14 13 7 5 4 6 3 SEG SE S S/N VIENVIE С 7 Η P/V DA

FIGURE 5 AMZ8001 FLAG AND CONTROL WORD

#### 15 14 13 12 11 10 9 8 7 6 5 3 2 4 1 Ø С N/S Ζ S SE VIE NVIE P/V DA Η

## FIGURE 6 AMZ8002 FLAG AND CONTROL WORD

The Carry (C) flag is used to indicate occurrence of a carry from the most significant bit position after an arithmetic instruction. By convention, bits are numbered starting from zero, hence bit 7 (eighth bit) is the most significant for bytes, bit 15 (sixteenth bit) is the most significant for words and bit 31 (thirty-second bit) is the most significant for long words.

The CPU can handle three types of external interrupts: non-maskable, nonvectored and vectored. The NVIE and VIE bits control the latter two. The non-maskable interrupt cannot be disabled in the CPU. On the other hand, vectored and non-vectored interrupts can be disabled by clearing the corresponding FCW bit to  $\emptyset$ . In other words, an interrupt enable bit must be 1 before the corresponding external interrupt signal will be recognized. The non-maskable interrupt has the highest priority while vectored interrupt has the next lower and non-vectored has the lowest priority.

The Stop Enable (SE) bit is provided to facilitate stopping the processor after executing a single instruction. There is an external input to the processor that participates in this operation. When the SE bit is 1, the external input signal will be honored.

The N/S bit determines the operating mode; logical "one" indicates SYSTEM and logical "zero" indicates NORMAL. In the System mode, all instructions are valid and are executed. In the Normal mode, only those instructions are valid that cannot be used to affect the system integrity. The instructions that are not valid in the Normal mode are called System or Privileged instructions. The System instructions include those that inspect or modify the control bits of the FCW, those that participate in interprocessor communication and those that perform input/output operations. If a system instruction is encountered while operating in the Normal mode, the instruction execution is suppressed and a trap will be generated to cause program interruption.

The AmZ8001 deals with 23-bit segmented addresses whereas AmZ8002 uses 16-bit non-segmented addressing. The SEG bit in the FCW allows the AmZ8001 to operate in the non-segmented mode. When this bit is 1, the CPU is operating in the segmented mode. This bit will always be zero in the AmZ8002.

The most significant byte of the FCW contains the control bits. Hence any instruction that operates on these bits is a privileged instruction. Significance of the FCW bits is summarized in Table 3.

When reset, the FCW in AmZ8001 will be automatically loaded from memory location 2 (segment  $\emptyset$ ) and the FCW in AmZ8002 will be automatically loaded from location  $\emptyset$ .

## New Program Status Area Pointer

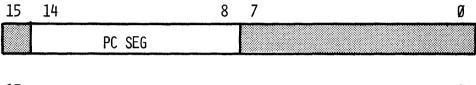

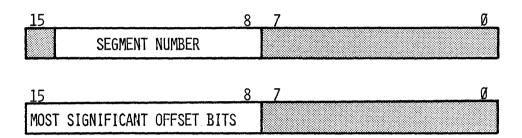

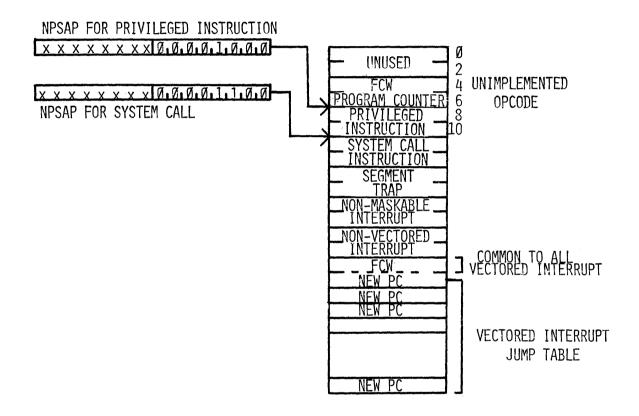

When a program interruption occurs, the CPU automatically saves the program status in the system stack. The program status consists of the processor status information and information relating to the reason for interruption called Identifier. After storing the pre-interrupt program status, new program status will be loaded into the FCW and PC. This new program status is obtained from pre-determined locations in the memory called New Program Status Area designated by the NEW PROGRAM STATUS AREA POINTER (NPSAP). The NPSAP in AmZ8001 is shown in Figure 7. It consists of two 8-bit registers, one for the 7-bit segment number and the other for the most significant eight bits of the offset. On the other hand, only one 8-bit register is used in the AmZ8002 as shown in Figure 8. This register specifies the most significant 8-bits of the 16-bit address. Access to the NPSAP is by using the LDCTL instruction.

## Refresh Counter

Both AmZ8001 and AmZ8002 contain a refresh counter to facilitate dynamic memory system implementations. The refresh counter is illustrated in Figure 9 consisting of a 9-bit binary ROW COUNTER and 6-bit binary RATE COUNTER and a REFRESH ENABLE (RE) bit. The RATE COUNTER is a programmable modulo 64 counter clocked at 25% of the frequency of the clock driving the CPU. The ROW COUNTER is clocked whenever the RATE COUNTER overflows. The

## FIGURE 8 AMZ8002 NEW PROGRAM STATUS AREA POINTER

| 15 | 14 |              | 9 | 8 |             | Ø |

|----|----|--------------|---|---|-------------|---|

| RE |    | RATE COUNTER |   |   | ROW COUNTER |   |

The automatic refresh feature can be disabled by loading a zero into REFRESH ENABLE bit. When the CPU is reset for initialization, this bit is set to "1" i.e. refresh is enabled. Access to the refresh counter is made using the LDCTL instruction.

## Addressing Modes

Operands needed to execute an instruction are designated by register addresses, memory addresses or 1/0 addresses. The addressing mode of a given instruction not only designates the relevant address space but also defines the method to be used in computing the operand address. Addressing modes are either explicitly specified or implied by the instruction. Eight explicit addressing modes are provided: Register (R), Indirect Register (IR), Direct Address (DA), Immediate (IM), Indexed (X), Base Address (BA), Base Indexed (BX) and Relative Address (RA). Autoincrement and Autodecrement are the two implied addressing modes in block and string manipulation instructions.

The following is a detailed explanation of explicit addressing modes.

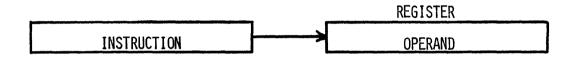

Register (R) Mode: The operand used by the instruction is located in a general purpose register as shown in Figure 10. The instruction specifies the length of the operand (byte, word or long word) and a 4-bit field in the instruction designates the intended register.

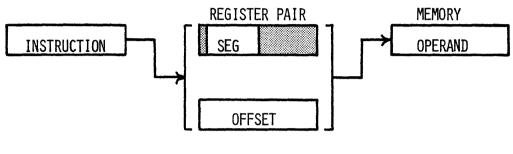

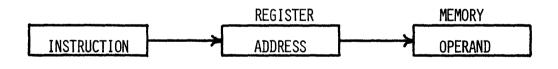

Indirect Register (IR): The instruction designates a general purpose register; contents of the designated register are not the operand but address of the operand. The AmZ8001 deals with 23-bit segmented addresses and hence a register pair is designated by the instruction. The first register contains the 7-bit segment number and the second register contains the 16-bit offset as shown in Figure 11. Any general purpose register pair except RRØ can be designated for this addressing mode. The AmZ8002 requires only 16-bit addresses as shown in Figure 12 and hence any general purpose register except RØ can be designated for IR addressing mode.

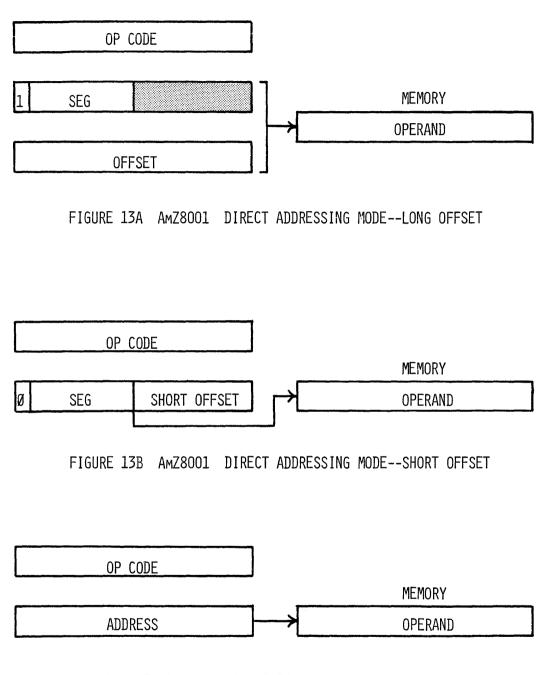

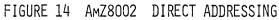

Direct Address (DA): The instruction itself explicitly specifies an address and the operand used by the instruction is located at that address. In AmZ8001 direct addresses are specified in one of two formats - long offset and short offset. For the long offset, the memory word immediately

## FIGURE 10 AMZ8001 AND AMZ8002 REGISTER ADDRESSING MODE

FIGURE 11 AMZ8001 INDIRECT REGISTER ADDRESSING MODE

FIGURE 12 AMZ8002 INDIRECT REGISTER ADDRESSING MODE

following the instruction opcode word contains the 7-bit segment number and the memory word immediately following the segment number word is the 16-bit offset as shown in Figure 13A. For the shoft offset, the memory word immediately following the instruction opcode word contains both 7-bit segment number and 8-bit offset as shown in Figure 13B. In AmZ8002, the memory word immediately following the instruction opcode word contains the 16-bit address as shown in Figure 14.

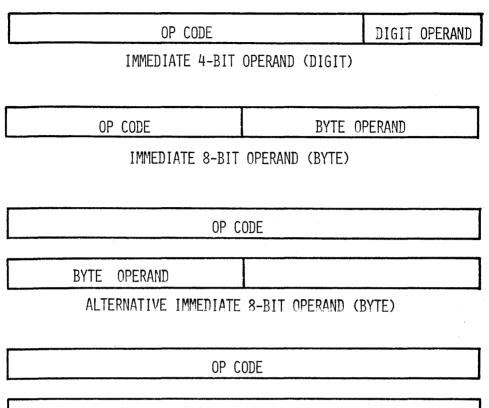

Immediate (IM): The instruction itself contains the operand as shown in Figure 15. In general, the memory word immediately following the instruction opcode word contains the immediate operand. In case of 32-bit immediate operand, two memory words immediately following the instruction opcode word are used.

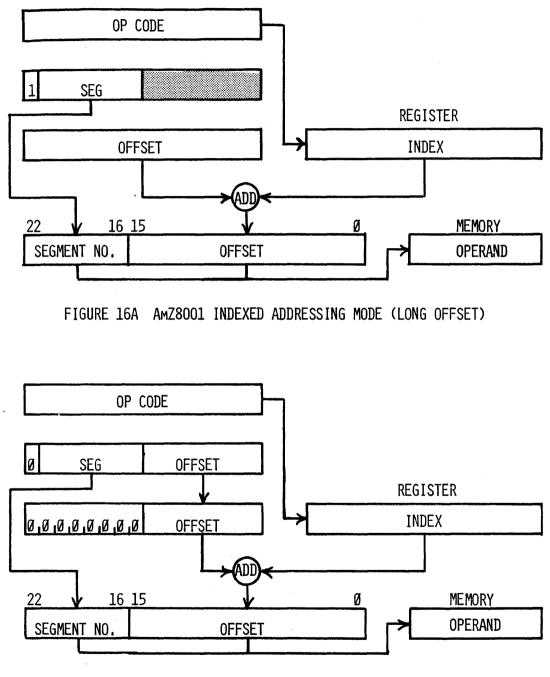

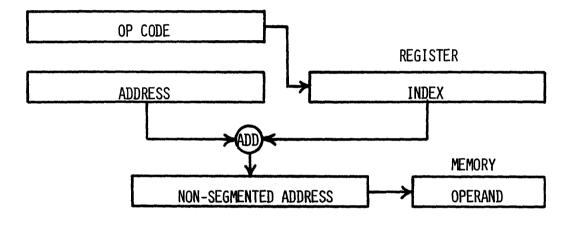

Indexed (X): The instruction designates a 16-bit general purpose register as the index register. Any general purpose register except RØ can be used as the index register. The instruction also specifies an address as in the direct address mode. In the AmZ8001, the 16-bit contents of the designated index register are added to the 16-bit offset value specified in the instruction. Both index and offset are treated as 16-bit unsigned integers and any carry from the most significant bit position during this addition is ignored. The resulting 16-bit sum together with the 7-bit segment number specified in the instruction is used as 23-bit segmented address as depicted in Figure 16A. The operand will be located at this address in memory. If short offset is used in the AmZ8001 for indexed addressing mode, the memory word immediately following the instruction opcode word contains both a 7-bit segment number and an 8-bit offset as shown in Figure 16B.

A 16-bit unsigned integer is formed whose least significant byte is the 8bit offset specified and most significant byte is zero. The 16-bit word thus formed is added to the 16-bit unsigned integer contained in the designated general purpose register. Any carry from the most significant bit position during this addition is ignored. The 16 bits resulting from this addition together with the 7-bit segment number specified is the 23-bit address. The operand will be located in the memory at this address.

WORD OPERAND

IMMEDIATE 16-BIT OPERAND (WORD)

OP CODE

MOST SIGNIFICANT 16 BITS OF OPERAND

LEAST SIGNIFICANT 16 BITS OF OPERAND

IMMEDIATE 32-BIT OPERAND (LONG WORD)

FIGURE 15 AMZ8001 AND AMZ8002 IMMEDIATE ADDRESSING MODE

FIGURE 16B AMZ8001 INDEXED ADDRESSING MODE (SHORT OFFSET)

In AmZ8002, the memory word immediately following the instruction opcode word contains a 16-bit address as shown in Figure 17. This unsigned integer is added to the 16-bit unsigned integer located in the designated index register. The carry from the most significant bit position during this addition is ignored. The resulting 16-bit address is where the operand is located in the memory.

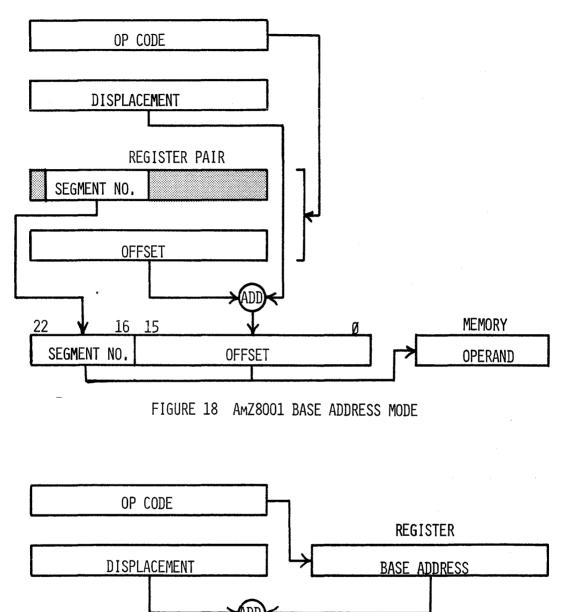

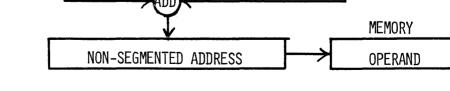

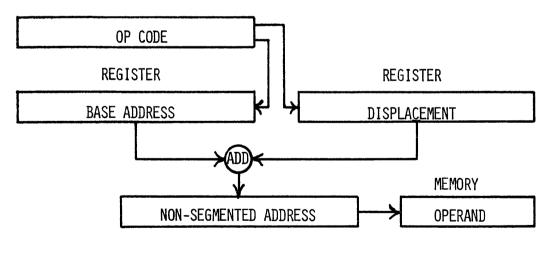

Base Address (BA): The instruction designates a general purpose register as the base address register. In case of AmZ8001, the instruction designates a register pair such that the 7-bit segment number is contained in one register and 16-bit offset is contained in the other as shown in Figure 18. In case of AmZ8002, the designated base address register contains 16-bit address as shown in Figure 19. Any general purpose register except RØ or register pair except RRØ can be designated as the base address register. The memory word immediately following the instruction opcode word contains a 16-bit displacement. Both displacement and base address are treated as unsigned binary integers. The 16-bit displacement is added to the 16-bit base address (16-bit offset is AmZ8001) and carry occurring from the most significant position during this addition is ignored. The resulting 16-bit value (together with the segment number of the base address in AmZ8001) is the address of the operand in memory.

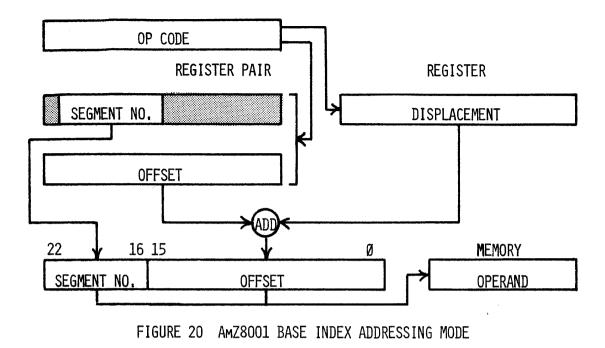

Base Indexed (BX): The instruction designates a general purpose register (register pair in AmZ8001) as the base address register. The instruction also designates a 16-bit general purpose register as displacement. Any general purpose register except RØ (AmZ8002) or any register pair except RRØ (AmZ8001) can be used as the base address register. Similarly any general purpose register except RØ can be used as the displacement register. Both base address and displacement are unsigned integers.

The 16-bit displacement is added to the base address (or offset of the base address in AmZ8001) and carry from the most significant bit position during this addition is ignored. The 16-bit result (together with base address segment number) is the address of the operand in memory. Figure 20 and Figure 21 illustrate this addressing mode for AmZ8001 and AmZ8002.

FIGURE 17 AMZ8002 INDEXED ADDRESSING MODE

FIGURE 19 AMZ8002 BASE ADDRESS MODE

FIGURE 21 AMZ8002 BASE INDEX ADDRESSING MODE

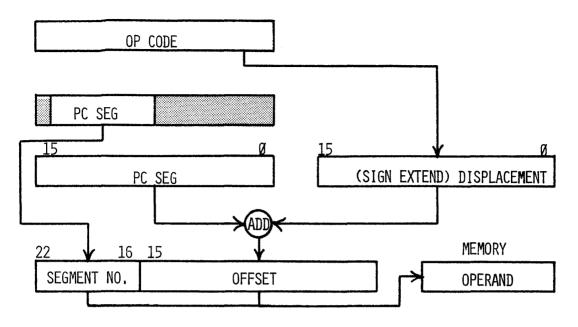

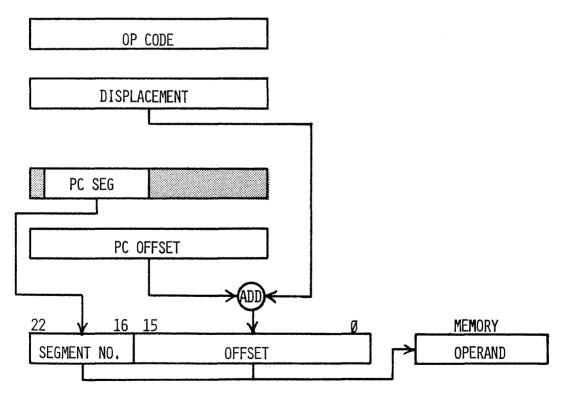

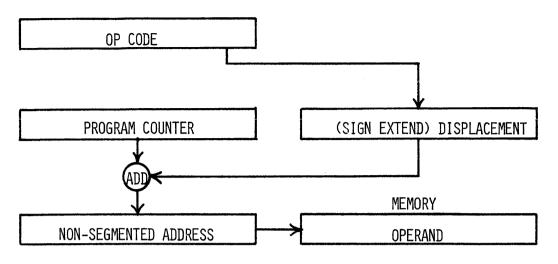

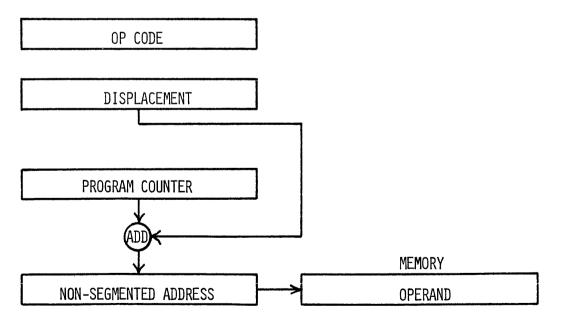

Relative Address (RA): The instruction itself contains a displacement. This displacement is a signed integer using two's complement notation. The number of bits allocated to represent the displacement depend on the instruction where relative addressing mode is available. The displacement is sign extended appropriately to obtain a signed 16-bit displacement. The sign extended displacement is added to the 16-bit program counter (PC OFFSET in AmZ8001). Carry from the most signifi= cant bit position during this addition is ignored. As soon as the instruction using the relative address mode is fetched, the PC will be updated. Hence, updated PC value (i.e. address of the following instruction) will be used for address calculation.

The 16-bit value obtained by adding the PC and displacement (together with the segment number in AmZ8001) is the address of the operand in memory. Figure 22 and Figure 23 illustrate the relative addressing mode.

Autoincrement and Autodecrement: These two implied addressing modes are only used in string manipulating instructions. These addressing modes are a variation of the IR addressing mode. The instruction designates a general purpose register (or a register pair in AmZ8001) whose contents are used as the address. After fetching the operand, the contents of the register are incremented or decremented depending on Autoincrement or Autodecrement. In case of AmZ8001, only the register containing the offset is affected and any carry resulting from this operation is ignored. For byte operations incrementing or decrementing by 1 occurs. For word operations incrementing or decrementing by 2 takes place.

FIGURE 22A AMZ8001 RELATIVE ADDRESSING MODE -- (ONE WORD INSTRUCTION)

FIGURE 22B AMZ8001 RELATIVE ADDRESSING MODE -- (TWO WORD INSTRUCTION)

FIGURE 23A AMZ8002 RELATIVE ADDRESSING MODE--(ONE WORD INSTRUCTION)

FIGURE 23B AMZ8002 RELATIVE ADDRESSING MODE -- (TWO WORD INSTRUCTION)

## Operand Addressing

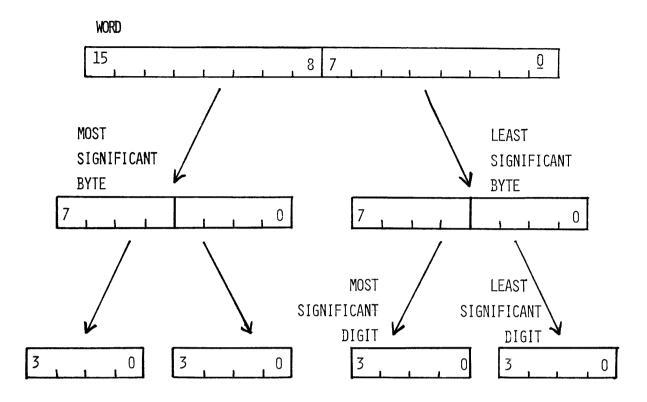

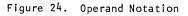

Seven types of operands are handled by the instructions - bits, digits (4-bits), bytes (8-bits), words (16-bits), long words (32-bits), byte strings and word strings. In general, operands may be contained in a general purpose register or located in memory. However, string operands must be located in memory only. The elements of a string reside in consecutive memory locations.

Figure 24 illustrates the conventions used in relating one operand type to another. A byte consists of two digits:; two bytes make a word and two words make a long word. The left most element whether bit, digit or byte is always the most significant. Bits of an operand are numbered from right to left starting with zero for the least significant bit. The bit operand located in a general purpose register is addressed by the designation of the byte register containing the desired bit and specifying the bit number in that byte. Bit operands can also be addressed by designating a 16-bit general purpose register holding the word that contains the desired bit and the bit number in that word. Digits are always addressed by designating the byte register containing the desired digit. Word and long word operands located in registers are addressed by the register or register pair designation. When a long word is specified using a register pair, the even numbered register of the pair contains the least significant 16-bits and the odd numbered register of the pair contains the least significant 16 bits.

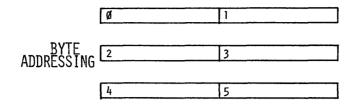

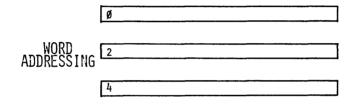

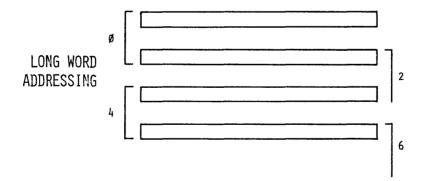

## Memory Addressing

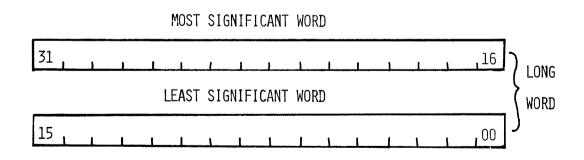

Memory address space is viewed as a chain of consecutively numbered (in ascending order) bytes as shown in Figure 25. Also note that the numbering starts with zero. The number of each byte is its address. Thus, the byte is the basic addressable element in memory. A word in memory spans two byte addresses. The most significant byte of a word must always be an even address and the least significant byte is the immediately following odd address. This arrangement is called "word aligned". Thus, words are addressed by the address of the most significant byte

FIGURE 25. MEMORY ADDRESSING

or even address. A long word in memory spans two words or four bytes. The most significant 16-bits are contained at a word address and the least significant 16-bits are contained at the immediately following word. For example a long word is contained in memory addresses  $\emptyset$  and 2, then location  $\emptyset$  contains the most significant 16-bits and location 2 contains the least significant 16 bits. Long word operands in memory are addressed by specifying the address of the most significant byte of the most significant word. For example, address  $\emptyset$  is used for a long word operand located at locations  $\emptyset$  and 2. Instructions are always addressed as words and hence instructions in memory must be word aligned.

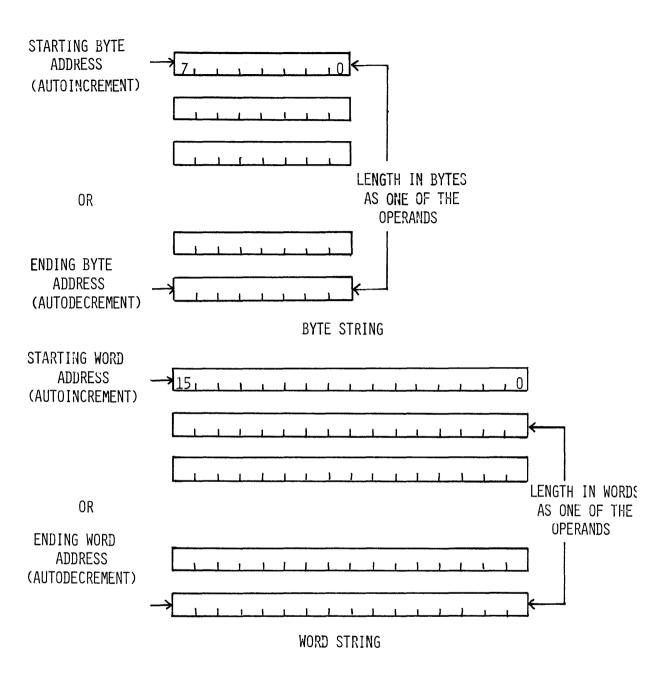

The CPU can handle both byte and word string operands. Two parameters are needed to specify a string - starting address (address of the first element) and the length of the string expressed in terms of the number of elements in the string as depicted in Figure 26. For example, a word string starting at address 100 and 25 words long will be characterized by the starting address 100 and length 25. Similarly a byte string which is 15 bytes long and starts at address 157 will be characterized by the starting address 157 and its length 15. By specifying Autoincrement addressing mode in a string manipulating instruction, successive elements of strings specified in the above manner can be accessed for processing. String operands can also be specified by the ending address (address of the last element) instead of the starting address and the length expressed in terms of number of elements in the string. Autodecrement addressing mode is used to access successive elements of the string in this case. It should be noted that when dealing with byte strings, there are no restrictions on whether the starting and ending addresses are odd or even. However, because of the word alignment requirement, word strings can have only even addresses.

33

Figure 26. String Operands

#### Interrupts and Traps

Program interruptions are divided into two groups - interrupts and traps. In general, interrupt is an external asynchronous event needing the CPU's attention. Trap usually is a synchronous event resulting from the execution of certain instructions under some specified condition. Also an interrupt may be disabled in the CPU by an appropriate control bit in the FCW; traps cannot be disabled. Procedures followed by the CPU are essentially the same for interrupts and traps.

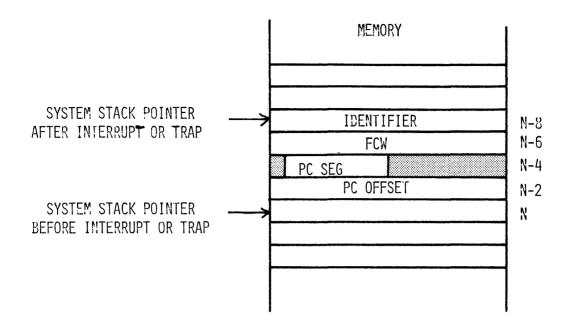

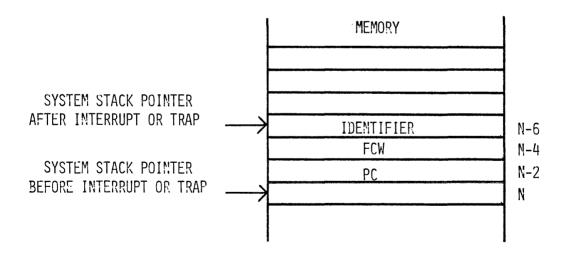

When an interruption occurs, the current program status information is automatically pushed on the system stack as shown in Figure 27. As discussed before, program status consists of Processor Status (PC and FCW) and a 16-bit word called Identifier. The Identifier contains information relating to the reason for this interruption.

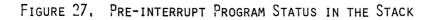

There are three interrupts listed in order of decreasing priority: non-maskable, vectored and non-vectored. There are four traps: system call, unimplemented opcode, privileged instruction in normal mode and segmentation error. For all three interrupts the Identifier is a 16-bit entity supplied by the interrupting device. The Identifier in case of traps (except segmentation error) is the first word of the instruction that caused the trap. This word always contains the instruction opcode.

The segmentation error actually results from several exception conditions that could occur when the Memory Management Unit (AmZ8010) is used in an AmZ8001 system. Detailed discussion of the Memory Management unit is beyond the scope of this document. It is sufficient for the current discussion to know that the Identifier for the segmentation error trap will be supplied by the Memory Management circuitry.

After saving the program status in the system stack, new processor status is automatically obtained from a predetermined area in memory called New Program Status Area. The New Program Status Area Pointer (NPSAP) specifies the area in memory where the New Program Status Area is located. In AmZ8001,

35

AMZ8001 PROGRAM STATUS-SAVING SEQUENCE

172

AmZ8002 PROGRAM STATUS-SAVING SEQUENCE

NPSAP consists of a 7-bit segment number and most significant eight bits of the offset. In AmZ8002 this pointer contains the most significant eight bits of the address. The CPU utilizes a predetermined value in the least significant eight bits of the NPSAP offset. Figure 28 and Figure 29 show the New Program Status Area format. For example, in AmZ8001, the first four locations are used for segmentation error, next four locations for system call trap and so on.

The format of storage for all interruptions is the same. In AmZ8001, New Program Status is contained in four consecutive memory locations. These are in ascending order, Reserved Word, New FCW, new PC SEG and PC OFFSET. The first location for every new processor status area of AmZ8001 is reserved for future CPU expansion and should not be used in the interest of upward software compatibility. In the AmZ8002, only two memory locations are needed for the new processor status information. Two consecutive memory locations in ascending address are used for new FCW and new PC.

FIGRE 28, AMZ8001 New Program Status Area

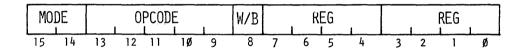

#### Instruction Format

The CPU instructions are one to five words long depending on the type of instruction and addressing mode. Instructions are located in memory and must be word aligned. The first word of an instruction always contains the opcode. Depending on the addressing mode, one or more words will follow the opcode word of an instruction. Figure 30 illustrates the general opcode word format. Some instructions contain fields that differ from the generalized format shown. All such variations can be ascertained by referring to the individual instruction descriptions found in later sections of this document. In Figure 30, the Mode Field (bit 14 and bit 15), together with bit 12 and bit 13 and bits 4, 5, y and 7 determine the applicable addressing mode. Bit 8 of the opcode word specified word or byte operand whenever applicable. Table 3 is a summary of addressing mode decoding. Bits 4, 5, 6 and 7 normally designate a general purpose register. Note that when designating a register pair, bit 4 must be zero and only 5, 6 and 7 are used.

From Table 3 it can be seen that for Register Mode of addressing there are no restrictions on the values of bits 4, 5, 6 and 7. Only the Mode field is needed to specify this addressing mode. This allows designating any general purpose register. However, for IM, RA and DA addressing modes, bits 4, 5, 6 and 7 must all be zero. For these addressing modes zeros in bits 4, 5, 6 and 7 are not interpreted as general purpose register number zero. Similarly, for IR, BA, X and BX addressing modes, bits 4, 5, 6 and 7 cannot be zero. In other words, general purpose register number zero cannot be used in these addressing modes. It should be emphasized that if a register pair is needed for these addressing modes, bit 4 is always zero and non-zero comment applies to bits 5, 6 and 7.

FIGURE 30. GENERAL INSTRUCTION FORMAT

| MODE<br>BITS<br>15, 14 | OP CODE<br>BITS<br>13, 12 | REG<br>BITS<br>7,6,5,4 | ADDRESSING<br>MODE |

|------------------------|---------------------------|------------------------|--------------------|

| 10                     | xx                        | XXXX                   | R                  |

| 0 0                    | Any Value<br>but 1 1      | 0                      | IM                 |

| 0 0                    | Any Value<br>but 1 1      | Non-Zero               | IR                 |

| 0 0                    | 1 1                       | 0                      | RA                 |

| 0 0                    | 1 1                       | Non-Zero               | BA                 |

| 0 1                    | XX                        | 0                      | DA                 |

| 01                     | Any Value<br>but 1 1      | Non-Zero               | x                  |

| 0 1                    | 1 1                       | Non-Zero               | ΒХ                 |

Table 3. Addressing Mode Encoding

#### Input/Output

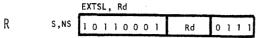

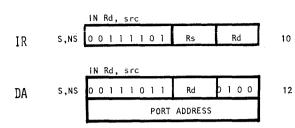

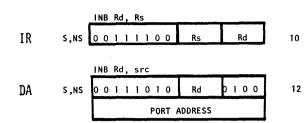

A set of input/output (1/0) instructions is provided to perform 16-bit or 8-bit transfers between the CPU and I/O devices. Input/Output devices are addressed using a 16-bit address called port address. Conceptually the port address is very similar to a memory address. Logically, however, port address space is not a part of the memory address space. Although memory and port address information is physically transmitted on the same bus lines in hardware, means are provided to distinguish memory addresses from I/O addresses using status output lines supplied by the CPU. Port address generation uses the same methodology that is used to generate operand addresses in the non-segmented CPU using IR and DA addressing modes.

Two types of 1/0 instructions are available - standard 1/0 and special 1/0. The address space used by the special 1/0 is logically separate from the standard 1/0. Special 1/0 address space can be distinguished from the standard 1/0 space using the status output lines from the CPU. A byte transferred using the standard 1/0 instruction appears on the least significant 8 bus lines in hardware. However, when transferring a byte using special 1/0 instruction, the byte will be on the most significant 8 bus lines. This is the only major difference between standard 1/0 and special 1/0 operations. Major discussion on the special 1/0 instructions is beyond the scope of this document. It should be enough to mention that special 1/0 instructions are intended for communicating with the Memory Management unit. The 1/0 instructions exist not only to transfer single words or bytes of data, but also blocks of data from contiguous memory locations.

# Condition Codes

The Condition Code (CC) is a 4-bit field in some instructions that specifies certain flag settings. The operation performed by the instruction is in most cases determined by the outcome of comparing the actual flag settings with that specified by the CC field. Instructions that specify CC field include conditional jumps, return from subroutine and block/string manipulating instructions. The Condition Code definitions consist of true and

false settings of the C, Z and P/V flags, signed and unsigned comparisons as shown in Table 4. One of the CC values specifies unconditional combination in which flag settings are ignored.

| NZ<br>Z<br>NC<br>C<br>PO<br>PE<br>PL<br>MI<br>NE<br>EQ<br>NOV<br>SIGNED C<br>GE<br>LT                                                                   | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>0MPAR                                     | Not zero<br>Zero<br>No carry<br>Carry<br>Parity odd<br>Parity even<br>Plus<br>Minus<br>Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set | $Z = \emptyset$ $Z = 1$ $C = \emptyset$ $C = 1$ $P/V = \emptyset$ $P/V = 1$ $S = \emptyset$ $S = 1$ $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$ $S \text{ XOR } P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | đ                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NC           C           PO           PE           PL           M1           NE           EQ           NOV           OV           SIGNED C           GE | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | No carry<br>Carry<br>Parity odd<br>Parity even<br>Plus<br>Minus<br>Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set                     | $C = \emptyset$ $C = 1$ $P/V = \emptyset$ $P/V = 1$ $S = \emptyset$ $S = 1$ $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | đ                                                                                                                                                 |

| C<br>PO<br>PE<br>PL<br>MI<br>NE<br>EQ<br>NOV<br>OV<br><u>SIGNED C</u><br>GE                                                                             | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>0MPAR                                     | Carry<br>Parity odd<br>Parity even<br>Plus<br>Minus<br>Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set                                 | $C = 1$ $P/V = \emptyset$ $P/V = 1$ $S = \emptyset$ $S = 1$ $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | đ                                                                                                                                                 |

| P0<br>PE<br>PL<br>M1<br>NE<br>EQ<br>NOV<br>OV<br><u>S1GNED C</u><br>GE                                                                                  | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>0MPAR                                | Parity odd<br>Parity even<br>Plus<br>Minus<br>Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set<br>SONS:<br>Greater than                 | $P/V = \emptyset$ $P/V = 1$ $S = \emptyset$ $S = 1$ $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | đ                                                                                                                                                 |

| PE<br>PL<br>MI<br>NE<br>EQ<br>NOV<br>OV<br><u>SIGNED C</u><br>GE                                                                                        | -<br>-<br>-<br>-<br>-<br>0MPAR<br>-                                                         | Parity even<br>Plus<br>Minus<br>Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set<br>SONS:<br>Greater than                               | $P/V = 1$ $S = \emptyset$ $S = 1$ $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | đ                                                                                                                                                 |

| PL<br>M1<br>NE<br>EQ<br>NOV<br>OV<br><u>S1GNED C</u><br>GE                                                                                              | -<br>-<br>-<br>-<br>-<br>0MPAR<br>-                                                         | Plus<br>Minus<br>Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set                                                                       | $S = \emptyset$ $S = 1$ $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | đ                                                                                                                                                 |

| MI<br>NE<br>EQ<br>NOV<br>OV<br><u>SIGNED C</u><br>GE                                                                                                    | -<br>-<br>-<br>0MPAR                                                                        | Minus<br>Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set<br>SONS:<br>Greater than                                                      | $S = 1$ $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | đ                                                                                                                                                 |

| NE<br>EQ<br>NOV<br>OV<br><u>SIGNED C</u><br>GE                                                                                                          | -<br>-<br>-<br>0MPAR                                                                        | Not equal<br>Equal<br>Overflow is<br>reset<br>Overflow is set<br>SONS:<br>Greater than                                                               | $Z = \emptyset$ $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | đ                                                                                                                                                 |

| EQ<br>NOV<br>OV<br><u>SIGNED C</u><br>GE                                                                                                                | -<br>-<br>0MPAR                                                                             | Equal<br>Overflow is<br>reset<br>Overflow is set<br>SONS:<br>Greater than                                                                            | $A = 1$ $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | đ                                                                                                                                                 |

| NOV<br>OV<br><u>SIGNED C</u><br>GE                                                                                                                      | -<br>-<br>0MPAR                                                                             | Overflow is<br>reset<br>Overflow is set<br>ISONS:<br>Greater than                                                                                    | $P/V = \emptyset$ $P/V = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ø                                                                                                                                                 |

| OV<br><u>Signed C</u><br>Ge                                                                                                                             | -                                                                                           | reset<br>Overflow is set<br>ISONS:<br>Greater than                                                                                                   | P/V = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ø                                                                                                                                                 |

| <u>SIGNED C</u><br>GE                                                                                                                                   | -                                                                                           | SONS:<br>Greater than                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ø                                                                                                                                                 |

| GE                                                                                                                                                      | -                                                                                           | Greater than                                                                                                                                         | S XOR P/V =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | đ                                                                                                                                                 |

|                                                                                                                                                         |                                                                                             |                                                                                                                                                      | S XOR $P/V =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | đ                                                                                                                                                 |

| LT                                                                                                                                                      | _                                                                                           |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ø                                                                                                                                                 |

|                                                                                                                                                         |                                                                                             | Less than                                                                                                                                            | S XOR $P/V =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                 |

| GT                                                                                                                                                      | -                                                                                           | Greater than                                                                                                                                         | Z OR (S XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P/V)                                                                                                                                              |

| LE ·                                                                                                                                                    | -                                                                                           | Less than or<br>equal                                                                                                                                | Z OR (S XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P/V)                                                                                                                                              |

| UNS I GNE D                                                                                                                                             | COMP                                                                                        | ARISONS:                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

| LGE                                                                                                                                                     | -                                                                                           | Logical greater<br>than or equal                                                                                                                     | C = Ø                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                   |

| LLT                                                                                                                                                     | -                                                                                           | Logical less<br>than                                                                                                                                 | C = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                   |

| LGT                                                                                                                                                     | -                                                                                           | Logical<br>greater than                                                                                                                              | $C = \emptyset AND Z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | = Ø                                                                                                                                               |

| LLE                                                                                                                                                     | -                                                                                           | Logical less<br>than or equal                                                                                                                        | C  OR  Z = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                   |

| UNCON                                                                                                                                                   | DITIO                                                                                       | NAL .                                                                                                                                                | And the second se |                                                                                                                                                   |

|                                                                                                                                                         | LGE                                                                                         | LGE -<br>LLT -<br>LGT -<br>LLE -                                                                                                                     | LLT - Logical less<br>than<br>LGT - Logical<br>greater than<br>LLE - Logical less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LGE - Logical greater C = Ø $LLT - Logical less C = 1$ $LGT - Logical C = Ø AND Z$ $greater than$ $LLE - Logical less C OR Z = 1$ $than or equal$ |

# INSTRUCTION SET

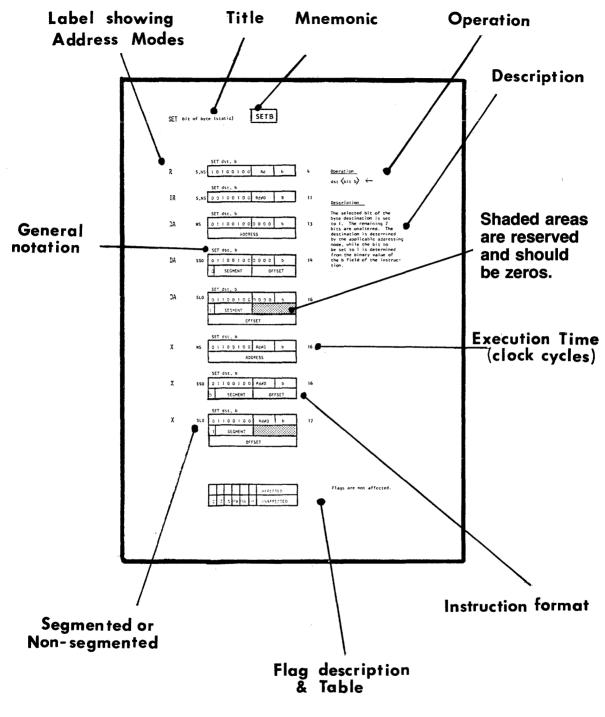

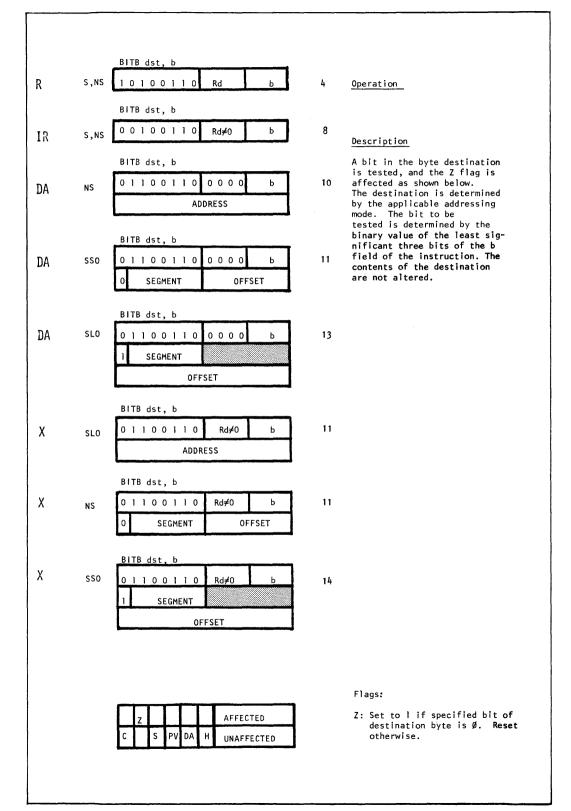

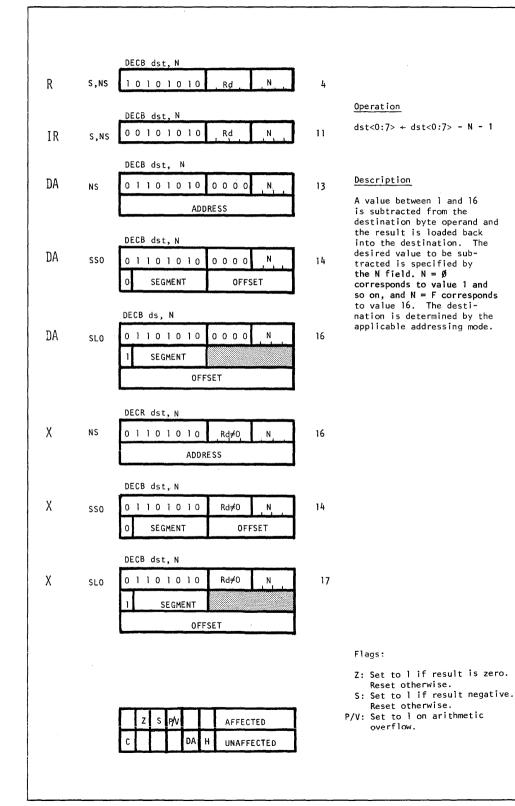

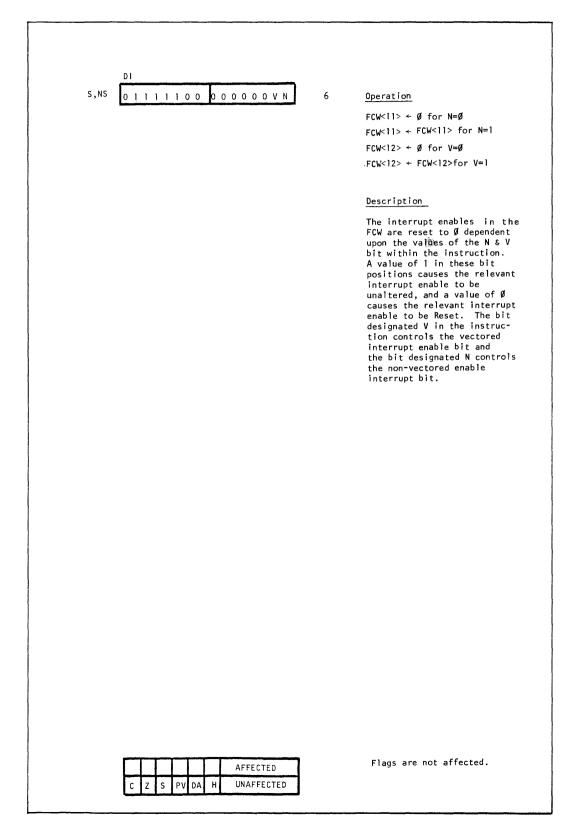

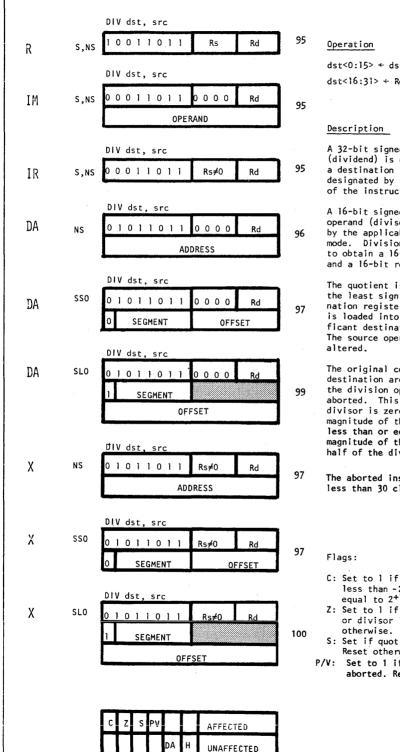

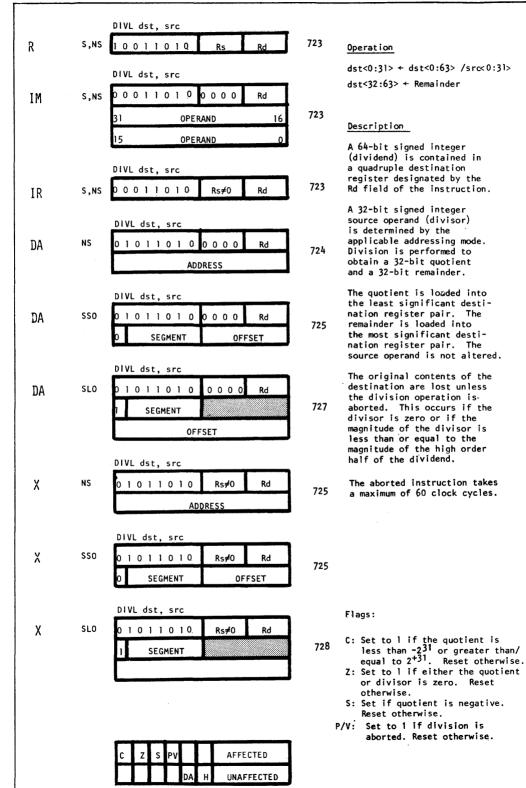

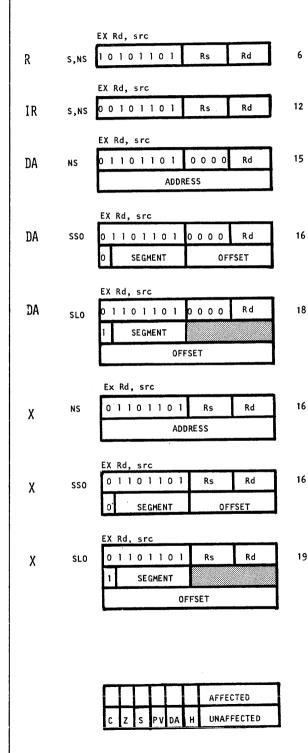

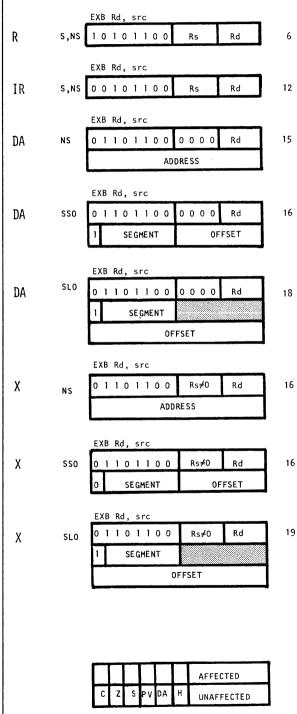

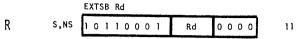

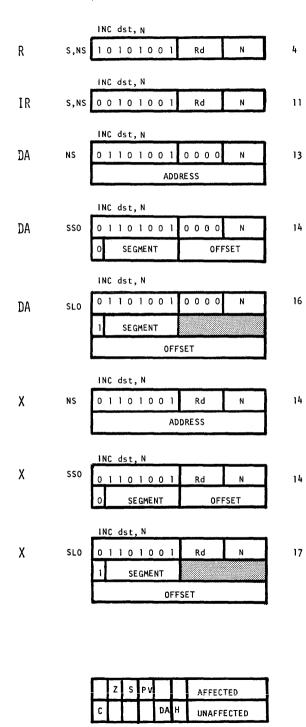

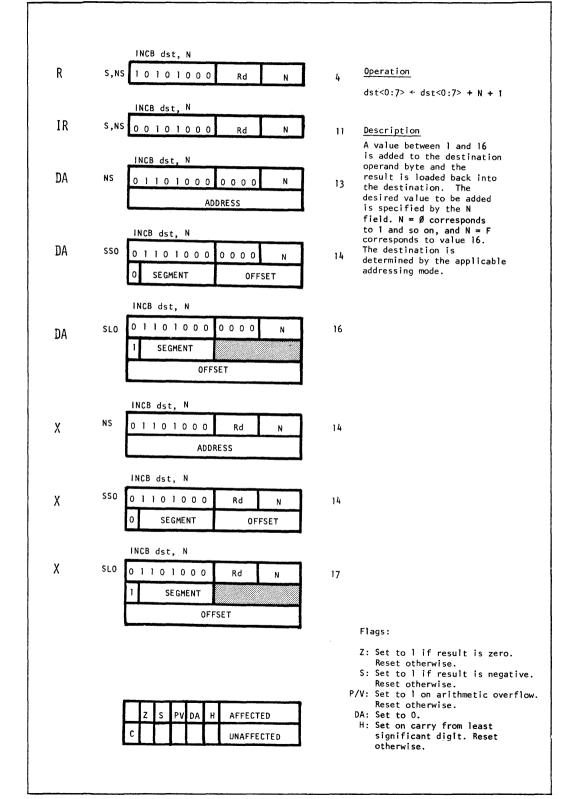

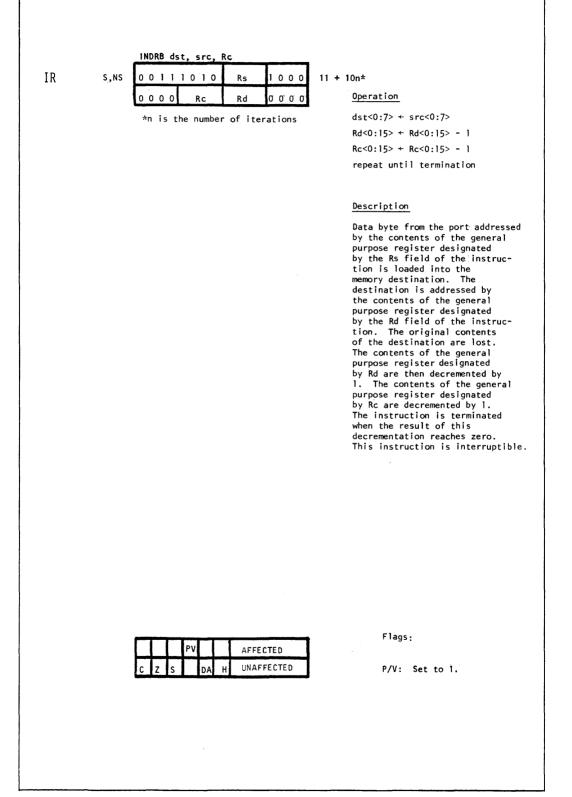

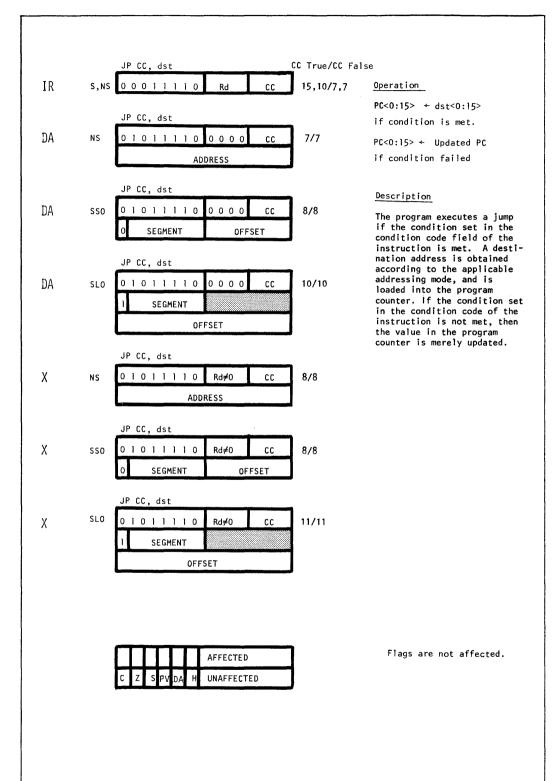

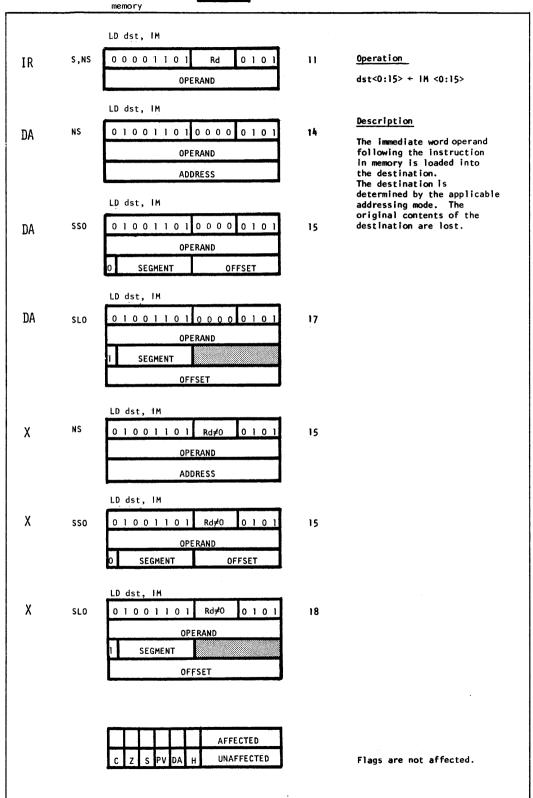

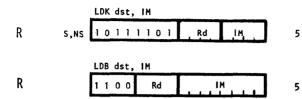

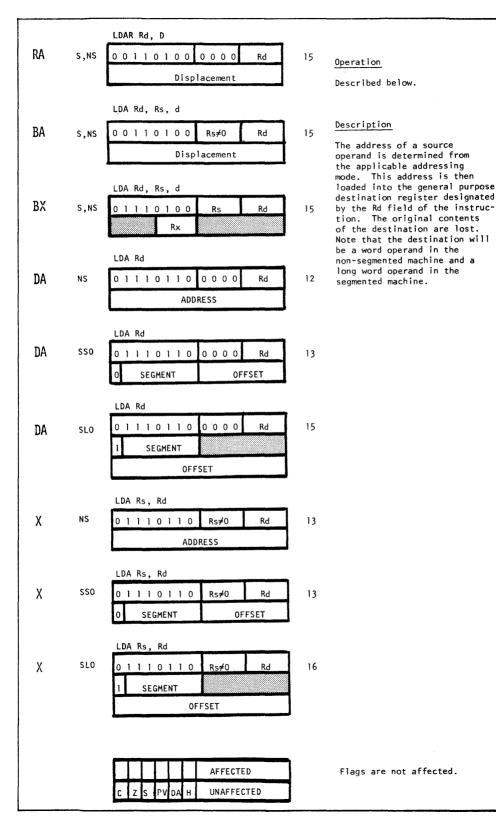

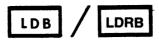

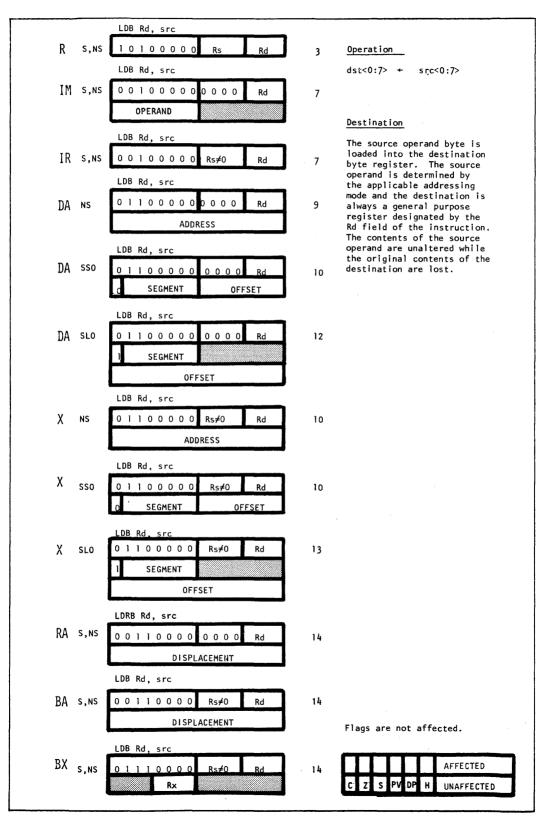

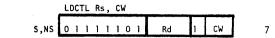

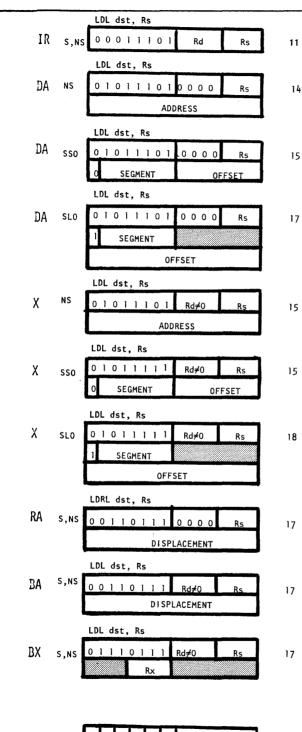

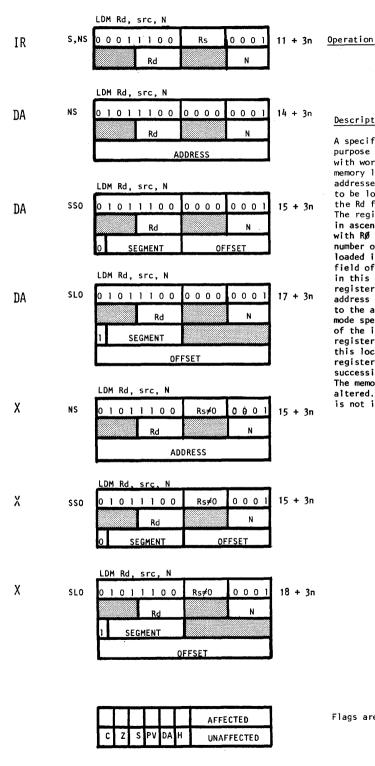

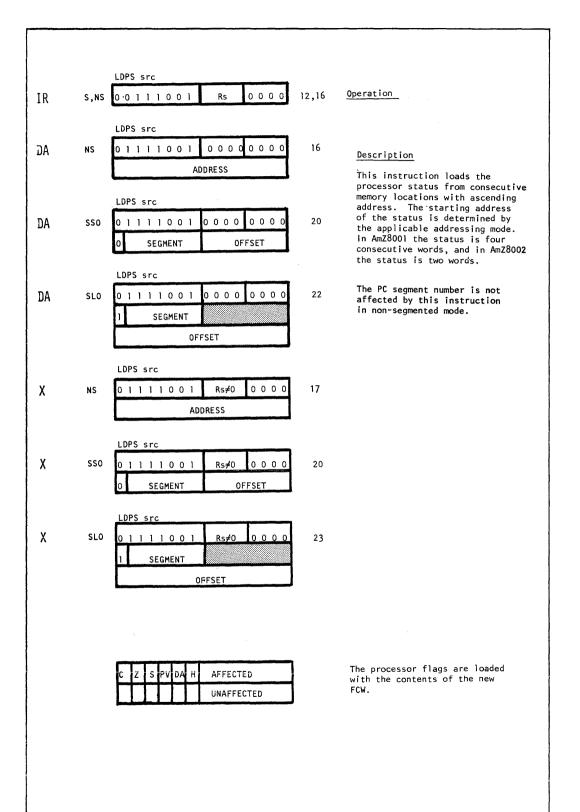

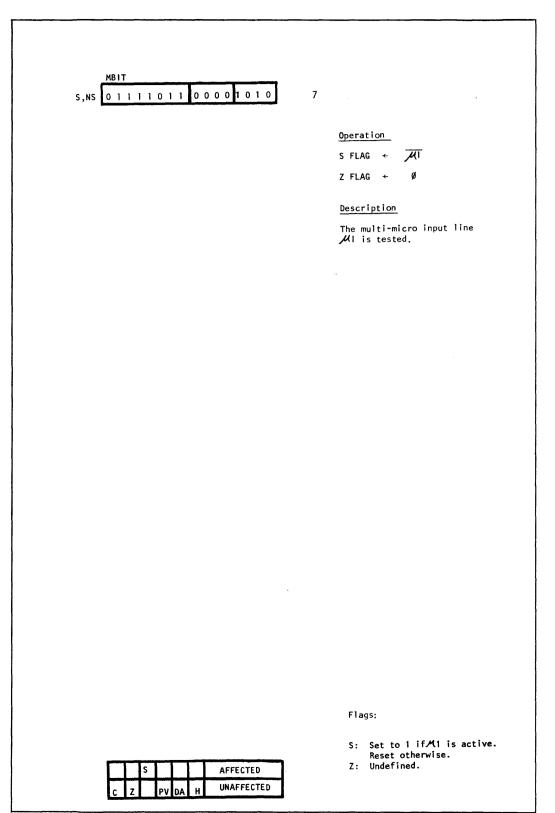

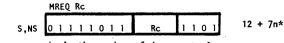

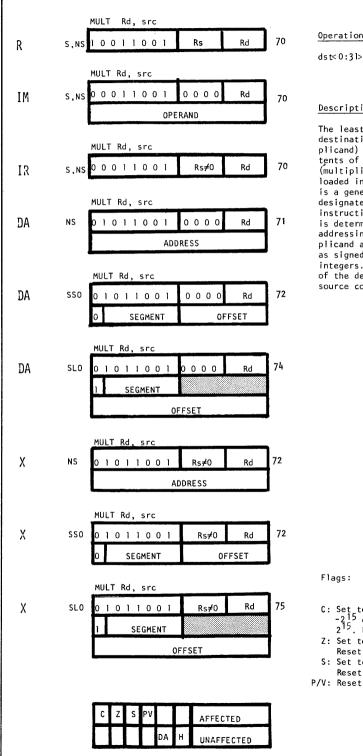

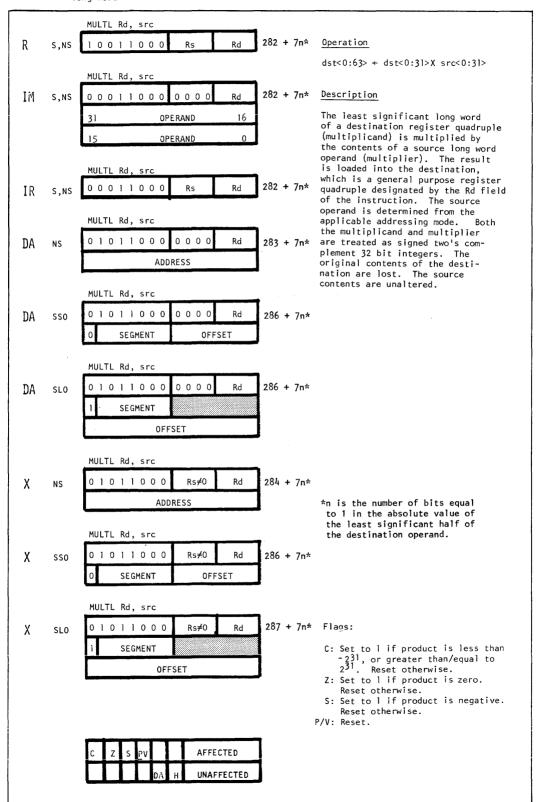

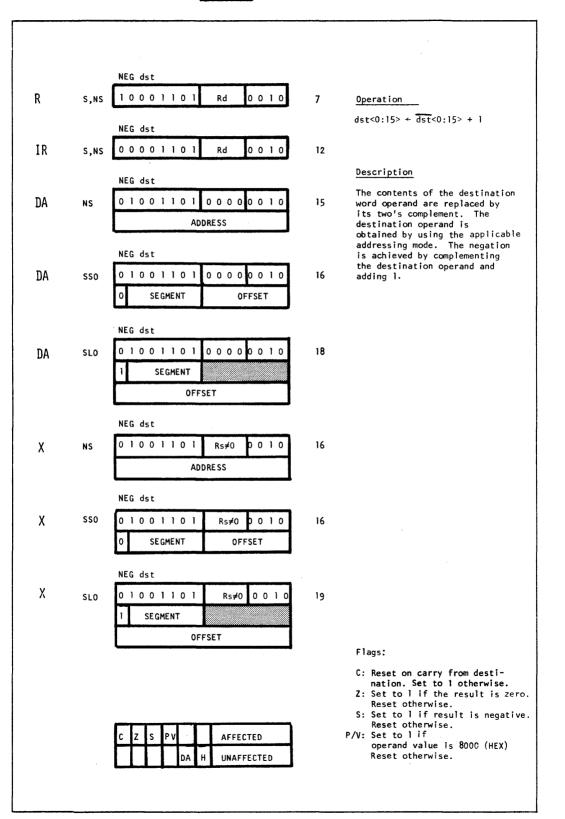

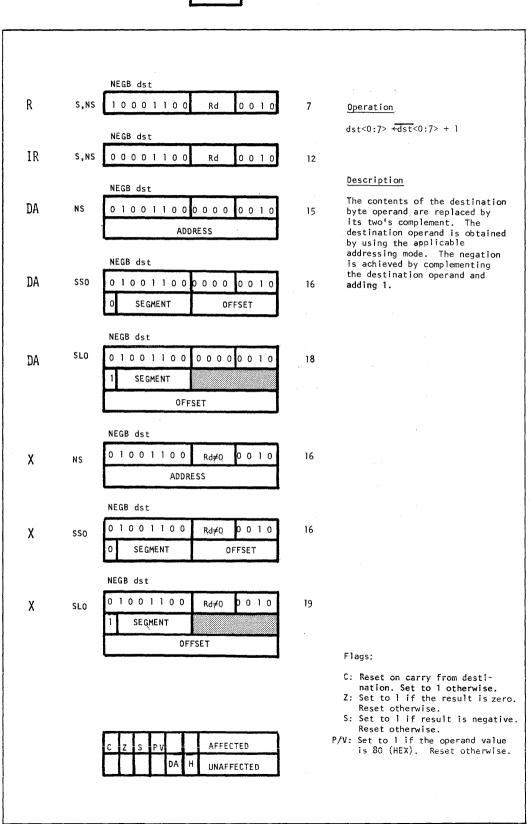

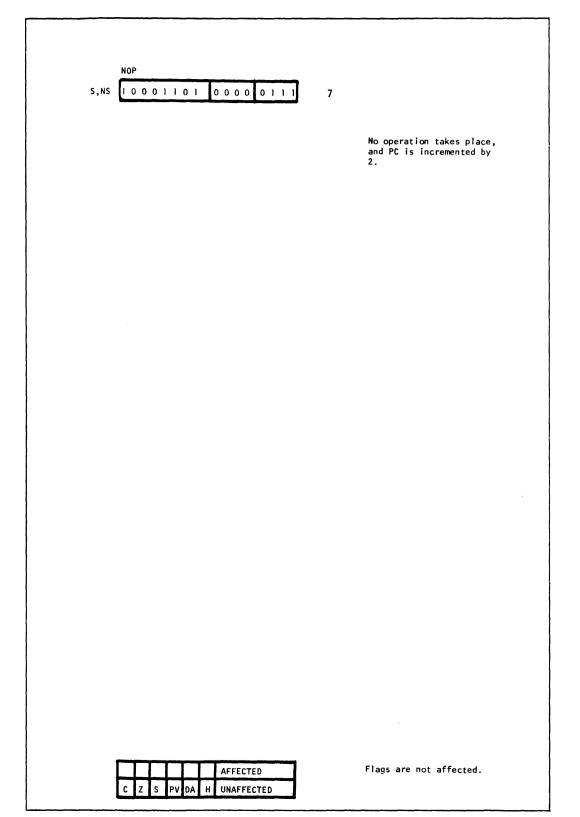

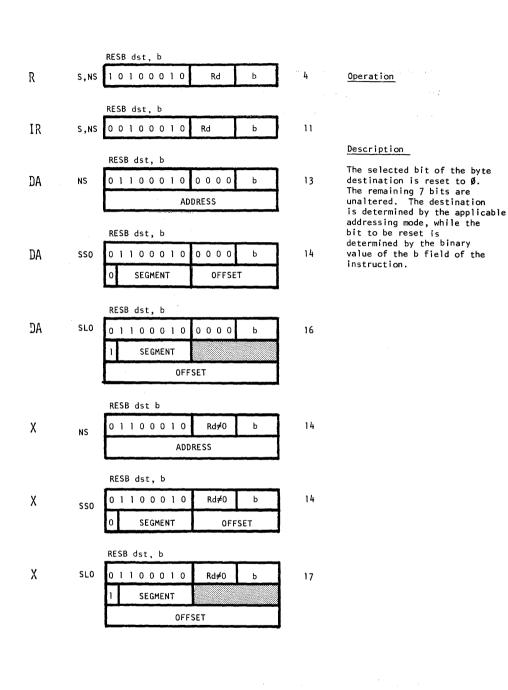

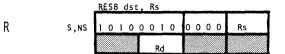

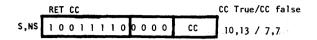

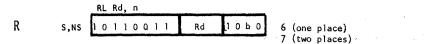

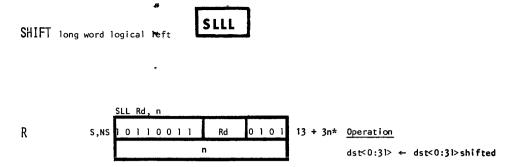

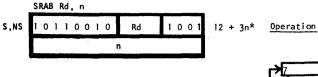

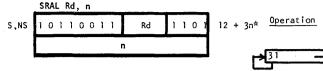

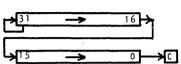

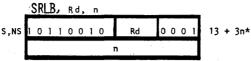

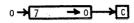

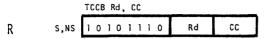

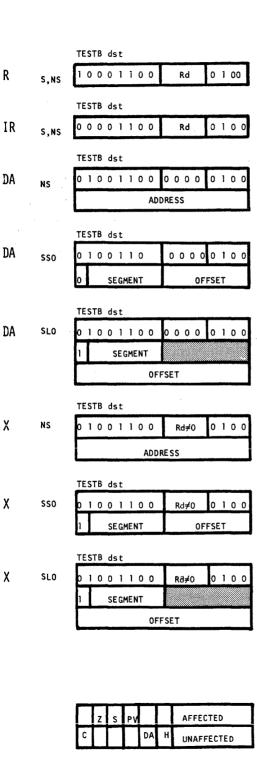

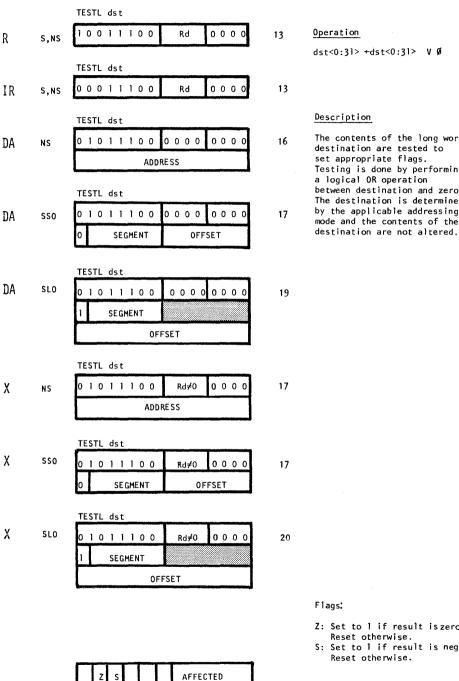

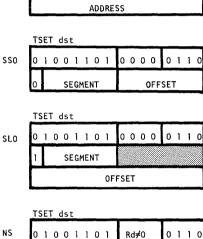

The following pages contain detailed description of the individual instructions. Figure 31 illustrates a sample of the information presented with each instruction.

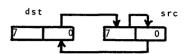

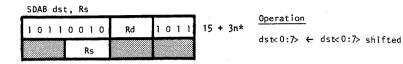

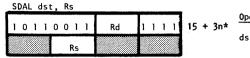

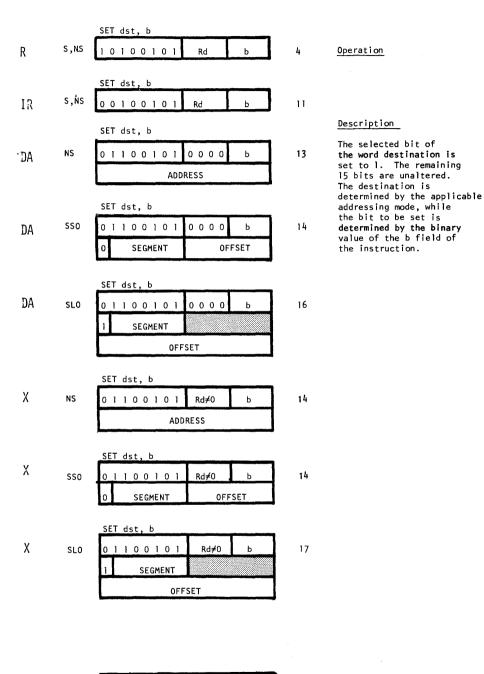

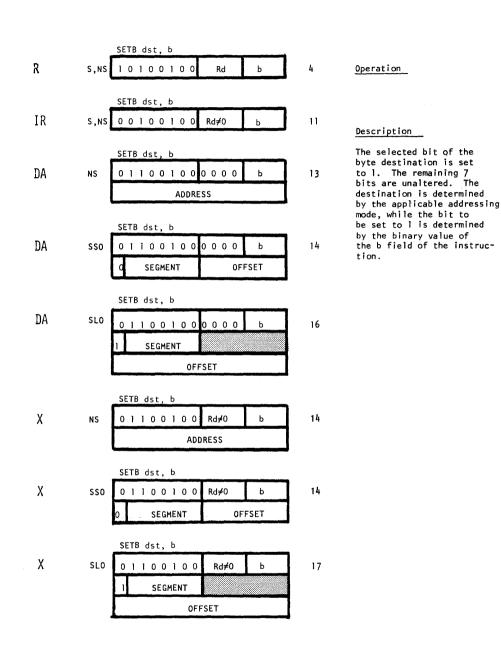

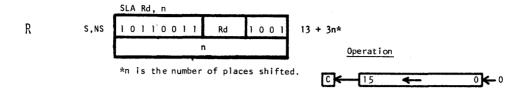

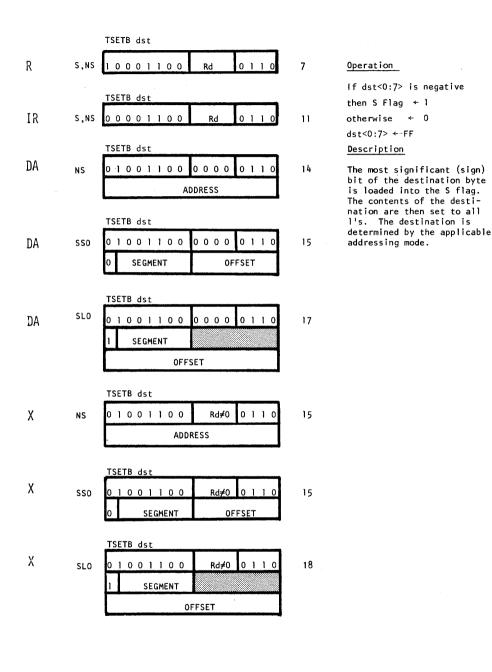

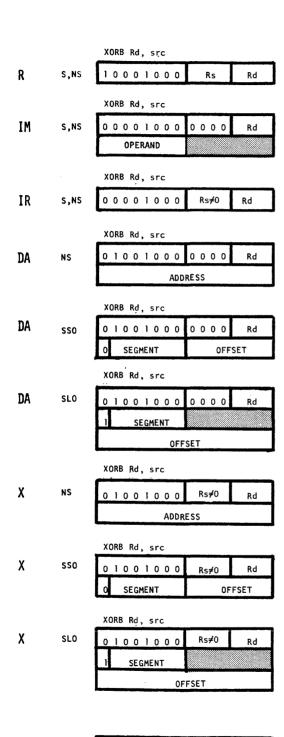

Top left hand corner shows the title of the instruction and then the mnemonic at the top center in each page. If an instruction is priviliged, this fact will be noted to the right of the mnemonic. The operation performed by the instruction is represented by symbolic notation or a simple diagram whenever possible. In the symbolic notation, the operand lengths are designated by two integers separated by a colon between two angled brackets. For example dst<0:15> means that the destination operand occupies 16-bits. If there is only one integer contained between the brackets then the integer represents the bit number in an operand. For example, src<8> means bit number 8 of the source operand.

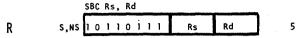

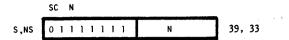

A detailed description of the instruction follows the operation. Also shown with each instruction are the applicable addressing modes for that instruction. The instruction format is shown with appropriate fields labelled. The instruction format shows the pre-assigned bit patterns for the fields whenever appropriate. The number of memory locations occupied by the instruction can also be found in the instruction format. For example, in Figure 31, SETB instruction using R addressing mode occupies one memory word.

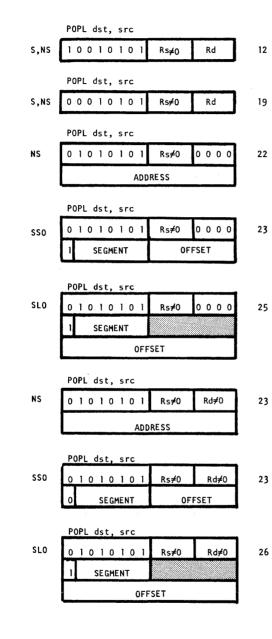

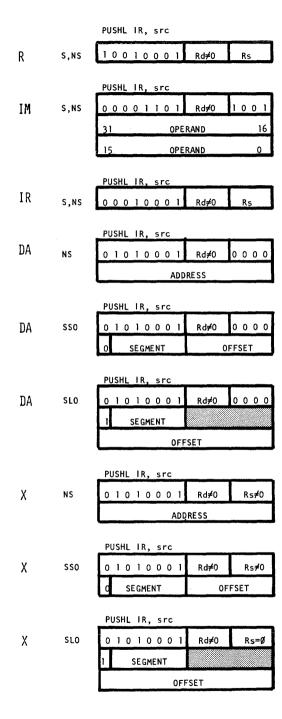

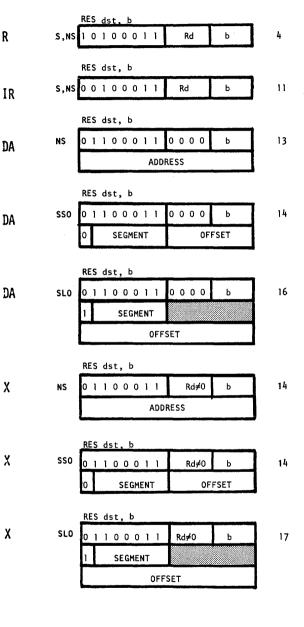

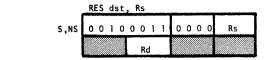

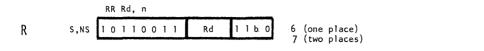

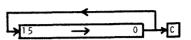

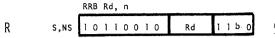

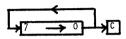

To the left of the instruction format are the CPU characteristics and offset representation using the following abbreviations: S = Segmented, NS = Non-segmented, SSO = Segmented Short Offset, SLO = Segmented Long Offset. The numbers to the right of the instruction format represent the execution time for the instruction in number of clock cycles. Above each instruction format is the general notation representing the operands needed for the instruction. At the bottom of each page is a description and summary of the flags affected. Any shaded areas in the instruction formats are reserved for future CPU expansion and should not be used.

FIGURE 31. SAMPLE INSTRUCTION PAGE

Operation

5

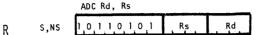

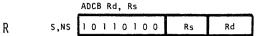

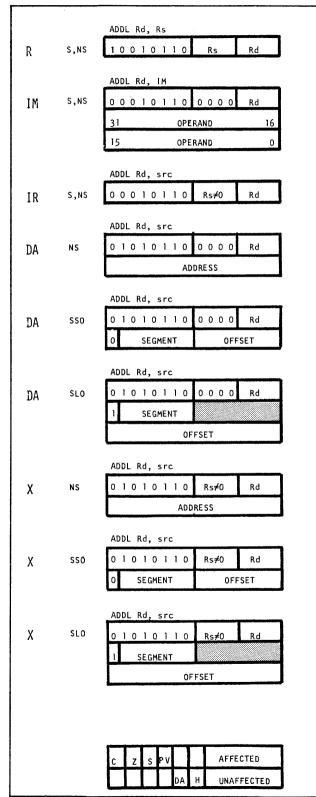

dst<0:15> ←src<0:15> + dst<0:15> + C

# Description

The contents of the general purpose registers designated by the Rs (source) and Rd (destination) fields of the instruction are added together along with the carry flag to obtain the result. The 16-bit result is loaded into the destination register, whose original contents are lost. The contents of the source are not altered.

| F١ | ags | : |  |

|----|-----|---|--|

|----|-----|---|--|

- C: Set to 1 if there is carry from the most significant bit position of the word. Reset otherwise.

- Z: Set to 1 if result is zero. Reset otherwise.

- S: Set to 1 if result is negative. Reset otherwise. P/V: Set to 1 on arithmetic

- overflow. Reset otherwise.

| С | z | s | P/V |    |   | AFFECTED   |

|---|---|---|-----|----|---|------------|

|   |   |   |     | DA | H | UNAFFECTED |

.

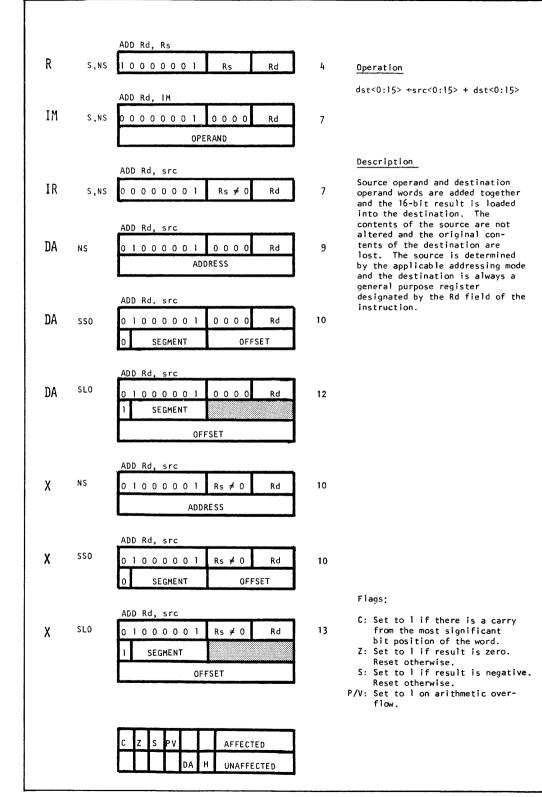

Operation

5

Dst<0:7> + Src<0:7>+ Dst<0:7>+ C

#### Description

The contents of the general purpose byte registers designated by the Rs (source) and Rd (destination) fields of the instruction are added together along with the carry flag to obtain the result. The 8-bit result is loaded into the destination register, whose original contents are lost. The contents of the source are not altered.

| -  | •   |    |   |   |

|----|-----|----|---|---|

| ⊢. | 1 = | ۱n | c | ٠ |

|    |     | ıч | э | ٠ |

- C: Set to 1 if there is a carry from most significant bit position of the byte. Reset otherwise.

- Z: Set to 1 if result is zero. Reset otherwise.

- S: Set to 1 if result is negative. Reset otherwise.

- P/V: Set to 1 on arithmetic overflow. Reset otherwise.

- DA: Reset always.

- H: Set to 1 on carry from the least significant digit of result. Reset otherwise.

| С | z | s | P٧ | DA | Н | AFFECTED   |

|---|---|---|----|----|---|------------|

|   |   |   |    |    |   | UNAFFECTED |

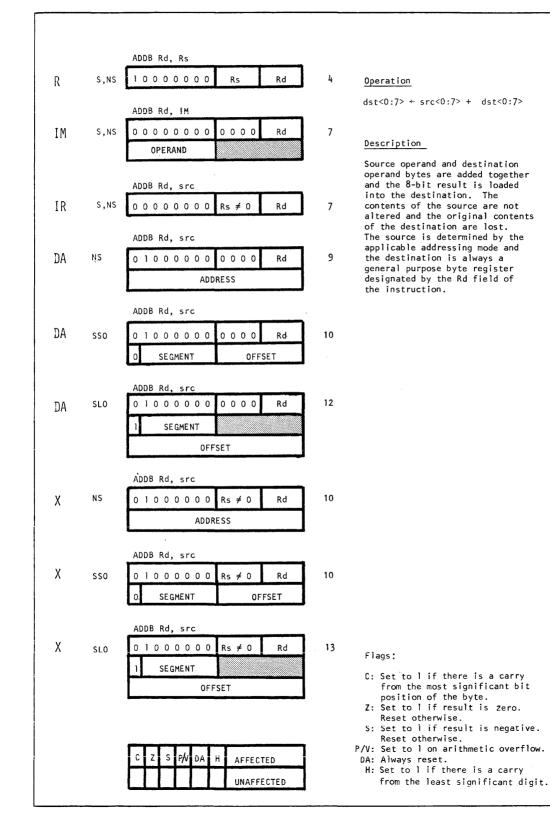

8 Operation

dst<0:31> + src<0:31> + dst<0:31>

14

16

#### Description

Source operand and destination operand long words are added together and the result is loaded into the destination. The contents of the source

- 14 are not altered and the original contents of the destination are lost. The source is determined by the applicable addressing mode and

- 15 the destination is always a general purpose register pair designated by the Rd field of the instruction.

- .

- 18

- 16

- 16

19

#### Flags:

- C: Set to l if there is a carry from the most significant bit position of the long word.

- Z: Set to 1 if result is zero. Reset otherwise.

- S: Set to 1 if result is negative. Reset otherwise. P/V: Set to 1 on arithmetic

- overflow.

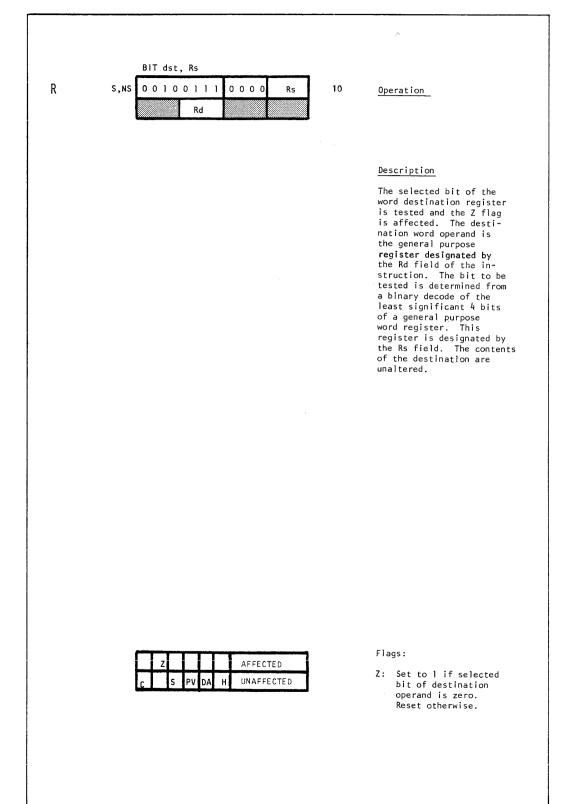

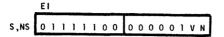

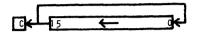

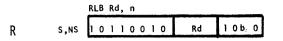

BIT test in a word (dynamic)

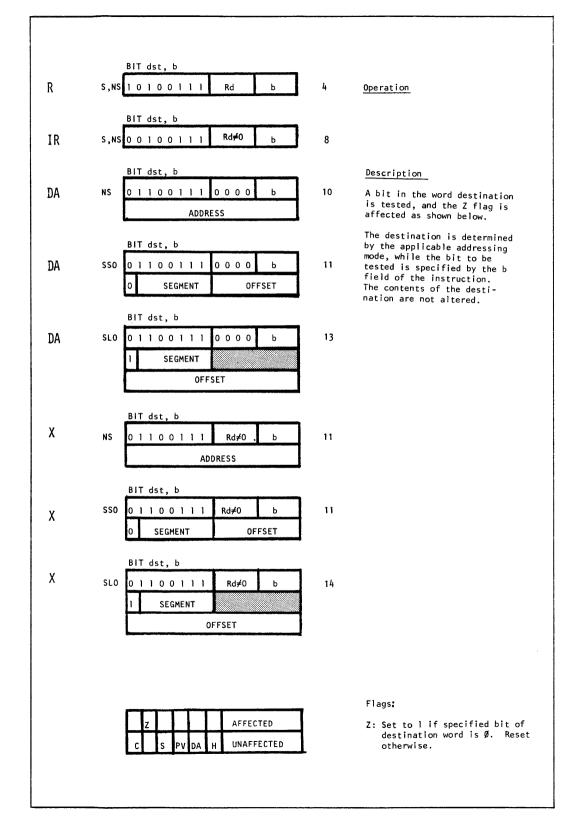

## **BIT** test in a word (static)

BIT test in a byte (dynamic)

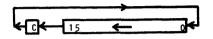

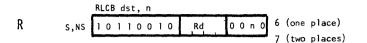

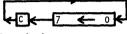

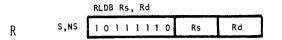

S,NS 00100110 0000 Rs

**Operation**

10

### Description

The selected bit of the byte destination register is tested and the Z flag is affected. The destination byte operand is the general purpose register designated by the Rd field of the instruction. The bit to be tested is determined from a binary decode of the least significant 3 bits of a general purpose word register. This register is designated by the Rs field of the instruction. The contents of the destination are unaltered.

|   | z |   |    |    |   | AFFECTED   |

|---|---|---|----|----|---|------------|

| С |   | s | ΡŅ | DA | H | UNAFFECTED |

Flags:

Z: Set to 1 if selected bit of destination operand is zero. Reset otherwise.

57

# **BIT** test in a byte (static)

# CALI

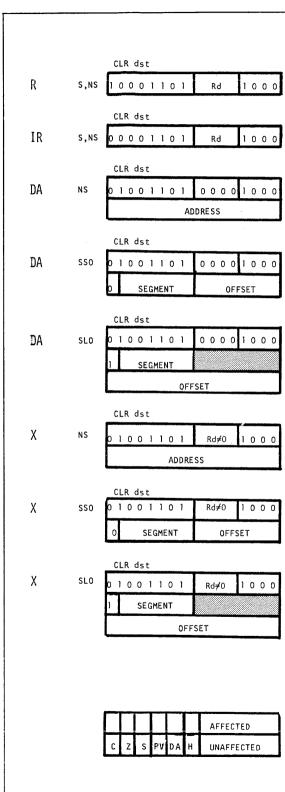

CLEAR word

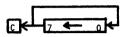

7 Operation

dst <∅:15≯ ← ∅

8

# Description

The 16 bits of the specified destination word are replaced with zeros. The original contents of the destination are lost. The destination is determined by the applicable addressing mode.

14

12

12

12

15

Flags are not affected.

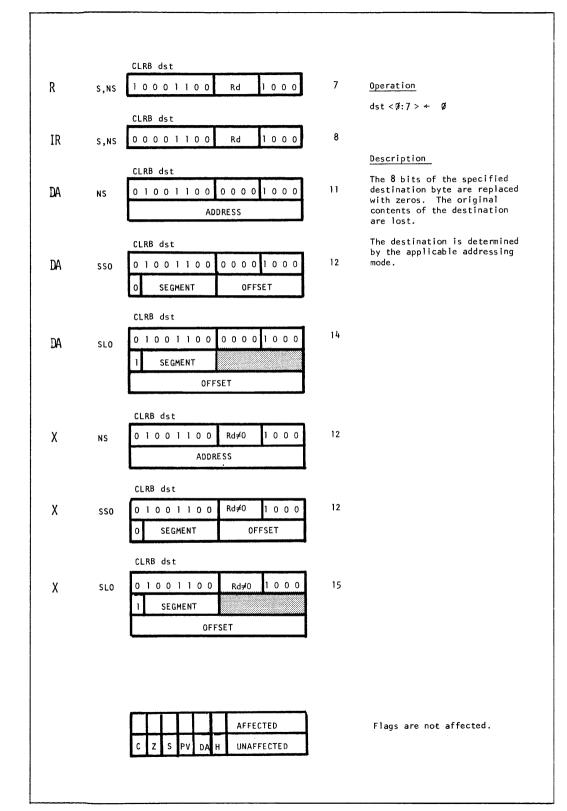

CLEAR byte

# CLRB

S,NS

S,NS

Rd

Rd

0 0 0 0

0000

0 0 0 0

OFFSET

OFFSET

ADDRESS

0 0 0 0

0000

0 0 0 0

0000

0 0 0 0

0000

OFFSET

5

11

14

15

17

15

15

18

R

IR

DA

DA

Х

Х

NS

SSO 01011100 0 SEGMENT

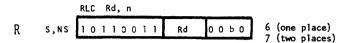

CLRL dst

CLRL dst

CLRL dst

CLRL dst

10011100

0 0 0 1 1 1 0 0

0 1 0 1 1 1 0 0

CLRL dst 0 1 0 1 1 1 0 0 DA SLO 1

> CLRL dst 0 1 0 1 1 1 0 0 Rd ≠ 0 0 0 0 0 ADDRESS

> > SEGMENT

SEGMENT

CLRL dst 0 0 0 1 1 1 0 0

0

sso

NS

Х SLO

| CLR | Ľ | ds | t   |     |     |   |    |      |   |   |   |   |   |   |