# Implementation of Write Allocate in the K86™ Processors

**Application Note**

|  |  |  | ť |

|--|--|--|---|

|  |  |  | • |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  | • |

|  |  |  | • |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

## **Application Note**

# Implementation of Write Allocate in the K86™ Processors

#### What is Write Allocate?

Write allocate, if enabled, occurs when the processor has a pending memory write cycle to a cacheable line and the line does not currently reside in the L1 data cache. In this case, the processor performs a burst read cycle to fetch the cache line addressed by the pending write cycle. The data associated with the pending write cycle is merged with the recently-allocated cache line and stored in the processor's L1 data cache in the modified state. The cache line is marked as modified because the pending write cycle is not performed on the processor's external bus.

During the write allocation, a 32-byte burst read cycle is executed in place of a non-burst write cycle. While the burst read cycle generally takes longer to execute than the write cycle, performance gains are realized on subsequent write cycle hits to the write-allocated cache line. Due to the nature of software, memory accesses tend to occur within proximity of each other (principle of locality). The likelihood of additional write hits to the write-allocated cache line is high.

#### **Programming Details**

The steps required for programming write allocate on K86<sup>TM</sup> processors are as follows:

- 1. Verify write allocate support by using the CPUID instruction to check for the correct type and revision of the processor.

- 2. Configure the MSRs.

- 3. Enable write allocate.

#### Step 1:

The first step in supporting the write allocate feature of the AMD K86 processors is determining the type of processor. Write allocate in the AMD-K5<sup>TM</sup> processor is supported only on Models 1, 2, and 3, with a Stepping of 4 or greater. Write allocate in the AMD-K6<sup>TM</sup> MMX processor is supported only on Models with a Stepping of 1 or greater. Use the CPUID instruction to determine if the proper model and stepping of the processor is present. See the AMD Processor Recognition application note, order# 20734 for more information.

After determining that the processor supports write allocate, the next step is to configure the Model-Specific Registers (MSR).

For an AMD-K5 processor Model 1, 2, or 3 with a Stepping of 4 or greater, go to "Step 2: AMD-K5<sup>TM</sup> Processor." For an AMD-K6 MMX processor with a Stepping of 2 or greater, go to "Step 2: AMD-K6<sup>TM</sup> MMX Processor" on page 8.

#### Step 2: AMD-K5™ Processor

The AMD-K5 processor implements write allocate by providing a global write allocate enable bit, three range-protection enable bits, and two memory range registers. The global write allocate enable bit is accessed using the Hardware Configuration Register (HWCR). The memory range registers and range enable bits are programmed by read/write MSR instructions.

The Write Allocate Enable bit (bit 4 of HWCR) should be set to 0, which prevents potential erroneous behavior in the case of a warm boot during write allocate initialization.

Two MSRs are defined to support write allocate. The MSRs are accessed using the RDMSR and WRMSR instructions (see "RDMSR and WRMSR" in the *AMD-K5<sup>TM</sup> Processor Software Development Guide*, order# 20007). The following index values in the ECX register access the MSRs:

- Write Allocate Top-of-Memory and Control Register (WATMCR)—ECX = 85h

- Write Allocate Programmable Memory Range Register (WAPMRR)—ECX = 86h

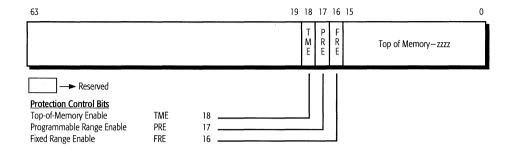

Three non-write-allocatable memory ranges are defined for use with the write allocate feature—one fixed range and two programmable ranges.

**Fixed Range.** The fixed memory range is  $000A_0000h_000F_FFFFh$  and can be enabled or disabled. When enabled, write allocate can not be performed in this range.

This region of memory, which includes standard VGA and other peripheral and BIOS access, is considered non-cacheable. Performing a write allocate in this area can cause compatibility problems. It is recommended that this bit be enabled (set to 1) to prevent write allocate to this range. Set bit 16 of WATMCR to enable protection of this range.

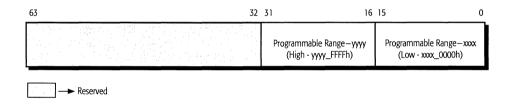

**Programmable Range.** One programmable memory range is xxxx\_0000h-yyyy\_FFFFh, where xxxx and yyyy are defined using bits 15-0 and bits 31-16 of WAPMRR, respectively. Set bit 17 of WATMCR to enable protection of this range. When enabled, write allocate can not be performed in this range.

This programmable memory range exists because a small number of uncommon memory-mapped I/O adapters are mapped to physical RAM locations. If a card like this exists in the system configuration, it is recommended that the BIOS program the 'memory hole' for the adapter into this non-write-allocatable range.

**Top of Memory.** The other programmable memory range is defined by the 'top-of-memory' field. The top of memory is equal to zzzz\_0000h, where zzzz is defined using bits 15-0 of WATMCR. Addresses above zzzz\_0000h are protected from write allocate when bit 18 of WATMCR is enabled.

Once the BIOS determines the size of RAM installed in the system, this size should also be used to program the top of memory. For example, a system with 32 Mbytes of RAM requires that the top-of-memory field be programmed with a value of 0200h, which enables protection from write allocate for memory above that value. Set bit 18 of WATMCR to enable protection of this range.

Caching and write allocate are generally not performed for the memory above the amount of physical RAM in the system. Video frame buffers are usually mapped above physical RAM. If write allocate were attempted in that memory area, there could be performance degradation or compatibility problems.

Bits 18–16 of WATMCR control the enabling or disabling of the three memory ranges as follows:

- Bit 18: Top-of-Memory Enable bit

- 0 = disabled (default)

- 1 = enabled (write allocate can not be performed above Top of Memory)

- Bit 17: Programmable Range Enable bit

- 0 = disabled (default)

- 1 = enabled (write allocate can not be performed in this range)

- Bit 16: Fixed Range Enable bit

- 0 = disabled (default)

- 1 = enabled (write allocate can not be performed in this range)

Figures 1 and 2 show the bit positions for these two new registers.

Figure 1. Write Allocate Top-of-Memory and Control Register (WATMCR) – MSR 85h

Figure 2. Write Allocate Programmable Memory Range Register (WAPMRR)-MSR 86h

#### Step 3: AMD-K5™ Processor

All of the write allocate features in the AMD-K5 processor are enabled by setting bit 4 (WA) of the HWCR (MSR 83h) to 1. For more information on the HWCR, see "Hardware Configuration Register" in the  $AMD-K5^{TM}$  Processor Software Development Guide, order# 20007. Figure 3 shows the definition of HWCR.

The BIOS programmer has several options regarding what the end-user can control. The BIOS can provide the end-user with a setup screen option to enable write allocate. The BIOS can provide the end-user with a setup screen option to also setup the other features (programmable ranges and fixed range). The BIOS can automatically enable and setup the write allocate feature and its registers without end-user intervention. This automatic setup is recommended.

Figure 3. Hardware Configuration Register (HWCR) - MSR 83h

#### AMD-K5™ Processor Programming Example for Write Allocate Registers

The following cases show examples of programming the write allocate feature for two types of systems:

#### Case 1:

For systems without a memory hole and 16 Mbytes of total memory:

- Program the WATMCR MSR (ECX=85h) with top of memory (0100h) and enable bits (0005h) to protect the fixed range and above the top of memory

- Use the WRMSR instruction and the 64-bit hex value 0000\_0000\_0005\_0100h

Note: For 8-Mbyte systems, program 0080h in the lowest 16 bits. For 32-Mbyte systems, program 0200h in the lowest 16 bits.

#### **Code Sample:**

```

:disable WA bit (bit 4 of HWCR)

MOV

ECX.83H

:read HWCR (83h)

RDMSR

AND

EAX, NOT 10H

WRMSR

:program top-of-memory and control bits

VOM

ECX,85H

;select WATMCR

MOV

EAX,50100H

;TME=1,PRE=0,FRE=1,TOM=0100h

XOR

EDX.EDX

WRMSR

:enable WA bit

MOV

ECX.83H

:read HWCR (83h)

RDMSR

EAX,10H

;set bit 4

0R

WRMSR

```

#### Case 2:

For systems with a 1 Mbyte memory hole starting at the 15 Mbyte boundary and 32 Mbytes of total memory:

- Program the WAPMRR MSR (ECX=86h) with 15 Mbytes (00F0h) to 16 Mbytes –1 (00FFh)

- Use the WRMSR instruction and the 64-bit hex value 0000 0000 00FF 00F0h

- Program the WATMCR MSR (ECX=85h) with top of memory (0200h) and all enable bits (0007h) to protect above the top of memory, the fixed range, and the programmable range

- Use the WRMSR instruction and the 64-bit hex value 0000\_0000\_0007\_0200h

**Note:** For 8-Mbyte systems, program 0080h in the lowest 16 bits. For 16-Mbyte systems, program 0100h in the lowest 16 bits.

#### **Code Sample:**

```

:disable WA bit (bit 4 of HWCR)

ECX,83H

;read HWCR (83h)

MOV

RDMSR

EAX.NOT 10H

AND

WRMSR

:program programmable range to 15-16Mbytes

:select WAPMRR

MOV

ECX.86H

;address from F00000 to FFFFFF

MOV

EAX.OFFOOFOH

XOR

EDX, EDX

;clear

WRMSR

program top of memory and control bits

;select WATMCR

ECX.85H

MOV

;TME=1,PRE=1,FRE=1,TOM=0200h

MOV

EAX,70200H

XOR

EDX.EDX

:clear

WRMSR

:enable WA bit

MOV

ECX,83H

:read HWCR (83h)

RDMSR

EAX.10H

0R

:set bit 4

WRMSR

```

#### Step 2: AMD-K6™ MMX Processor

The AMD-K6 MMX processor implements write allocate differently than the AMD-K5 processor. This section describes two programmable mechanisms used by the AMD-K6 processor to determine when to perform write allocate. When either of these mechanisms indicates that a pending write is to a cacheable area of memory, a write allocate is performed.

Before programming any registers, the BIOS must writeback and invalidate the internal cache by using the WBINVD instruction. In addition, prior to setting up the write allocate registers, the WHCR should be set to 0000\_0000\_0000\_0000h, which prevents potential erroneous behavior in the case of a warm boot.

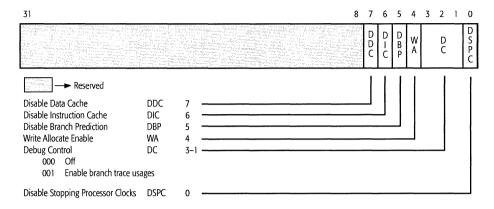

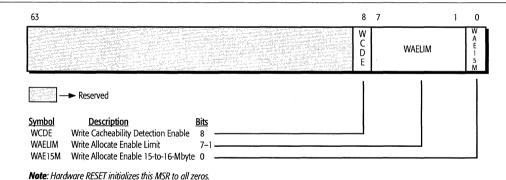

Write Handling Control Register (WHCR). The Write Handling Control Register (WHCR) is an MSR that contains three fields—the WCDE bit, the Write Allocate Enable Limit (WAELIM) field, and the Write Allocate Enable 15-to-16-Mbyte (WAE15M) bit (See Figure 4).

Figure 4. Write Handling Control Register (WHCR)—MSR C000\_0082h

Write Cacheability Detection Enable. Write Cacheability Detection causes a write allocate to occur only if the Write Cacheability Detection Enable (WCDE) bit (bit 8) in the Write Handling Control Register (WHCR) MSR is set to 1. For more details on the Write Cacheability Detection Mechanism, see the Cache

Organization chapter in the AMD- $K6^{TM}$  MMX Processor Data Sheet, order# 20695.

If the address is cacheable, support of the Write Cacheability Detection mechanism requires the system logic to assert KEN during a write cycle. Some chipsets assert KEN during a write cycle and some chipsets do not assert KEN during a write cycle. (Triton chipsets eventually generate a correct value for KEN, but not during the sample point. Therefore do not enable WCDE in systems that use the Triton chipset.) If Write Cacheability Detection is enabled, KEN is sampled during write cycles in the same manner it is sampled during read cycles (KEN is sampled on the clock edge on which the first BRDY or NA of a cycle is sampled asserted).

It is recommended that the BIOS enable the WCDE feature only if it is known that the chipset properly asserts KEN during a write cycle.

Write Allocate Enable Limit. The WAELIM field is 7 bits wide. This field, multiplied by 4 Mbytes, defines an upper memory limit. Any pending write cycle that addresses memory below this limit causes the processor to perform a write allocate. Write allocate is disabled for memory accesses at and above this limit unless the processor determines a pending write cycle is cacheable by means of one of the other Write Cacheability Detection mechanisms. The maximum value of this limit is (( $2^7$ -1) · 4 Mbytes) = 508 Mbytes. When all the bits in this field are set to 0, all memory is above this limit and the write allocate mechanism is disabled.

The WAELIM field is similar to the AMD-K5 processor top-of-memory field. Once the BIOS determines the amount of RAM installed in the system, this number should also be used to program the WAELIM field. For example, a system with 32 Mbytes of RAM would program the WAELIM field with the value 0001000b. This value (8), when multiplied by 4 Mbytes, yields 32 Mbytes as the write allocate limit.

Write Allocate Enable 15-to-16-Mbyte. The WAE15M bit is used to enable write allocations for the memory write cycles that address the 1 Mbyte of memory between 15 Mbytes and 16 Mbytes. This bit must be set to 0 to prevent write allocates in this memory area. This sub-mechanism of the WAELIM provides a memory hole to prevent write allocates. This

memory hole is provided to account for a small number of uncommon memory-mapped I/O adapters that use this particular memory address space. If the system contains one of these peripherals, the bit should be set to 0. The WAE15M bit is ignored if the value in the WAELIM field is set to less than 16 Mbytes.

By definition, write allocations in the AMD-K6 are never performed in the memory area between 640 Kbytes and 1 Mbyte. It is not safe to perform write allocations between 640 Kbytes and 1 Mbyte (000A\_0000h to 000F\_FFFFh) because it is considered a non-cacheable region of memory.

#### Step 3: AMD-K6™ MMX Processor

The BIOS programmer has several options regarding what the end-user can control. The BIOS can provide the end-user with a setup screen option to enable write allocate. The BIOS can provide the end-user with a setup screen option for the other features (Write Cacheability Detection, Write Allocate Enable Limit, and Write Allocate Enable 15-to-16-Mbyte). The BIOS can also automatically enable and setup the write allocate feature and its registers without end-user intervention. This automatic setup is recommended. To disable all write allocate features for the AMD-K6 processor, the WHCR must be set to  $0000\_0000\_0000\_00000\_0000h$ —the default value at boot-up.

# AMD-K6™ MMX Processor Programming Example for Write Allocate Registers

The following cases show examples of programming the write allocate feature for two types of systems:

#### Case 1:

For systems that contain chipsets that do not properly support KEN on write cycles, have a 1 Mbyte memory hole starting at the 15 Mbyte boundary, and 32 Mbytes of total memory:

- Program the WHCR MSR (ECX=C000\_0082h) with WCDE=0, WAELIM=8, and WAE15M=0

- Use the WRMSR instruction and the 64-bit hex value 0000\_0000\_0000\_0010h

**Code Sample:**

:flush cache

PUSHE

:save state

CLI :disable interrupts

WBINVD ;write back and invalidate cache

;set Write Allocate Limit and clear WAE15M bit

MOV ECX.0C0000082H

MOV EAX.10H

:WCDE=0.WAELIM=8.WAE15M=0

XOR EDX.EDX

WRMSR

POPF

;restore original state

Case 2:

For systems with chipsets that properly support KEN on write cycles, do not have a memory hole, and have 16 Mbytes of total memory:

- Program the WHCR MSR (ECX=C000\_0082h) with WCDE=1, WAELIM=4, and WAE15M=1

- Use the WRMSR instruction and the 64-bit hex value 0000 0000 0000 0109h

**Code Sample:**

:flush cache

**PUSHF** ;save state

CLI :disable interrupts

WBINVD ;write back and invalidate cache

:set Write Allocate Limit and set WAE15M bit

MOV ECX,0C0000082H

; WCDE=1, WAELIM=4, WAE15M=1 MOV EAX.109H

EDX, EDX XOR

WRMSR

POPF ;restore original state

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

K86, AMD-K5, AMD-K6, and the AMD-K6 logo are trademarks of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### Sales Offices

#### North American

| ALABAMA                    |                  |

|----------------------------|------------------|

| ARIZONA                    | (602) 242-4400   |

| CALIFORNIA,                |                  |

| Calabasas                  |                  |

| Irvine                     |                  |

| Sacramento (Roseville)     |                  |

| San Diego                  | (619) 560-7030   |

| San Jose                   |                  |

| CANADA, Ontario,           | , ,              |

| Kanata                     | (613) 592-0060   |

| Woodbridge                 | (905) 856-3377   |

| COLORADO                   |                  |

| CONNECTICUT                |                  |

| FLORIDA.                   |                  |

| Clearwater                 | (813) 530-9971   |

| Ft. Lauderdale             |                  |

| Orlando (Longwood)         |                  |

| GEORGIA                    |                  |

| IDAHO                      |                  |

| ILLINOIS, Chicago (Itasca) |                  |

| KENTUCKY                   |                  |

|                            |                  |

| MARYLAND                   |                  |

| MASSACHUSETTS              |                  |

| MINNESOTA                  | (612) 938-0001   |

| NEW JERSEY,                | ()               |

| Cherry Hill                |                  |

| Parsippany                 | (201) 299-0002   |

| NEW YORK,                  |                  |

| Brewster                   |                  |

| Rochester                  | (716) 425-8050   |

| NORTH CAROLINA,            |                  |

| Charlotte                  | (704) 875-3091   |

| Raleigh                    | (919) 878-8111   |

| OHIO,                      |                  |

| Columbus (Westerville)     | (614) 891-6455   |

| Dayton                     |                  |

| OREGON                     | (503) 245-0080   |

| PENNSYLVANIA               | (610) 398-8006   |

| TEXAS.                     | ` ,              |

| Austin                     | (512) 346-7830   |

| Dallas                     |                  |

| Houston                    |                  |

| nouston                    | (713) 070-000-   |

| International              |                  |

| AUSTRALIA, N Sydney TEL    | (61) 2 9959-1937 |

|                            | (61) 2 9959-1937 |

| BELGIUM, Antwerpen TEL     |                  |

|                            |                  |

| FAX                        | (03) 248-4642    |

| AUSTRALIA, N Sydney | TEL (61) 2 9959-1937 |

|---------------------|----------------------|

|                     | FAX (61) 2 9959-1037 |

| BELGIUM, Antwerpen  | TEL (03) 248-4300    |

|                     | FAX (03) 248-4642    |

| CHINA,              |                      |

| Beijing             | TEL (8610) 501-1566  |

|                     | FAX(8610) 465-1291   |

|                     | TEL (8621) 6267-8857 |

|                     | TEL (8621) 6267-9883 |

|                     | FAX(8621) 6267-8110  |

|                     | TEL (358) 9 881 3117 |

|                     | FAX (358) 9 804 1110 |

|                     | TEL (1) 49-75-1010   |

|                     | FAX(1) 49-75-1013    |

| GERMANY,            | ,                    |

|                     | TEL (06172) 92670    |

|                     | FAX (06172) 23195    |

|                     | TEL(089) 450530      |

|                     | FAX(089) 406490      |

|                     | TEL (852) 2956-0388  |

|                     | FAX(852) 2956-0588   |

|                     | TEL(02) 381961       |

|                     | FAX (02) 3810-3458   |

| JAPAN,              | ,                    |

| Osaka               | TEL (06) 243-3250    |

|                     | FAX (06) 243-3253    |

| Tokyo               | TEL (03) 3346-7600   |

| •                   | FAX (03) 3346-5197   |

| KOREA, Seoul         | TEL | (82) 2784-0030   |

|----------------------|-----|------------------|

|                      | FAX | (82) 2784-8014   |

| SINGAPORE, Singapore |     |                  |

|                      |     | (65) 338-1611    |

| SCOTLAND, Stirling   |     |                  |

|                      |     | (44) 1786-446188 |

| SWITZERLAND, Geneva  | TEL | (41) 22-788-0251 |

|                      | FAX | (41) 22-788-0617 |

| SWEDEN,              |     | , ,              |

| Stockholm area       | TEL | (08) 629-2850    |

| (Bromma)             | FAX | (08) 98-0906     |

| TAIWAN, Taipei       | TEL | (886) 2715-3536  |

|                      |     | (886) 2712-2182  |

| UNITED KINGDOM,      |     |                  |

| London area          | TEL | (01483) 74-0440  |

| (Woking)             | FAX | (01483) 75-6196  |

| Manchester area      | TEL | (01925) 83-0380  |

| (Warrington)         | FAX | (01925) 83-0204  |

| , , ,                |     | , ,              |

#### North American Representatives

| riorin rimorioan rioprocomanico            |       |       |     |

|--------------------------------------------|-------|-------|-----|

| ARIZONA,                                   |       |       |     |

| Scottsdale - THORSON DESERT STATES         | (602) | 998-2 | 444 |

| CALIFORNIA,                                |       |       |     |

| Chula Vista – SONIKA ELECTRONICA           | (619) | 498-8 | 340 |

| CANADA,                                    |       |       |     |

| Burnaby, B.C DAVETEK MARKETING             | (604) | 430-3 | 680 |

| Dorval, Quebec - POLAR COMPONENTS          | (514) | 683-3 | 141 |

| Kanata, Ontario - POLAR COMPONENTS         | (613) | 592-8 | 807 |

| Woodbridge, Ontario - POLAR COMPONENTS     | (416) | 410-3 | 377 |

| ILLINOIS,                                  |       |       |     |

| Skokie - INDUSTRIAL REPS, INC              | (847) | 967-8 | 430 |

| INDIANA,                                   |       |       |     |

| Kokomo - SCHILLINGER ASSOC                 | (317) | 457-7 | 241 |

| IOWA,                                      | . ,   |       |     |

| Cedar Rapids - LORENZ SALES                | (319) | 377-4 | 666 |

| KANSAS.                                    | . ,   |       |     |

| Merriam - LORENZ SALES                     | (913) | 469-1 | 312 |

| Wichita - LORENZ SALES                     | (316) | 721-0 | 500 |

| MEXICO,                                    | ` '   |       |     |

| Guadalajara - SONIKA ELECTRONICA           | (523) | 647-4 | 250 |

| Mexico City - SONIKA ELECTRONICA           |       |       |     |

| Monterrey - SONIKA ELECTRONICA             |       |       |     |

| MICHIGAN.                                  | ()    |       |     |

| Brighton - COM-TEK SALES, INC              | (810) | 227-0 | 007 |

| Holland - COM-TEK SALES, INC               |       |       |     |

| MINNESOTA,                                 | . ,   |       |     |

| Edina - MEL FOSTER TECH. SALES, INC        | (612) | 941-9 | 790 |

| MISSOURI.                                  | ` '   |       |     |

| St Louis - LORENZ SALES                    | (314) | 997-4 | 558 |

| NEBRASKA.                                  | . ,   |       |     |

| Lincoln - LORENZ SALES                     | (402) | 475-4 | 660 |

| NEW YORK,                                  | ` '   |       |     |

| Plainview - COMPONENT CONSULTANTS          | (516) | 273-5 | 050 |

| East Syracuse - NYCOM                      |       |       |     |

| Fairport - NYCOM                           |       |       |     |

| OHIO,                                      | ` '   |       |     |

| Centerville - DOLFUSS ROOT & CO            | (513) | 433-6 | 776 |

| Powell - DOLFUSS ROOT & CO                 |       |       |     |

| Middleburg Hts - DOLFUSS ROOT & CO         |       |       |     |

| PUERTO RICO.                               | (,    |       |     |

| Caguas - COMP REP ASSOC, INC               | (787) | 746-6 | 550 |

| UTAH.                                      | (,    |       |     |

| Murray – FRONT RANGE MARKETING             | (801) | 288-2 | 500 |

| WASHINGTON.                                | (,    |       |     |

| Kirkland – ELECTRA TECHNICAL SALES         | (206) | 821-7 | 442 |

| WISCONSIN,                                 | (=50) | /     |     |

| Pewaukee – Industrial Representatives, Inc | (414) | 574-9 | 393 |

| 30, 110                                    | , ,   | •     |     |

|                                            |       |       |     |

Advanced Micro Devices reserves the right to make changes in its product without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

|  |  | ٠ |  |

|--|--|---|--|

ř

ņ

One AMD Place P.O. Box 3453 Sunnyvale, California 94088-3453 408-732-2400 Toll Free 800-538-8450 TWX 910-339-9280 TELEX 34-6306

### TECHNICAL SUPPORT & LITERATURE ORDERING

USA 800-222-9323 USA PC CPU Technical Support 408-749-3060

> JAPAN 03-3346-7550 Fax 03-3346-9628 FAR EAST Fax 852-2956-0599

EUROPE & UK 44-(0)-1276-803299 Fax 44-(0)-1276-803298 BBS 44-(0)-1276-803211 FRANCE 0590-8621 GERMANY 089-450-53199

ARGENTINA 001-800-200-1111, after tone 888-263-8500 BRAZIL 000-811-718-5573 CHILE 800-570-048 MEXICO 95-800-263-4758

ITALY 1678-77224

PC CPU Technical Support E-mail: hwsupt@brahms.amd.com

Europe Technical Support E-mail: euro.tech@amd.com

Europe Literature Request E-mail: euro.lit@amd.com

http://www.amd.com

Printed in USA Con-5.4M-3/97-0 21326A