# Am286<sup>TM</sup>ZX/LX Integrated Processor Technical Manual

Advanced Micro Devices

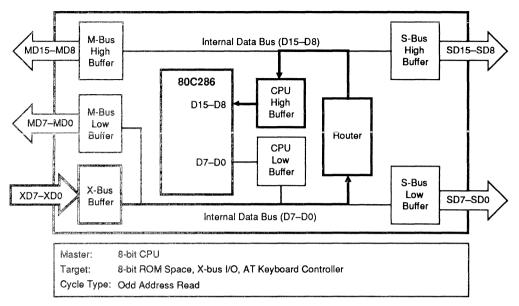

1991

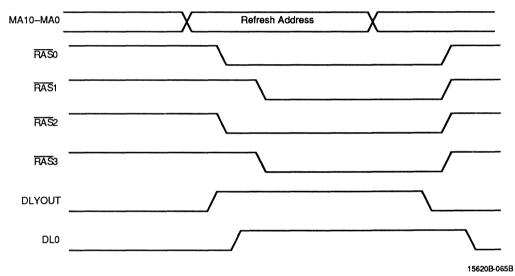

# Am286<sup>™</sup>ZX/LX Integrated Processor Technical Manual

ADVANCED MICRO DEVICES 🗖

© 1991 Advanced Micro Devices, Inc. All rights reserved.

#### Advanced Micro Devices, Inc. reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

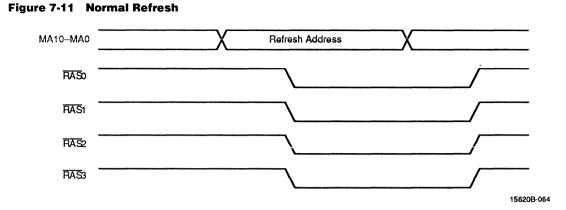

This publication neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability of fitness for a particular application. AMD® assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

AMD is a registered trademark of Advanced Micro Devices, Incorporated. Am286 and AMD 80C287 are trademarks of Advanced Micro Devices, Incorporated.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **TABLE OF CONTENTS**

| Oberland  | Inducation                                 |       |

|-----------|--------------------------------------------|-------|

| Chapter 1 | Introduction                               |       |

|           | Design Goals                               |       |

|           | Distinctive Characteristics                |       |

|           | General Description                        |       |

|           | Pin Descriptions                           |       |

|           |                                            |       |

|           | AT System Bus (S Bus) Interface            |       |

|           | DRAM Interface                             |       |

|           | X Bus Interface                            |       |

|           | Coprocessor Interface                      |       |

|           | Keyboard Controller Interface              |       |

|           | Miscellaneous Signals                      | .1-13 |

| Chapter 2 | 80C286 and Standard Peripherals            | 2-1   |

|           | 80C286 Microprocessor Core                 |       |

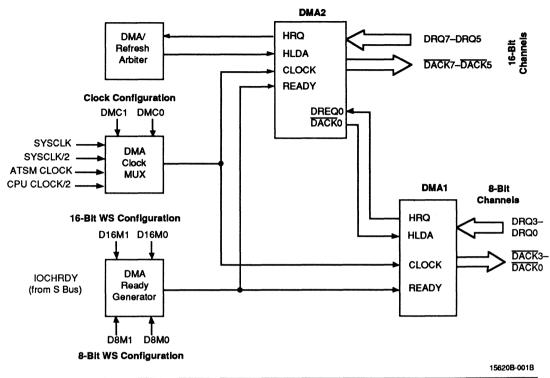

|           | DMA Controllers                            |       |

|           | Clock Control                              |       |

|           | Cycle Control                              |       |

|           | X-Bus Redirection                          |       |

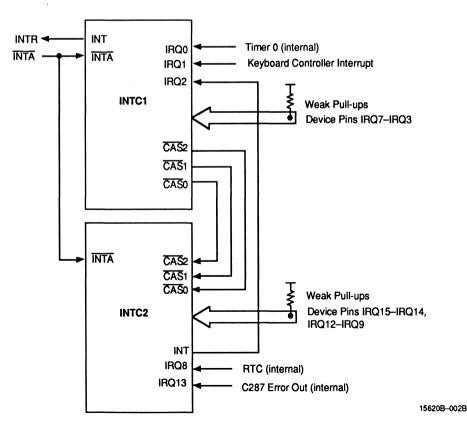

|           | Interrupt Controllers                      |       |

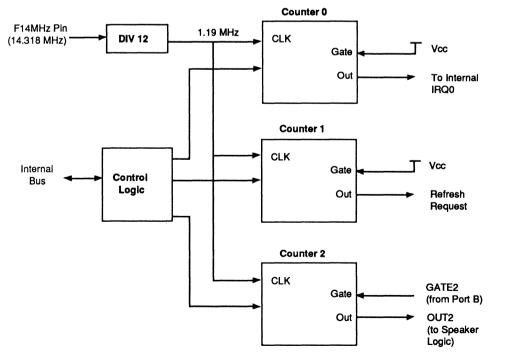

|           | Counter/Timer                              |       |

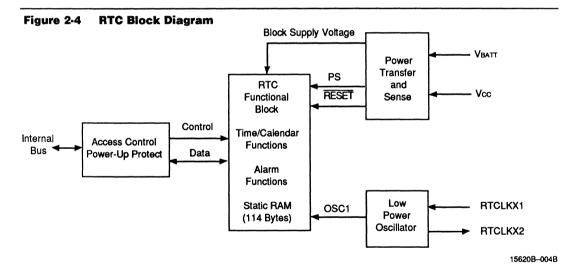

|           | Real Time Clock and CMOS Static RAM        |       |

|           | RTC Address Map                            |       |

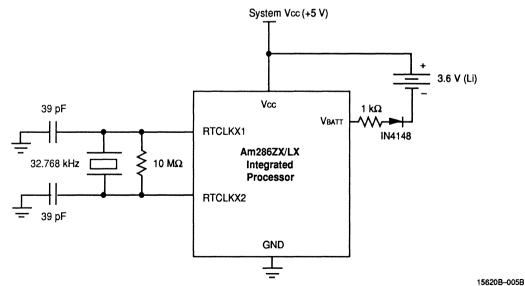

|           | External Connections                       |       |

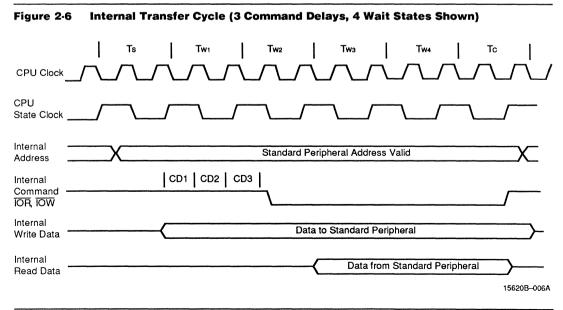

|           | Standard Peripheral I/O Cycle Control      |       |

|           | Description of Cycles                      |       |

|           | Programmable Options                       |       |

| Obenies 2 | Sustan Control Logia                       |       |

| Chapter 3 | System Control Logic                       |       |

|           | Configuration Registers                    |       |

|           | Access Method                              |       |

|           | Off-Chip Expansion                         |       |

|           | Enhanced Clock Generator                   |       |

|           | CPU Clock                                  |       |

|           | AT State Machine Clock                     |       |

|           | CPU and AT State Machine Clock Interaction |       |

|           | Keyboard Clock                             |       |

|           | Coprocessor Clock                          |       |

|           | Clocking Mode Indication                   |       |

|           | Enhanced Bus Controller                    | .3-10 |

|           | Features                                   |       |

|           | Bus Control Configuration                  |       |

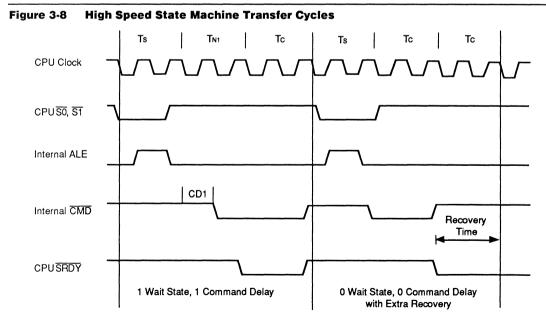

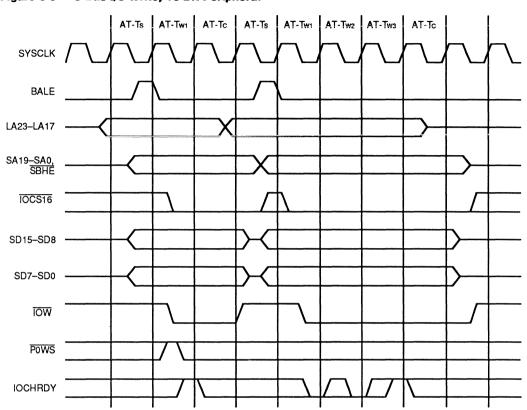

|           | High Speed State Machine Cycles            |       |

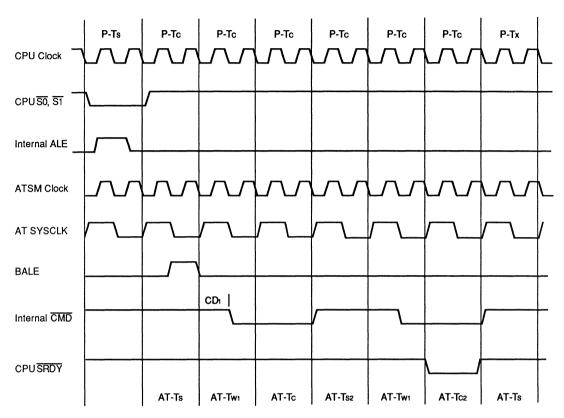

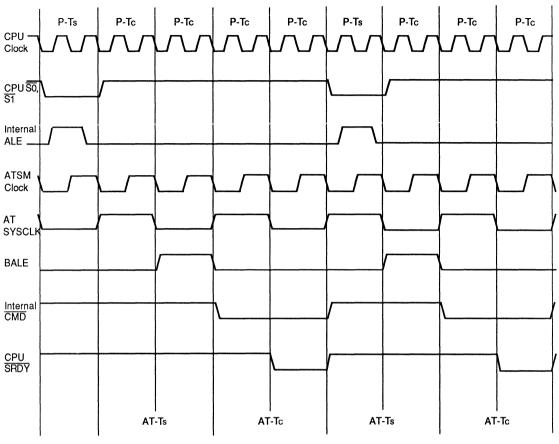

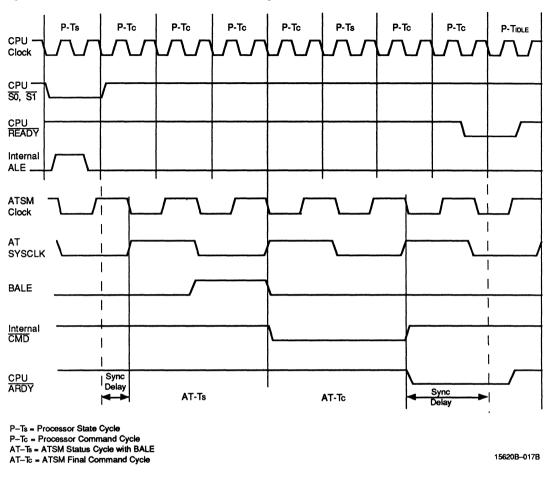

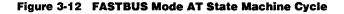

|           | AT State Machine Cycles                    |       |

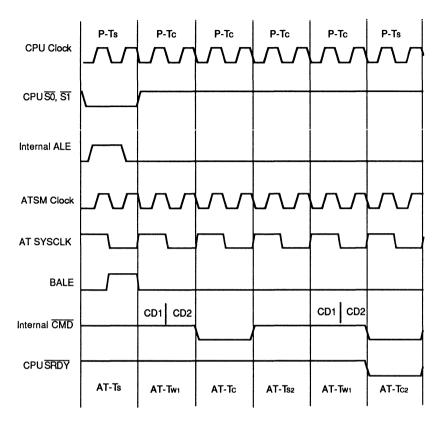

|           | Power Saving Features (Am286LX Only)       |       |

|           | Clock Control                              |       |

|           | Refresh Cycle Options                      | .3-23 |

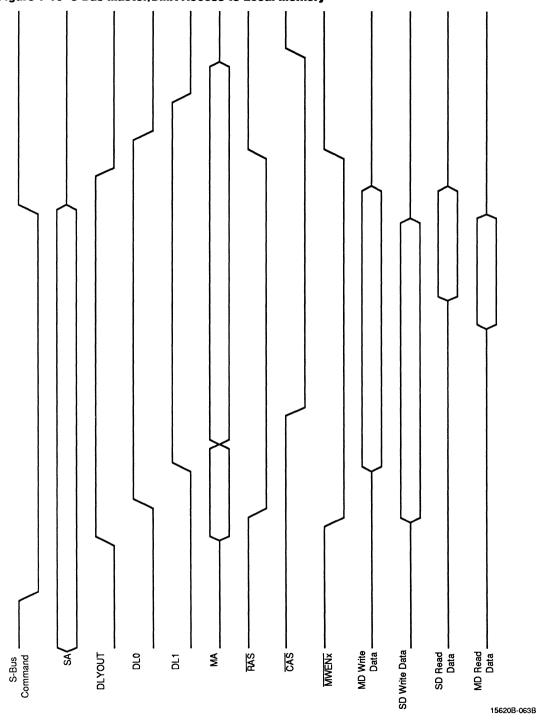

|           | Bus Master Mode                                     |     |

|-----------|-----------------------------------------------------|-----|

|           | Functional Description                              |     |

|           | Configuration and Connection                        |     |

|           | Bus Master Mode Transfer Cycles<br>Memory Subsystem |     |

|           | DRAM Interface                                      |     |

|           | RAS Time Out                                        |     |

|           |                                                     |     |

|           | Shadow RAM                                          |     |

|           | 384-kb Relocation                                   |     |

|           | EMS 4.0 Memory Management                           |     |

| Chapter 4 | AT Support Logic                                    | 4-1 |

|           | NMI and Port B Logic                                | 4-1 |

|           | Port B Register                                     |     |

|           | NMI Enable Register                                 |     |

|           | Speaker Interface                                   |     |

|           | Device and CPU Reset                                |     |

|           | Device Hardware Reset                               |     |

|           | CPU-Only Reset Control                              |     |

|           | A20 Address Control                                 |     |

|           | AT Standard A20 Control                             |     |

|           | Fast Gate A20 Support                               |     |

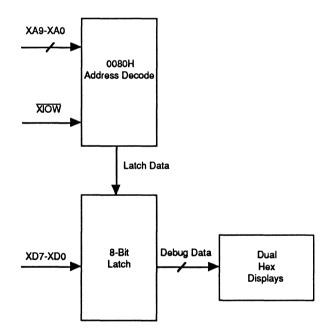

|           | Manufacturing Debug Port                            |     |

| Chapter 5 | External Bus Interfaces                             | 5-1 |

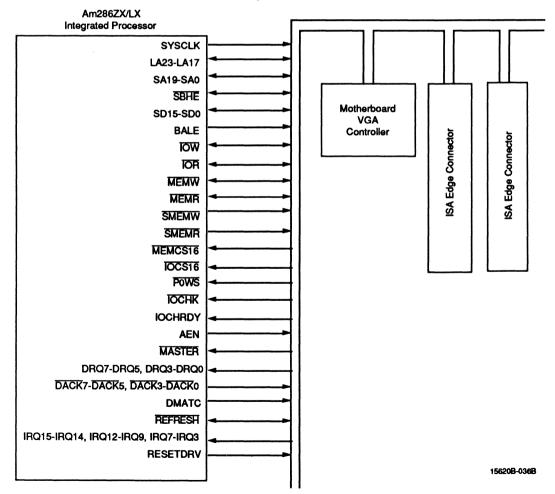

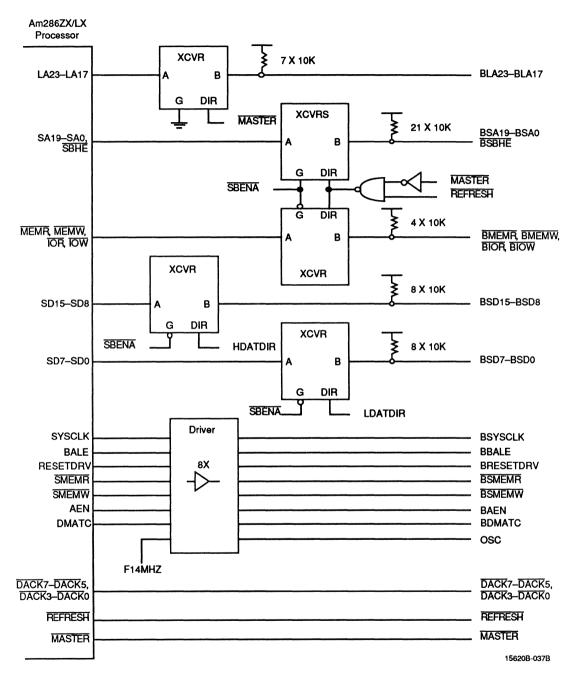

| •         | AT System Bus (S Bus) Connection                    |     |

|           | Configuration                                       |     |

|           | Direct Connection                                   |     |

|           | Buffered Connection                                 |     |

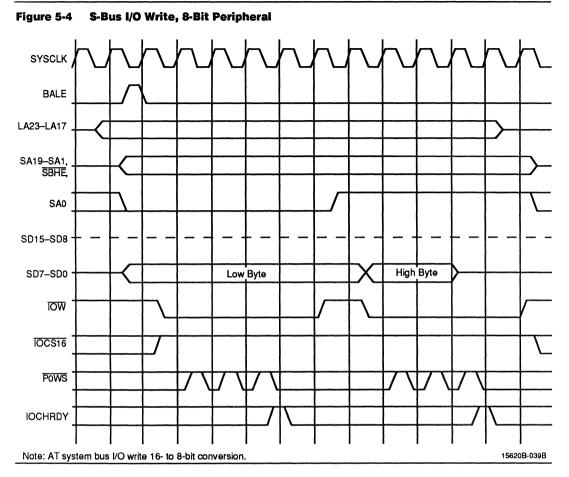

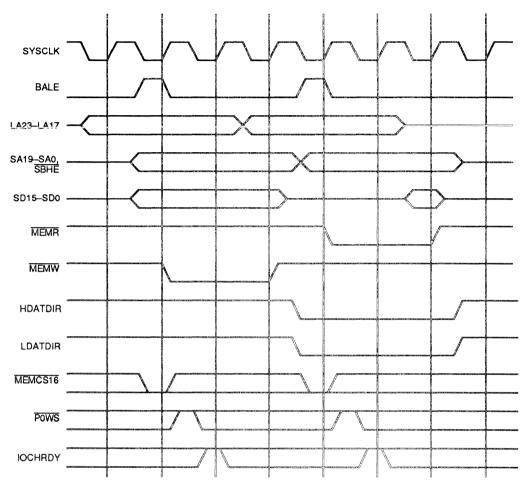

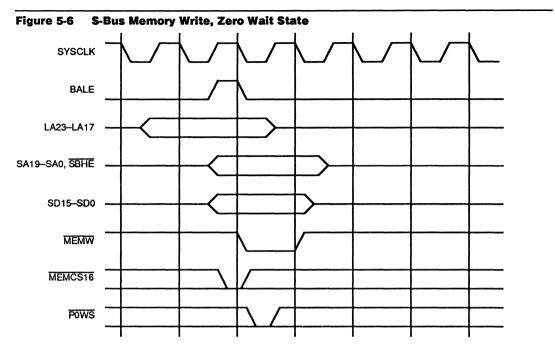

|           | S-Bus Cycles                                        |     |

|           | CPU Cycles                                          |     |

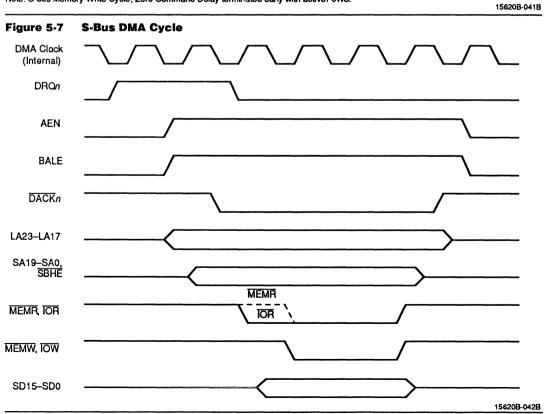

|           | DMA Cycle                                           |     |

|           | Refresh Cycle                                       |     |

|           | Bus Master Cycle                                    |     |

|           |                                                     |     |

| Chapter 6 | Peripheral Expansion Bus (X Bus)                    | 6-1 |

|           | Keyboard Controller Interface                       |     |

|           | Mode Selection                                      | 6-1 |

|           | AT Mode Connection                                  |     |

|           | AT Mode Bus Cycles                                  |     |

|           | XT Mode Direct Keyboard Interface                   | 6-3 |

|           | XT Mode Cycles                                      | 6-4 |

|           | Math Coprocessor Interface                          |     |

|           | Interface Control Functions                         |     |

|           | Connection                                          | 6-4 |

|           | Bus Cycles                                          | 6-5 |

|           | ROM/EPROM Interface                                 | 6-5 |

|           | Functional Description                              |     |

|           | Connection (8 bit and 16 bit)                       |     |

|           | Bus Cycles                                          |     |

|           | Other X-Bus Peripherals                             |     |

|           | Functional Description                              |     |

|           | Connection                                          |     |

|           | Bus Cycles                                          |     |

|           | -                                                   |     |

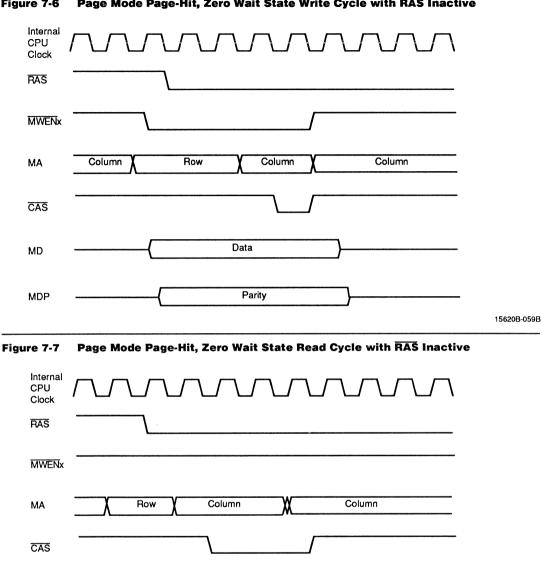

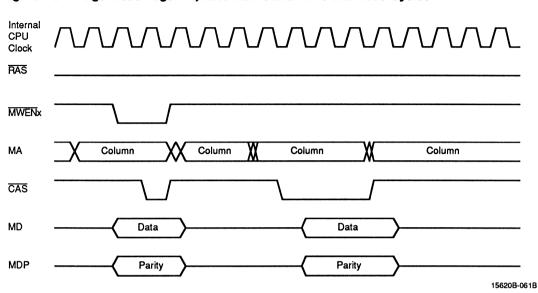

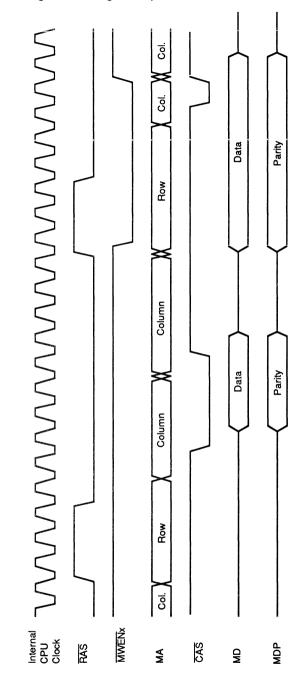

| Chapter 7  | Memory Bus (M Bus)                                          | 7-1 |

|------------|-------------------------------------------------------------|-----|

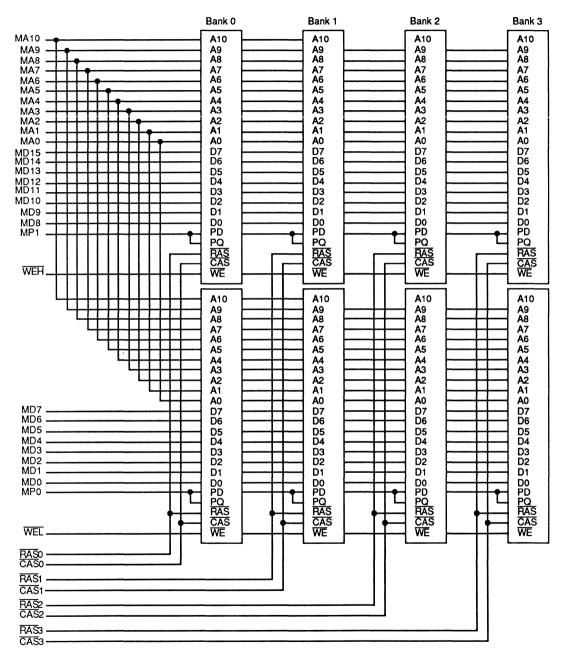

|            | DRAM Interface                                              | 7-1 |

|            | Connection (2/4 Bank)                                       |     |

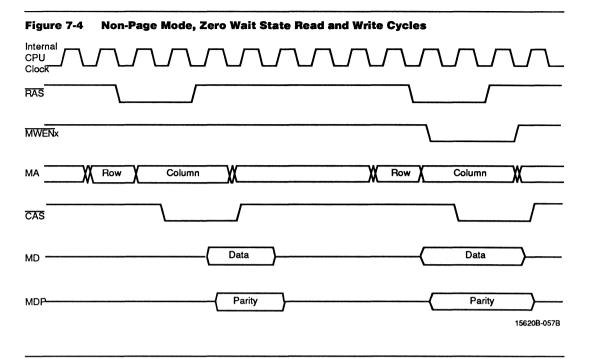

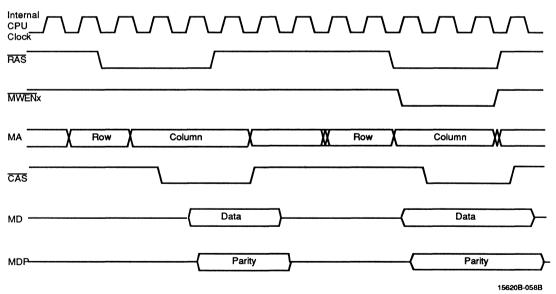

|            | DRAM Cycles                                                 |     |

|            | Other Connections                                           | 7-2 |

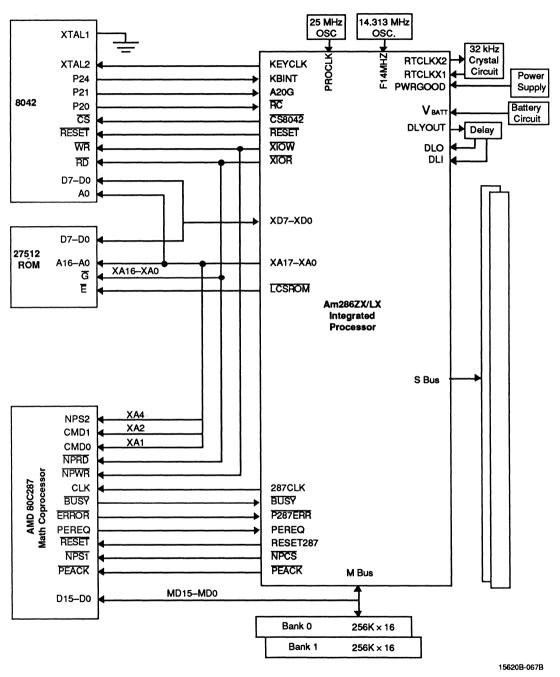

| Chapter 8  | System Configurations                                       | 8-1 |

|            | System Block Diagrams                                       |     |

|            | Introduction                                                |     |

|            | Keyboard Interface                                          |     |

|            | ROM Interface                                               |     |

|            | AMD 80C287 Math Coprocessor Interface                       |     |

|            | Local Memory Interface<br>ISA Expansion Bus Interface       |     |

|            | Clock, Reset, and Delay Line Circuitry                      |     |

|            | Configuration Register Initialization                       |     |

|            | Introduction                                                |     |

|            | Cycle Control Group                                         |     |

|            | Clock Control Group                                         |     |

|            | General Setup                                               |     |

| Chapter 9  | Bios Programming Guidelines                                 | 9-1 |

| a          | Introduction                                                |     |

|            | Initialization                                              |     |

|            | Speed Switching                                             |     |

|            | Fast Reset and Gate A20                                     | 9-1 |

|            | X-Bus Peripherals                                           |     |

|            | Power Save Features                                         |     |

|            | EMS 4.0 Register Programming                                |     |

|            | XT Keyboard Interface Programming                           | 9-2 |

| Chapter 10 | System Support Products                                     |     |

|            | Hewlett Packard In-Circuit Emulator (ICE)                   |     |

|            | Phoenix Technologies Systen BIOS and EMS 4.0 Driver         |     |

|            | AMP Incorporated 216-Position MCR TapePak Production Socket |     |

|            | Advanced Micro Devices Mercury/286ZLX Development Kit       |     |

| Appendix A | Standard Logic Literature References                        | A-1 |

| Appendix B | Configuration Register Reference                            | B-1 |

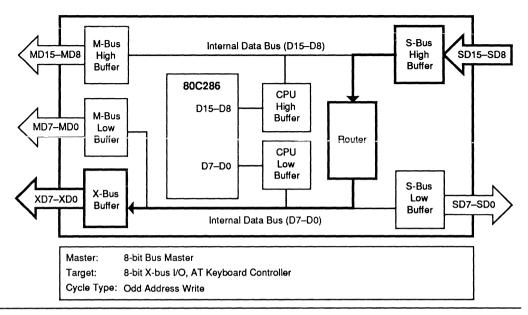

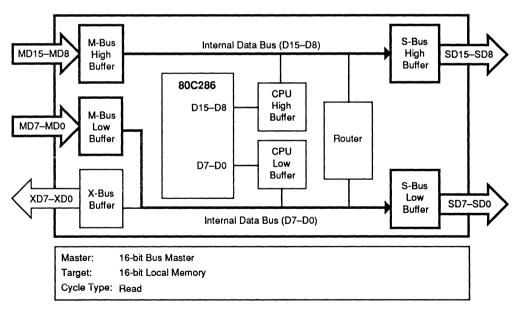

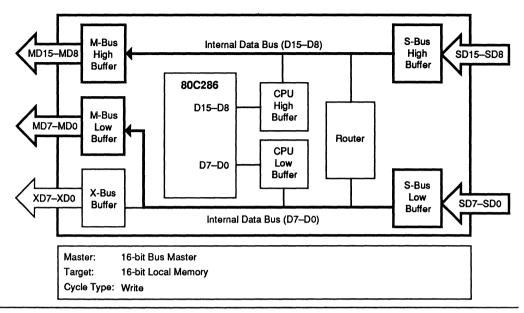

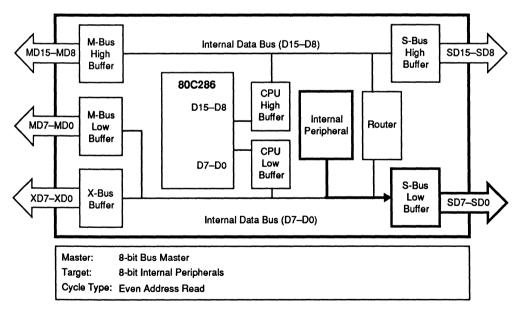

| Appendix C | Transfer Cycle Reference                                    | C-1 |

| Appendix D | Pin Buffer Reference                                        | D-1 |

| Appendix E | Quick References                                            | E-1 |

# INTRODUCTION

# **DESIGN GOALS**

The Am286ZX/LX integrated processor integrates all of the logic functions on the original AT motherboard, along with enhancements in operational speed, memory management, DRAM requirements, and configurability. AMD's goal was the integration of all "non-memory-based" functional blocks (not including the DRAMs, BIOS EPROMs, or the ROM-based 8042 keyboard controller) onto a single CMOS device.

As AMD was already producing the logic functions contained in the AT design as individual silicon devices, development of the Am286ZX/LX integrated processor was the next logical step. Also, AMD had the manufacturing and packaging technology to place all of these devices, along with flexible control logic, into a single silicon device.

Target markets for the Am286ZX/LX integrated processor shaped its feature set, taking it beyond just integrating a standard AT design. The prime system targets for the Am286ZX/LX integrated processor are 80286-based hand-held, notebook, and laptop computer systems. Another system target, due to the nature of the functional units that were combined into a single device, is the "embedded computer" system, where integration, ease of implementation, and power consumption are critical system issues.

The system requirements for these target markets prompted AMD to extend the definition of the Am286ZX/LX integrated processor to include high-speed operation with standard DRAM and system bus speeds, direct interconnection with other devices on the motherboard, and the power saving features of the Am286LX processor version.

AMD's design goals for this project were ease of implementation, low total system cost, high reliability, and strict compatibility. These design goals mapped directly into the following device specific goals.

- Direct interface of memory-based devices within the system (DRAM, EPROM, and 8042 controller).

- A triple bus design for minimizing the need for external buffers and transceivers.

- An AT-compatible bus controller with both synchronous and asynchronous operation for ease of system implementation at all CPU/system bus speed combinations.

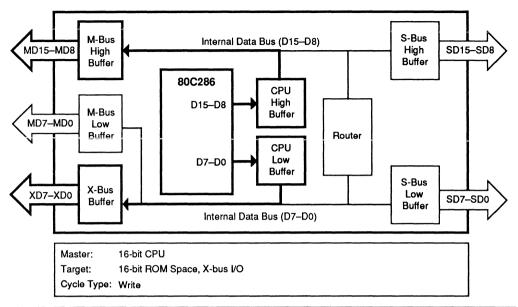

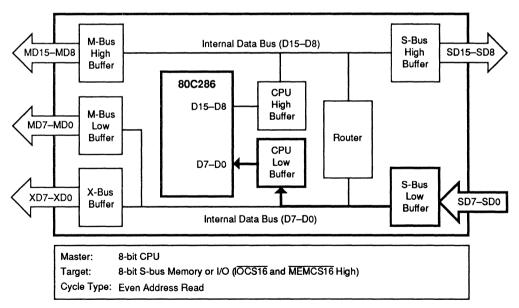

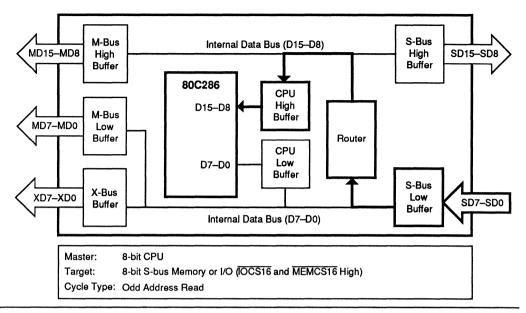

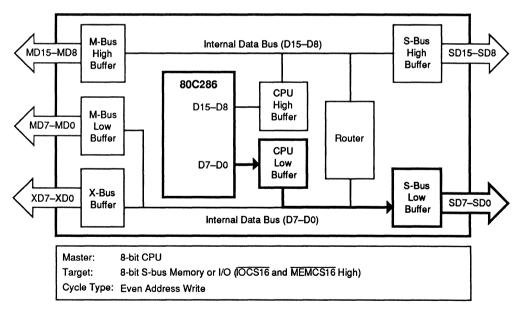

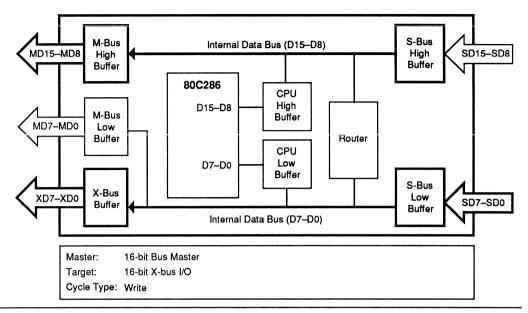

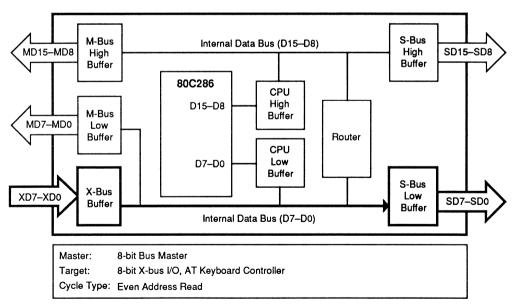

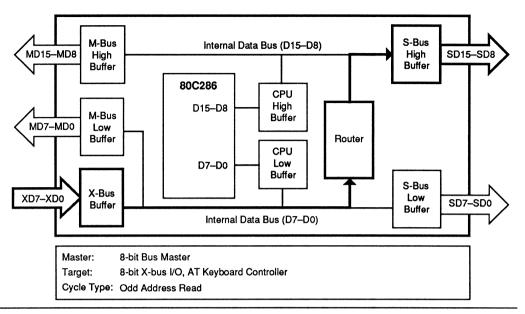

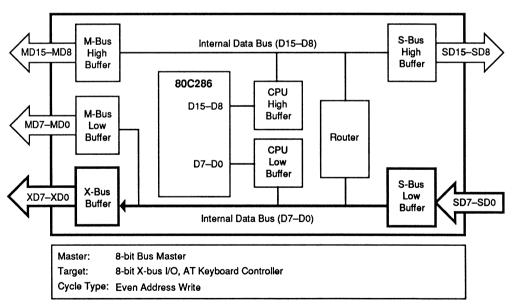

- Fail-safe internal data routing, guaranteeing that data bus contention will not happen.

- DRAM size mixing without limitations.

- · Flexible clocking options with fail-safe clock speed switching.

- Power savings by controlling internal clocks and minimizing DRAM power consumption during refreshes.

- Device configurability via software for interfacing to various speeds of DRAM, ROM, and system peripherals.

These design goals molded the Am286ZX/LX integrated processor into a system solution that breaks new ground in the integration of the PC-AT system function, surpassing other solutions forced to stop at the processor boundary. This device's adaptability to a wide variety of system environments and requirements make it an ideal solution for the implementation of 80286 microprocessor-based, AT-compatible systems.

# **DISTINCTIVE CHARACTERISTICS**

- Integrates entire IBM PC-AT motherboard logic plus enhancements.

- -80C286 Microprocessor core

- -Enhanced Bus Controller

- -Enhanced Clock Generator

- -DMA Controllers

- -Interrupt Controllers

- ---Counter/Timer

- -Real Time Clock and CMOS Static RAM

- Direct connection to DRAM, AMD 80C287<sup>™</sup> math coprocessor, EPROMs, keyboard controller, and AT-bus slots for a complete AT-compatible system.

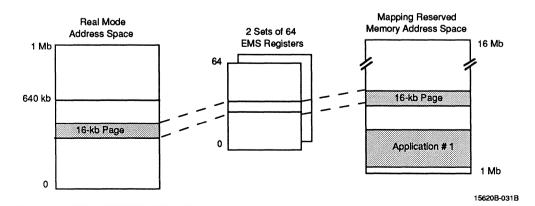

- Full hardware support for EMS 4.0 memory management with 128 EMS registers.

- 100% compatible with the IBM PC-AT standard.

- Low power operation with power saving features for battery powered systems (Am286LX processor only).

- Industry standard I/O port 92H fast reset and GATE A20 features for high-speed switching between real and protected mode.

- Page mode/interleave DRAM Controller with direct interface to 256-kbit, 1-Mbit, and 4-Mbit DRAMs supports up to 16 Mb of physical memory.

- Complete line of support products available including Demo Boards, ICE, BIOS, and EMS Drivers.

- 28mm x 28mm, 216-Pin EIAJ Plastic Quad Flat Pack (PQFP), with socket available.

# **GENERAL DESCRIPTION**

The Am286ZX and Am286LX integrated processors are AMD proprietary PC-AT motherboard-on-a-chip devices for personal computers. They integrate all of the logic functions from the original IBM PC-AT motherboard, plus enhancements, onto one chip. Included are the 80C286 microprocessor, all of the AT standard peripherals, and memory management, to provide a high-performance, low-cost, low-power system solution for personal computers. The high integration of the Am286ZX/LX processor allows designers to reduce size, power consumption, and cost of a PC-AT compatible system while increasing functionality and adding features.

The Am286ZX/LX integrated processor is ideal for design of hand-held, notebook, laptop, embedded, and other industry standard AT personal computers where performance, size, power consumption, and cost are critical factors. The Am286LX processor version provides additional power-saving features including CPU shutdown mode, system shutdown mode, staggered DRAM refresh, and slow-refresh DRAM support.

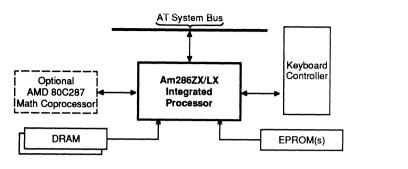

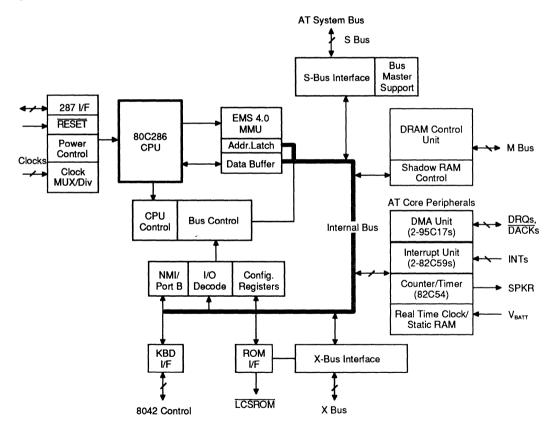

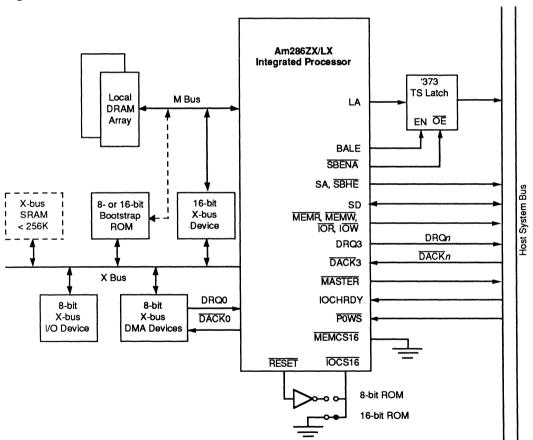

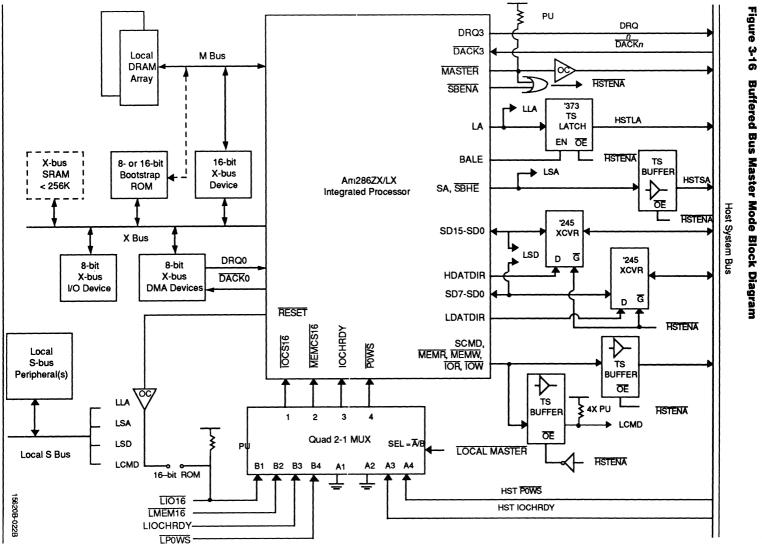

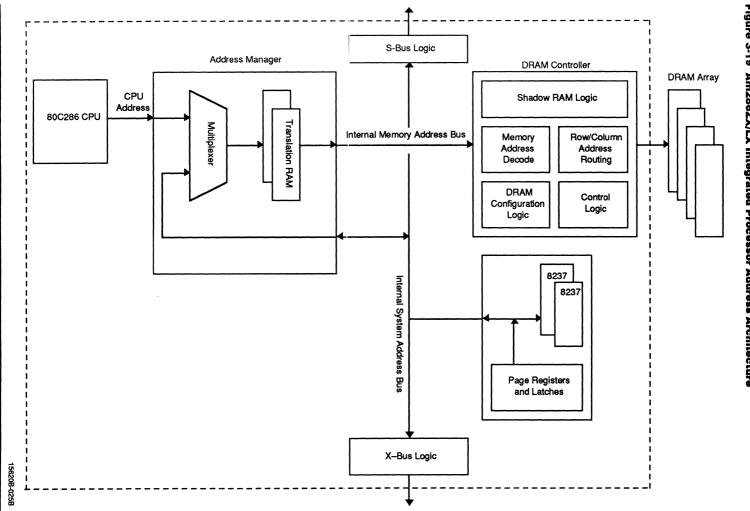

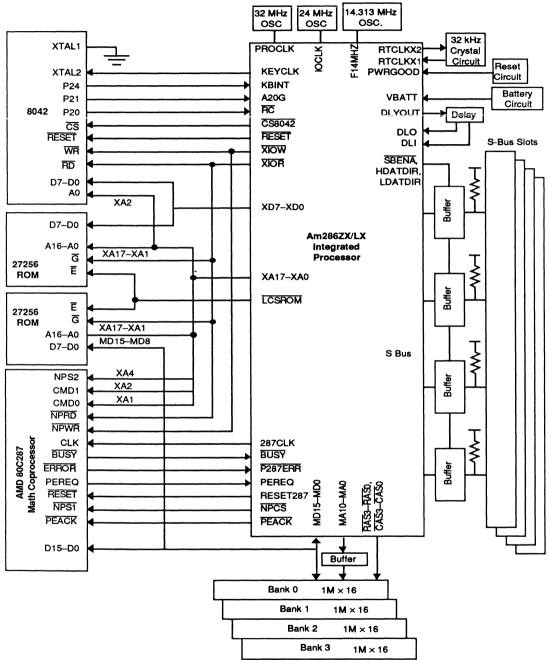

Figure 1-1 shows a system block diagram for an AT motherboard illustrating the high level of integration achieved by the Am286ZX/LX integrated processor.

Figure 1-1 PC-AT System Block Diagram Using the Am286ZX/LX Integrated Processor

14753C--001

14753C--003

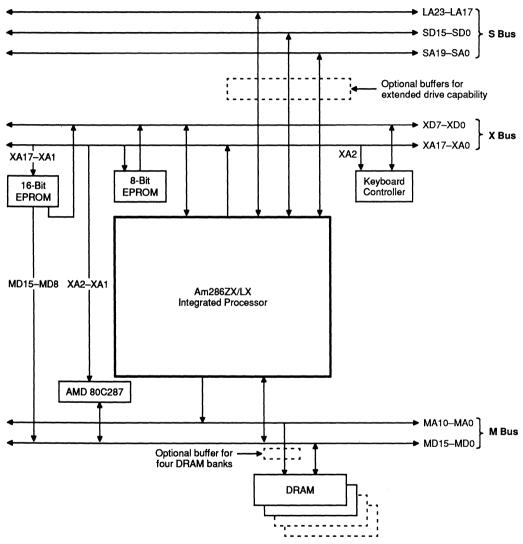

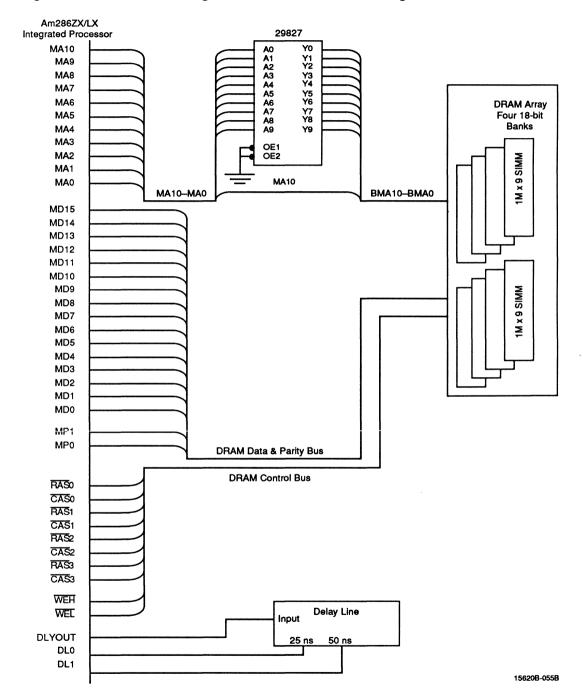

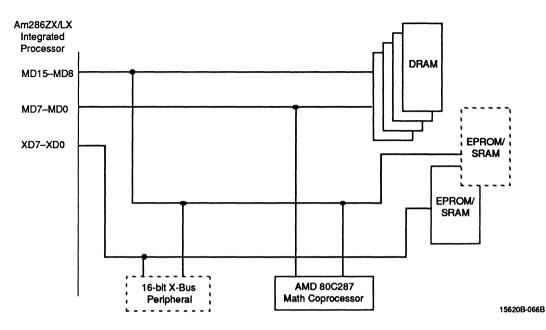

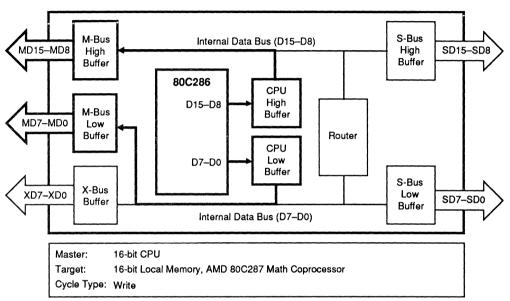

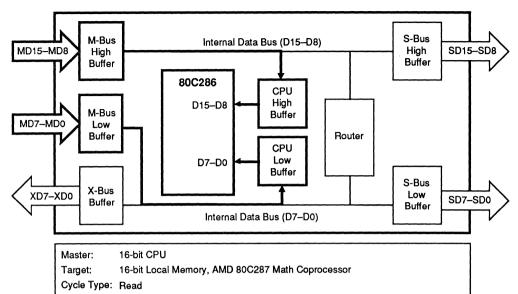

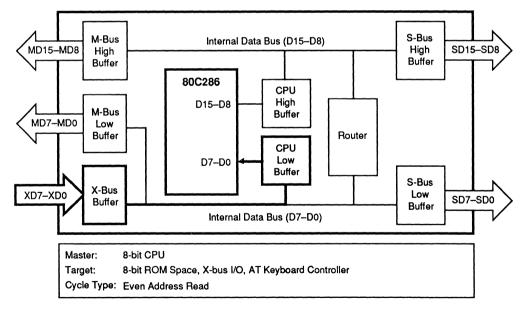

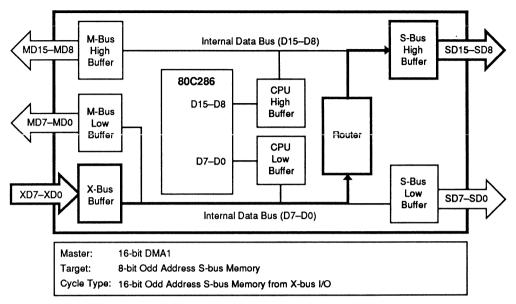

Figure 1-3 shows the Am286ZX/LX integrated processor bus interface. The AT system bus (S Bus), memory bus (M Bus), and I/O Bus (X Bus) directly interface to the rest of the system components. Optional buffers are shown for applications that require extended S-bus drive capability and/or four DRAM banks.

#### Figure 1-3 Am286ZX/LX Integrated Processor Bus Interface

14753C-002

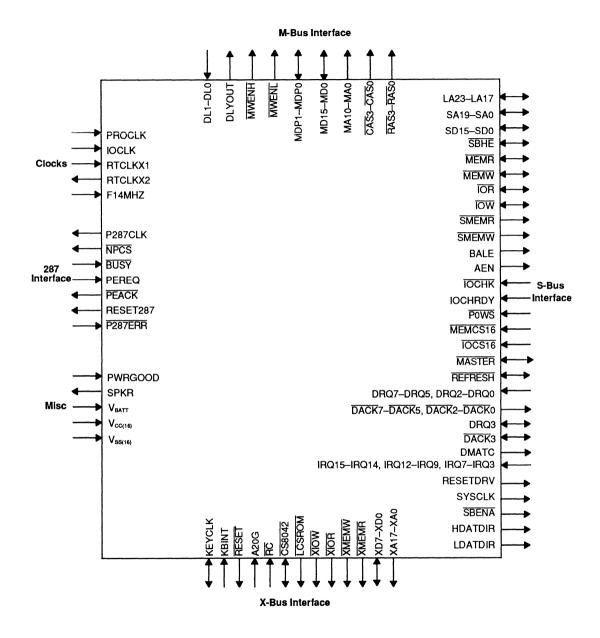

Figure 1-4 Am286ZX/LX Integrated Processor Logic Symbol

14753C-004

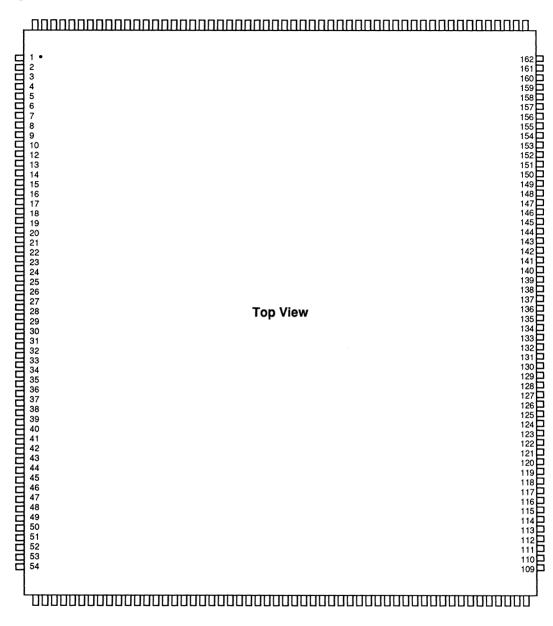

#### Figure 1-5 Am286ZX/LX Integrated Processor Connection Diagram

Note: Pin 1 is marked for orientation.

14753C-005

| Pin NoPin NoPin NoPin NoPin NoPin NoPin NoPin No1LDATDIR56V.c.111SA18166MDP13MASTER58XA12113SA19168SD034DRO759XA11114LA19169SD155DACK760XA10115LA20170SD26DRO661XA9116LA21171SD37DACK662XA8117LA22172SD49DACK564XA7118LA23175SD7110DRO665XA3122V.c.177SD59DACK668XA2122PK2178SD914MEMR69XA1124PK52179SD115DACK668XA2123PK52193SD116IRO1471V.c.126CA51182SD117IRO1572V.s.126CA51182SD118IRO1273MA0128V.s.184SD119IRO1474MA1129CA52186SD120IRO1576MA2130CA53186V.s.21IRO1577MA4132IMENTH180V.s.22IRO1675MA2136V.s.126 <th>rigure 1-6</th> <th colspan="4">Pin Designation Table (by pin number)</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rigure 1-6 | Pin Designation Table (by pin number) |         |                 |         |                 |         |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------|---------|-----------------|---------|-----------------|---------|----------|

| 2         SBENA         57         Vaster         112         LA18         157         MDP1           3         MASTER         58         XA12         113         SA19         168         SO0           4         DACK7         60         XA10         115         LA20         170         SD2           5         DACK7         60         XA10         115         LA20         170         SD3           6         DRG6         62         XA8         117         LA22         172         SD4           8         DRG6         62         XA8         117         LA22         173         SD5           9         DACK5         64         XA6         119         RASS         177         Vaster           10         DRO6         65         XA3         122         Vaster         177         Vaster           111         Vaster         66         XA4         121         Vaster         177         Vaster         177         Vaster         177         Vaster         178         SD7           114         MEMR         69         XA11         124         RAS3         180         SD11         151 </th <th>Pin No.</th> <th>Pin Name</th> <th>Pin No.</th> <th>Pin Name</th> <th>Pin No.</th> <th>Pin Name</th> <th>Pin No.</th> <th>Pin Name</th> | Pin No.    | Pin Name                              | Pin No. | Pin Name        | Pin No. | Pin Name        | Pin No. | Pin Name |

| 3         MASTER         58         XA12         113         SA10         168         SD0           4         DRO7         59         XA11         114         LA19         169         SD1           5         DRO6         61         XA9         116         LA21         171         SD2           6         DRO6         61         XA9         116         LA21         172         SD3           7         DACK6         62         XA8         118         LA22         173         SD5           9         DACK5         64         XA6         119         PAS5         177         Va           10         DRO0         65         XA5         120         RA51         176         Vac           11         Vac         67         XA3         121         Vac         177         Vas         SD6           12         Vas         67         XA3         122         Vas         177         Vas         SD10           13         DACK0         68         XA2         123         RA52         178         SD10           14         MEMI         194         RO14         71         Vac                                                                                                                                                                     | 1          |                                       | 56      | V <sub>cc</sub> | 111     | SA18            | 166     | MDPo     |

| 3         MASTER         58         XA12         113         SA19         168         SD0           4         DRO7         59         XA11         114         LA19         170         SD2           5         DROF         60         XA10         115         LA20         170         SD2           6         DROF         61         XA9         116         LA21         171         SD3           7         DACK6         62         XA3         118         LA22         173         SD5           9         DACK5         64         XA6         119         FAS0         176         Va           10         DRO0         65         XA5         120         FAS1         176         Va           11         Vac         66         XA4         121         Vas         177         Vas           13         DACK0         68         XA2         123         FAS3         180         SD10           15         MEMR         69         XA1         124         FAS3         180         SD14           16         MEMR         70         Xa0         125         CAS5         180         SD14 </td <td>2</td> <td>SBENA</td> <td>57</td> <td>V<sub>ss</sub></td> <td>112</td> <td>LA18</td> <td>167</td> <td>MDP1</td>                                         | 2          | SBENA                                 | 57      | V <sub>ss</sub> | 112     | LA18            | 167     | MDP1     |

| 4         DRQ7         59         XA11         114         LA19         169         SD1           5         DACK7         60         XA10         115         LA20         170         SD2           6         DPO6         61         XA9         116         LA21         171         SD3           7         DACK6         62         XA8         117         LA22         173         SD5           8         DRO6         63         XA7         118         LA21         176         SD7           9         DACK5         64         XA6         119         FA35         176         SD7           11         Vcc         66         XA4         121         Vcc         177         Vas           13         DACK0         68         XA2         122         Vas         178         SD8           14         MEMR         69         XA1         124         FA35         180         SD11           16         IRQ14         71         Vcc         126         CA35         180         SD13           174         MEMW         70         XA0         128         Vas         184         SD14 </td <td>3</td> <td>MASTER</td> <td>58</td> <td>XA12</td> <td>1</td> <td></td> <td>168</td> <td>SD0</td>                                                         | 3          | MASTER                                | 58      | XA12            | 1       |                 | 168     | SD0      |

| 5         DĂCK7         60         XA10         115         LA20         170         SD2           6         DRO6         61         XA9         116         LA21         171         SD3           7         DACK6         62         XA8         117         LA22         172         SD4           8         DRO5         63         XA7         118         LA23         174         SD5           9         DÄCK5         64         XA6         120         RÄ51         175         SD7           10         DRO6         65         XA3         122         Vas         178         SD8           11         Vcs         67         XA3         122         Vas         177         Vas           13         DACK0         68         XA2         123         RÄ52         179         SD9           14         MEMW         70         XA0         125         CÄ50         181         SD14           15         IRC14         71         Vas         127         Vas         183         SD13           16         IRC15         72         Vas         127         Vas         183         SD14 <td>4</td> <td>DRQ7</td> <td>59</td> <td>XA11</td> <td></td> <td></td> <td>169</td> <td>SD1</td>                                                                  | 4          | DRQ7                                  | 59      | XA11            |         |                 | 169     | SD1      |

| 6         DR06         61         XA9         116         LA21         171         SD3           7         DACK6         62         XA9         117         LA22         172         SD4           9         DACK5         64         XA6         119         FAS30         173         SD5           9         DACK5         64         XA6         119         FAS30         175         SD7           10         DR00         65         XA4         121         Vac         176         Vac           11         Vac         66         XA4         121         Vac         177         Vas           13         DACK0         68         XA2         123         FAS2         179         SD8           14         MEMF         69         XA1         124         FAS30         180         SD10           15         MEMT         70         XA0         125         CAS30         181         SD11           16         IRO14         71         Vac         127         Vac         183         SD13           17         Vas         127         Vac         183         SD14         SD14                                                                                                                                                                          | 5          | DACK7                                 |         |                 |         |                 | 170     | SD2      |

| 7         DACK6         62         XA8         117         LA22         172         SD4           8         DROS         63         XA7         118         LA23         174         SD5           9         DACK5         64         XA6         119         FAS0         175         SD7           10         DRQ0         65         XA5         120         FAS1         176         Vac           12         Vas         67         XA3         122         Vas         177         SD9           13         DACK0         68         XA2         123         HA52         179         SD9           14         MEMW         70         XA0         125         CAS0         181         SD11           15         MEMW         70         XA0         122         CAS2         188         SD13           16         IRO14         71         Yac         183         SD13         SD5           17         IRO15         72         Vas         127         Vac         184         SD14           171         ICOS16         76         MA3         131         IMWENT         189         Vas                                                                                                                                                                        | 6          | DRQ6                                  |         |                 |         |                 | 171     | SD3      |

| B         DROS         E3         XA7         118         LA23         173         SD5           9         DACK5         64         XA6         119         FAS0         175         SD7           10         DRQ0         65         XA5         120         FAS1         176         Voc           11         Voc         66         XA4         121         Voc         177         Vas           13         DACK0         68         XA2         123         FAS2         179         SD8           14         MEMR         69         XA1         124         FAS3         180         SD10           15         MEMR         69         XA1         124         FAS3         180         SD11           16         IRO14         71         Voc         126         CAS1         182         SD12           17         IRO15         76         MA2         130         CAS2         183         SD14           18         IRO11         74         MA1         129         Voc         183         SD14           190         IRO10         75         MA42         130         CAS2         180 <t< td=""><td></td><td></td><td></td><td>1</td><td>1</td><td></td><td>172</td><td>SD4</td></t<>                                                                       |            |                                       |         | 1               | 1       |                 | 172     | SD4      |

| 9         DACK5         64         XA6         110         PAS0         174         SD6           10         DR00         65         XA5         120         PAS1         175         SD7           11         Vcc         66         XA4         121         Vcc         177         SD7           12         Vst         67         XA3         122         Vst         177         SD8           13         DACK0         68         XA4         121         Vst         178         SD8           14         MEMP         69         XA1         124         PAS2         179         SD9           15         MEMW         70         XA0         125         CAS1         183         SD11           16         IRO11         74         MA1         129         CAS2         188         SD15           20         IRO10         75         MA4         131         IWENT         188         RTCLX41           21         IOOST6         76         MA3         131         IWENT         188         RTCLX41           22         MEMCST6         77         MA4         132         IWMENT         189                                                                                                                                                              | 8          |                                       |         | 1               |         |                 | 173     | SD5      |

| 10         DRAG         65         XAG         113         PAGS         175         SD7           11         Vac         66         XA4         121         Vac         177         Vas           12         Vas         67         XA3         122         Vas         178         SD8           13         DACK0         68         XA2         123         FAS2         179         SD9           14         MEMR         69         XA1         124         FAS3         180         SD10           15         MEMW         70         XA0         125         CAS0         181         SD11           16         IRO14         71         Vcc         126         CAS1         182         SD12           17         IRO15         72         Vca         123         CAS2         185         SD14           181         IRO11         75         MA2         130         CAS2         185         SD14           20         IRO16         75         MA2         133         DLYOUT         190         Vac           21         IOCST6         76         MA3         134         DL0         Uar                                                                                                                                                                     |            |                                       |         | 1               |         |                 | 174     | SD6      |

| 11 $V_{xc}$ 66         XA4         121 $V_{xc}$ 177 $V_{xs}$ 12 $V_{xs}$ 67         XA3         122 $V_{xs}$ 178         SD8           13         DACK0         68         XA2         123         FAS2         179         SD9           14         MEMR         69         XA1         124         FAS3         180         SD10           15         MEMW         70         XA0         125         CAS1         182         SD12           16         IRQ14         71         V $_{cc}$ 126         CAS1         182         SD12           177         IRQ15         72         V $_{xs}$ 127         V $_{cc}$ 183         SD14           19         IRQ11         74         MA1         129         CAS2         185         Vatr           21         IOCS16         75         MA3         131         MWENL         187         PTCLKX1           22         MEMCST6         77         MA4         132         MWENH         188         V <sub>atr</sub> 21         IOCST6         76         MA3         131                                                                                                                                                                                                                                                  |            |                                       |         |                 |         | 1               | 175     | SD7      |

| 12 $V_{as}$ 67         XA3         121 $V_{as}$ 178         SD8           13         DACKO         68         XA2         123         FAS2         179         SD9           14         MEMR         69         XA1         124         FAS3         180         SD10           15         MEMW         70         XA0         125         CAS0         181         SD11           16         IPQ14         71         Vcc         126         CAS1         182         SD12           177         IRQ15         72         Vsc         183         SD13         SD13           18         IPQ12         73         MA0         128         Vsc         183         SD15           20         IRQ10         75         MA2         130         CAS3         186         Vurr <ttttt< td="">           21         IOCS16         77         MA4         132         WWENH         188         PTCLKN2           23         SBHE         78         Vcc         133         DLOUT         190         Vss           24         BALE         79         Vss         134         DL0         191</ttttt<>                                                                                                                                                                         |            |                                       |         |                 |         |                 |         |          |

| 13         DACK0         66         XA2         123         Pass<br>PAS2         179         SD9           14         MEMR         69         XA1         124         FAS3         180         SD10           15         MEMW         70         XA0         125         CAS0         181         SD11           16         IRQ14         71         V <sub>cc</sub> 126         CAS1         182         SD12           17         IRQ15         72         V <sub>ss</sub> 127         V <sub>cc</sub> 183         SD13           18         IRQ11         74         MA1         129         V <sub>cs</sub> 184         SD14           20         IPQ10         75         MA2         130         CAS2         185         SD15           21         IOCS16         76         MA3         131         MWENL         187         PTCLKX1           22         MEMCS16         77         MA4         132         MWENT         189         V <sub>cc</sub> 23         SBRE         78         V <sub>cc</sub> 133         DLYOUT         189         V <sub>cc</sub> 24         BALE         79         V <sub>ss</sub> 133         DLYOUT                                                                                                                               |            |                                       |         | 1               |         |                 |         |          |

| 14         MEMR         69         XA1         124         PAXS         179         SD9           15         MEMW         70         XA0         125         CAS0         181         SD10           16         IRQ14         71         Voc         126         CAS1         182         SD12           17         IRQ15         72         Voc         126         CAS2         183         SD13           18         IRQ12         73         MA0         128         Voc         183         SD15           20         IRQ10         75         MA2         130         CAS2         186         Voc           21         ICCS76         76         MA3         131         MWENIC         187         RTCLKX1           22         MEMCS16         77         MA4         132         WWENNH         188         RTCLKX2           23         SBRE         78         Voc         133         DLYOUT         190         Vos           24         BALE         79         Vos         133         DL         191         LCSNDM           25         DMATC         80         MA5         134         DL0                                                                                                                                                                |            |                                       |         | 1               |         |                 |         |          |

| 15         MEMW         70         XA0         125         CAS0         181         SD11           16         IRQ14         71         V <sub>GC</sub> 126         CAS1         182         SD12           17         IRQ15         72         V <sub>SS</sub> 127         V <sub>GC</sub> 183         SD13           18         IRQ12         73         MA0         128         V <sub>SS</sub> 184         SD14           19         IRQ10         75         MA2         130         CAS3         186         V <sub>Aur</sub> 21         ICCST6         76         MA3         131         IWENL         187         RTCLKX1           223         SBHE         78         V <sub>CC</sub> 133         DL/YOUT         188         RTCLKX2           24         BALE         79         V <sub>SS</sub> 136         V <sub>SS</sub> 192         XMEMW           26         DACK2         81         V <sub>CC</sub> 136         V <sub>SS</sub> 192         XMEMW           27         V <sub>CC</sub> 82         V <sub>SS</sub> 137         DL1         193         XIMEMW           26         DACK2         81         V <sub>CC</sub> 138                                                                                                                           |            |                                       |         | 1               |         |                 | 1       |          |

| 16         IRQ14         71         Vac         126         CAS1         182         SD12           17         IRQ15         72         Vss         127         Vcc         183         SD13           18         IRQ12         73         MA0         128         Vss         184         SD14           19         IRQ11         74         MA1         129         CAS2         185         SD15           20         IRQ10         75         MA2         130         CAS3         186         Varr           21         ICCS16         76         MA3         131         IWWENL         187         RTCLKX1           22         MEMCS16         77         MA4         132         IWWENL         188         FTCLKX1           23         SBRE         78         Vcc         133         DL/OUT         190         Vss           24         BALE         79         Vss         134         DL0         191         LCSROM           26         DACK2         81         Vac         136         Vss         193         XMEMP           27         Vcc         82         Vss         138         XD0 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                      |            |                                       |         |                 |         |                 |         |          |

| 17         IRQ15         72 $V_{ss}$ 127 $V_{cc}$ 183         SD13           18         IRQ12         73         MA0         128 $V_{ss}$ 184         SD14           19         IRQ11         74         MA1         129         CAS2         185         SD15           20         IRQ10         75         MA2         130         CAS3         186 $V_{wrr}$ 21         ICOS16         76         MA3         131         MWENT         187         RTCLKX1           22         MEMCS16         77         MA4         132         MWENT         189 $V_{cc}$ 23         SBHE         78         V_{cc}         133         DLYOUT         189 $V_{cc}$ 24         BALE         79         V_{ss}         133         DLYOUT         189 $V_{cc}$ 25         DMATC         80         MA5         133         DLYOUT         199         Vss           26         DACK2         81 $V_{cc}$ 138         XD0         194         CS8042           27 $V_{cc}$ 82         V_ss                                                                                                                                                                                                                                                                                              |            |                                       |         |                 | 1       | 1               |         |          |

| 18         IRQ12         73         MA0         128         Vast<br>Vast         184         SD14           19         IRQ11         74         MA1         129         CAS2         185         SD15           20         IRQ10         75         MA2         130         CAS3         186         Vast           21         ICOS16         76         MA3         131         MWENL         187         RTCLKX1           22         MEMCS16         77         MA4         132         MWENH         188         RTCLKX1           23         SBHE         78         Vcc         133         DLYOUT         190         Vss           24         BALE         79         Vss         133         DLYOUT         190         Vss           26         DACK2         81         Vcc         136         Vss         192         XMEMR           27         Vcc         82         Vss         137         DL1         193         XMEMR           28         Vss         83         MA6         138         XD0         194         CS8042           30         IRQ4         85         MA8         140         XD2                                                                                                                                                        |            |                                       |         |                 |         | 1               | 4       |          |

| 19         IRQ11         74         MA1         129         CAS2         185         SD15           20         IRQ10         75         MA2         130         CAS3         186         Varr           21         ICOCST6         76         MA3         131         MWENL         187         RTCLKX1           22         MEMCST6         77         MA4         131         MWENH         188         RTCLKX2           23         SBHE         78         Vcc         133         DLYOUT         189         Vcc           24         BALE         79         Vas         136         Vcc         191         UCSROW           25         DMATC         80         MA5         135         Vcc         192         XMEMW           26         DACR2         81         Vcc         136         Vas         192         XMEMW           27         Vcc         82         Vas         133         XD0         194         CS8042           30         IRQ3         84         MA7         139         XD1         195         XIOR           31         IRQ6         87         MA10         141         XD3 <t< td=""><td></td><td></td><td></td><td></td><td></td><td>V<sub>cc</sub></td><td>1</td><td></td></t<>                                                       |            |                                       |         |                 |         | V <sub>cc</sub> | 1       |          |

| 20         IRQ10         75         MA2         130         CAS3         186         Vart           21         IOCS16         76         MA3         131         MWENL         187         RTCLKX1           23         SBHE         78         Vcc         133         MWENH         188         RTCLKX2           23         SBHE         78         Vcc         133         DLYOUT         189         Vcc           24         BALE         79         Vss         133         DLO         191         LCSROM           25         DMATC         80         MA5         135         Vcc         192         XMEMW           26         DACR2         81         Vcc         138         XDO         194         CSS042           27         Vcc         82         Vss         138         XDO         194         CSS042           29         IRQ3         84         MA7         138         XDO         194         CSS042           30         IRQ4         85         MA8         140         XD2         196         XIOW           31         IRQ5         86         MA9         141         XD3         19                                                                                                                                                       |            |                                       | 5       |                 |         |                 | 1       |          |

| 21         IOCST6         76         MA3         131         MWENL         187         RTCLKX1           22         MEMCST6         77         MA4         132         MWENH         189         RTCLKX1           23         SBHE         78         Vcc         133         DLYOUT         199         Vss           24         BALE         79         Vss         134         DLO         190         Vss           25         DMATC         80         MA5         135         Vcc         191         LCSROM           26         DACK2         81         Vcc         136         Vss         192         XMEMW           27         Vcc         82         Vss         133         DL1         193         XMEM           28         Vss         83         MA6         138         XD0         194         CS8042           30         IRQ3         84         MA7         139         XD1         195         XIOR           31         IRQ5         86         MA9         140         XD2         196         XIOR           32         IRQ6         87         MA10         142         XD4         198 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>1</td> <td></td>                                                                         |            |                                       |         |                 |         |                 | 1       |          |

| 22         MEMCST6         77         MA4         131         MWENL         188         RTCLKX2           23         SBHE         78         Vcc         133         DLYOUT         199         Vcc           24         BALE         79         Vss         133         DLYOUT         199         Vcc           25         DMATC         80         MA5         135         Vcc         191         LCSROM           26         DACK2         81         Vcc         136         Vss         192         XMEMR           27         Vcc         82         Vss         137         DL1         194         CSB042           29         IRQ3         84         MA7         139         XD1         195         XIOR           30         IRQ4         85         MA8         140         XD2         196         XIOW           31         IRQ7         86         MA9         141         XD3         197         RC           32         IRQ6         87         MA10         142         XD4         198         A20G           33         IRQ7         88         Vcc         143         XD5         199                                                                                                                                                               |            |                                       |         |                 | 130     | CAS3            | 1       |          |

| 22         MEMCS16         7/         MA4         132         MWENH         188         H1CLX2           23         SBHE         78         Vcc         133         DLYOUT         190         Vas           24         BALE         79         Vcc         133         DLOUT         190         Vas           25         DMATC         80         MA5         135         Vac         191         LCSROM           26         DACK2         81         Vac         136         Vas         192         XMEMW           27         Vac         82         Vas         136         Vas         193         XMEMR           28         Vas         83         MA6         138         XD0         194         CS8042           29         IRQ3         84         MA7         139         XD1         195         XIOR           31         IRQ5         86         MA9         141         XD3         197         RC           32         IRQ6         87         MA10         142         XD4         198         A20G           33         IRQ7         88         Vas         144         XD6         200                                                                                                                                                                 |            |                                       | 4       |                 | 131     | MWENL           | 1       |          |

| 23         SBHE         78         Vcc         133         DLYOUT         189         Vcc           24         BALE         79         Vss         134         DL0         191         LCSROM           25         DMATC         80         MA5         135         Vcc         191         LCSROM           26         DACK2         81         Vcc         136         Vss         192         XMEMR           27         Vcc         82         Vss         137         DL1         193         XMEMR           28         Vss         83         MA6         138         XD0         195         XIOR           29         IRQ3         84         MA7         139         XD1         195         XIOR           30         IRQ4         85         MA8         140         XD2         196         XIOW           31         IRQ5         86         MA9         141         XD3         197         RC           32         IRQ6         87         MA10         141         XD6         200         KEVCLK           33         IRQ7         88         Vcc         143         XD5         199 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td>1</td><td></td></t<>                                                                              |            |                                       |         |                 |         |                 | 1       |          |

| 24         BALE         79         Vss         134         DL0         190         Vss           25         DMATC         80         MA5         135         Vac         191         LCSROM           26         DACK2         81         Vac         135         Vac         192         XMEMW           27         Vac         82         Vss         137         DL1         193         XMEMW           28         Vss         83         MA6         138         XD0         194         CS8042           29         IRQ3         84         MA7         139         XD1         195         XIOR           30         IRQ4         85         MA8         140         XD2         196         XIOW           31         IRQ5         86         MA9         141         XD3         197         RC           33         IRQ7         88         Vac         142         XD4         198         A206           34         REFRESH         89         Vas         144         XD6         200         KEYCLK           35         DRQ1         90         SA0         144         XD6         203 <t< td=""><td>23</td><td>SBHE</td><td>1</td><td>Vcc</td><td></td><td>1</td><td></td><td></td></t<>                                                                     | 23         | SBHE                                  | 1       | Vcc             |         | 1               |         |          |

| 25DMATC80MA5135 $V_{cc}$ 191LUSHOM26DACK281 $V_{cc}$ 136 $V_{ss}$ 192XMENM27 $V_{cc}$ 82 $V_{ss}$ 137DL1193XMEMR28 $V_{ss}$ 83MA6138XD0194CS804229IRQ384MA7139XD1195XIOR30IRQ485MA8140XD2196XIOW31IRQ586MA9141XD3197RC32IRQ687MA10142XD4198A20G33IRQ788 $V_{cc}$ 143XD5199RESET34REFRESH89Vss144XD6200KEYCLK35DRQ190SA0145XD7201KBINT36SYSCLK91SA1146 $V_{cc}$ 202PWRGOC37DACK192SA2147Vss203PROCLK39DACK394SA4149MD1205F14MHZ40IOR95SA5150MD2206 $V_{cc}$ 41IOR96SA6151MD4208SPKR43SMEMW97SA7152MD4208SPKR43SMEMR98SA8153MD5210NPC544IOCHRDY99SA9154MD6 <td< td=""><td></td><td>BALE</td><td>1</td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | BALE                                  | 1       |                 |         |                 |         |          |

| 26         DACK2         81 $V_{cc}$ 136 $V_{ss}$ 192         XMEMR           27 $V_{cc}$ 82 $V_{ss}$ 137         DL1         193         XMEMR           28 $V_{ss}$ 83         MA6         138         XD0         195         XIOR           29         IRQ3         84         MA7         139         XD1         195         XIOR           30         IRQ4         85         MA8         140         XD2         196         XIOW           31         IRQ5         86         MA9         141         XD3         197         RC           32         IRQ6         87         MA10         142         XD4         198         A20G           33         IRQ7         88 $V_{cc}$ 143         XD5         199         RESET           34         REFRESH         89         Vss         144         XD6         200         KEYCLK           35         DRQ1         90         SA0         145         XD7         201         PWRGOC           37         DACK1         92         SA2         147         Vss                                                                                                                                                                                                                                                     | 25         | DMATC                                 | 80      | MA5             |         |                 | 1       |          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26         | DACK2                                 | 81      | V <sub>cc</sub> |         |                 |         |          |

| 28         Vss         83         MA6         138         XD0         194         CS8042           29         IRQ3         84         MA7         139         XD1         195         XIOR           30         IRQ4         85         MA8         140         XD2         196         XIOW           31         IRQ5         86         MA9         141         XD3         197         RC           32         IRQ6         87         MA10         141         XD3         199         RESET           34         REFRESH         89         Vss         143         XD7         201         KEYCLK           35         DRO1         90         SA0         144         XD6         200         KEYCLK           36         SYSCLK         91         SA1         145         XD7         201         KBINT           36         SYSCLK         91         SA1         145         XD7         201         KBINT           36         DRQ3         93         SA3         148         MD0         204         IOCLK           38         DRQ5         94         SA4         149         MD1         205                                                                                                                                                                 | 27         | V <sub>cc</sub>                       | 82      | V <sub>ss</sub> | 1       | 1               | 193     | XMEMR    |

| 29         IRQ3         84         MA7         139         XD1         195         XIOR           30         IRQ4         85         MA8         140         XD2         196         XIOW           31         IRQ5         86         MA9         141         XD3         197         RC           32         IRQ6         87         MA10         141         XD3         198         A20G           33         IRQ7         88         Vac         143         XD5         199         RESET           34         REFRESH         89         Vas         144         XD6         200         KEYCLK           35         DRQ1         90         SA0         145         XD7         201         KBINT           36         SYSCLK         91         SA1         146         Vac         202         PWRGOC           37         DACK1         92         SA2         147         Vss         203         PROCLK           38         DRQ3         93         SA3         148         MD0         204         IOCLK           39         DACK3         94         SA4         149         MD1         205                                                                                                                                                                 | 28         |                                       | 83      | MA6             |         |                 | 194     | CS8042   |

| 30         IRO4         85         MA8         140         XD2         196         XIOW           31         IRO5         86         MA9         141         XD3         197         RC           32         IRO6         87         MA10         141         XD3         198         A20G           33         IRQ7         88         Vac         142         XD4         198         A20G           34         REFRESH         89         Vas         143         XD5         199         RESET           34         REFRESH         89         Vas         144         XD6         200         KEYCLK           35         DRQ1         90         SA0         145         XD7         201         KBINT           36         SYSCLK         91         SA1         146         Vac         202         PWRGOC           38         DRQ3         93         SA2         147         Vss         203         PROCLK           39         DACK3         94         SA4         149         MD1         205         F14MHZ           40         IOW         95         SA5         150         MD2         206                                                                                                                                                               | 29         |                                       |         |                 |         |                 | 195     | XIOR     |

| 31         IRQ5         86         MA9         141         XD3         197         RC           32         IRQ6         87         MA10         142         XD4         198         A20G           33         IRQ7         88         Vcc         143         XD5         199         RESET           34         REFRESH         89         Vss         144         XD6         200         KEYCLK           35         DRQ1         90         SA0         144         XD6         202         PWRGOC           36         SYSCLK         91         SA1         145         XD7         201         KBINT           38         DRQ3         93         SA3         144         MD0         204         IOCLK           39         DACK3         94         SA4         149         MD1         205         F14MHZ           40         IOW         95         SA5         150         MD2         206         Vcc           41         IOR         96         SA6         151         MD3         207         Vss           42         SMEMW         97         SA7         152         MD4         208                                                                                                                                                                     | 30         | IRQ4                                  |         | 1               |         |                 | 196     | XIOW     |

| 32IRQ687MA10141AD3198A20G33IRQ788 $V_{cc}$ 143XD5199RESET34REFRESH89 $V_{ss}$ 144XD6200KEYCLK35DRQ190SA0145XD7201KBINT36SYSCLK91SA1146 $V_{cc}$ 202PWRGOC37DACK192SA2147 $V_{ss}$ 203PROLK38DRQ393SA3147 $V_{ss}$ 203PROLK39DACK394SA4149MD1205F14MHZ40IOW95SA5150MD2206 $V_{cc}$ 41IOR96SA6151MD3207 $V_{ss}$ 42SMEMW97SA7152MD4208SPKR43SMEMR98SA8153MD5209P227CLK44IOCHRDY99SA9154MD6210NPCS45AEN100SA10155MD7211BUSY46POWS101SA11156MD8212PEREQ47DRQ2102SA15160 $V_{cc}$ 216HDATDIR50IOCHK105SA15160 $V_{cc}$ 216HDATDIR51XA16107SA17162MD12216HDATDIR53XA16107SA1716                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31         | IRQ5                                  | 1       |                 | 1       | 1               | 197     | RC       |

| 33IRQ788 $V_{cc}$ 143XD5199RESET34REFRESH89 $V_{ss}$ 144XD6200KEYCLK35DRQ190SA0145XD7201KBINT36SYSCLK91SA1146 $V_{cc}$ 202PWRGOO37DACK192SA2147 $V_{ss}$ 203PROCLK38DRQ393SA3144MD0204IOCLK39DACK394SA4149MD1205F14MHZ40IOW95SA5150MD2206 $V_{cc}$ 41IOR96SA6151MD3207 $V_{ss}$ 42SMEMW97SA7152MD4208SPKR43SMEMR98SA8153MD5209P287CLK44IOCHRDY99SA9154MD6210NPCS45AEN100SA10155MD7211BUSY46POWS101SA11156MD8212PEREQ47DRQ2102SA15160 $V_{cc}$ 216HDATDIR50IOCHK105SA15160 $V_{cc}$ 216HDATDIR51XA16107SA17162MD12216HDATDIR53XA16107SA17162MD12216HDATDIR54XA16107SA171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32         | IRQ6                                  | 1       |                 | (       | 1               |         |          |

| 34         REFRESH         89         Vss         144         XD6         200         KEYCLK           35         DRQ1         90         SA0         144         XD6         201         KBINT           36         SYSCLK         91         SA1         146         Vcc         202         PWRGOO           37         DACK1         92         SA2         147         Vss         203         PROCLK           38         DRQ3         93         SA3         148         MD0         204         IOCLK           39         DACK3         94         SA4         149         MD1         205         F14MHZ           40         IOW         95         SA5         150         MD2         206         Vcc           41         IOR         96         SA6         151         MD3         207         Vss           42         SMEMW         97         SA7         152         MD4         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210 <td>33</td> <td>IRQ7</td> <td>88</td> <td>V<sub>cc</sub></td> <td></td> <td></td> <td></td> <td></td>                                                     | 33         | IRQ7                                  | 88      | V <sub>cc</sub> |         |                 |         |          |

| 35         DRQ1         90         SA0         145         XD7         201         KBINT           36         SYSCLK         91         SA1         146         Vcc         202         PWRGOO           37         DACK1         92         SA2         147         Vss         203         PROCLK           38         DRQ3         93         SA3         148         MD0         204         IOCLK           39         DACK3         94         SA4         149         MD1         205         F14MHZ           40         IOW         95         SA5         150         MD2         206         Vcc           41         IOR         96         SA6         151         MD3         207         Vss           42         SMEMW         97         SA7         152         MD4         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210         NPCS           45         AEN         100         SA10         155         MD7         211                                                                                                                                                               | 34         | REFRESH                               | 89      | V <sub>ss</sub> | 1       |                 | 1       |          |

| 36         SYSCLK         91         SA1         146         V <sub>cc</sub> 202         PWRGOO           37         DACK1         92         SA2         147         V <sub>ss</sub> 203         PROCLK           38         DRQ3         93         SA3         148         MD0         204         IOCLK           39         DACK3         94         SA4         149         MD1         205         F14MHZ           40         IOW         95         SA5         150         MD2         206         V <sub>cc</sub> 41         IOR         96         SA6         151         MD3         207         V <sub>ss</sub> 42         SMEMW         97         SA7         152         MD4         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210         NPCS           45         AEN         100         SA11         155         MD7         211         BUSY           46         POWS         101         SA11         156         MD8         21                                                                                                                                                   | 35         | DRQ1                                  | 90      | SA0             |         |                 |         |          |

| 37         DACK1         92         SA2         147         Vac         203         PROCLK           38         DRQ3         93         SA3         147         Vss         204         IOCLK           39         DACK3         94         SA4         149         MD1         205         F14MHZ           40         IOW         95         SA5         150         MD2         206         Vcc           41         IOR         96         SA6         151         MD3         207         Vss           42         SMEMW         97         SA7         152         MD4         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210         NPCS           45         AEN         100         SA10         155         MD7         211         BUSY           46         POWS         101         SA11         156         MD8         212         PEREQ           47         DRQ2         102         SA13         158         MD10         214                                                                                                                                                              | 36         | SYSCLK                                | 91      | SA1             |         |                 | 1       | 1        |

| 38         DRQ3         93         SA3         147         Vss         204         IOCLK           39         DACK3         94         SA4         148         MD0         205         F14MHZ           40         IOW         95         SA5         150         MD2         206         V <sub>cc</sub> 41         IOR         96         SA6         151         MD3         207         V <sub>ss</sub> 42         SMEMW         97         SA7         152         MD4         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210         NPCS           45         AEN         100         SA10         155         MD7         211         BUSY           46         POWS         101         SA11         156         MD8         212         PEREQ           47         DRQ2         102         SA13         157         MD9         213         PEACK           48         IRQ9         103         SA14         159         MD10         214 <td>37</td> <td>DACK1</td> <td>92</td> <td>SA2</td> <td></td> <td></td> <td>8</td> <td></td>                                                             | 37         | DACK1                                 | 92      | SA2             |         |                 | 8       |          |

| 39         DACK3         94         SA4         140         MD0         205         F14MHZ           40         IOW         95         SA5         150         MD1         206         V <sub>cc</sub> 41         IOR         96         SA6         151         MD3         207         V <sub>ss</sub> 42         SMEMW         97         SA7         152         MD4         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210         NPCS           45         AEN         100         SA10         155         MD7         211         BUSY           46         POWS         101         SA11         156         MD8         212         PEREQ           47         DRQ2         102         SA13         158         MD10         214         RESET28           48         IRQ9         103         SA14         159         MD11         215         P287ERR           50         IOCHK         105         SA15         160         V <sub>cc</sub>                                                                                                                                                  | 38         | DRQ3                                  | 93      | SA3             |         |                 |         |          |

| 40         IOW         95         SA5         149         MD1         206         V <sub>cc</sub> 41         IOR         96         SA6         150         MD2         206         V <sub>cc</sub> 42         SMEMW         97         SA7         152         MD4         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210         NPCS           45         AEN         100         SA10         155         MD7         211         BUSY           46         POWS         101         SA11         156         MD8         212         PEREQ           47         DRQ2         102         SA12         157         MD9         213         PEACK           48         IRQ9         103         SA14         159         MD10         214         RESET28           49         RESETDRV         104         SA15         160         V <sub>cc</sub> 216         HDATDIR           51         XA17         106         SA16         161         V <sub>ss</sub>                                                                                                                                            | 1          |                                       | 94      | SA4             |         |                 | 1       | 1        |

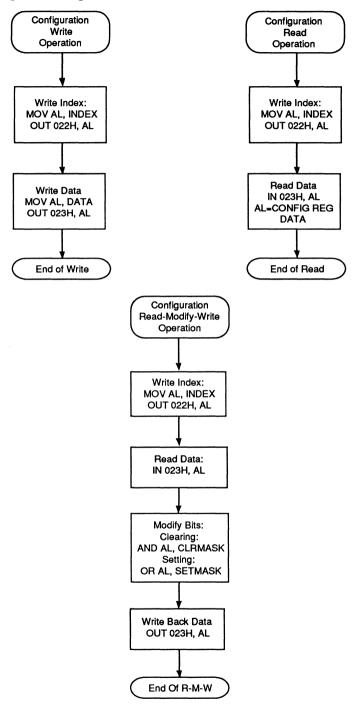

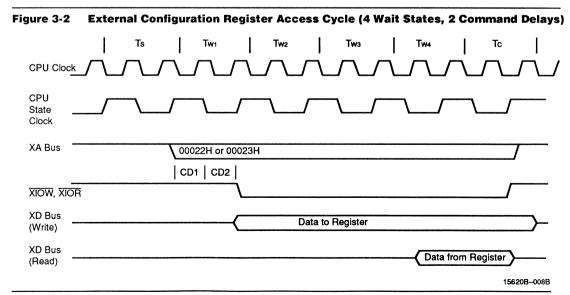

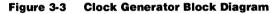

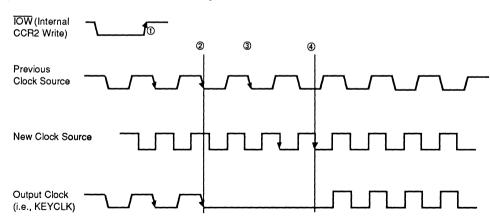

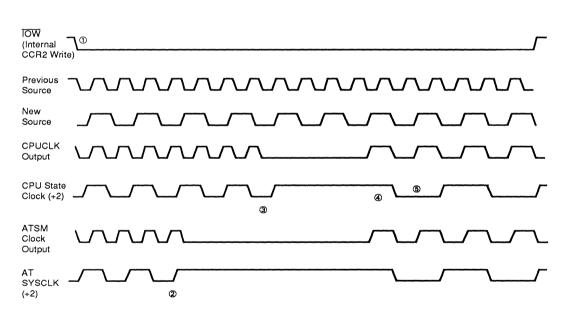

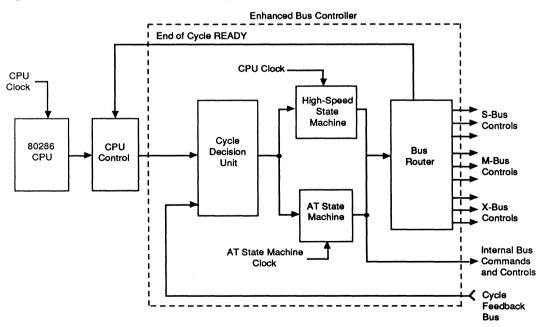

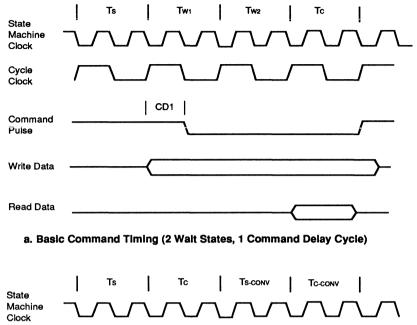

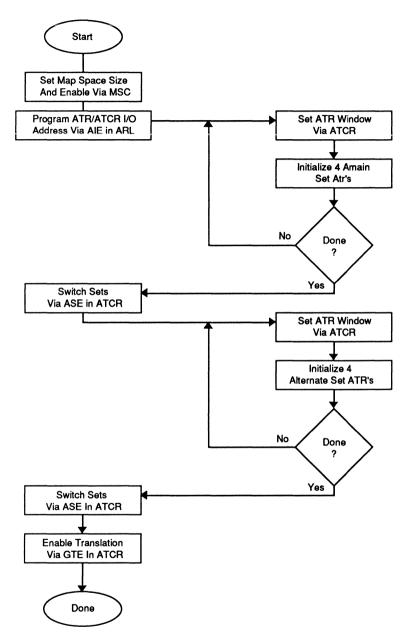

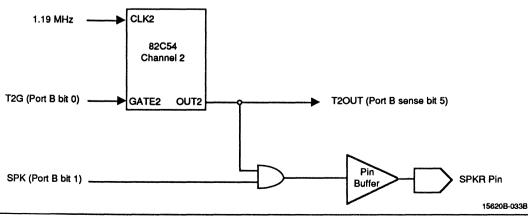

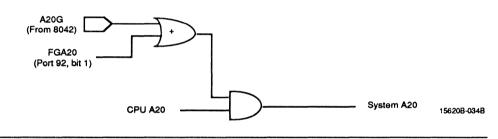

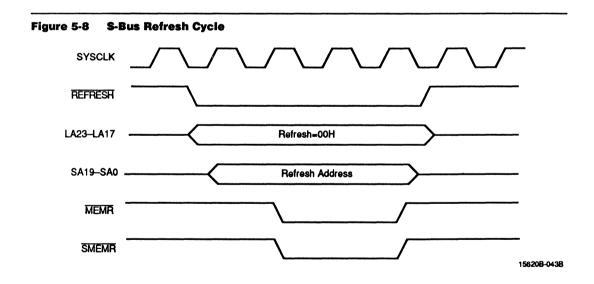

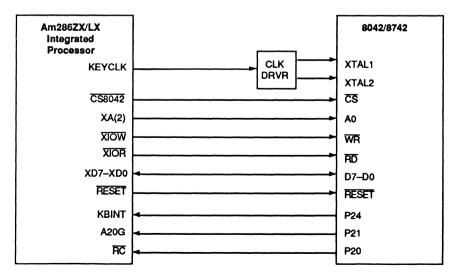

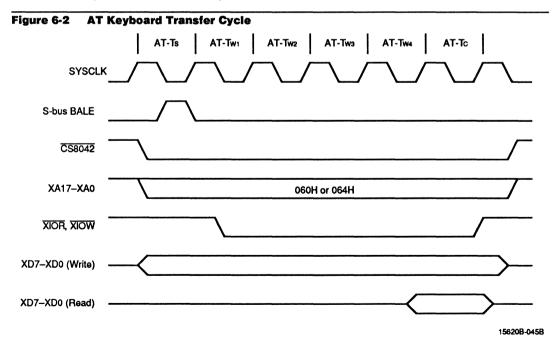

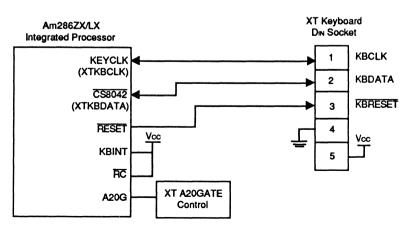

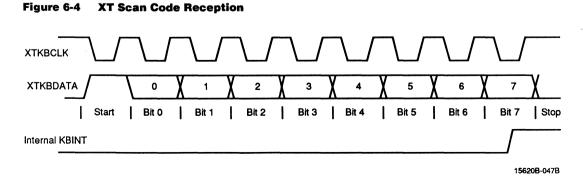

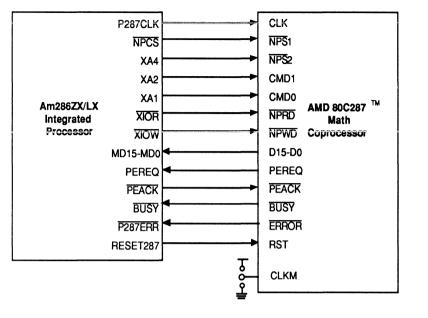

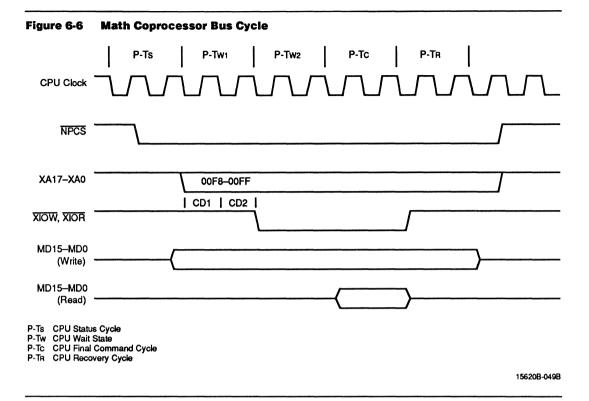

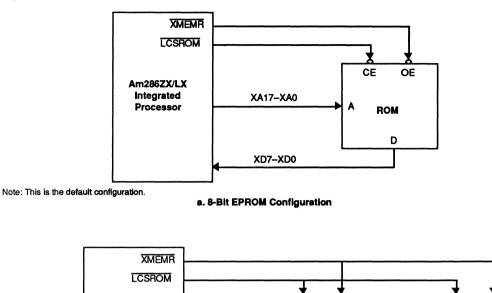

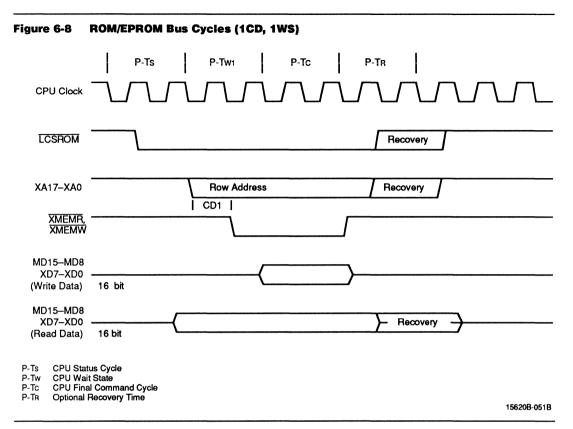

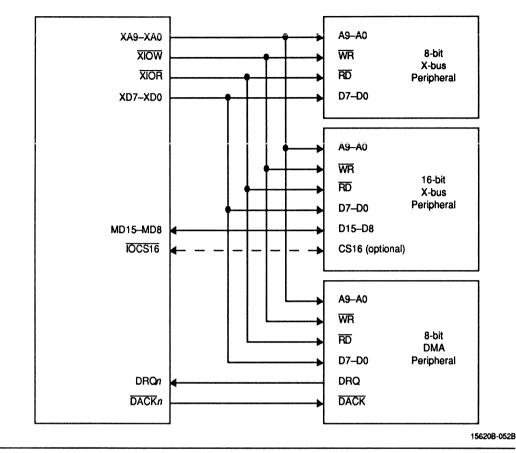

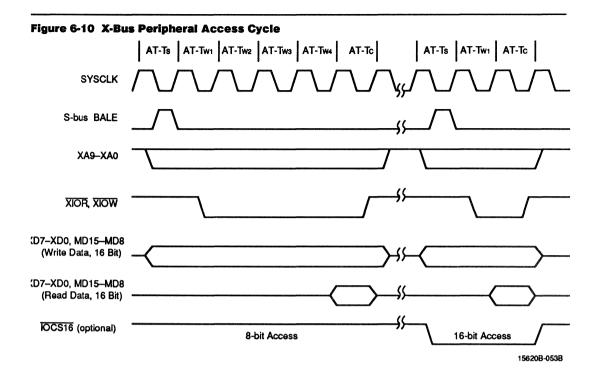

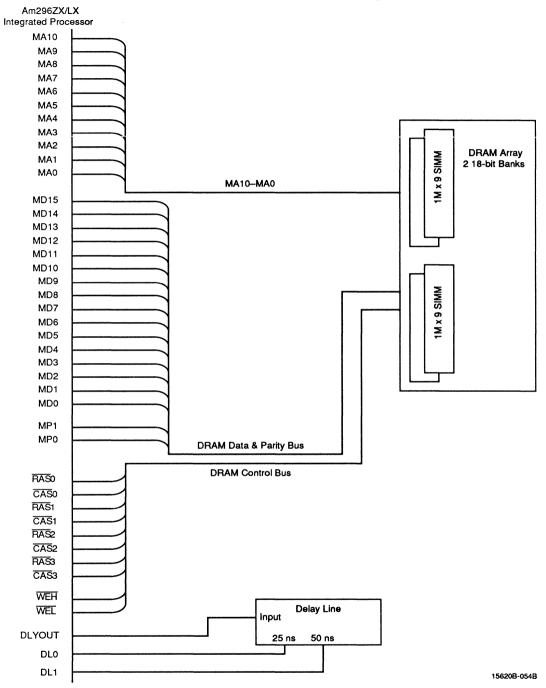

| 41         IOR         96         SA6         150         MD2         207         Vss           42         SMEMW         97         SA7         151         MD3         208         SPKR           43         SMEMR         98         SA8         153         MD5         209         P287CLK           44         IOCHRDY         99         SA9         154         MD6         210         NPCS           45         AEN         100         SA10         155         MD7         211         BUSY           46         POWS         101         SA11         156         MD8         212         PEREQ           47         DRQ2         102         SA12         157         MD9         213         PEACK           48         IRQ9         103         SA13         158         MD10         214         RESET28           49         RESETDRV         104         SA15         160         Vcc         216         HDATDIR           51         XA17         106         SA16         161         Vss         216         HDATDIR           52         XA16         107         SA17         162         MD12                                                                                                                                                        | 40         | WOI                                   | 95      | SA5             | 2       | 1               | B       |          |