Vantis

0

6

Including CPLD, FPGA, & PAL Products

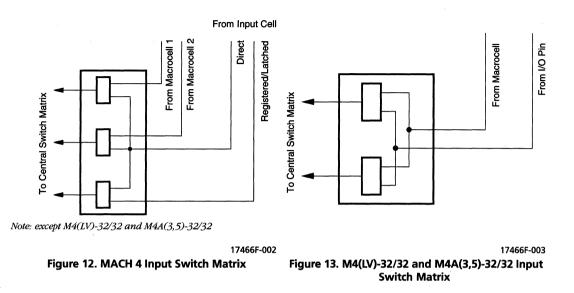

VANTIS

# Vantis Data Book 1999 Including MACH, VF1, & PAL Products

**BEYOND PERFORMANCE**

## Vantis Data Book 1999

| Mail:  | Vantis Corporation<br>P.O. Box 3755<br>995 Stewart Drive<br>Sunnyvale, CA 94088<br>USA |

|--------|----------------------------------------------------------------------------------------|

| Phone: | 1 (408) 616-8000<br>1 (888) VANTIS2 (826-8472)                                         |

| Web:   | www.vantis.com                                                                         |

#### ©1999 Vantis Corporation

Vantis reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warranty of merchantability or fitness for a particular application. Vantis assumes no responsibility for the use of any circuitry other than the circuitry in a Vantis product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. Vantis assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, Vantis assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

Vantis, the Vantis logo and combinations thereof, Beyond Performance, Bus-Friendly, DesignDirect, Ease-of-Success, First-Time-Fit, SpeedLocking, Fast-Fit-Time, VantisPRO, SpeedLocked, Variable-Grain-Architecture, Variable-Grain-Block, Variable-Length-Interconnect, and VF1 are trademarks of Vantis Corporation. MACH, MACHPRO, MACHXL, and PAL are registered trademarks of Vantis Corporation. AMD is a trademark of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. Welcome to Vantis! We are proud to introduce our new 1999 Data Book. It's not just MACH<sup>®</sup> anymore! Now featuring our entire line of programmable logic products, this is our most comprehensive and easy-to-use data book to date.

Vantis brings unmatched emphasis and depth to the industry with our high-density MACH (Macro Array CMOS High Density) CPLD family, our newly-announced FPGA (field programmable gate array) family, VF1<sup>™</sup>, as well as our SPLD product, the PAL<sup>®</sup>. In addition, our current software offerings have been expanded to include the DesignDirect<sup>™</sup> tool suite, establishing software as a much stronger part of the Vantis solution.

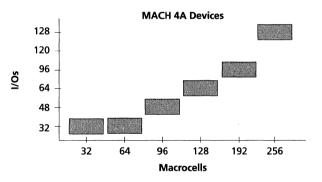

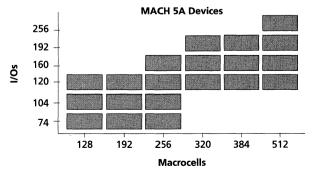

Vantis' MACH 4 and MACH 5 families represent the most comprehensive CPLD offering in the industry. Currently the leader in 3.3-Volt offerings, the MACH family has recently been expanded with the MACH 4A and MACH 5A product lines offering even greater density solutions while still maintaining the exceptional performance MACH devices are known for.

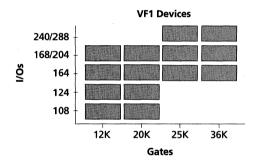

The VF1 family marks Vantis' entry into the FPGA market. These new devices are designed to effectively double system performance by providing 50-100 percent faster system speed than any other FPGA vendor.

Innovation and dedicated focus are at the heart of everything we do here at Vantis. From the development of ground-breaking architectures and advanced process technologies to our industryrenown customer service. At Vantis, programmable logic performance is not measured in nanoseconds alone. By combining software performance with proven quality and reliability and the best on-time-delivery in the business, Vantis is committed to taking our customers Beyond Performance.

Cheers,

Andrew D. Polin

Andy Robin Vice President of Marketing

iv

IV.

## Contents

## Vantis Overview

| Introduction       3         Vantis Device Selector Guide       9                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MACH FamiliesMACH 4 CPLD Family.25MACH 5 CPLD Family.77MACH 1 and 2 CPLD Families.127                                                                                                                                                                                                                                   |

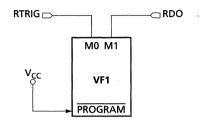

| VF1 FPGA Family<br>VF1 FPGA Family                                                                                                                                                                                                                                                                                      |

| PAL DevicesPALCE16V8 and PALCE16V8Z Families247PALLV16V8-10 and PALLV16V8Z Families279PALCE20V8 Family303PALCE22V10 and PALCE22V10Z Families331PALLV22V10 and PALLV22V10Z Families365                                                                                                                                   |

| General Information $f_{MAX}$ Theory and Calculations387Switching Test Circuit391Endurance Characteristics393Power-Up Reset395Latch-Up397Ground Bounce403Metastability409Inside Vantis' EE CMOS PLD Technology413Product Reliability Monitoring Program453Packages463Programming Support & Tools511Technical Support521 |

## **Application Notes**

| Hot Socketing and Mixed Supply Design with MACH 4 and MACH 5 Devices 525 |

|--------------------------------------------------------------------------|

| MACH 4 Timing and High Speed Design                                      |

| MACH 5 Timing and High Speed Design                                      |

| MACH 5 Power                                                             |

| The Evolution of Bus-Friendly Inputs and I/Os                            |

| Mixed Supply Design with MACH 1 & 2 SP Devices                           |

| VF1 FPGA Power Estimation                                                |

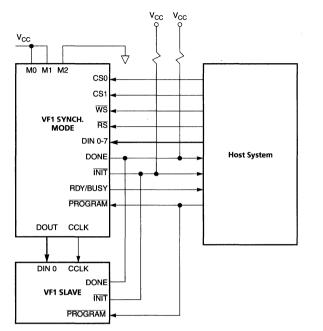

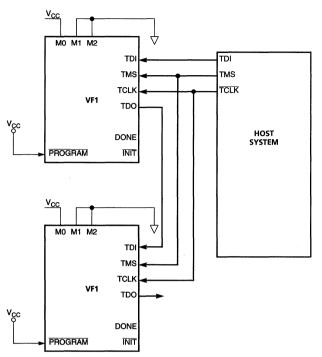

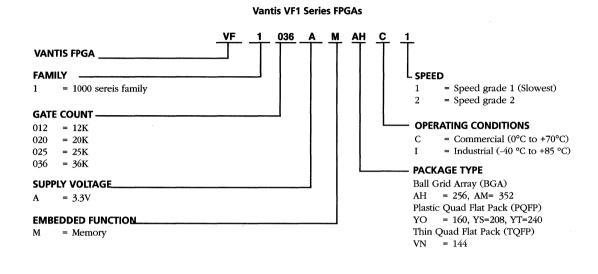

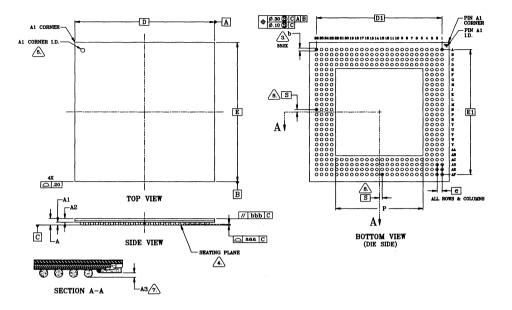

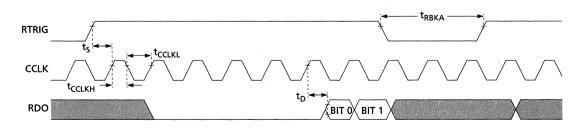

| VF1 FPGA Configuration Guide 571                                         |

vi

## **Vantis Overview**

1

Introduction

Formed in 1996, Vantis is an AMD company that exists solely to better serve the specialized requirements of programmable logic customers. Vantis brings expertise to the industry from almost two decades of innovation and excellence as one of the top PLD suppliers.

## TOTAL PROGRAMMABLE LOGIC LEADERSHIP

Today's leading-edge electronic systems require programmable logic devices (PLDs) to provide a variety of benefits including quick time-to-market and design flexibility. Vantis is one of the only PLD suppliers that offers a complete portfolio of programmable logic solutions: SPLDs (Simple PLDs), CPLDs (Complex PLDs) and FPGAs (Field Programmable Gate Arrays). This complete portfolio ensures the optimal solution for each system need. In addition, Vantis PLDs are recognized as the industry's highest performance devices.

Vantis is more than just the speed performance leader. Vantis ships more PLD components than any other supplier. Becoming the PLD volume leader required paying close attention to our customers' needs. These needs include accelerating system performance, simplifying PLD integration and delivering results with outstanding product quality that exceed our customers' expectations. At Vantis, we refer to this total product commitment as "Beyond Performance".

## **Accelerating System Performance**

As the PLD performance leader, Vantis strives to enhance every aspect of our products to provide superior benefits to the designer. There are three basic components that affect performance in PLD devices: process technology, architecture and circuit design techniques. Vantis excels in all three.

**Process Technology:** Vantis utilizes leading-edge process technologies to drive system performance. In addition, Vantis has an experienced process technologies group that specializes in defining next-generation processes and improving existing processes. These technical experts also work closely with Vantis circuit designers to exploit process features to the fullest for superior speed performance while optimizing for other important device attributes such as low-power operation and 5-Volt tolerant I/Os in 2.5-Volt processes.

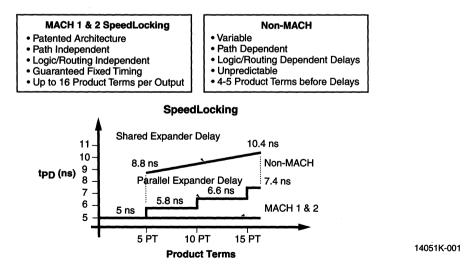

**Architecture Design:** The basic device concept, or architecture, can greatly affect how fast the PLD device will run. Vantis has proven its performance leadership by designing and shipping faster programmable logic solutions. The original 22V10 architecture, the MACH<sup>®</sup> CPLD architectures and the innovative VF1<sup>™</sup> FPGA architecture are examples of high-performance architecture leadership. All were specified and designed to provide better performing solutions. For example, the MACH products are SpeedLocked<sup>™</sup> to ensure guaranteed timing regardless of usage, a capability that no other supplier offers. And, VF1 FPGAs offer a unique Variable-Grain-Architecture<sup>™</sup> that adapts to the designer's logic to achieve faster performance.

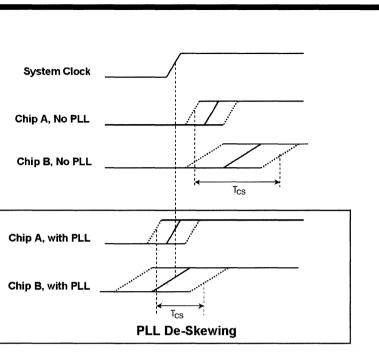

**Circuit Design:** Circuit design affects every aspect of PLD performance. Special attention is paid to minimize data setup time and clock-to-output time, resulting in faster external system bus speeds. Analog phase-locked-loops are designed to offer clock multiplication, doubling and tripling internal frequencies. On-chip drivers are scaled for optimal interconnect performance

improving overall chip speed. In addition, logic and memory blocks are carefully planned to yield maximum speed and versatility. All of these are accomplished while minimizing power dissipation and with minimal silicon overhead.

The focus Vantis places on PLD performance in process, architecture and circuit design translates into accelerated system speeds and shorter design cycles for the customer. Vantis is the PLD performance leader.

### **Simplifying System Integration**

The time-to-market advantage of PLD technology allows system designers to complete the design of programmable logic devices long after many other components on the printed circuit board (PCB) have been finalized. This implies that the PLD must seamlessly integrate into a pre-defined system environment. System integration issues may include power dissipation limitations, In-System Programming (ISP) requirements and I/O interoperability. Vantis believes that simplifying system integration is key to the success of Vantis and our customers.

To enable fast and easy integration into leading-edge electronic systems, Vantis provides 3.3-Volt safe 5-Volt devices, 5-Volt tolerant 3.3-Volt devices and a roadmap to 2.5-Volt operation. PCI compliance, hot-socketing, programmable slew rate, and programmable Bus-Friendly<sup>™</sup> or pull-up operation are additional Vantis capabilities that aid in system integration. Power management capabilities allow the users of Vantis devices to trade speed in non-critical portions of their designs for lower power consumption. This feature, combined with the industry's most robust offering of 3.3-Volt devices, allows users to reduce their overall power consumption. Testability and programming are supported through the use of industry-standard JTAG interfacing. The use of the JTAG industry standard, not universal among PLD suppliers, further simplifies the integration of Vantis PLDs into the customer's overall system. Also, the availability of industrial and commercial temperature range devices allows designers to use these capabilities over a wide range of operating conditions. Most importantly, Vantis PLDs simplify system integration *without* compromising speed.

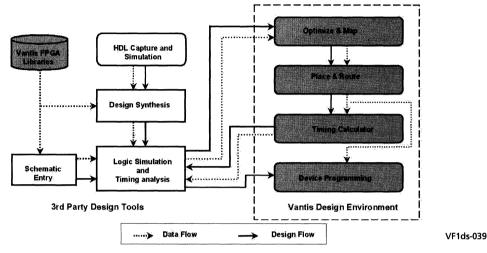

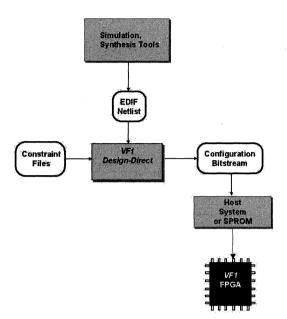

### **Delivering Results**

Programmable logic's key value proposition to electronic system designers is time-to-market. Yet time-to-market is often achieved at the expense of system performance. Vantis ensures that designers can quickly access the performance that they seek while exploiting the time-to-market value provided by PLDs. Vantis takes the first step in delivering this capability many months before producing the first silicon of a new product family. Device architects, software tool designers and silicon engineers work in concert to ensure that new Vantis architectures easily support capabilities such as First-Time-Fit<sup>™</sup>, Fast-Fit-Time<sup>™</sup>, pin-locking, SpeedLocking<sup>™</sup>, and greater logic flexibility. Vantis DesignDirect<sup>™</sup> software enables system designers to easily access these features. DesignDirect software is available either as a fully-integrated tool providing all design steps from capture to device programming or as a stand-alone silicon implementation tool that interfaces seamlessly with the industry's most popular third-party design capture, synthesis and simulation tools. DesignDirect software provides a rapid design environment that facilitates design changes while delivering superior speed performance to the customer. Vantis is *committed* to delivering superior results to our customers.

## VANTIS PRODUCTS

### MACH CPLDs

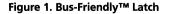

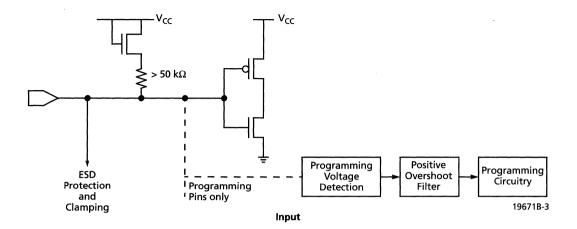

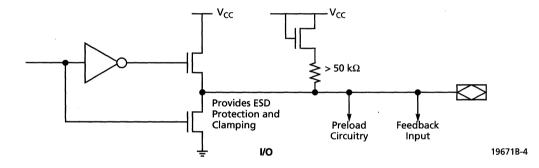

Addressing the need for speed in networking, telecommunications, and computing, Vantis' MACH 1, 2, 4 and 5 families offer the industry's highest performance CPLDs. Devices are available in speeds as fast as 5ns  $t_{PD}$  and in densities ranging from 32 to 512 macrocells. The MACH families are PCI-compliant and support JTAG-ISP, a critical customer requirement providing flexibility in the manufacturing environment. They also include other features such as SpeedLocking architecture for guaranteed fixed timing, Bus-Friendly inputs and I/Os, and programmable powerdown modes for extra power savings.

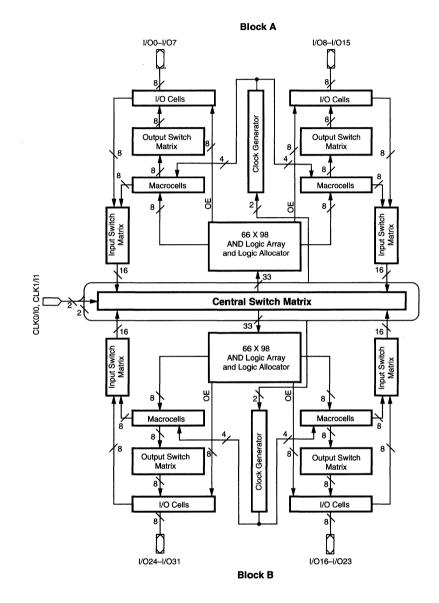

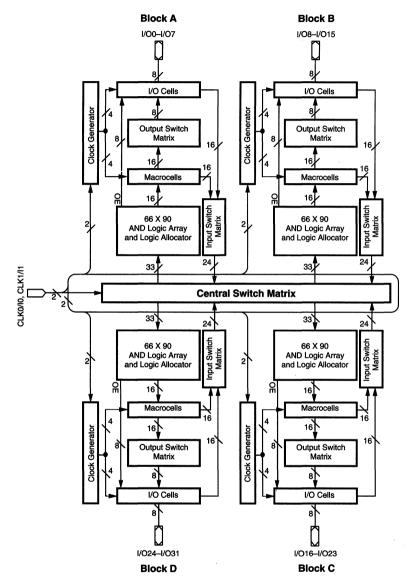

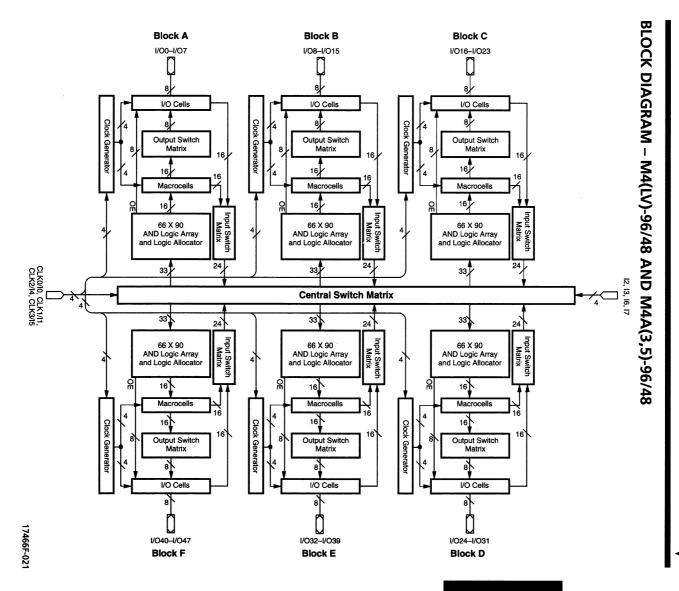

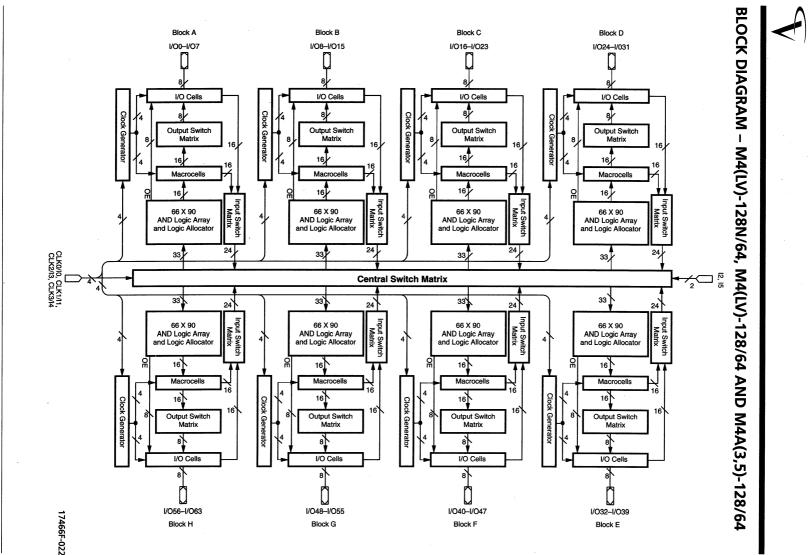

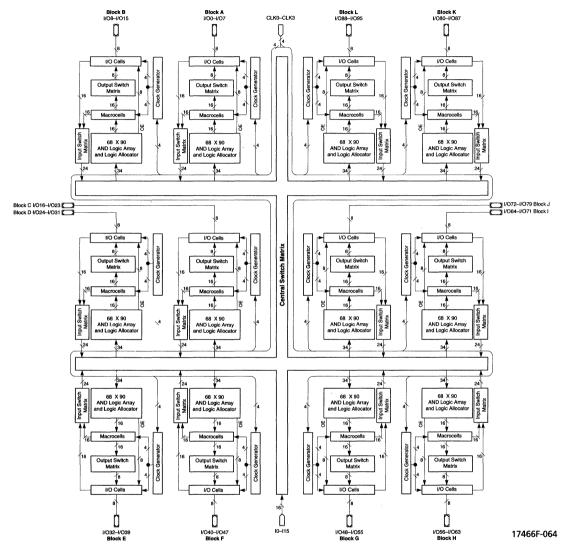

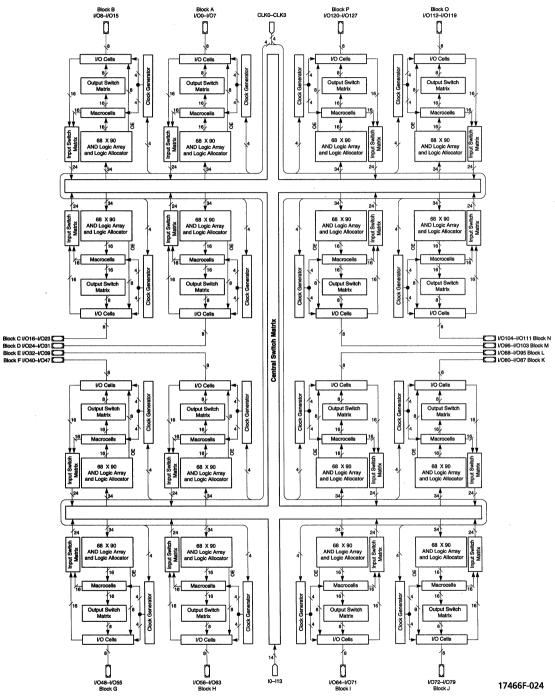

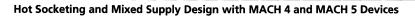

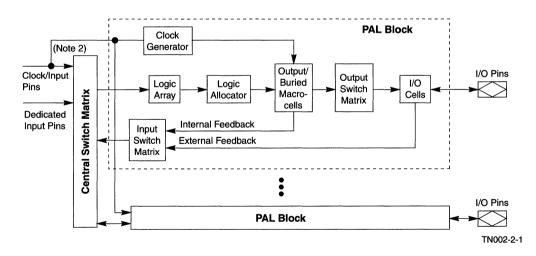

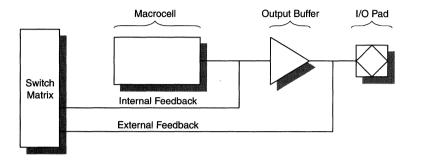

## **MACH 4 Family**

Vantis' MACH 4 family is the most flexible CPLD solution on the market today, providing designers with high-speed, SpeedLocked solutions for both 5-Volt and 3.3-Volt applications. With the architecture of multiplexer-based central switch matrices, MACH 4 delivers First-Time-Fit, Fast-Fit-Time, and easy system integration with 100% pin-out retention after any design change and refit. Other features include synchronous and asynchronous modes available for each macrocell, and input registers for extra design flexibility.

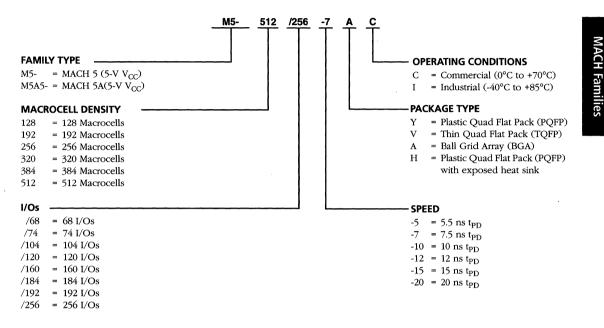

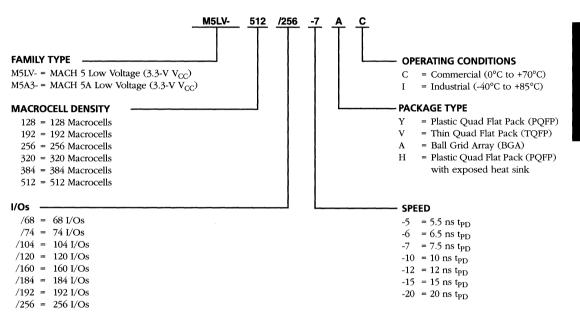

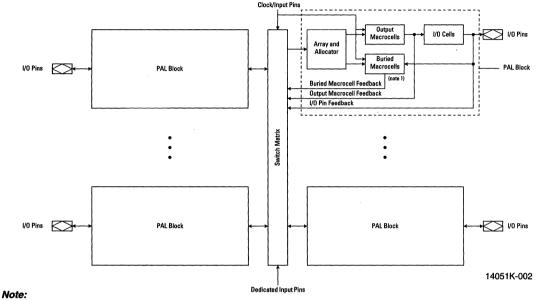

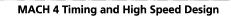

### **MACH 5 Family**

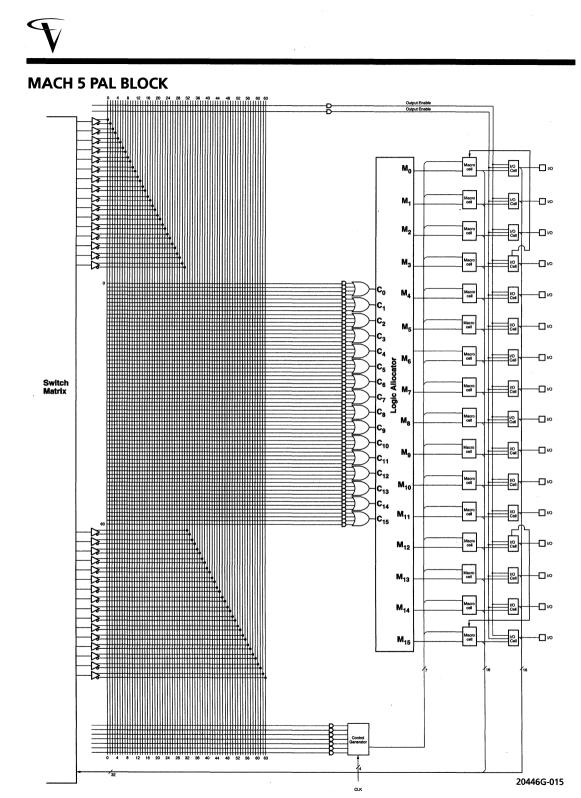

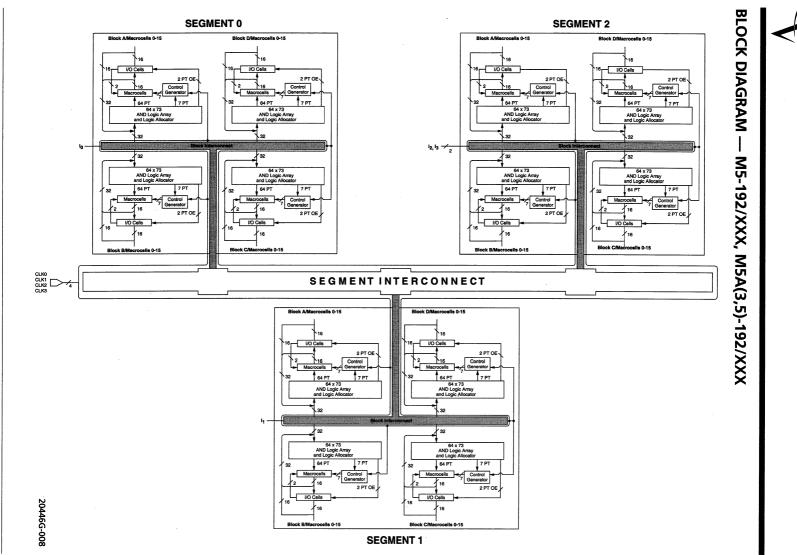

The MACH 5 family from Vantis offers high-performance CPLDs with speeds as fast as 5.5ns and densities ranging from 128 to 512 macrocells. All MACH 5 family members deliver fast fit and easy system integration with excellent pin-out retention. The MACH 5 family is the industry's fastest high-density CPLD family enabling significantly higher speeds at higher densities than ever achieved before.

### VF1 FPGAs

Vantis' VF1 family is designed to provide "best in class" performance with a combined synergy of software and architecture that delivers unmatched Ease-of-Success™ to customers. Providing the industry's most cost-effective FPGA solutions for high-performance, low-power systems, products from the Vantis VF1 family are designed to provide 50 to 100 percent faster system speed than any other FPGA vendor, effectively doubling system performance.

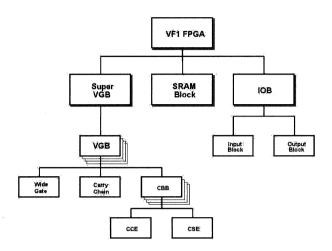

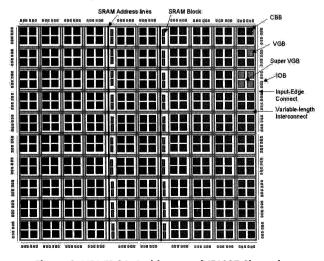

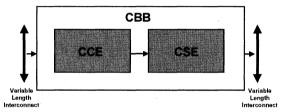

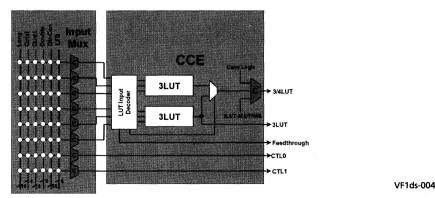

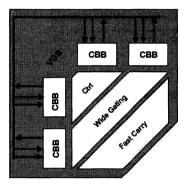

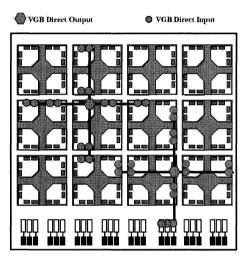

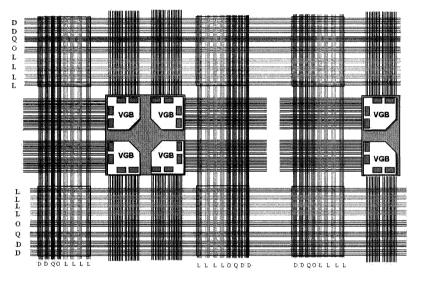

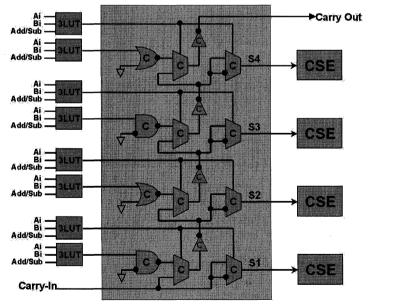

The VF1 family is based on a proprietary innovative and synthesis-friendly Variable-Grain-Architecture design, unique Variable-Length-Interconnect<sup>™</sup> hierarchy, and high-performance embedded memory. The VF1 architecture provides the ability to vary FPGA block configuration to adapt to a large variety of possible applications and design styles. The VF1 chip is designed with embedded, dual-port, 5-ns memory. Strategically located in vertical channels on the device, the memory provides maximum connectivity for the surrounding logic. At the core of the VF1 family architecture is Variable-Grain-Block<sup>™</sup> (VGB<sup>™</sup>) logic. Each VGB is capable of implementing finegrained three-input functions to coarse-grained 16-input functions, all providing extremely high performance. In addition, adjacent VGBs can be combined to create fast 32-input functions.

#### PAL SPLDs

As the SPLD leader, Vantis continues to provide a broad range of products including all the fundamental SPLD architectures. We offer key PAL devices in speed grades as fast as 5ns, along with low-power options, 3.3-Volt versions, industrial temperature range devices, and a wide range of packages.

#### Vantis Software

Vantis offers a suite of world-class software including DesignDirect software, MACHXL<sup>®</sup> software, and MACH-Synario software.

Vantis now offers internally-developed software targeted at FPGA, CPLD and SPLD devices. The DesignDirect software tool suite supports flexible top-down design methodologies optimized for high-density PLD design, thus allowing users to realize the benefits of designing in HDLs without sacrificing design performance and utilization.

MACHXL software is the design implementation software for Vantis MACH and PAL devices that allows designers to use their own third-party design tools.

Overview

MACH-Synario software is a complete development system for MACH and PAL devices, providing a highly productive, low-cost environment for the design, implementation and simulation of VHDL, ABEL-HDL, and schematic-based designs on the PC.

## **BEYOND PERFORMANCE**

To Vantis, Beyond Performance means providing our customers with more than what the competition offers. It means providing easy-to-use, high-performance devices that will help our customers get their products to market quicker. It means allowing them to breathe easy, knowing they can get top-notch customer support, day or night. It also means easy-to-use software that allows customers to design at the push of a button, and a proven 98 percent on-time delivery rate. Vantis knows how important it is to go beyond providing our customers with just the performance they desire. Vantis is committed to helping our customers succeed in the marketplace.

That's why Vantis takes you Beyond Performance.

Introduction

Vanis Device Selector Guide

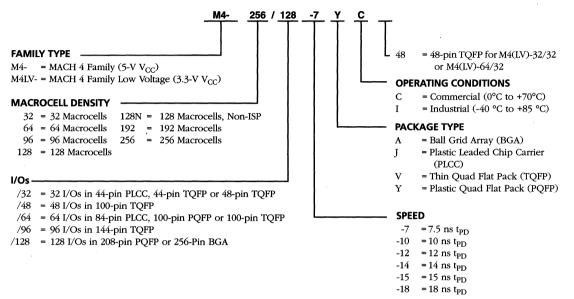

## MACH<sup>®</sup> 4 FAMILY

|                   |                    |                           |           |                     |                   |                                     |                |              | Comn               | nercial                 | Ind'l <sup>2</sup> |                      |                     |                                |

|-------------------|--------------------|---------------------------|-----------|---------------------|-------------------|-------------------------------------|----------------|--------------|--------------------|-------------------------|--------------------|----------------------|---------------------|--------------------------------|

| Device            | Package            | Macrocells<br>(PLD Gates) | I/Os      | Dedicated<br>Inputs | Output<br>Enables | PT per Output<br>(w/NO speed adder) | Flip-<br>Flops | JTAG-<br>ISP | t <sub>PD</sub> ns | f <sub>CNT</sub><br>MHz | t <sub>PD</sub> ns | t <sub>ss</sub> ³ ns | t <sub>co</sub> 4ns | l <sub>CC</sub> mA<br>(Static) |

| M4(LV)-32/32-7    |                    |                           |           |                     |                   |                                     |                |              | 7.5                | 111.1                   | 10                 | 5.5                  | 5.5                 |                                |

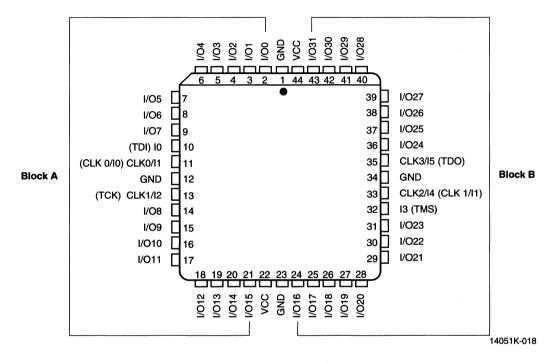

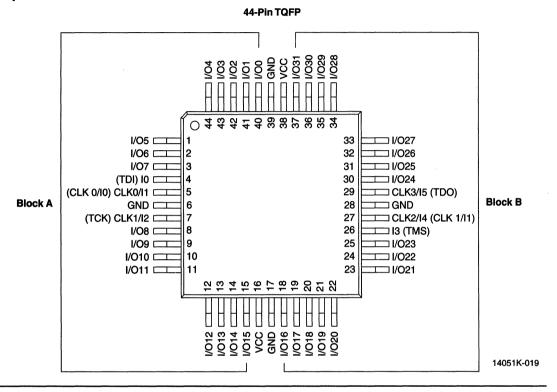

| M4(LV)-32/32-10   | 44PLCC,            | 32                        | 20        | 2                   | 32                | U= t= 20                            | 20             | N            | 10                 | 95.2                    | 12                 | 6                    | 6.5                 | 25                             |

| M4(LV)-32/32-12   | 44TQFP,<br>48TQFP  | (1,250)                   | 32        | 2                   | 52                | Up to 20                            | 32             | Yes          | 12                 | 76.9                    | 14                 | 7                    | 8                   | 25                             |

| M4(LV)-32/32-15   |                    |                           |           |                     |                   |                                     |                |              | 15                 | 55.6                    | 18                 | 10                   | 10                  | {                              |

| M4(LV)-64/32-7    |                    |                           |           |                     |                   |                                     |                |              | 7.5                | 111.1                   | 10                 | 5.5                  | 5.5                 |                                |

| M4(LV)-64/32-10   | 44PLCC,<br>44TQFP, | 64                        | 32        | 2                   | 32                | Up to 20                            | 96             | Vaa          | 10                 | 95.2                    | 12                 | 6                    | 6.5                 | 25                             |

| M4(LV)-64/32-12   | 48TQFP             | (2,500)                   | 54        | 4                   | 54                | 00 10 20                            | 90             | Yes          | 12                 | 76.9                    | 14                 | 7                    | 8                   | 45                             |

| M4(LV)-64/32-15   |                    |                           |           |                     |                   |                                     |                |              | 15                 | 55.6                    | 18                 | 10                   | 10                  |                                |

| M4(LV)-96/48-7    |                    |                           |           |                     |                   |                                     |                |              | 7.5                | 111.1                   | 10                 | 5.5                  | 5.5                 |                                |

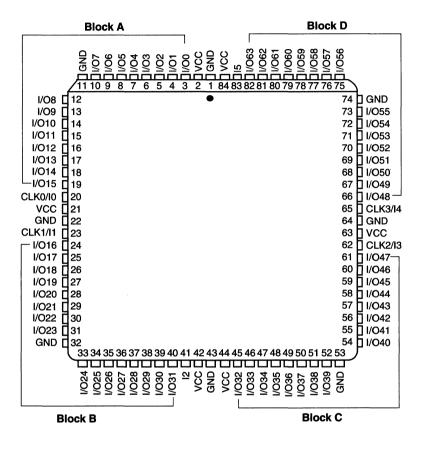

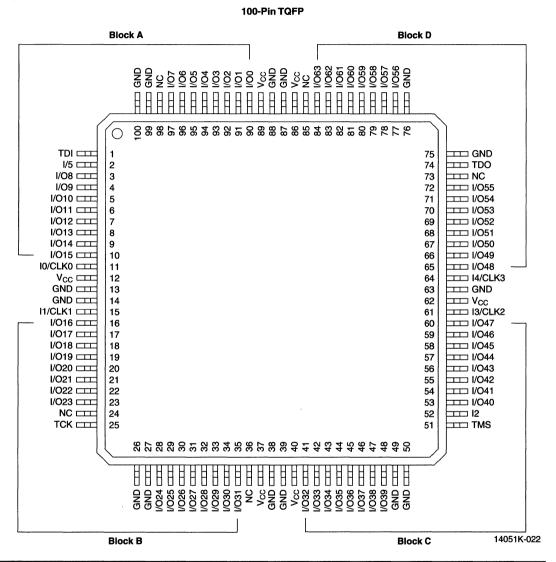

| M4(LV)-96/48-10   | 100TOFP            | 96                        | 48        | 8                   | 48                | Up to 20                            | 144            | Yes          | 10                 | 95.2                    | 12                 | 6                    | 6.5                 | 50                             |

| M4(LV)-96/48-12   | IUUIQIP            | (3,750)                   | 48        | 0                   | 40                | 00 10 20                            | 144            | ies          | 12                 | 76.9                    | 14                 | 7                    | 8                   | 50                             |

| M4(LV)-96/48-15   |                    |                           |           |                     |                   |                                     |                |              | 15                 | 55.6                    | 18                 | 10                   | 10                  |                                |

| M4(LV)-128N/64-7  |                    |                           |           |                     |                   |                                     |                |              | 7.5                | 111.1                   | 10                 | 5.5                  | 5.5                 |                                |

| M4(LV)-128N/64-10 | 84PLCC             | 128                       | 64        | 6                   | 64                | Up to 20                            | 192            | No           | 10                 | 95.2                    | 12                 | 6                    | 6.5                 | 70                             |

| M4(LV)-128N/64-12 | ourice             | (5,000)                   | 04        | 0                   | 04                | 00 10 20                            | 192            | NO           | 12                 | 76.9                    | 14                 | 7                    | 8                   | /0                             |

| M4(LV)-128N/64-15 |                    |                           |           |                     |                   |                                     |                |              | 15                 | 55.6                    | 18                 | 10                   | 10                  |                                |

| M4(LV)-128/64-7   |                    |                           |           |                     |                   |                                     |                |              | 7.5                | 111.1                   | 10                 | 5.5                  | 5.5                 |                                |

| M4(LV)-128/64-10  | 100PQFP,           | 128                       | 64        | 6                   | 64                | Up to 20                            | 192            | Yes          | 10                 | 95.2                    | 12                 | 6                    | 6.5                 | 70                             |

| M4(LV)-128/64-12  | 100TQFP            | (5,000)                   | 04        | 0                   | 04                | 00 10 20                            | 192            | 105          | 12                 | 76.9                    | 14                 | 7                    | 8                   | /0                             |

| M4(LV)-128/64-15  |                    |                           |           |                     |                   |                                     |                |              | 15                 | 55.6                    | 18                 | 10                   | 10                  |                                |

| M4(LV)-192/96-7   |                    |                           |           |                     |                   |                                     |                |              | 7.5                | 111.1                   | 10                 | 5.5                  | 5.5                 |                                |

| M4(LV)-192/96-10  | 144TOFP            | 192                       | 96        | 16                  | 96                | Up to 20                            | 288            | Yes          | 10                 | 95.2                    | 12                 | 6                    | 6.5                 | 85                             |

| M4(LV)-192/96-12  | 1441QfP            | (7,500)                   | 90        | 10                  | 90                | 00 10 20                            | 400            | ies          | 12                 | 76.9                    | 14                 | 7                    | 8                   | 67                             |

| M4(LV)-192/96-15  |                    |                           |           |                     |                   |                                     |                |              | 15                 | 55.6                    | 18                 | 10                   | 10                  |                                |

| M4(LV)-256/128-7  |                    |                           |           |                     |                   |                                     |                |              | 7.5                | 111.1                   | 10                 | 5.5                  | 5.5                 |                                |

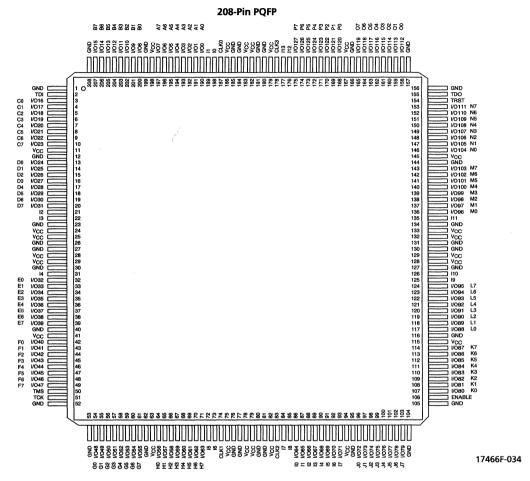

| M4(LV)-256/128-10 | 208PQFP            | 256                       | 128       | 14                  | 120               | Un to 20                            | 29/            | Voc          | 10                 | 95.2                    | 12                 | 6                    | 6.5                 | 100                            |

| M4(LV)-256/128-12 | 256BGA             | 256BGA (10,000) 128       | 28 14 128 |                     | 28 Up to 20 384   | 384                                 | 384 Yes        | 12           | 76.9               | 14                      | 7                  | 8                    | 100                 |                                |

| M4(LV)-256/128-15 |                    |                           |           |                     |                   |                                     |                |              | 15                 | 55.6                    | 18                 | 10                   | 10                  |                                |

### Table 1. MACH 4 Devices<sup>1</sup>

#### Notes:

1. M4 devices reflect a new nomenclature. A brief cross reference is provided below:

| OLD OPN  | NEW M4 OPN | OLD OPN  | NEW M4 OPN |

|----------|------------|----------|------------|

| MACH355> | M4-96/96   | MACH446> | M4-128/64  |

| MACH436> | M4-128N/64 | MACH466> | M4-256/128 |

2. MACH devices are dual-marked with both commercial and industrial speeds while CMOS PAL devices are marked separately.

3. Minimum setup time from input, I/O, or feedback to clock.

4. Maximum time from clock to output.

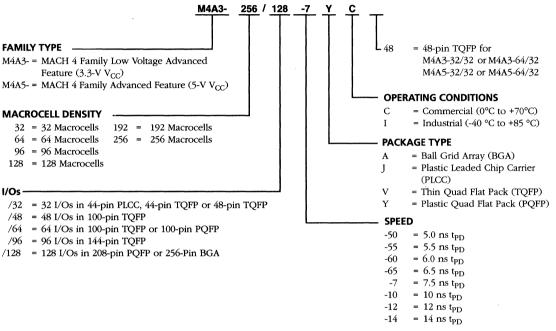

Table 2. MACH 4A Devices<sup>1</sup>

|                     |                     |            |      |                     |                   |                  |            |          | Com                | mercial                 | Ind'l <sup>2</sup> |                         |                         |

|---------------------|---------------------|------------|------|---------------------|-------------------|------------------|------------|----------|--------------------|-------------------------|--------------------|-------------------------|-------------------------|

| Device              | Package             | Macrocells | I/Os | Dedicated<br>inputs | Output<br>Enables | PT per<br>Output | Flip Flops | JTAG-ISP | t <sub>PD</sub> ns | f <sub>CNT</sub><br>MHz | t <sub>PD</sub> ns | t <sub>ss</sub> ³<br>ns | t <sub>co</sub> 4<br>ns |

| M4A(3,5)-32/32-50   |                     |            |      |                     |                   |                  |            |          | 5                  | 182                     | 7.5                | 3                       | 4                       |

| M4A(3,5)-32/32-60   | 44PLCC,             |            |      |                     |                   |                  |            |          | 6                  | 154                     | 10                 | 4                       | 4.5                     |

| M4A(3,5)-32/32-7    | 44TQFP,             | 32         | 32   | 2                   | 32                | Up to 20         | 32         | Yes      | 7.5                | 125                     | 10                 | 5.5                     | 5                       |

| M4A(3,5)-32/32-10   | 48TQFP              |            |      |                     |                   |                  |            |          | 10                 | 118                     | 12                 | 6                       | 5.5                     |

| M4A(3,5)-32/32-12   | ]                   |            |      |                     |                   |                  |            |          | 12                 | 95                      | 14                 | 7                       | 6.5                     |

| M4A(3,5)-64/32-50   |                     |            |      |                     |                   |                  |            |          | 5                  | 182                     | 7.5                | 3                       | 4                       |

| M4A(3,5)-64/32-60   | 44PLCC              |            |      |                     |                   |                  |            |          | 6                  | 154                     | 10                 | 4                       | 4.5                     |

| M4A(3,5)-64/32-7    | 44TQFP              | 64         | 32   | 2                   | 32                | Up to 20         | 96         | Yes      | 7.5                | 125                     | 10                 | 5.5                     | 5                       |

| M4A(3,5)-64/32-10   | 48TQFP              | 1          |      |                     |                   |                  |            |          | 10                 | 118                     | 12                 | 6                       | 5.5                     |

| M4A(3,5)-64/32-12   | 1                   |            |      |                     |                   |                  |            |          | 12                 | 95                      | 14                 | 7                       | 6.5                     |

| M4A(3,5)-96/48-50   |                     |            |      |                     |                   |                  |            |          | 5                  | 182                     | 7.5                | 3                       | 4                       |

| M4A(3,5)-96/48-60   |                     |            |      |                     |                   |                  |            |          | 6                  | 154                     | 10                 | 4                       | 4.5                     |

| M4A(3,5)-96/48-7    | 100TQFP             | 96         | 48   | 8                   | 48                | Up to 20         | 144        | Yes      | 7.5                | 125                     | 10                 | 5.5                     | 5                       |

| M4A(3,5)-96/48-10   | 1                   |            |      |                     |                   |                  |            |          | 10                 | 118                     | 12                 | 6                       | 5.5                     |

| M4A(3,5)-96/48-12   | 1                   |            |      |                     |                   |                  |            |          | 12                 | 95                      | 14                 | 7                       | 6.5                     |

| M4A(3,5)-128/64-50  |                     |            |      |                     |                   |                  |            |          | 5                  | 182                     | 7.5                | 3                       | 4                       |

| M4A(3,5)-128/64-60  |                     |            |      |                     |                   |                  |            |          | 6                  | 154                     | 10                 | 4                       | 4.5                     |

| M4A(3,5)-128/64-7   | 100TQFP,<br>100PQFP | 128        | 64   | 6                   | 64                | Up to 20         | 192        | Yes      | 7.5                | 125                     | 10                 | 5.5                     | 5                       |

| M4A(3,5)-128/64-10  | 1001Q11             |            | )    |                     |                   |                  |            |          | 10                 | 118                     | 12                 | 6                       | 5.5                     |

| M4A(3,5)-128/64-12  | 1                   |            |      |                     | ]                 |                  |            |          | 12                 | 95                      | 14                 | 7                       | 6.5                     |

| M4A(3,5)-192/96-50  |                     |            |      |                     |                   |                  |            |          | 5                  | 182                     | 7.5                | 3                       | 4                       |

| M4A(3,5)-192/96-60  |                     |            |      |                     |                   |                  |            |          | 6                  | 154                     | 10                 | 4                       | 4.5                     |

| M4A(3,5)-192/96-7   | 144TQFP             | 192        | 96   | 16                  | 96                | Up to 20         | 288        | Yes      | 7.5                | 125                     | 10                 | 5.5                     | 5                       |

| M4A(3,5)-192/96-10  | 1                   |            |      |                     |                   |                  |            |          | 10                 | 118                     | 12                 | 6                       | 5.5                     |

| M4A(3,5)-192/96-12  | 1                   |            |      |                     |                   |                  |            |          | 12                 | 95                      | 14                 | 7                       | 6.5                     |

| M4A(3,5)-256/128-50 |                     |            |      |                     |                   |                  |            |          | 5                  | 182                     | 7.5                | 3                       | 4                       |

| M4A(3,5)-256/128-60 | 1                   |            |      |                     |                   |                  |            |          | 6                  | 154                     | 10                 | 4                       | 4.5                     |

| M4A(3,5)-256/128-7  | 208PQFP<br>256BGA   | 256        | 128  | 14                  | 128               | Up to 20         | 384        | Yes      | 7.5                | 125                     | 10                 | 5.5                     | 5                       |

| M4A(3,5)-256/128-10 | - 430DUA            |            |      |                     |                   |                  |            |          | 10                 | 118                     | 12                 | 6                       | 5.5                     |

| M4A(3,5)-256/128-12 | 1                   |            |      |                     |                   |                  |            |          | 12                 | 95                      | 14                 | 7                       | 6.5                     |

Notes:

1. Advance Information

2. MACH devices are dual-marked with both commercial and industrial speeds while CMOS PAL devices are marked separately.

3. Minimum setup time from input, I/O, or feedback to clock.

4. Maximum time from clock to output.

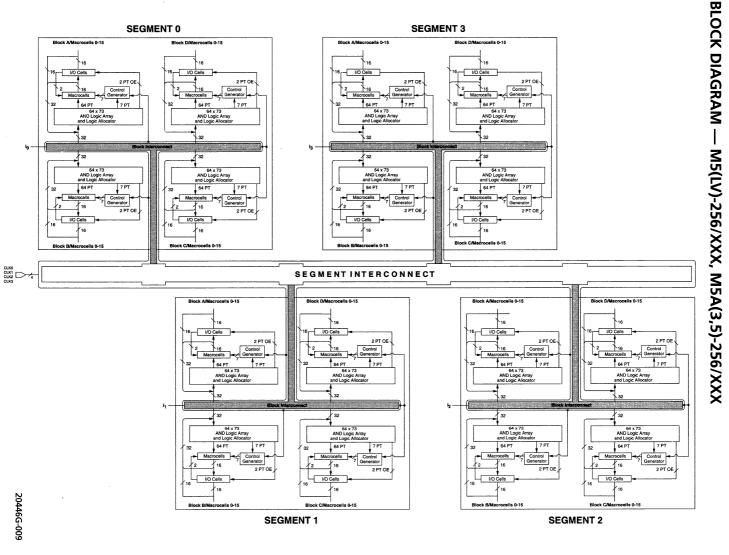

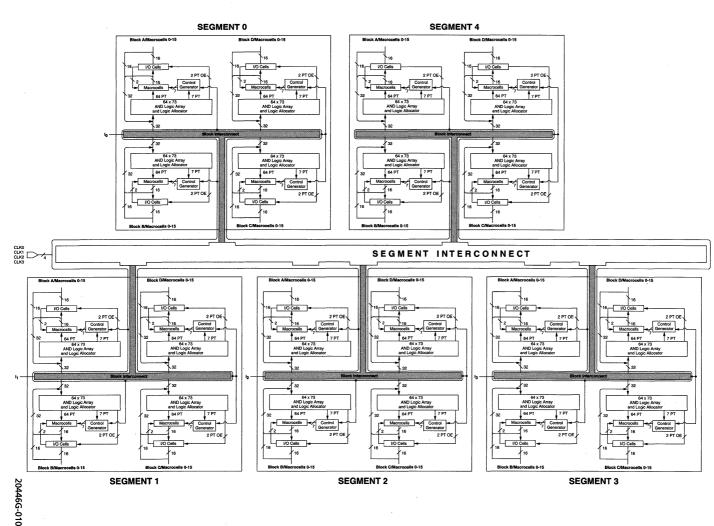

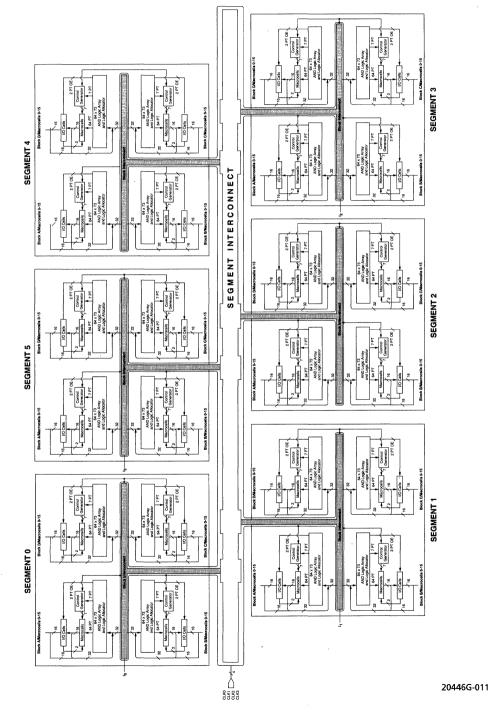

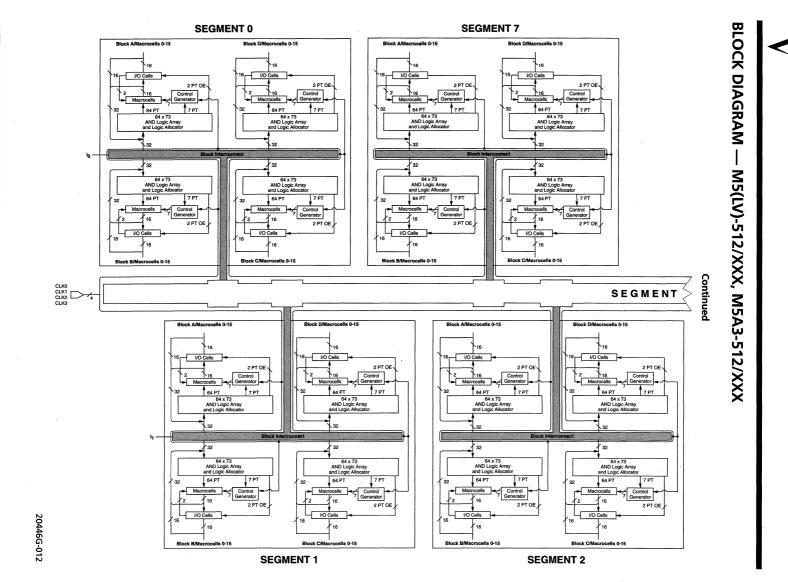

## **MACH 5 FAMILY**

|                   |                         |                           |      |                     |                   |                  |          | Comn                  | nercial                 | Ind'l <sup>1</sup>    |                         |                         |                                |

|-------------------|-------------------------|---------------------------|------|---------------------|-------------------|------------------|----------|-----------------------|-------------------------|-----------------------|-------------------------|-------------------------|--------------------------------|

| Device            | Package                 | Macrocelis<br>(PLD Gates) | I/Os | Dedicated<br>Inputs | Output<br>Enables | PT per<br>Output | JTAG-ISP | t <sub>PD</sub><br>ns | f <sub>CNT</sub><br>MHz | t <sub>PD</sub><br>ns | t <sub>ss</sub> ²<br>ns | t <sub>CO</sub> 3<br>ns | l <sub>CC</sub> mA<br>(Static) |

| M5LV-128/68-5     |                         |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                       | 4.5                     |                                |

| M5(LV)-128/68-7   | 100PQFP,                |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-128/68-10  | 100TQFP                 | 128 (5,000)               | 68   | 4                   | 16                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                       | 7                       | 35                             |

| M5(LV)-128/68-12  |                         | (),000)                   |      | 1                   |                   |                  |          | 12                    | 83.3                    | 15 .                  | 6                       | 8                       |                                |

| M5-128/68-15      |                         |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5LV-128/74-5     |                         |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                       | 4.5                     |                                |

| M5LV-128/74-7     | 1007070                 | 128                       | -4   | 4                   |                   | 11- 1- 20        | ¥        | 7.5                   | 125                     | 10                    | 4                       | 6                       | 25                             |

| M5LV-128/74-10    | 100TQFP                 | (5,000)                   | 74   | 4                   | 16                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                       | 7                       | 35                             |

| M5LV-128/74-12    |                         |                           |      |                     |                   |                  |          | 12                    | 83.3                    | 15                    | 6                       | 8                       |                                |

| M5LV-128/104-5    |                         |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                       | 4.5                     |                                |

| M5(LV)-128/104-7  | -                       |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       | 1                              |

| M5(LV)-128/104-10 | - 144PQFP,<br>- 144TQFP | 128<br>(5,000)            | 104  | 4                   | 16                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                       | 7                       | 35                             |

| M5(LV)-128/104-12 | 1441Qfr                 | (3,000)                   |      |                     |                   |                  |          | 12                    | 83.3                    | 15                    | 6                       | 8                       |                                |

| M5-128/104-15     | -                       |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5LV-128/120-5    |                         |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                       | 4.5                     |                                |

| M5(LV)-128/120-7  | -                       |                           | ļ    |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       | 1                              |

| M5(LV)-128/120-10 | 160PQFP                 | 128 (5,000)               | 120  | 4                   | 16                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                       | 7                       | 35                             |

| M5(LV)-128/120-12 | -                       | (),000)                   |      |                     |                   |                  |          | 12                    | 83.3                    | 15                    | 6                       | 8                       |                                |

| M5-128/120-15     |                         |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5-192/68-7       |                         |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5-192/68-10      | 100PQFP,                | 192                       | 6    |                     |                   |                  |          | 10                    | 100                     | 12                    | 5                       | 7                       |                                |

| M5-192/68-12      | 100TQFP                 | (7,500)                   | 68   | 4                   | 24                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 45                             |

| M5-192/68-15      | -                       |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5-192/104-7      |                         |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5-192/104-10     | 1//0000                 | 192                       |      |                     |                   |                  | ¥7       | 10                    | 100                     | 12                    | 5                       | 7                       |                                |

| M5-192/104-12     | - 144PQFP               | (7,500)                   | 104  | 4                   | 24                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 45                             |

| M5-192/104-15     |                         |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5-192/120-7      |                         |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5-192/120-10     | 1(00000                 | 192                       | 1.00 |                     | 24                |                  |          | 10                    | 100                     | 12                    | 5                       | 7                       |                                |

| M5-192/120-12     | 160PQFP                 | (7,500)                   | 120  | 4                   | 24                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 45                             |

| M5-192/120-15     | 7                       |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5-192/160-7      |                         |                           |      |                     |                   | 1                |          | 7.5                   | 125                     | 10                    | 4                       | .6                      |                                |

| M5-192/160-10     |                         | 192                       | 1/0  |                     |                   |                  | v        | 10                    | 100                     | 12                    | 5                       | 7                       | 1                              |

| M5-192/160-12     | 208PQFP                 | (7,500)                   | 160  | 4                   | 24                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 45                             |

| M5-192/160-15     |                         |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      | 1                              |

Table 3. MACH 5 Devices

Table 3. MACH 5 Devices (Continued)

|                   |          | [                         |      |                     |                   |                  |          | Comn                  | nercial                 | Ind'I <sup>1</sup>    |                              |                                    |                                |

|-------------------|----------|---------------------------|------|---------------------|-------------------|------------------|----------|-----------------------|-------------------------|-----------------------|------------------------------|------------------------------------|--------------------------------|

| Device            | Package  | Macrocells<br>(PLD Gates) | I/Os | Dedicated<br>Inputs | Output<br>Enables | PT per<br>Output | JTAG-ISP | t <sub>PD</sub><br>ns | f <sub>CNT</sub><br>MHz | t <sub>PD</sub><br>ns | t <sub>ss</sub> <sup>2</sup> | t <sub>co</sub> <sup>3</sup><br>ns | l <sub>CC</sub> mA<br>(Static) |

| M5LV-256/68-5     | 1        | ( ,                       |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                            | 4.5                                | (5 111 10)                     |

| M5(LV)-256/68-7   | 1        |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-256/68-10  | 100PQFP, | 256                       | 68   | 4                   | 32                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                            | 7                                  | 55                             |

| M5(LV)-256/68-12  | 100TQFP  | (10,000)                  |      | -                   | 5-                | or               |          | 12                    | 83.3                    | 15                    | 6                            | 8                                  |                                |

| M5-256/68-15      | 1        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 |                                |

| M5LV-256/74-5     |          |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                            | 4.5                                |                                |

| M5LV-256/74-7     | -        | 256                       |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5LV-256/74-10    | 100TQFP  | (10,000)                  | 74   | 4                   | 32                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                            | 7                                  | 55                             |

| M5LV-256/74-12    |          |                           |      |                     |                   |                  |          | 12                    | 83.3                    | 15                    | 6                            | 8                                  |                                |

| M5LV-256/104-5    |          |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                            | 4.5                                |                                |

| M5(LV)-256/104-7  | -        |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-256/104-10 | 144PQFP, | 256                       | 104  | 4                   | 32                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                            | 7                                  | 55                             |

| M5(LV)-256/104-12 | 144TQFP  | (10,000)                  |      |                     |                   |                  |          | 12                    | 83.3                    | 15                    | 6                            | 8                                  |                                |

| M5-256/104-15     | 1        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 |                                |

| M5LV-256/120-5    |          |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                            | 4.5                                |                                |

| M5(LV)-256/120-7  | 1        |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-256/120-10 | 160PQFP  | 256                       | 120  | 4                   | 32                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                            | 7                                  | 55                             |

| M5(LV)-256/120-12 |          | (10,000)                  |      |                     | -                 |                  |          | 12                    | 83.3                    | 15                    | 6                            | 8                                  |                                |

| M5-256/120-15     | 1.       |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 |                                |

| M5LV-256/160-5    |          |                           |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                            | 4.5                                |                                |

| M5(LV)-256/160-7  | -        |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-256/160-10 | 208PQFP  | 256                       | 160  | 4 .                 | 32                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                            | 7                                  | 55                             |

| M5(LV)-256/160-12 | 1        | (10,000)                  |      |                     |                   | -                |          | 12                    | 83.3                    | 15                    | 6                            | 8                                  |                                |

| M5-256/160-15     | -        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 |                                |

| M5(LV)-320/120-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-320/120-10 |          | 320                       |      |                     |                   |                  |          | 10                    | 100                     | 12                    | 5                            | 7                                  |                                |

| M5(LV)-320/120-12 | 160PQFP  | (12,500)                  | 120  | 4                   | 40                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                            | 8                                  | 70                             |

| M5(LV)-320/120-15 | 1        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 |                                |

| M5(LV)-320/160-7  |          |                           |      |                     |                   |                  | 1        | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-320/160-10 | 1        | 320                       |      | ,                   | 1-                |                  |          | 10                    | 100                     | 12                    | 5                            | 7                                  |                                |

| M5(LV)-320/160-12 | 208PQFP  | (12,500)                  | 160  | 4                   | 40                | Up to 32         | Yes      | ·12                   | 83.3                    | 15                    | 6                            | 8                                  | 70                             |

| M5(LV)-320/160-15 | 1        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 |                                |

| M5(LV)-320/184-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-320/184-10 |          | 320                       |      | ,                   | 6                 |                  |          | 10                    | 100                     | 12                    | 5                            | 7                                  | -                              |

| M5(LV)-320/184-12 | 240PQFP  | (12,500)                  | 184  | 4                   | 40                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                            | 8                                  | 70                             |

| M5(LV)-320/184-15 | 1        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 |                                |

| M5(LV)-320/192-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                            | 6                                  |                                |

| M5(LV)-320/192-10 | 1        | 320                       |      | ,                   |                   |                  |          | 10                    | 100                     | 12                    | 5                            | 7                                  | <u>-</u> -                     |

| M5(LV)-320/192-12 | - 256BGA | (12,500)                  | 192  | 4                   | 40                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                            | 8                                  | 70                             |

| M5(LV)-320/192-15 | 1        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                            | 10                                 | 1                              |

|                   |          |                           |      |                     |                   |                  |          | Comn                  | nercial                 | Ind'l <sup>1</sup>    |                         |                         |                                |

|-------------------|----------|---------------------------|------|---------------------|-------------------|------------------|----------|-----------------------|-------------------------|-----------------------|-------------------------|-------------------------|--------------------------------|

| Device            | Package  | Macrocells<br>(PLD Gates) | I/Os | Dedicated<br>Inputs | Output<br>Enables | PT per<br>Output | JTAG-ISP | t <sub>PD</sub><br>ns | f <sub>CNT</sub><br>MHz | t <sub>PD</sub><br>ns | t <sub>ss</sub> ²<br>ns | t <sub>C0</sub> 3<br>ns | I <sub>CC</sub> mA<br>(Static) |

| M5(LV)-384/120-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-384/120-10 | -        | 384                       |      | ,                   | (2)               |                  |          | 10                    | 100                     | 12                    | 5                       | 7                       |                                |

| M5(LV)-384/120-12 | 160PQFP  | (15,000)                  | 120  | 4                   | 48                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 75                             |

| M5(LV)-384/120-15 |          |                           | Ì    |                     |                   | 1                |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5(LV)-384/160-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-384/160-10 | 20000050 | 384                       | 160  | 4                   | 48                | 11- 4- 20        | Nee      | 10                    | 100                     | 12                    | 5                       | 7                       |                                |

| M5(LV)-384/160-12 | 208PQFP  | (15,000)                  | 100  | 4                   | 48                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 75                             |

| M5(LV)-384/160-15 | -        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5(LV)-384/184-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-384/184-10 | 2400000  | 384                       | 104  | 4                   | 40                | 11- 4- 20        | Vez      | 10                    | 100                     | 12                    | 5                       | 7                       |                                |

| M5(LV)-384/184-12 | 240PQFP  | (15,000)                  | 184  | 4                   | 48                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 75                             |

| M5(LV)-384/184-15 |          |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5(LV)-384/192-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-384/192-10 | 25(20)   | 384                       | 100  | 4                   | 6                 |                  |          | 10                    | 100                     | 12                    | 5                       | 7                       | <u>-</u> -                     |

| M5(LV)-384/192-12 | - 256BGA | (15,000)                  | 192  | 4                   | 48                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 75                             |

| M5(LV)-384/192-15 | 7        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5(LV)-512/120-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-512/120-10 | 1(00000  | 512                       | 100  | 4                   | 0                 |                  |          | 10                    | 100                     | 12                    | 5                       | 7                       | 100                            |

| M5(LV)-512/120-12 | 160PQFP  | (20,000)                  | 120  | 4                   | 64                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 100                            |

| M5(LV)-512/120-15 |          |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5(LV)-512/160-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-512/160-10 |          | 512                       | 100  |                     |                   |                  |          | 10                    | 100                     | 12                    | 5                       | 7                       | 100                            |

| M5(LV)-512/160-12 | 208PQFP  | (20,000)                  | 160  | 4                   | 64                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 100                            |

| M5(LV)-512/160-15 | -        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | · 20                  | 8                       | 10                      |                                |

| M5(LV)-512/184-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-512/184-10 | 14000FF  | 512                       | 104  | 4                   | 64                | Up to 20         | V        | 10                    | 100                     | 12                    | 5                       | 7                       | 100                            |

| M5(LV)-512/184-12 | 240PQFP  | (20,000)                  | 184  | 4                   | 04                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 100                            |

| M5(LV)-512/184-15 | 7        | 1                         |      |                     |                   | 1                |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5(LV)-512/192-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-512/192-10 | 25 (BC)  | 512                       | 102  | 4                   | 64                | Un to 22         | Vac      | 10                    | 100                     | 12                    | 5                       | 7                       | 100                            |

| M5(LV)-512/192-12 | - 256BGA | (20,000)                  | 192  | 4                   | 64                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 100                            |

| M5(LV)-512/192-15 | 7        |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      |                                |

| M5(LV)-512/256-7  |          |                           |      |                     |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |                                |

| M5(LV)-512/256-10 | 25200    | 512                       | 256  | 4                   |                   | 1 22             | N        | 10                    | 100                     | 12                    | 5                       | 7                       | 100                            |

| M5(LV)-512/256-12 | - 352BGA | (20,000)                  | 256  | 4                   | 64                | Up to 32         | Yes      | 12                    | 83.3                    | 15                    | 6                       | 8                       | 100                            |

| M5(LV)-512/256-15 |          |                           |      |                     |                   |                  |          | 15                    | 62.5                    | 20                    | 8                       | 10                      | 1                              |

#### Notes:

1. MACH devices are dual-marked with both commercial and industrial speeds while CMOS PAL devices are marked separately.

2. Minimum setup time from input, I/O, or feedback to clock.

3. Maximum time from clock to output.

Overview

### Table 4. MACH 5A Devices<sup>1</sup>

|                     |           |            |      |                     |                   |                  |          | Comr                  | nercial                 | Ind'l <sup>2</sup>    |                         |                         |

|---------------------|-----------|------------|------|---------------------|-------------------|------------------|----------|-----------------------|-------------------------|-----------------------|-------------------------|-------------------------|

| Device              | Package   | Macrocells | I/Os | Dedicated<br>Inputs | Output<br>Enables | PT per<br>Output | JTAG-ISP | t <sub>PD</sub><br>ns | f <sub>CNT</sub><br>MHz | t <sub>PD</sub><br>ns | t <sub>ss</sub> ³<br>ns | t <sub>co</sub> 4<br>ns |

| M5A(3,5)-128/68-5   |           |            |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                       | 4.5                     |

| M5A(3,5)-128/68-7   | 100000    | 100        | 6    | ,                   |                   |                  |          | 7.5                   | 125                     | 10                    | 4                       | 6                       |

| M5A(3,5)-128/68-10  | 100PQFP   | 128        | 68   | 4                   | 16                | Up to 32         | Yes      | 10                    | 100                     | 12                    | 5                       | 7                       |

| M5A(3,5)-128/68-12  |           | × .        |      |                     |                   |                  |          | 12                    | 83.3                    | 15                    | 6                       | 8                       |

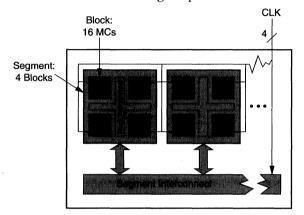

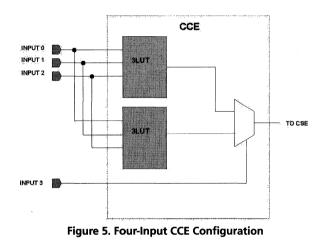

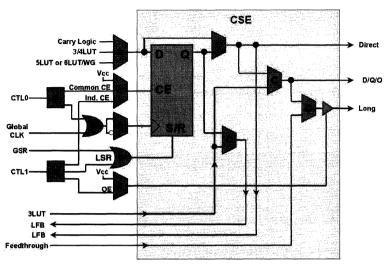

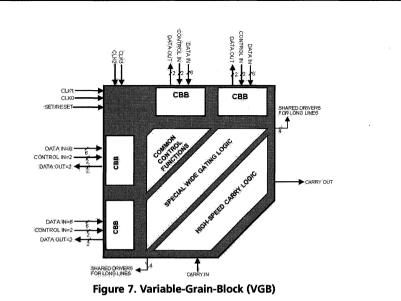

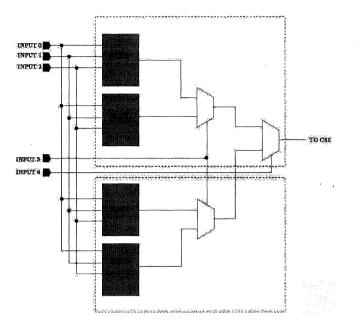

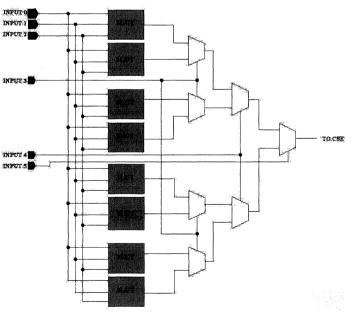

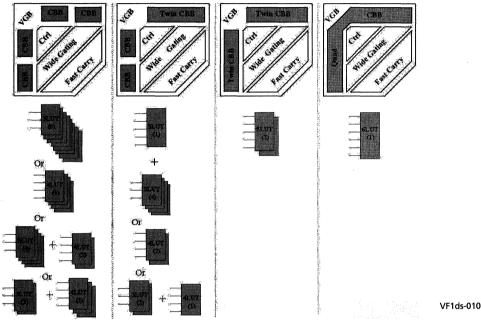

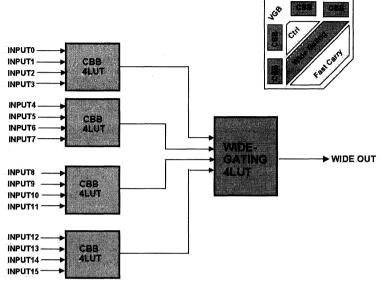

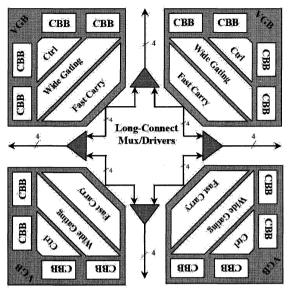

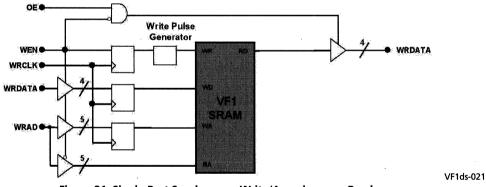

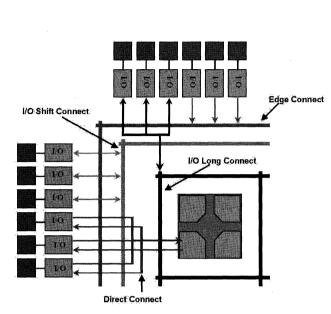

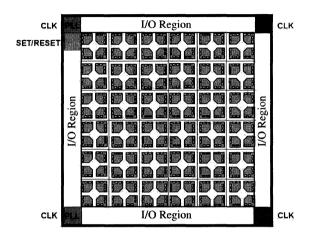

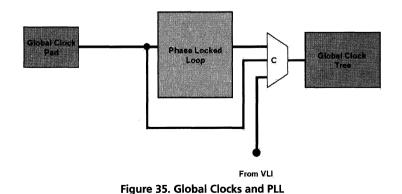

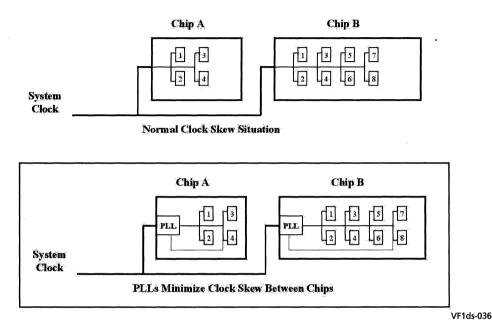

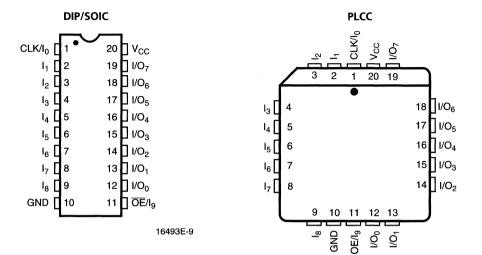

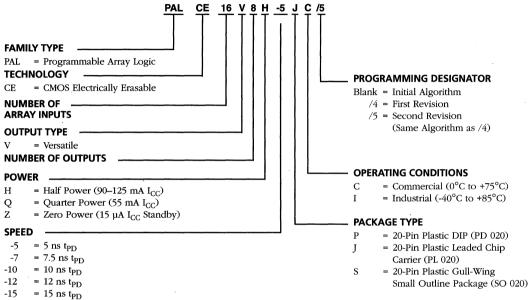

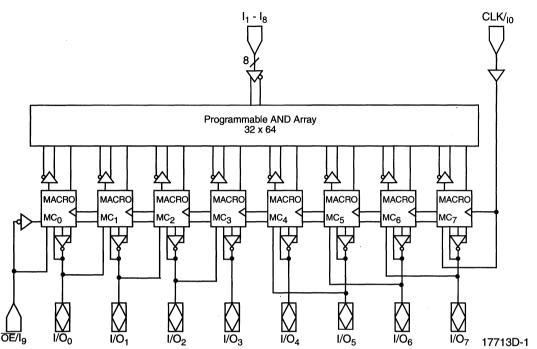

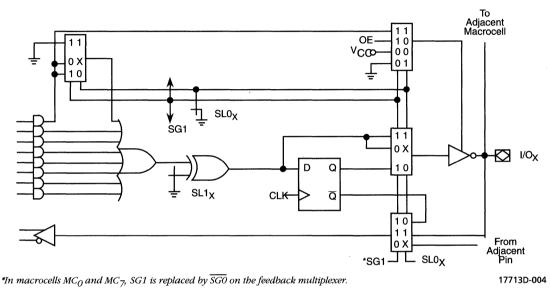

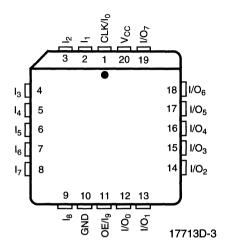

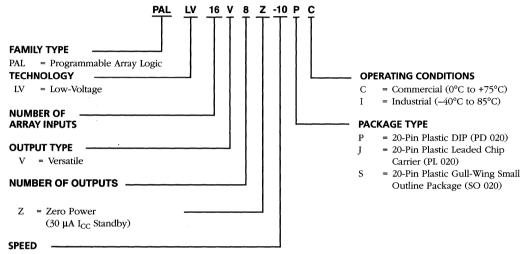

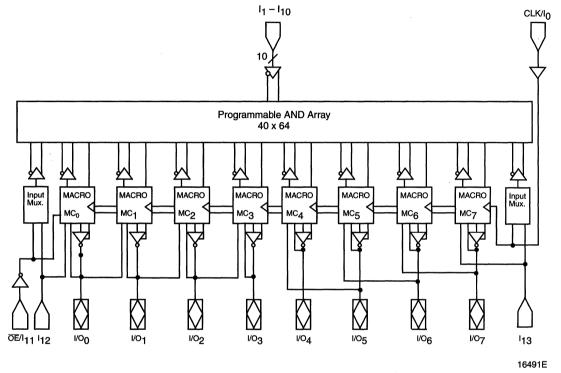

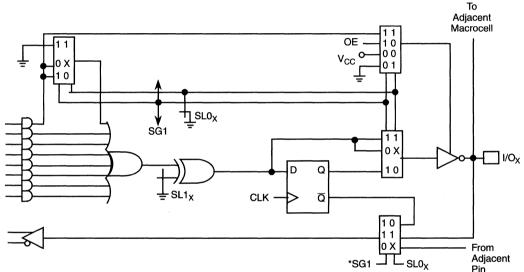

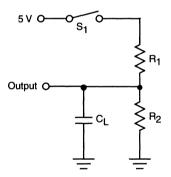

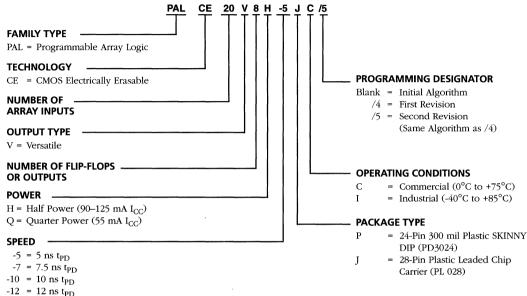

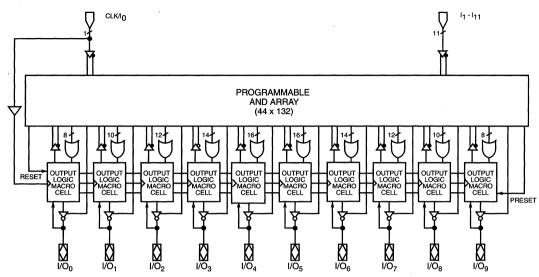

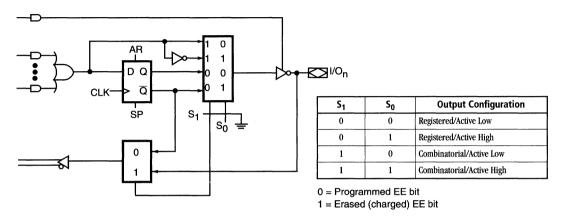

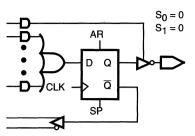

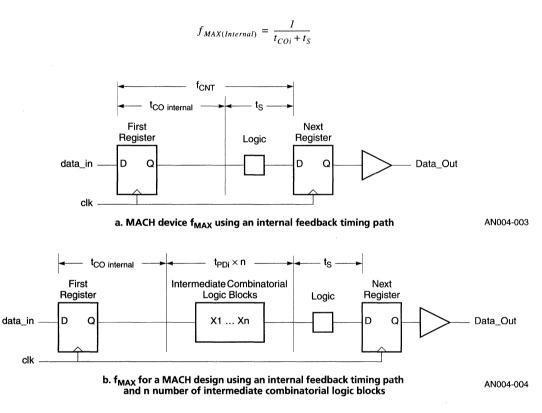

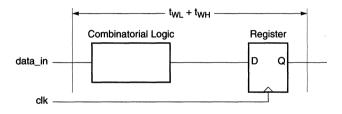

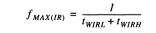

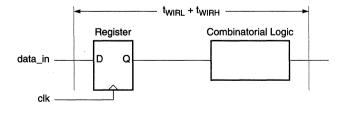

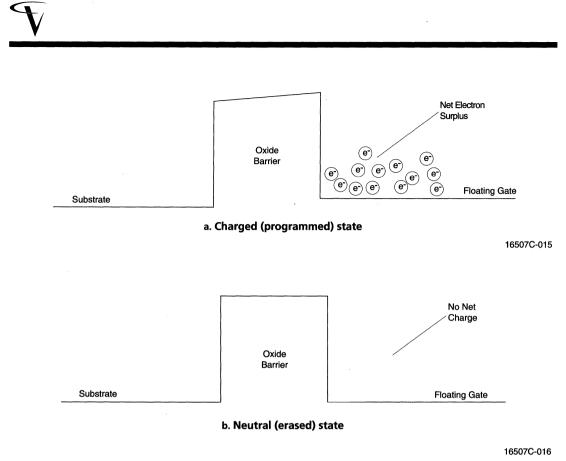

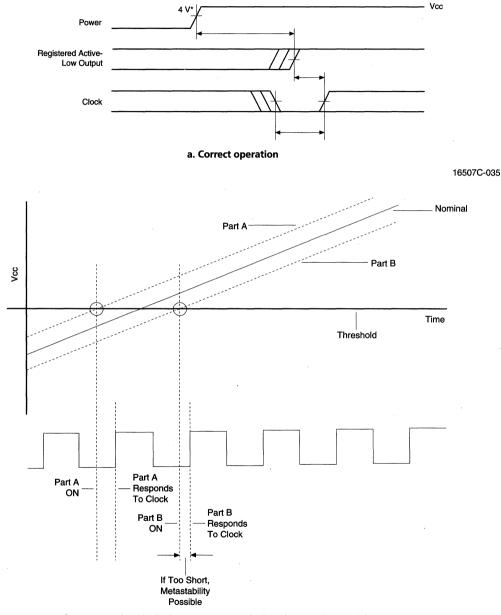

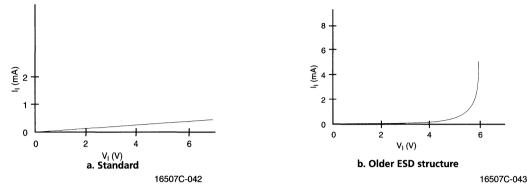

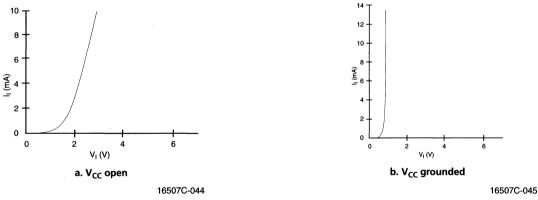

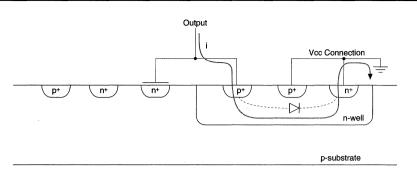

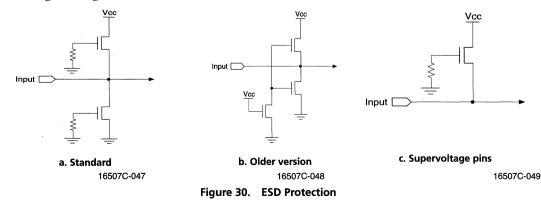

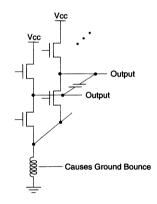

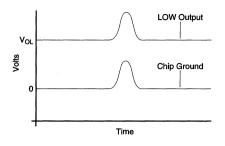

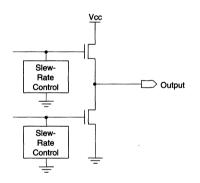

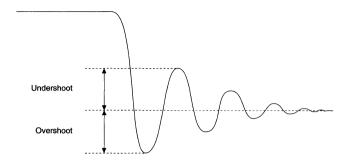

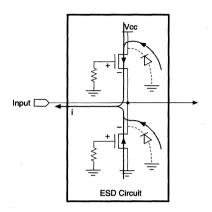

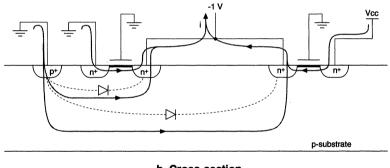

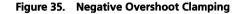

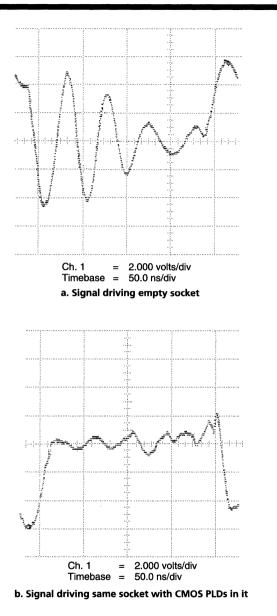

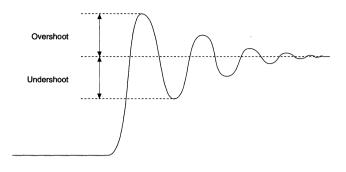

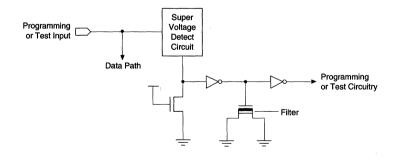

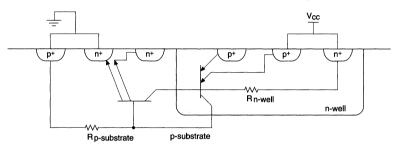

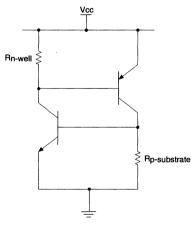

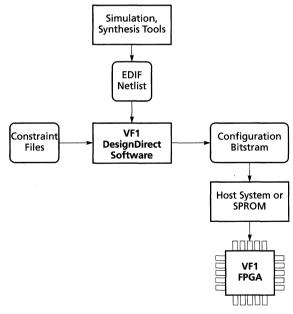

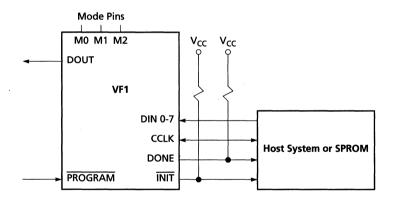

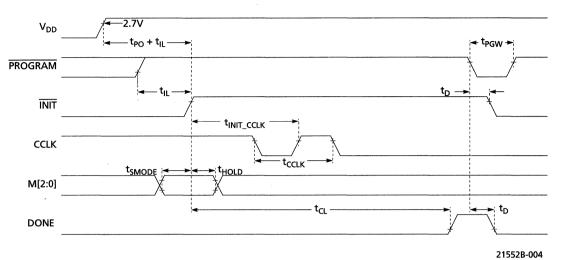

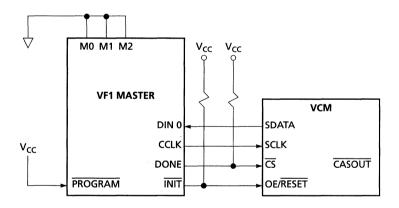

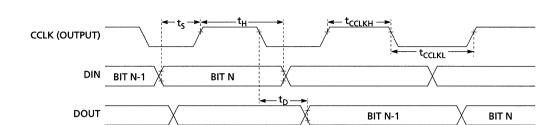

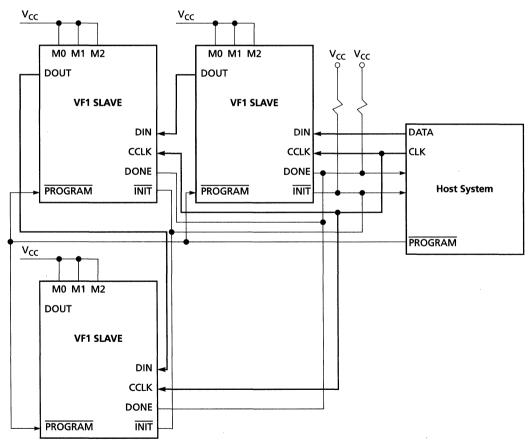

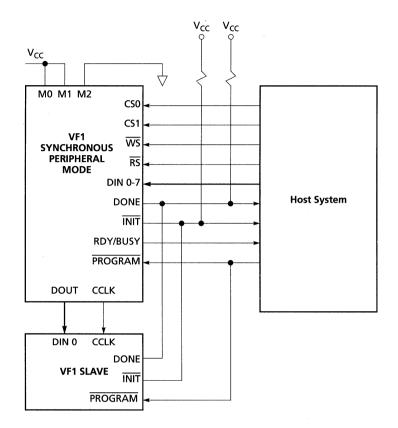

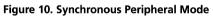

| M5A(3,5)-128/74-5   |           |            |      |                     |                   |                  |          | 5.5                   | 181.8                   | 7.5                   | 3                       | 4.5                     |