Programmable Logic Handbook/Data Book 1986–1987

# PROGRAMMABLE

PAL" Devices

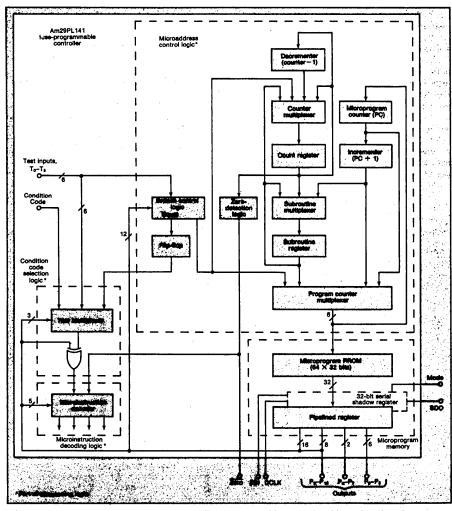

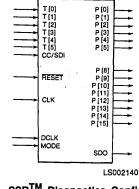

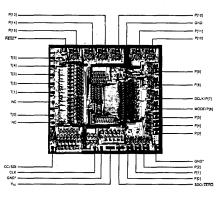

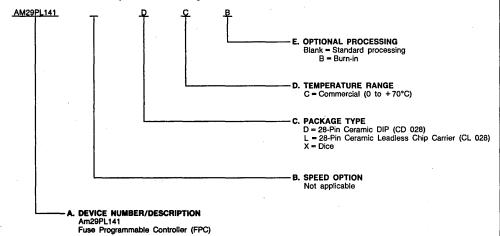

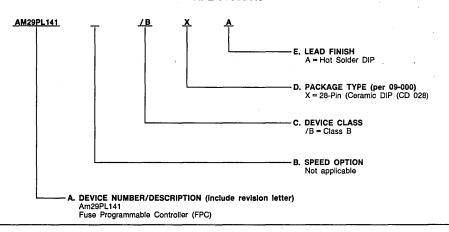

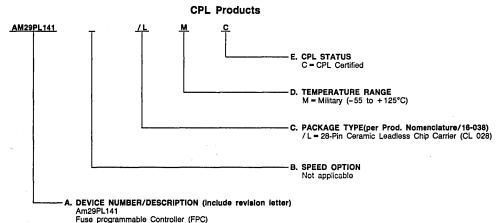

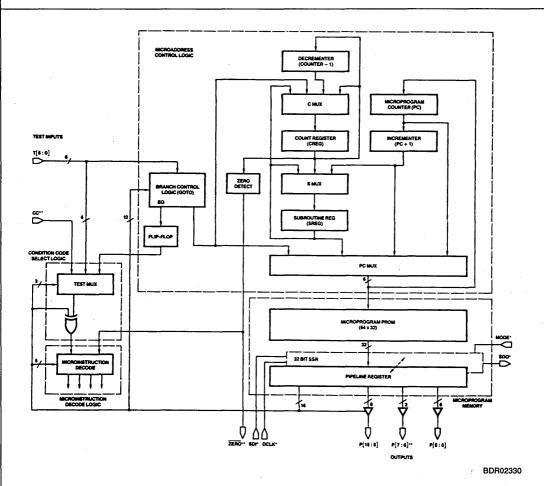

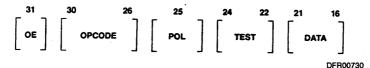

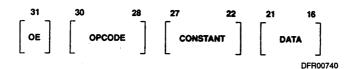

Fuse Programmable Controller

PROMS

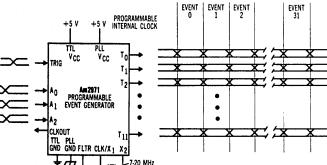

Programmable Event Generator

Sequencers

# **Advanced Micro Devices**

# Programmable Logic Handbook/Data Book

The International Standard of Quality guarantees a 0.05% AQL on all electrical parameters, AC and DC, over the entire operating range.

INTSID-500

© 1986 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

#### **CREDITS**

المساء والمساواة

Prepared by the Fuse Programmable Logic (FPL) staff at Advanced Micro Devices, Inc. (listed in alphabetical order)

#### **Editing:**

Jeri Burdick Naushik Desai

#### Technical:

Om Agrawal Peter Alfke Matthew Bonn Sal Cagnina Rick Calle William Chen Paul Coggeshall Naushik Desai Vineet Dujari Steve Grossman Alexandra Huff Alfred Jey Doug Kern Arthur Khu Brent McKay Teresa Ordez John Potterbom Mitch Richman Kapil Shankar Bill Sievers

Jenny Yee

#### **TRADEMARKS**

ABEL, DASH/ABEL, FINGERPRINT, PLDtest, and PROMlink are trademarks of Data I/O Corporation.

CUPL is a trademark of Personal CAD Systems, Inc.

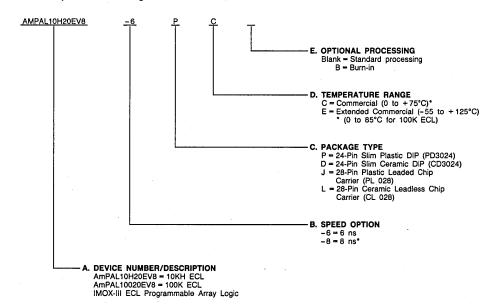

IMOX-III is a trademark of Advanced Micro Devices, Inc.

MULTIBUS is a trademark of Intel Corporation.

PALASAM is a registered trademark of Monolithic Memories, Inc.

Z8000 is a trademark of Zilog, Inc.

#### **PREFACE**

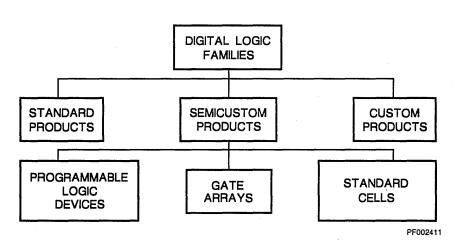

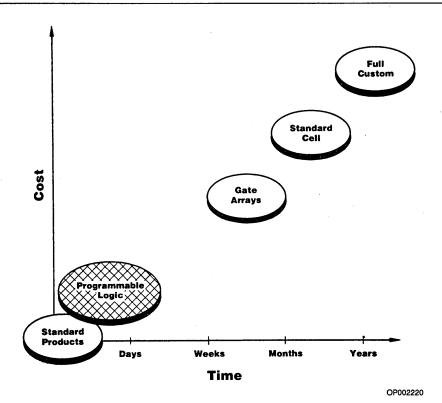

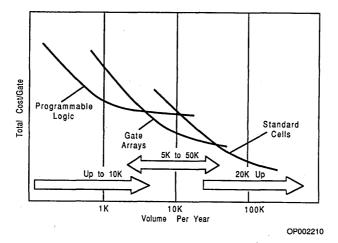

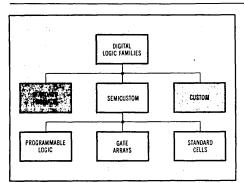

At Advanced Micro Devices we are committed to helping you solve design problems with innovative products that give you maximum flexibility to meet your particular needs. In the past, you often have had to choose between costly semi-custom products and standard devices that limit your design options. Now there's another choice.

Programmable Array Logic (PAL) devices from AMD give you the best of two worlds: the architectural flexibility of custom design and immediate availability, multiple-sourcing, and low cost of standard products.

PAL devices are user-programmable logic building blocks that give you the freedom to structure components for a specific application, often using a single PAL package to create functions that once would have required the use of hundreds of conventional TTL gates.

This handbook is your guide to AMD's growing list of PAL devices. It is intended to be both an introduction to field programmable logic devices, as well as a resource manual for experienced designers. In the following pages you will find data and descriptions of new, proprietary devices from AMD, as well as information on standard products. Whether you need CMOS, ECL, or TTL, AMD offers solutions to your design problems that give you a choice.

Best of all, AMD offers you the industry's leading commitment to quality, reliability, innovation, and customer satisfaction. If you have a question about any of the products described in this book or simply want to know more about the use of programmable logic devices, call your local Advanced Micro Devices' Sales Office.

W.J. Sanders III Chairman, and Chief Executive Officer

#### TABLE OF CONTENTS

#### SECTION 1 — INTRODUCTION TO PROGRAMMABLE LOGIC

| 1.1   |                                                                                                                                                 | ogrammable Logic Design Alternative1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

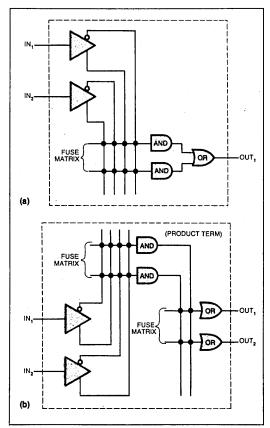

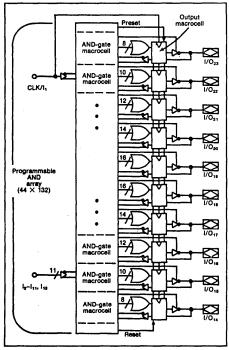

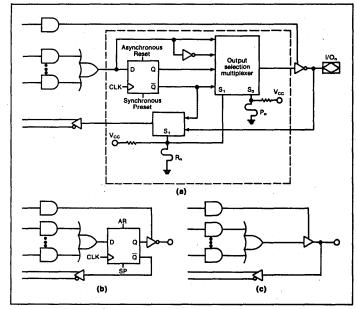

| 1.2   |                                                                                                                                                 | oduction to Programmable Logic Architecture1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

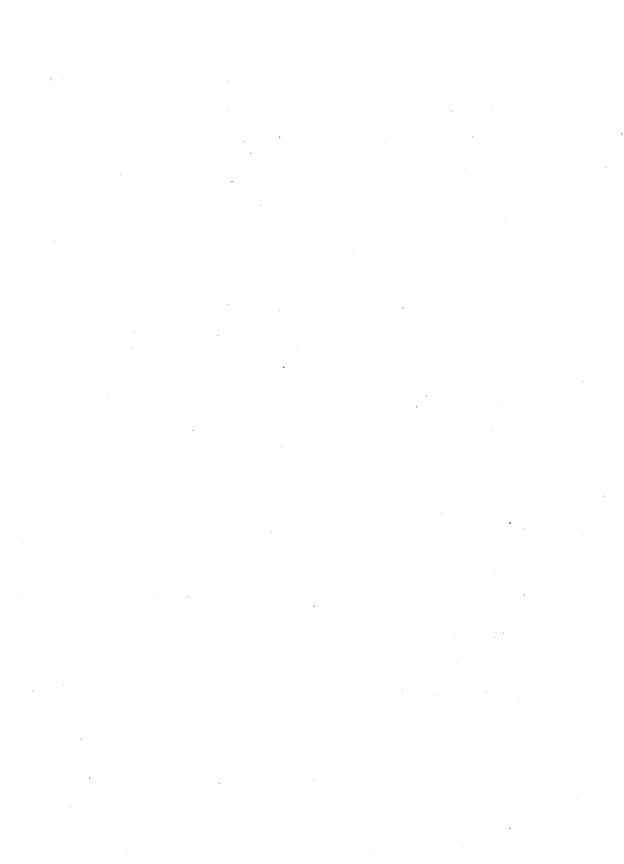

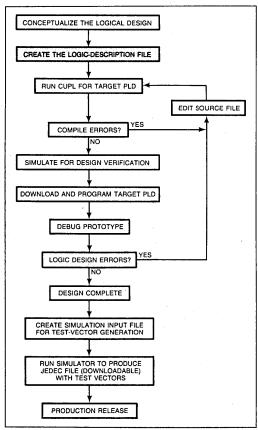

| 1.3   | How to                                                                                                                                          | Design with Programmable Logic Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SECT  | ION 2 .                                                                                                                                         | - SOFTWARE, PROGRAMMING, TESTING, RELIABILITY, AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| JEO 1 | ION 2                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |                                                                                                                                                 | TECHNOLOGY INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

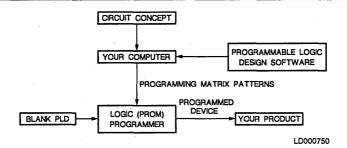

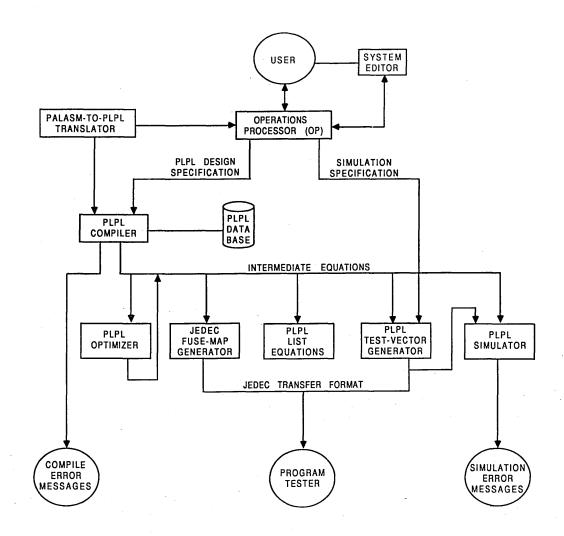

| 2.1   | Softwa                                                                                                                                          | re Support for AMD's Programmable Logic Devices2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 2.1.1                                                                                                                                           | Design-Aid Software for Programmable Logic2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

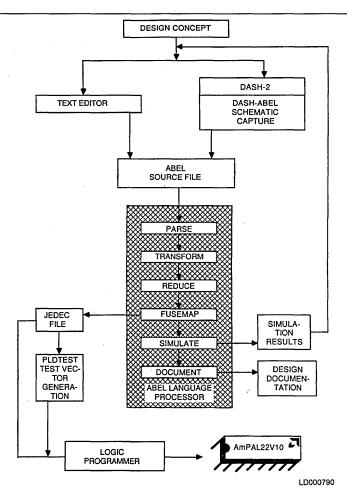

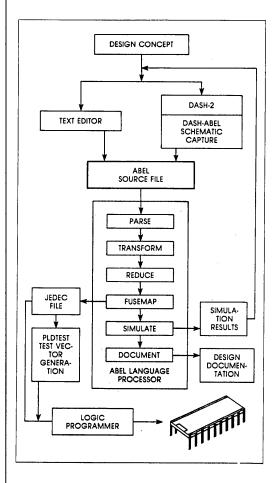

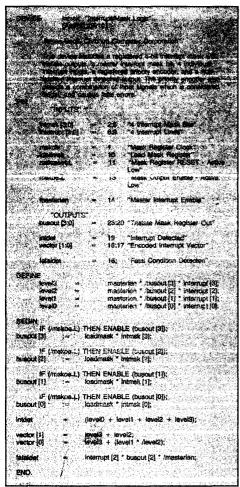

|       | 2.1.2                                                                                                                                           | ABEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | 2.1.2                                                                                                                                           | CUPL, AmCUPL 2-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | 2.1.4                                                                                                                                           | PLPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

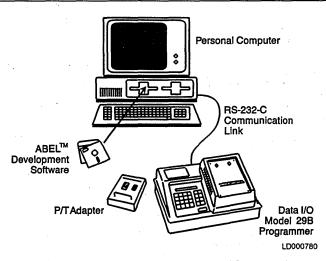

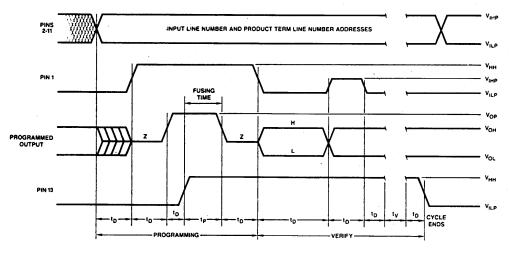

| 2.2   |                                                                                                                                                 | mming Hardware2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3   | _                                                                                                                                               | Information2-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

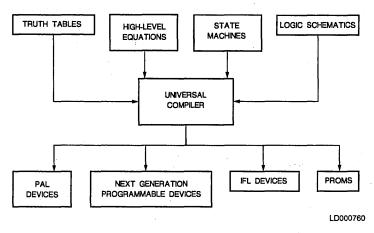

|       | 2.3.1                                                                                                                                           | Factory Testing of PAL Devices2-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 2.3.2                                                                                                                                           | How Testability is Designed into AMD's Programmable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                                                                                                 | Logic Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

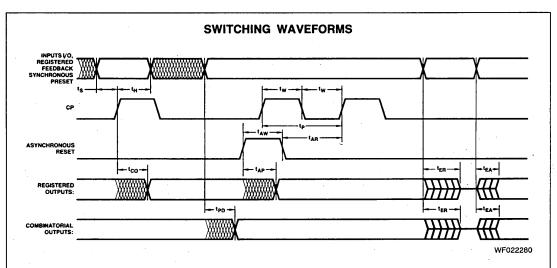

|       | 2.3.3                                                                                                                                           | Specifications for Switching-Delay Minimums                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.4   | AMD F                                                                                                                                           | Programmable Array Logic Reliability2-52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.5   |                                                                                                                                                 | mmable Logic Technology2-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

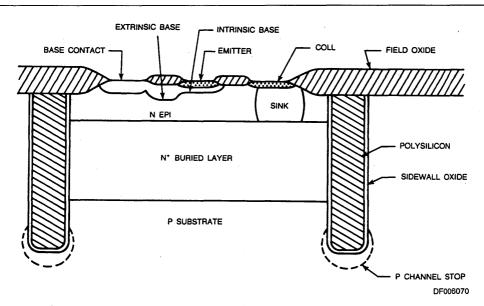

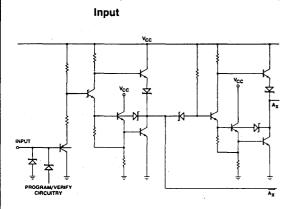

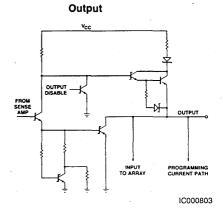

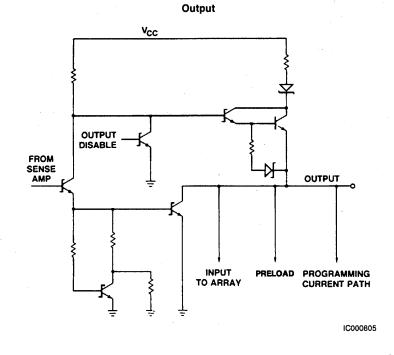

|       | 2.5.1                                                                                                                                           | IMOX-III — Advanced Bipolar Technology for PAL Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

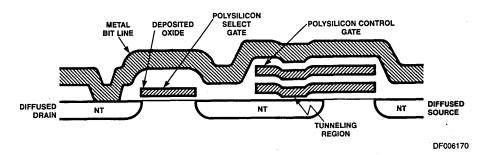

|       | 2.5.2                                                                                                                                           | Advanced CMOS Technology for PAL Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 2.0.2                                                                                                                                           | Advanced GMCG Technology for TAL Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SECT  | ION 3 -                                                                                                                                         | - APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1   | Overvie                                                                                                                                         | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2   |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0.2   | 3.2.1                                                                                                                                           | natorial Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                                                                                 | natorial Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

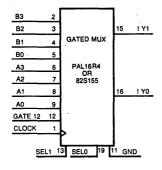

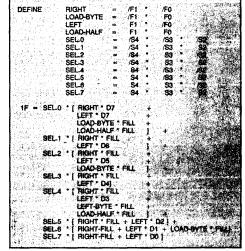

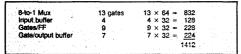

|       | 2.2.2                                                                                                                                           | Multiplexers3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | 3.2.2                                                                                                                                           | Multiplexers 3-3 Demultiplexers 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

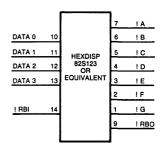

|       | 3.2.3                                                                                                                                           | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

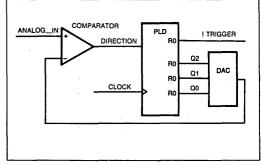

|       | 3.2.3<br>3.2.4                                                                                                                                  | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

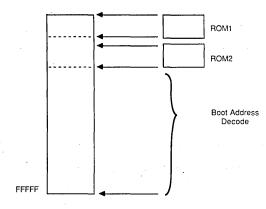

|       | 3.2.3                                                                                                                                           | Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 3.2.3<br>3.2.4<br>3.2.5                                                                                                                         | Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3   | 3.2.3<br>3.2.4<br>3.2.5                                                                                                                         | Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3   | 3.2.3<br>3.2.4<br>3.2.5                                                                                                                         | Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

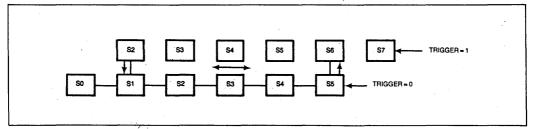

| 3.3   | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer                                                                                                               | Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

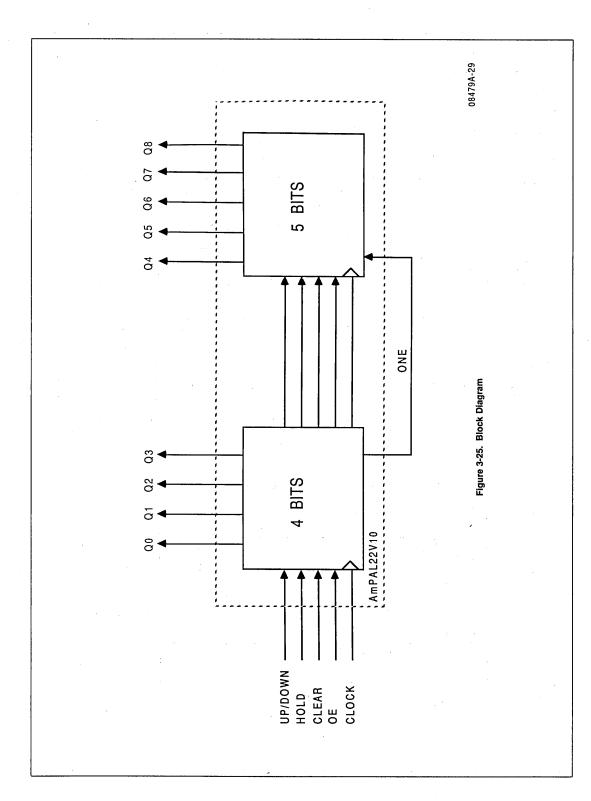

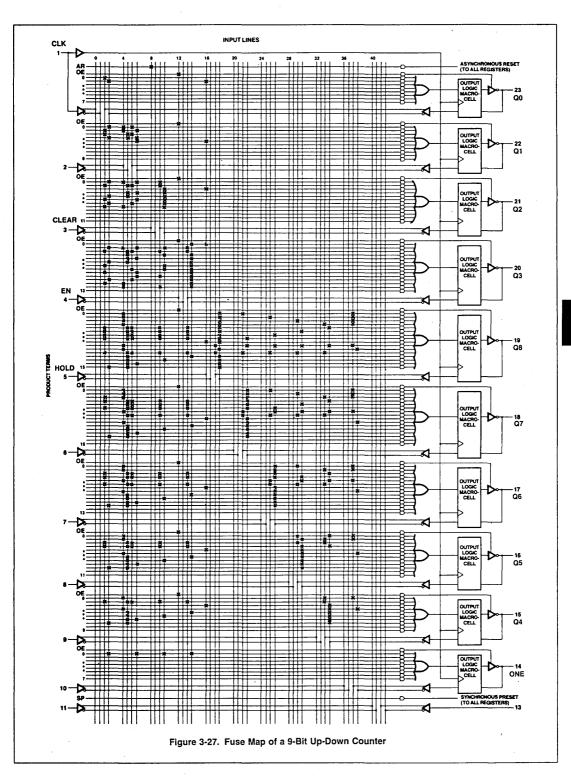

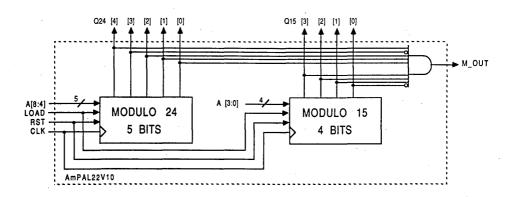

| 3.3   | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2                                                                                             | Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

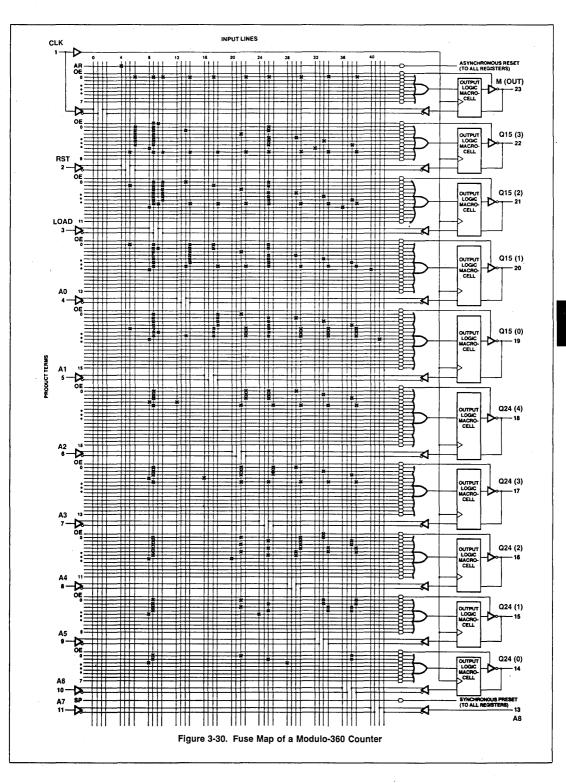

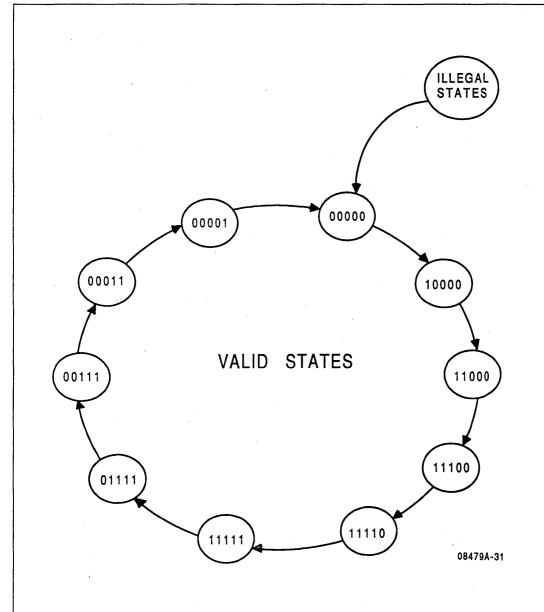

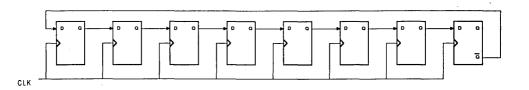

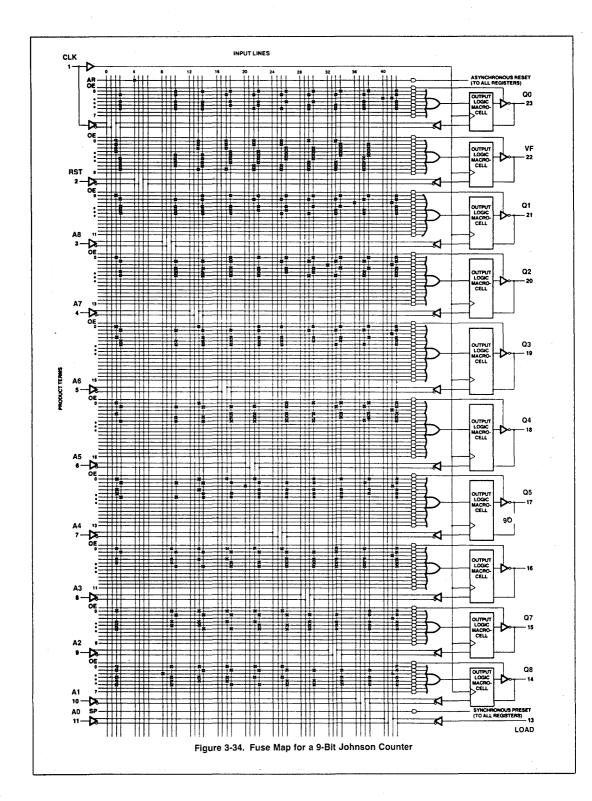

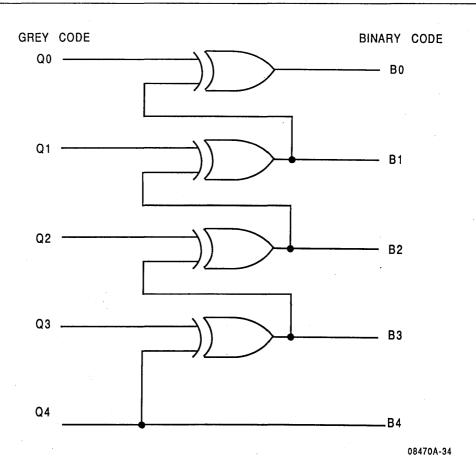

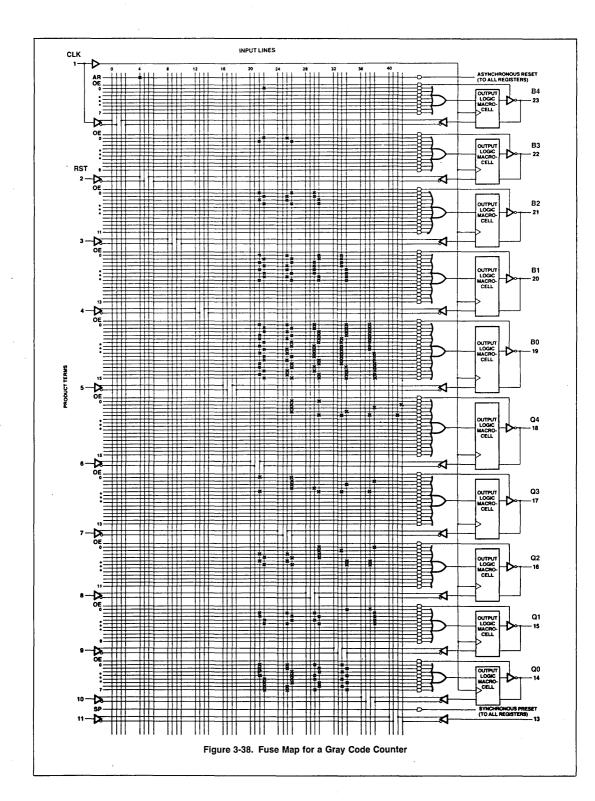

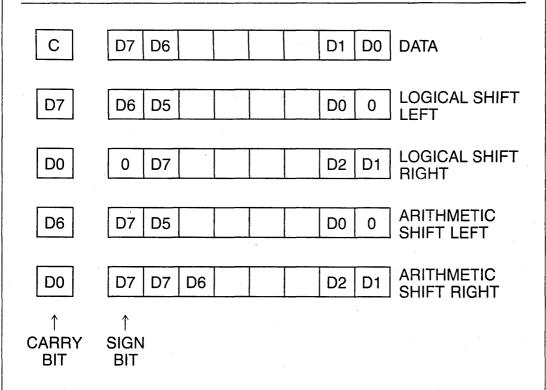

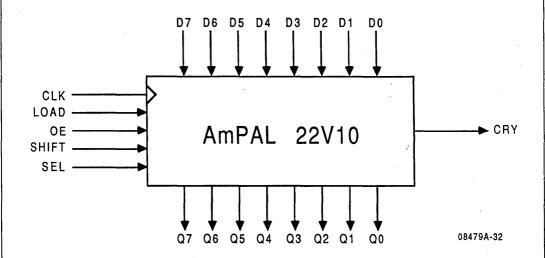

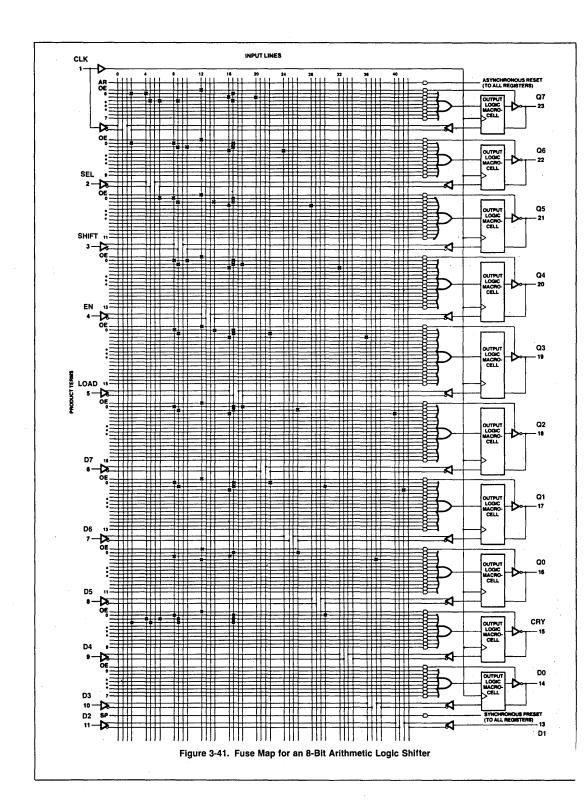

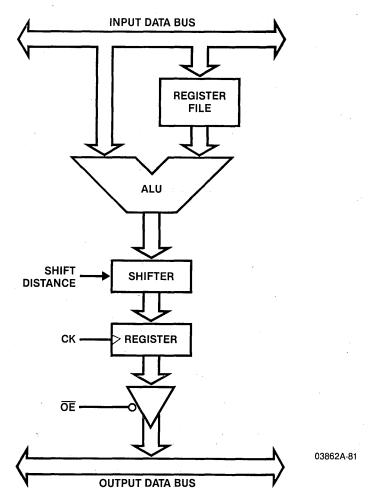

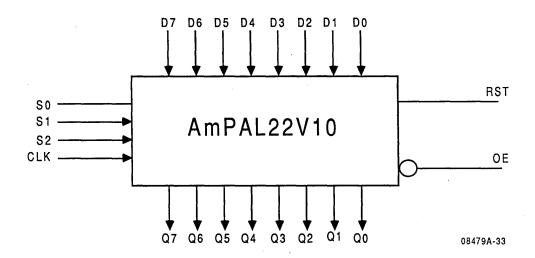

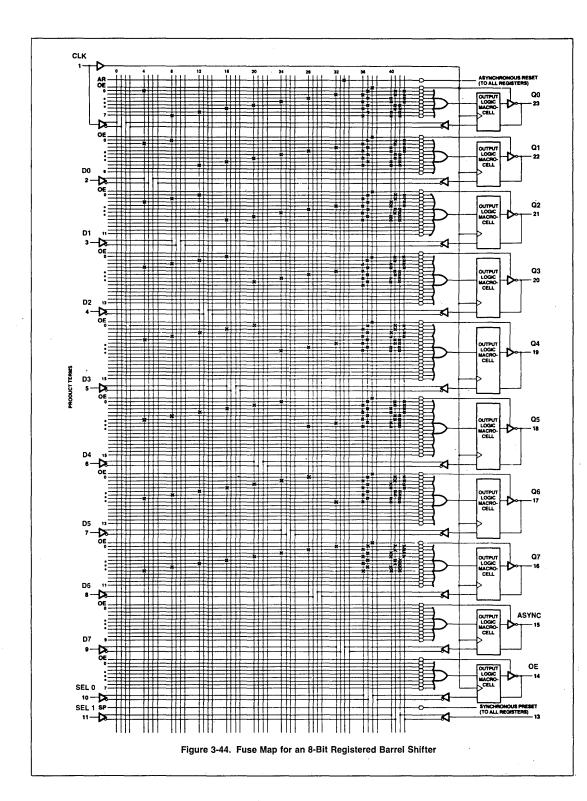

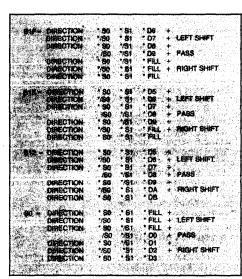

|       | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Micropi                                                                                  | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Itial Logic       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Micropi<br>3.4.1                                                                         | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-25         Itial Logic       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55                                                                                                                                                                                                                                                                                                                                                                                                  |

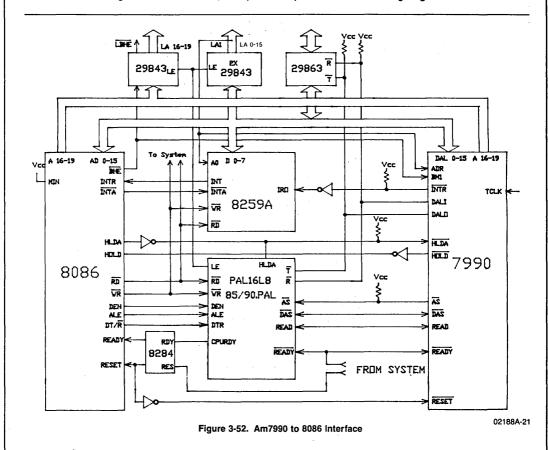

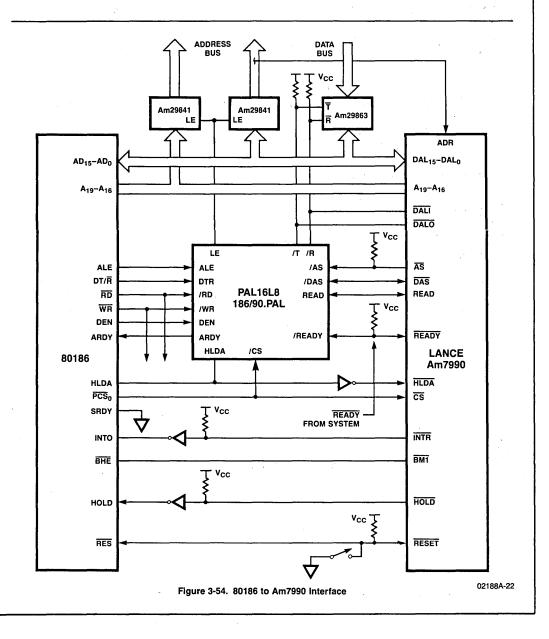

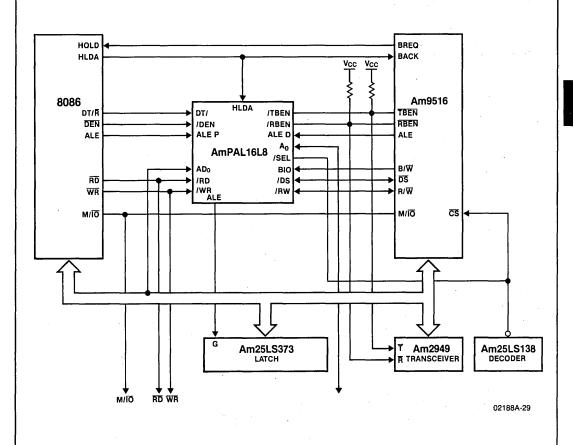

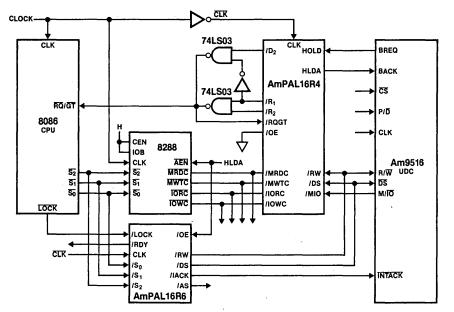

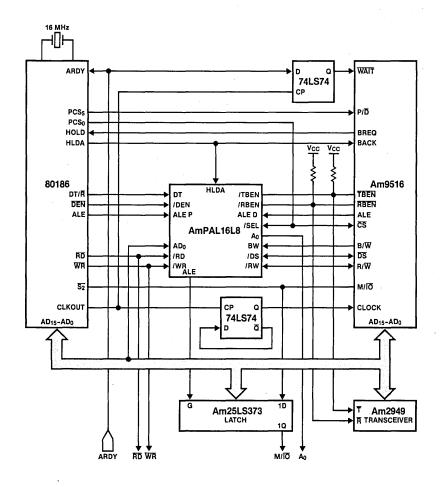

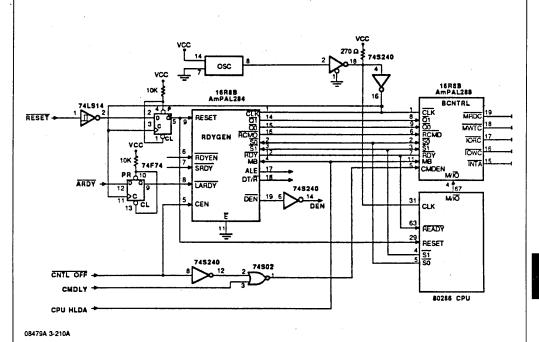

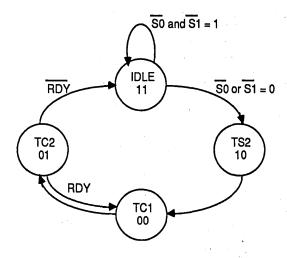

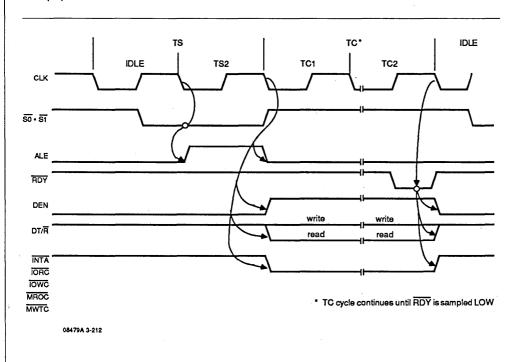

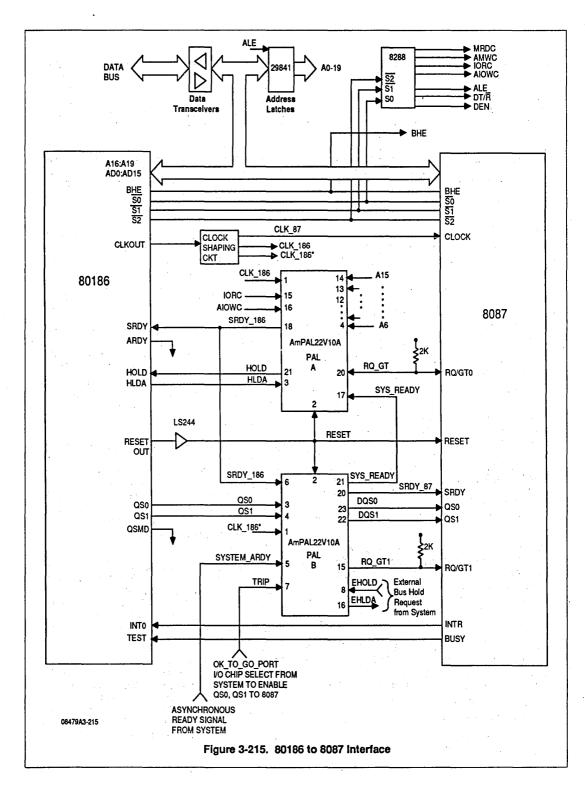

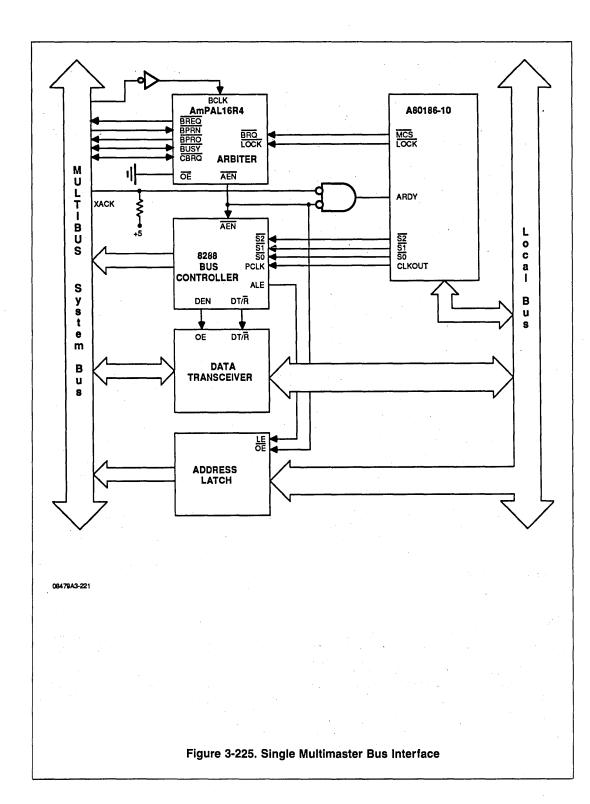

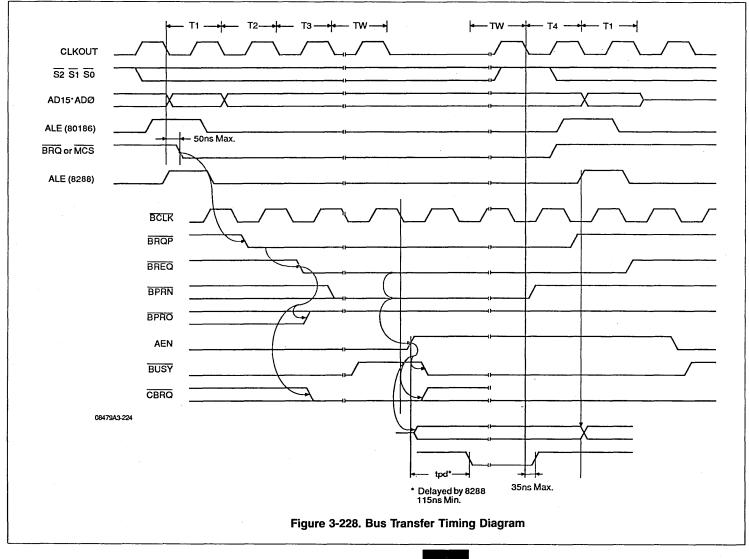

|       | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Micropp<br>3.4.1<br>3.4.2                                                                | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60                                                                                                                                                                                                                                                                                                                                                                          |

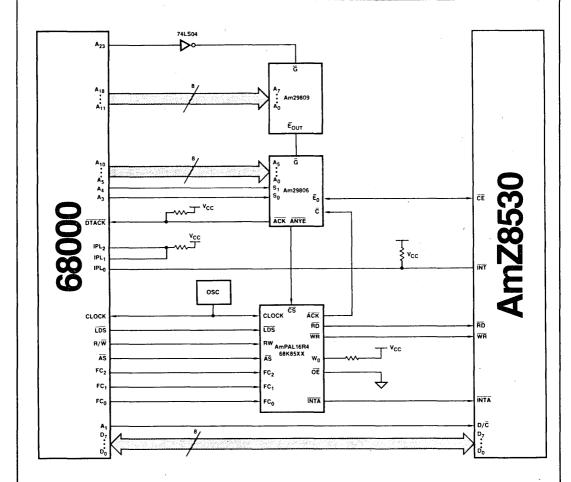

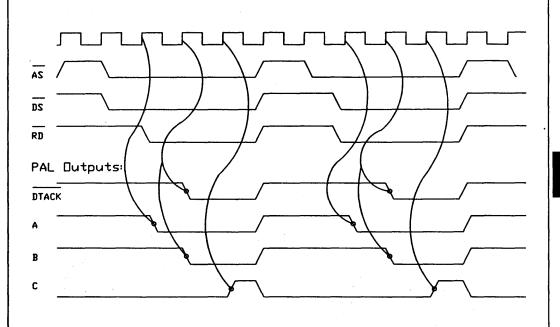

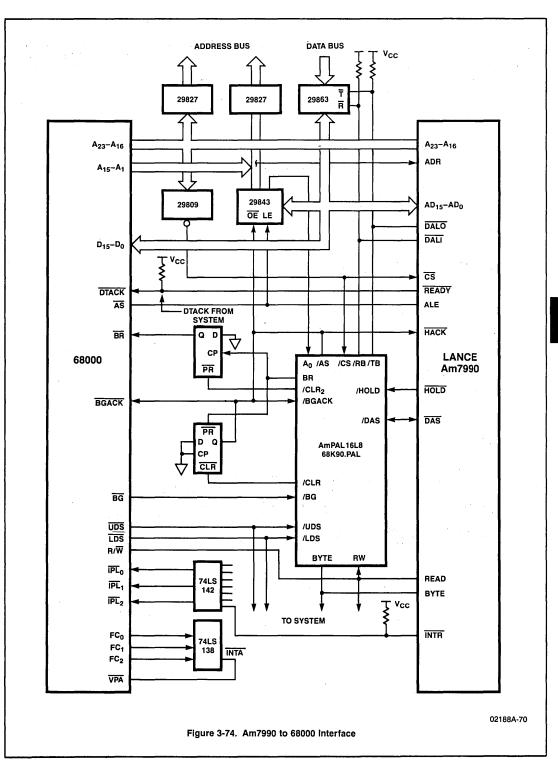

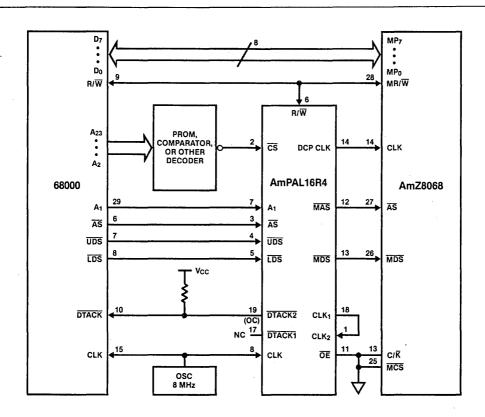

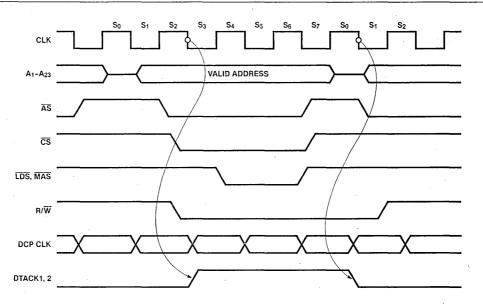

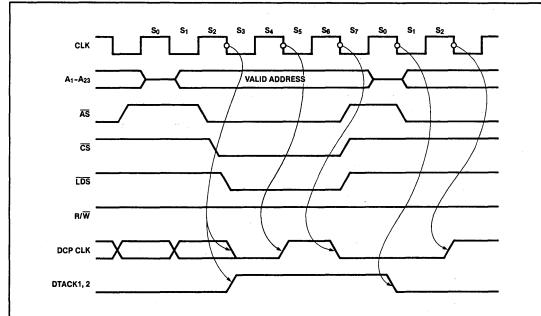

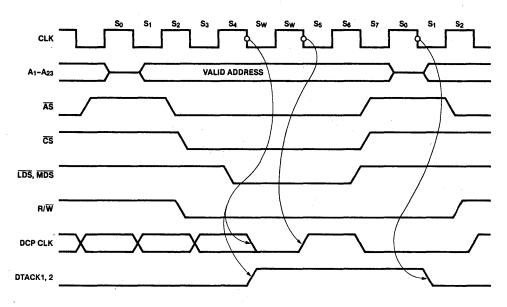

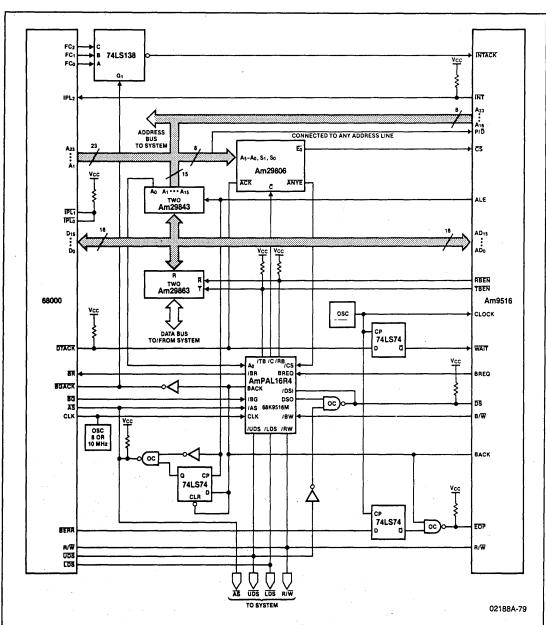

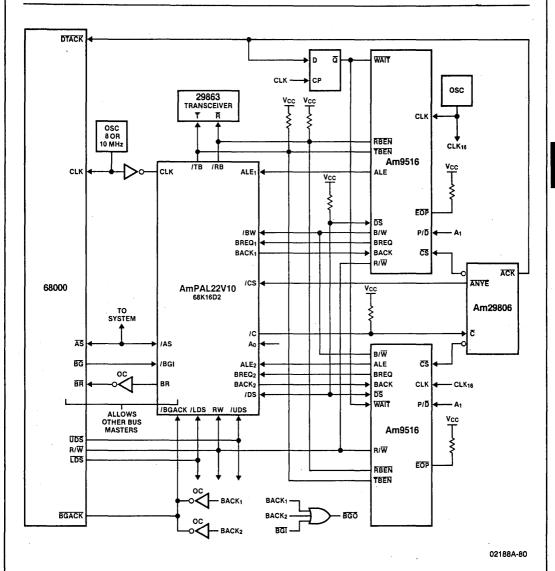

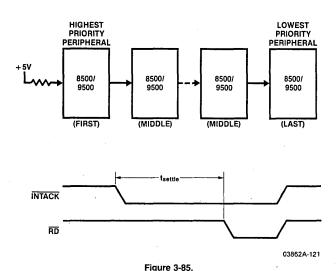

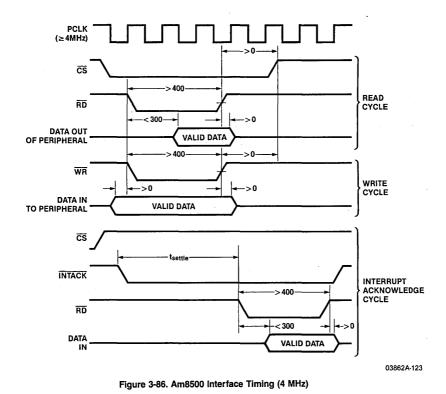

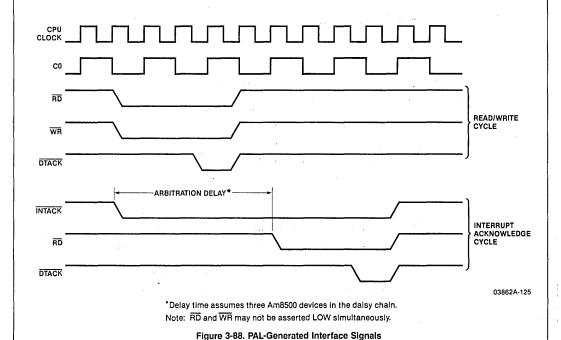

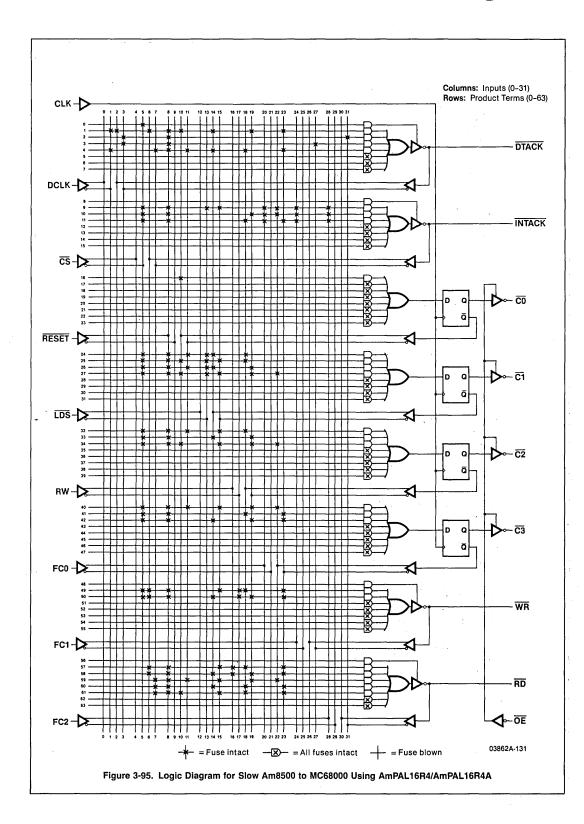

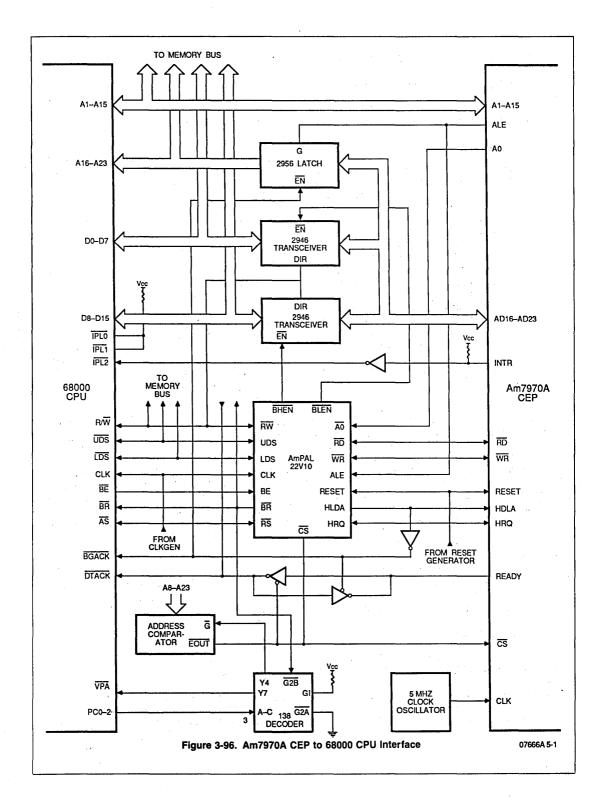

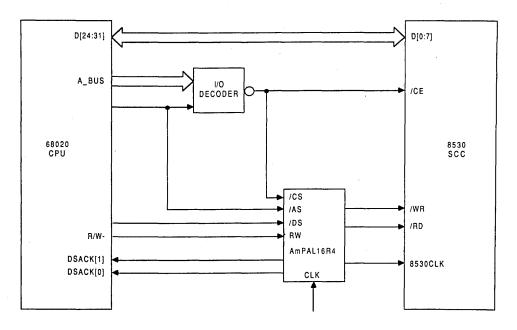

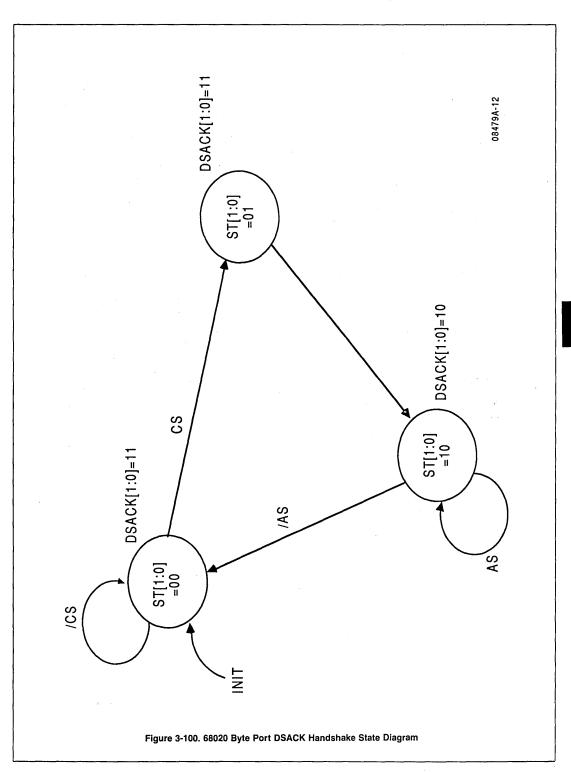

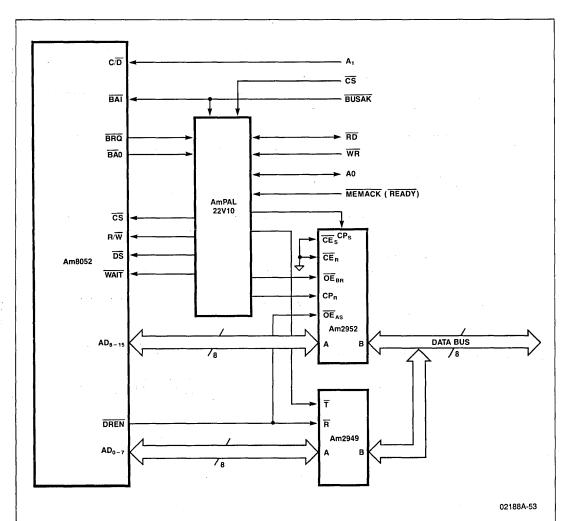

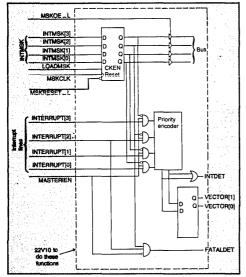

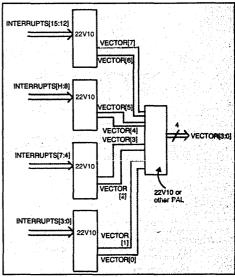

|       | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Microp<br>3.4.1<br>3.4.2<br>3.4.3                                                        | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 68000/68020       3-81                                                                                                                                                                                                                                                                                                                        |

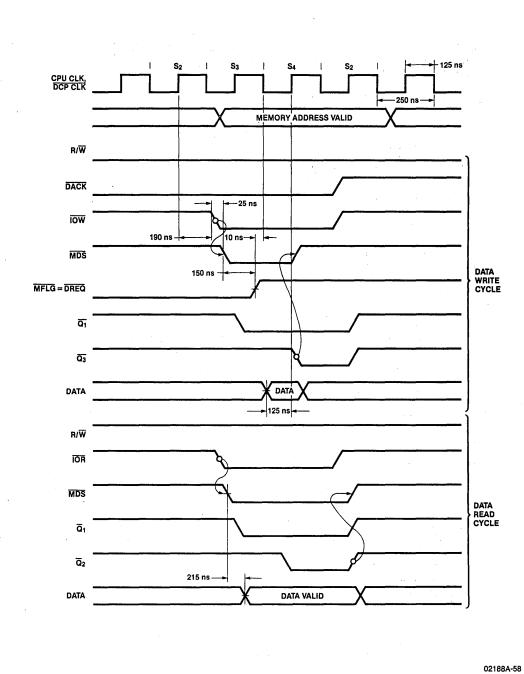

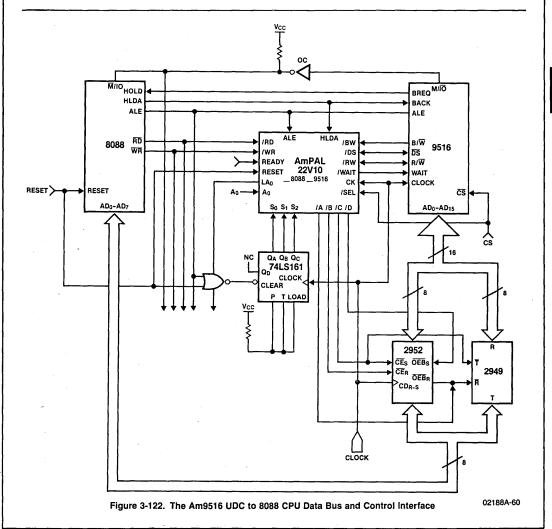

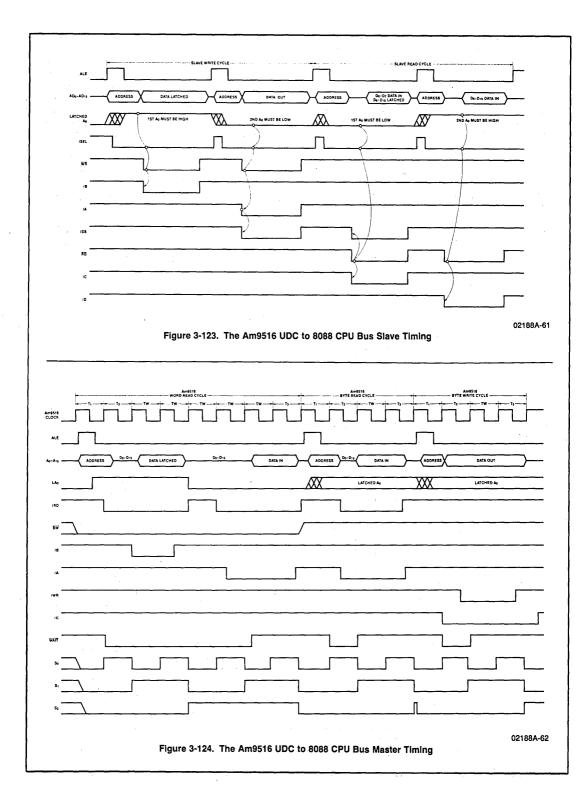

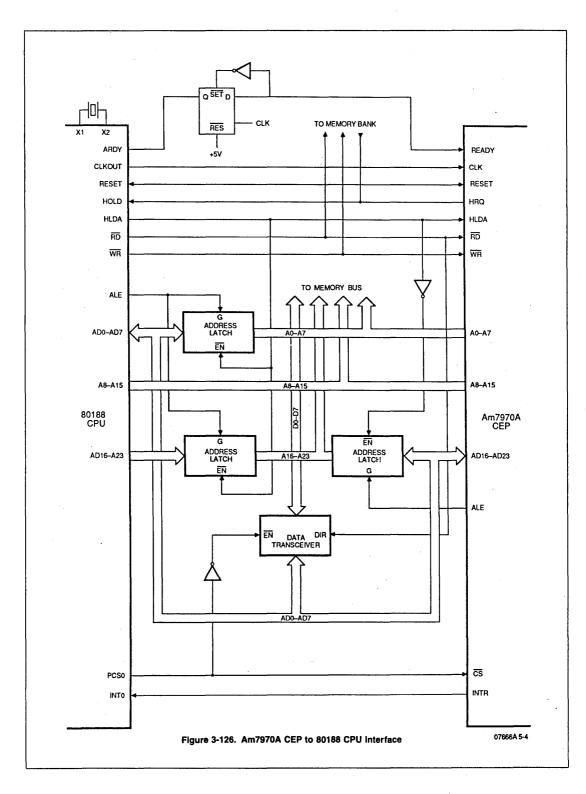

|       | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Microp<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                               | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 6000/68020       3-81         Interfacing to the 8088/80188       3-137                                                                                                                                                                                                                                                                       |

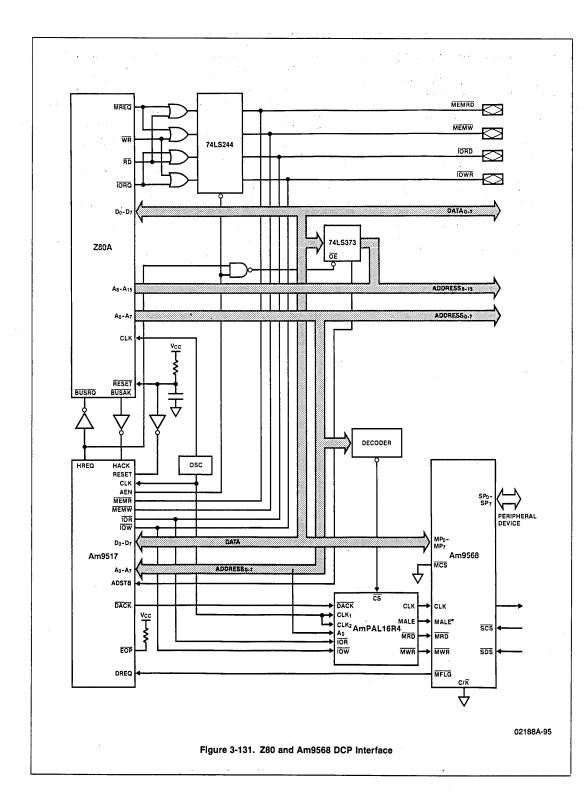

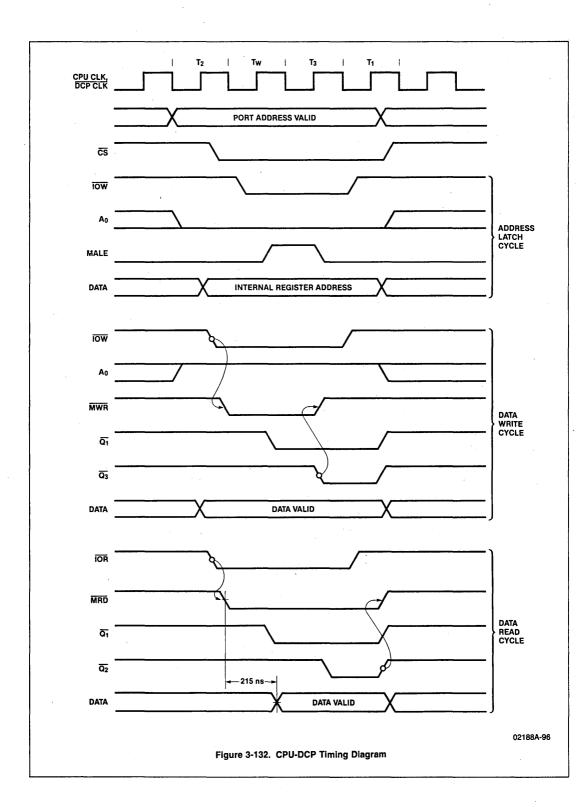

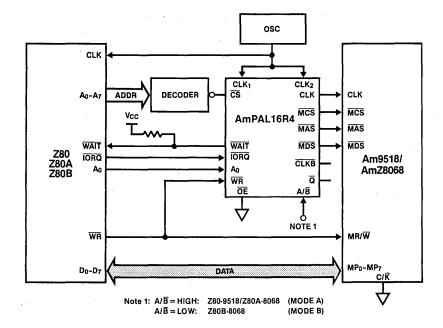

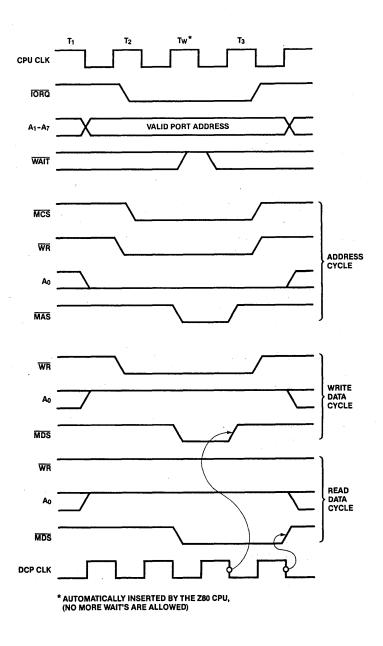

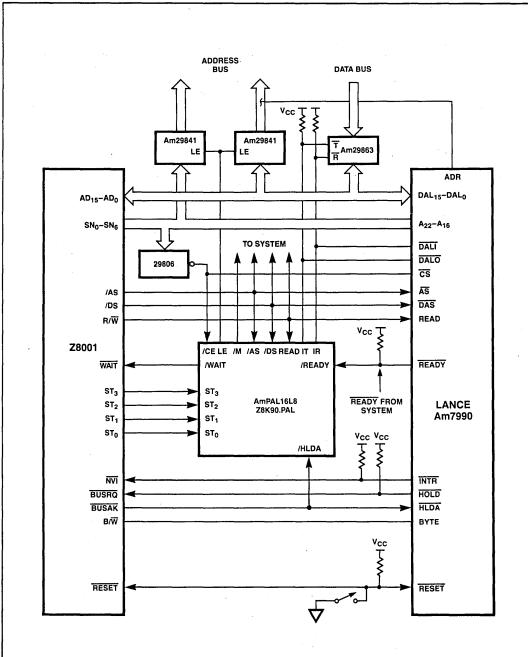

| 3.4   | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Microp<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                                      | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 8088/80188       3-137         Interfacing to the 280/Z8000       3-171                                                                                                                                                                                                                                                                       |

|       | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Micropr<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>Bus In                           | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         recessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 68000/68020       3-81         Interfacing to the 8088/80188       3-137         Interfacing to the Z80/Z8000       3-171         Ierface Logic       3-187                                                                                                                                                                                   |

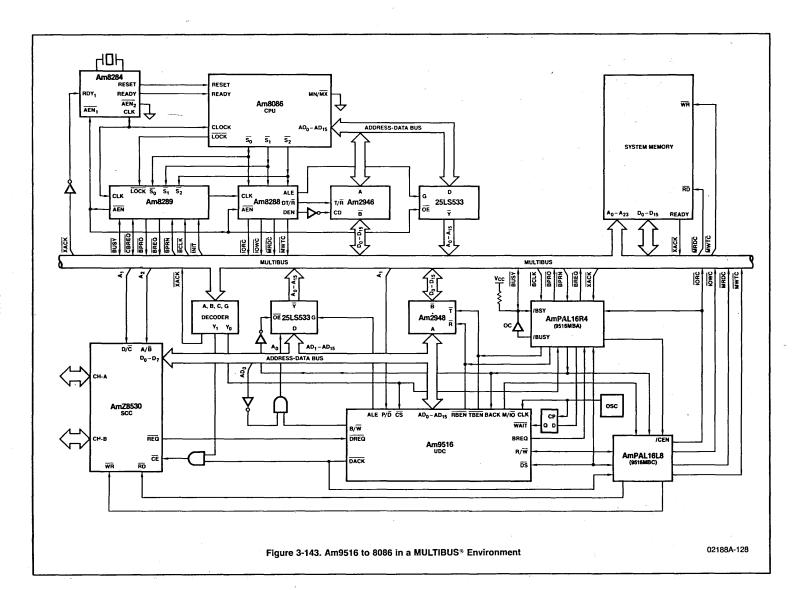

| 3.4   | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Microp<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>Bus In<br>3.5.1                   | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         recessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 68000/68020       3-81         Interfacing to the 8088/80188       3-137         Interfacing to the Z80/Z8000       3-171         lerface Logic       3-187         MULTIBUS to Am9516 Interface       3-187                                                                                                                                  |

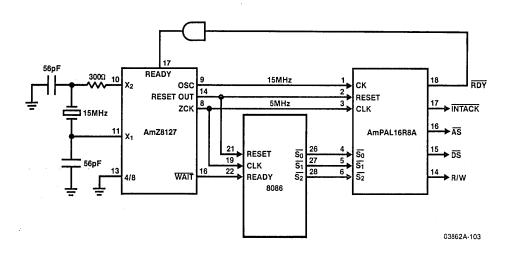

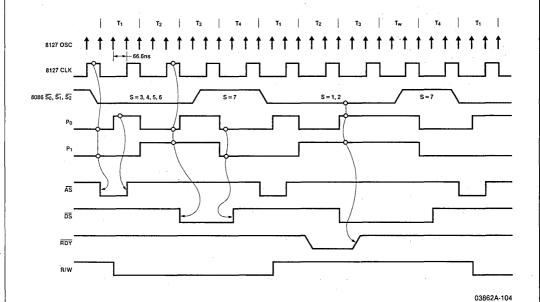

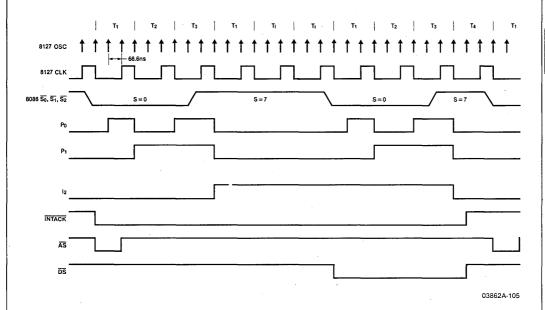

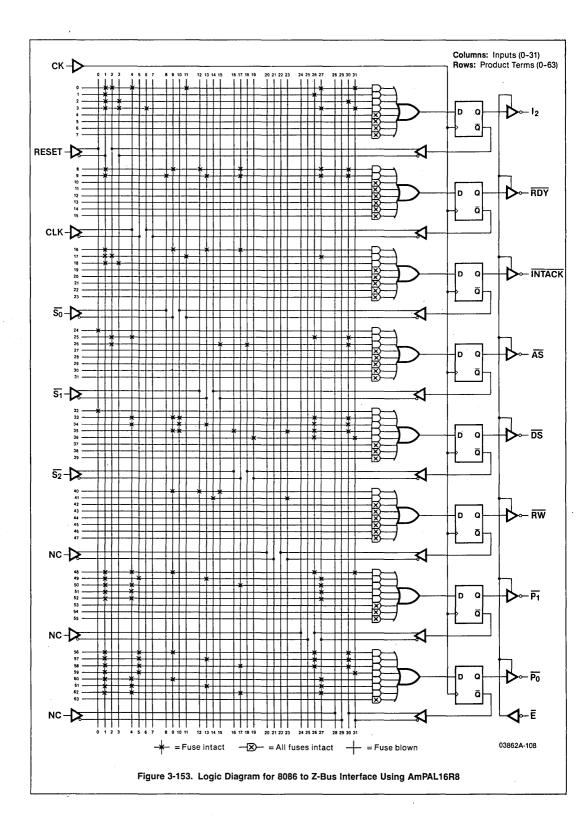

| 3.4   | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Microp<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>Bus In<br>3.5.1<br>3.5.2          | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 8088/80188       3-137         Interfacing to the 280/Z8000       3-81         Interfacing to the Z80/Z8000       3-171         terface Logic       3-187         MULTIBUS to Am9516 Interface       3-187         Z-Bus and 8088/8086 Interface       3-191                                                                                  |

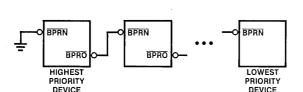

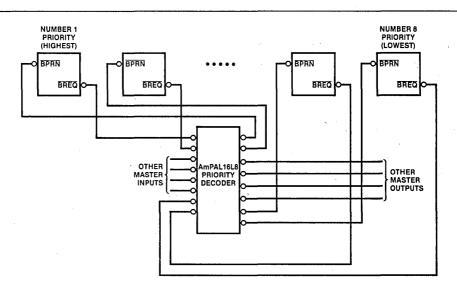

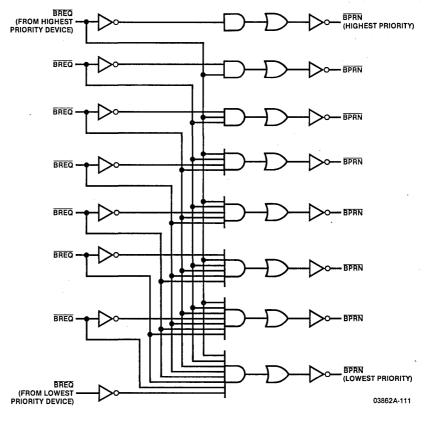

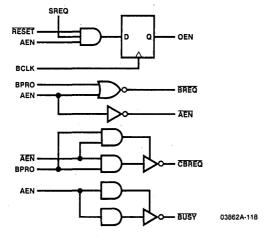

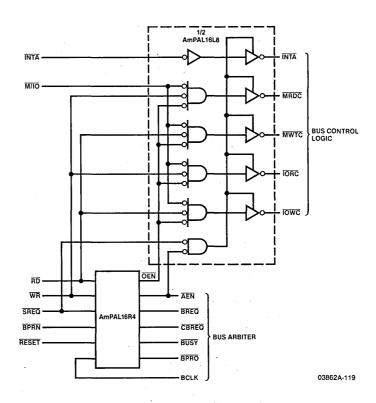

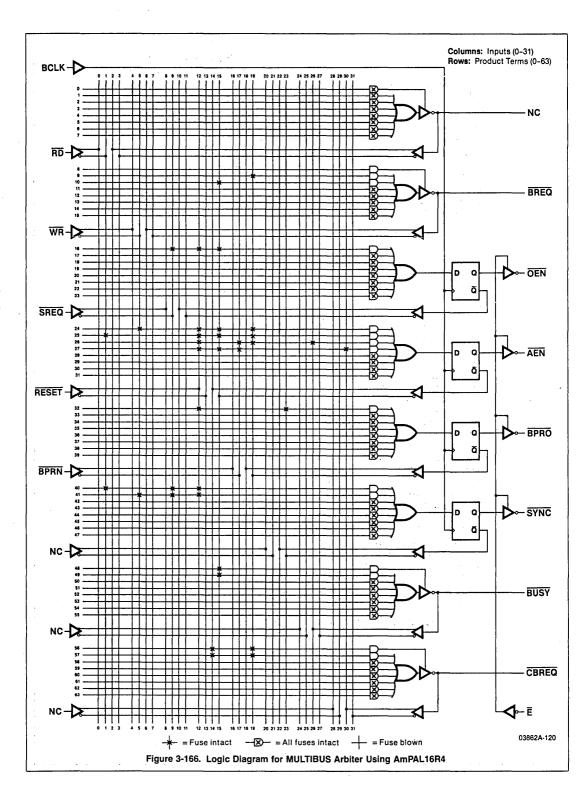

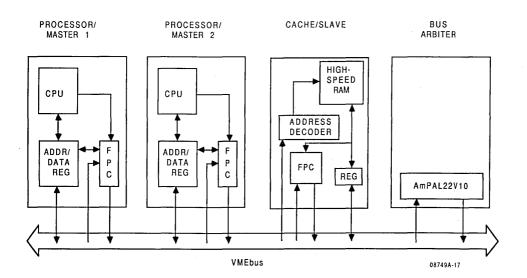

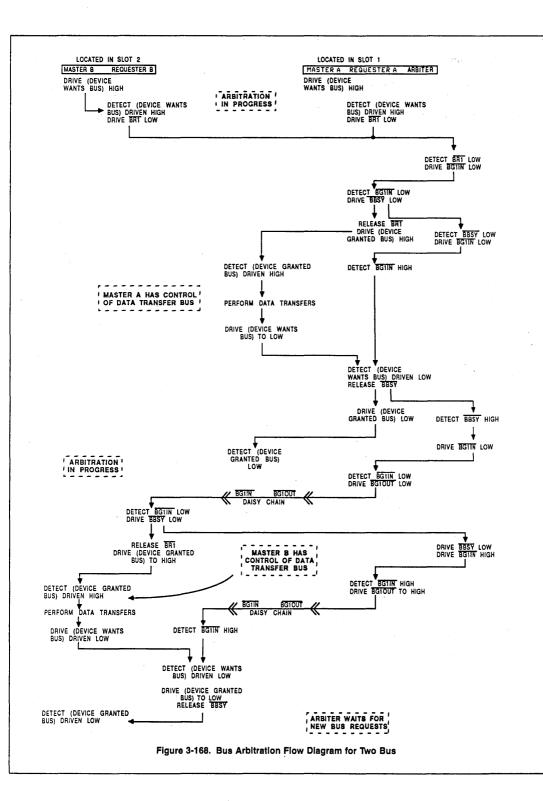

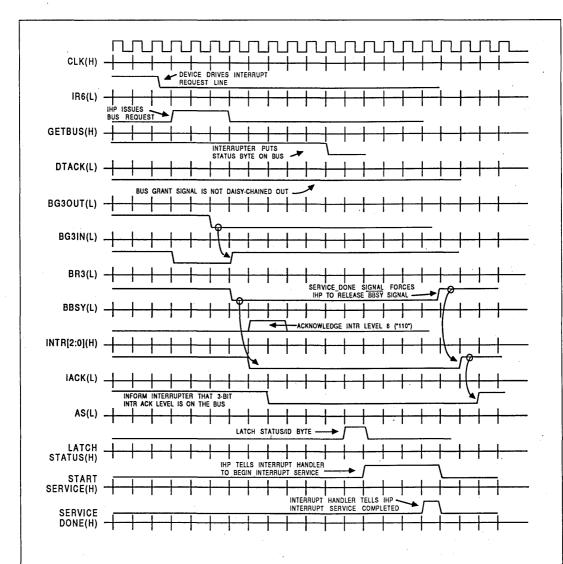

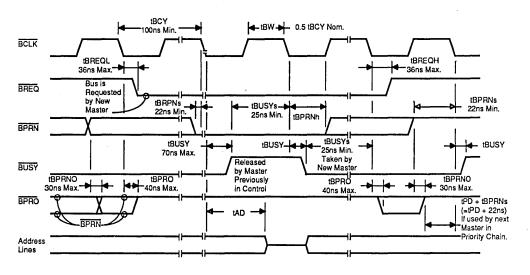

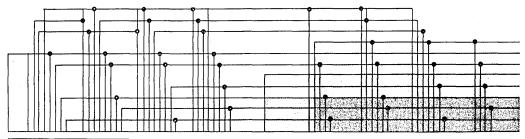

| 3.4   | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Microp<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>Bus In<br>3.5.1<br>3.5.2<br>3.5.3 | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         tital Logic       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 68080/68020       3-81         Interfacing to the 8088/80188       3-137         Interfacing to the 280/Z8000       3-111         terface Logic       3-187         MULTIBUS to Am9516 Interface       3-187         Z-Bus and 8088/8086 Interface       3-191         An AMD PAL MULTIBUS Arbiter       3-201 |

| 3.4   | 3.2.3<br>3.2.4<br>3.2.5<br>Sequer<br>3.3.1<br>3.3.2<br>Microp<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>Bus In<br>3.5.1<br>3.5.2          | Multiplexers       3-3         Demultiplexers       3-3         Encoders/Decoders       3-9         Comparators       3-22         Address Decoding and Chip Select Generation Simplified with       3-25         Combinatorial PAL Devices       3-29         Counters       3-29         Shifters       3-47         rocessor Interface Logic       3-55         The Interface Problem       3-55         Interfacing to the 8086/80186/80286       3-60         Interfacing to the 8088/80188       3-137         Interfacing to the 280/Z8000       3-81         Interfacing to the Z80/Z8000       3-171         terface Logic       3-187         MULTIBUS to Am9516 Interface       3-187         Z-Bus and 8088/8086 Interface       3-191                                                                                  |

| 3.6                                                                      | Miscella                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | aneous Logic Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

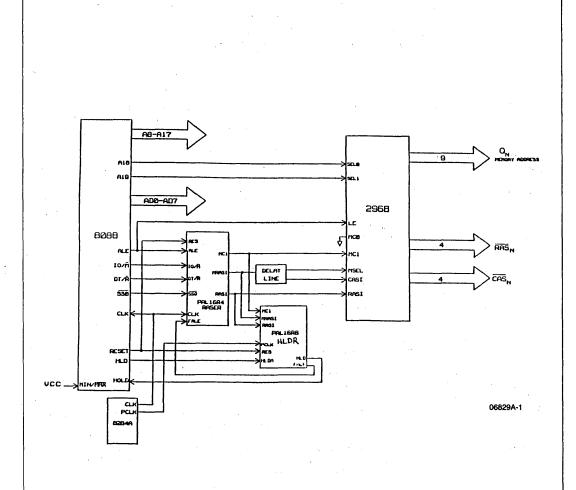

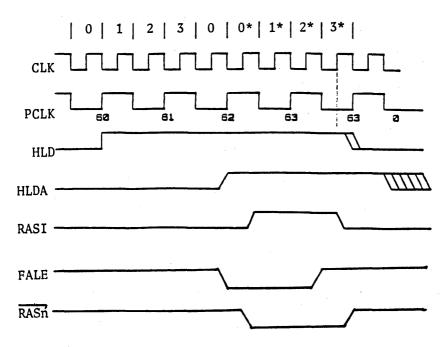

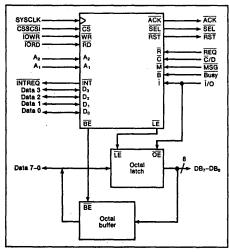

|                                                                          | 3.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8088 to Am2968 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                          | 3.6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A General-Purpose Interface for the Am2968                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          | 3.6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MC68000 to Am2968 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                          | 3.6.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | General-Purpose Dual-Port Arbiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

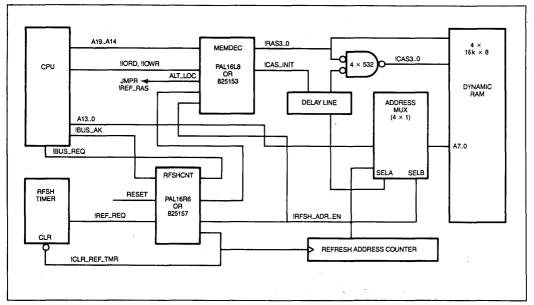

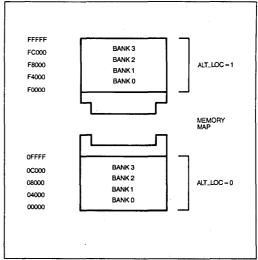

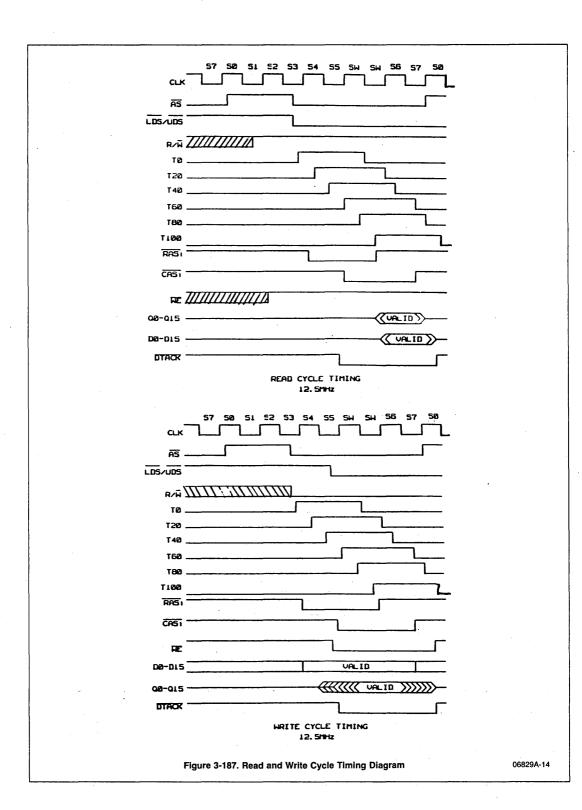

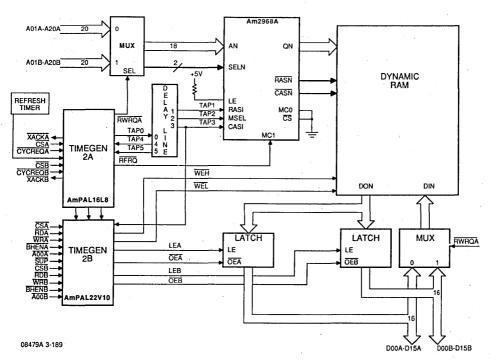

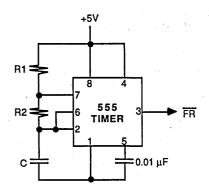

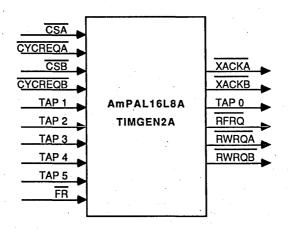

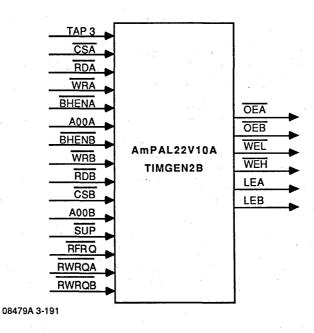

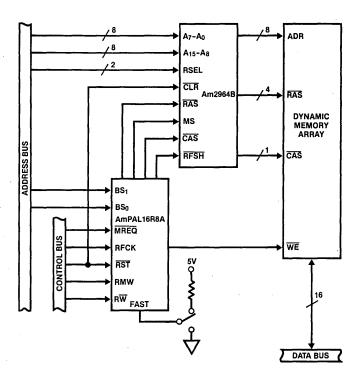

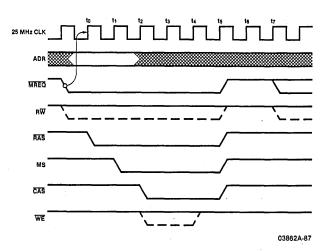

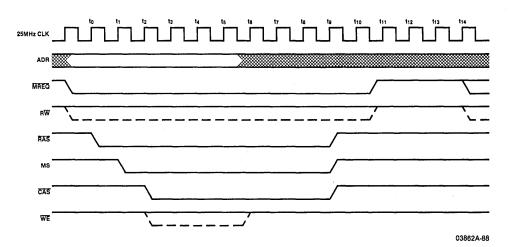

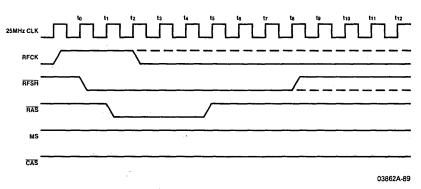

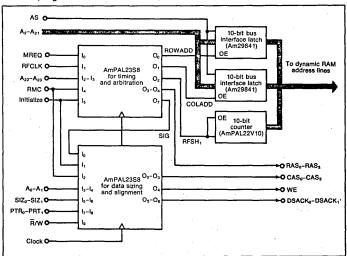

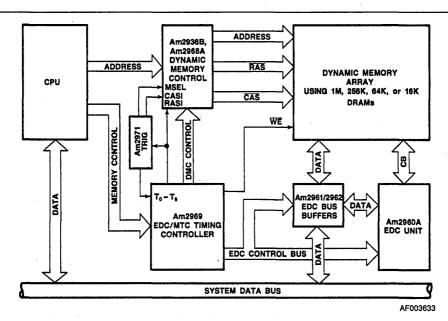

|                                                                          | 3.6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Customize a Flexible DRAM Controller Using Second-Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |