Am29332 Instruction Manual

Am29332 Instruction Manual Advanced Micro Devices

### **Advanced Micro Devices**

## Am29332 32-Bit Arithmetic Logic Unit

### Instruction Manual

### © 1987 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This manual neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

09287B

| Product Overview                                       | 1 - 1            |

|--------------------------------------------------------|------------------|

| Functional Description                                 | 1 - 2            |

| Data Types<br>Instruction Format                       | 1 - 5<br>1 - 5   |

| Instruction Classification                             | 1-5              |

| Instruction Set Summary                                | 1 - 7            |

| Data Movement Instruction                              | 1 - 8            |

| Logical Instructions                                   | 1 - 9            |

| Single - Bit Shift Instructions                        | 1 - 10           |

| Prioritize Instructions                                | 1 - 11           |

| Arithmetic Instructions                                | 1 - 11           |

| Shift/Rotate Instructions                              | 1 - 15           |

| Bit - Manipulation Instructions                        | 1 - 15           |

| Field Logical Instructions<br>Mask Instructions        | 1 - 17           |

| Glossary                                               | 1 - 18<br>1 - 18 |

| Glossary                                               | 1 - 10           |

| Detailed Instruction Description in Alphabetical Order | 2 - 1            |

| Appendix A                                             |                  |

| BCD Arithmetic                                         | A - 1            |

| Appendix B                                             |                  |

| Multiplication<br>Division                             | B - 1<br>B - 7   |

|                                                        |                  |

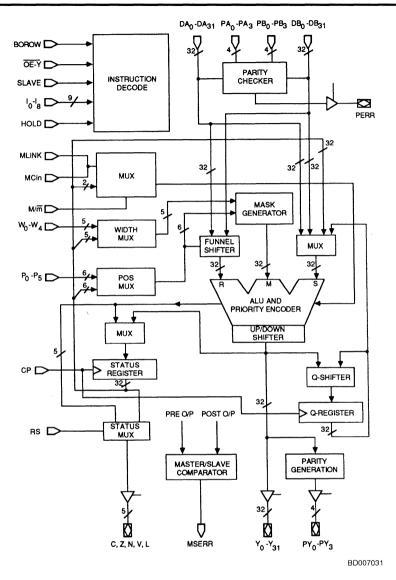

Figure 1. Detailed Block Diagram

### **CHAPTER 1**

## Am29332 32-Bit Arithmetic Logic Unit

#### **PRODUCT OVERVIEW**

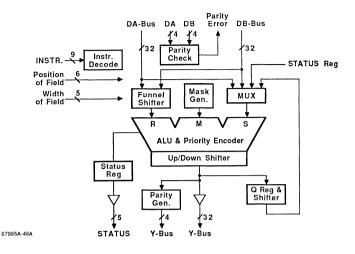

The Am29332 is a 32-bit wide, high-performance, non-expandable Arithmetic Logic Unit (ALU). It has two 32-bit wide input ports (A and B) and one 32-bit wide output port (Y). These three ports provide flexibility and accessibility for high-performance processor designs. Dedicated input and output ports provide a flow-through architecture and avoid the penalty associated with switching the bus half-way through the cycle for input and output of data. The chip is designed for use with a dual-access RAM (Am29334) as a register file. In addition, the three-bus architecture facilitates the connection of other arithmetic units in parallel with the Am29332 for high-performance systems.

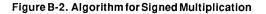

The Am29332 supports one-, two-, three-, and four-byte arithmetic operations. It also supports multiprecision arithmetic and multiple bit shifts. For logical operations, it can handle variable-length fields of up to 32 bits. The chip incorporates dedicated hardware to allow efficient implementation of a two bit-at-a-time (modified Booth) multiply algorithm, supporting signed and unsigned arithmetic data types. Similarly, hardware is provided to support a bit-at-a-time divide algorithm, also supporting signed and unsigned arithmetic data types. An internal 32-bit register (Q) is used by the multiply and divide hardware for double precision operands. For business applications, the Am29332 supports variable-length BCD arithmetic.

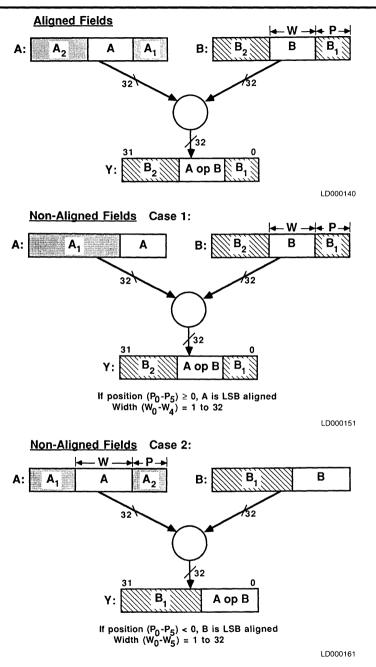

Field logical instructions operate on bit-fields taken from the A and B data inputs; they may be of variable width and starting position. A is normally the source input and B the destination input. In general, destination bits not falling within a specified field are passed by the ALU unchanged. Field width and position are specified either by direct inputs to the chip, or by entries in the status register. There are two kinds of field logical instructions – aligned and non-aligned. The first type of instruction assumes that source and destination fields are aligned and the operation is performed only for bits within the specified fields. In the second type of instruction, source and destination fields are normally non-aligned. However, it is always assumed that one field (either source or destination) is least-significant-bit (LSB) aligned.

If the destination field is LSB aligned then the source field is downshifted in order to make it LSB aligned as well. Downshifting is accomplished by making the 6-bit position input equal to the two's complement of the number of places the field is to be downshifted. If the source field is LSB aligned then it is upshifted in order to align it with the destination. Upshifting is accomplished by making the position inputs equal to the number of places the field is to be upshifted. Any other type of field operation is not allowed. Whenever the field crosses the word boundary, the portion not falling within the word boundary is ignored. This effect is useful when performing operations on fields that overlap two different words. Instructions to perform straightforward multiple-bit shifts (either up or down) are also provided. Additionally, it is possible to extract a bit-field from a word in one instruction, even if that field overlaps a word boundary.

The power and the flexibility of the processor comes partly from its ability to generate a mask to control the width of an operation for each instruction without any overhead. For all byte aligned instructions (three quarters of the instruction set), the mask is either 1, 2, 3 or 4 bytes wide and is generated from the byte width input ( $I_8 - I_7$ ). For all field instructions the mask is of variable width and is generated from the position inputs ( $P_0 - P_5$ ) and the width inputs ( $W_0 - W_4$ ). Table 1 describes the bottien displacement from the position inputs and Table 2 the bit field from the width inputs.

|    |    | Inp            | Bit Displacement |    |    |            |

|----|----|----------------|------------------|----|----|------------|

| P5 | Ρ4 | P <sub>3</sub> | P <sub>2</sub>   | P1 | Po | p          |

| 0  | 0  | 0              | 0                | 0  | 0  | 0          |

| 0  | 0  | 0              | 0                | 0  | 1  | 1          |

| 0  | 0  | 0              | 0                | 1  | 0  | 2          |

| :  | :  | :              | :                | :  | :  | :          |

| 0  | 1  | 1              | 1                | 1  | 1  | 31         |

| 1  | 0  | 0              | 0                | 0  | 0  | -32<br>-31 |

| 1  | 0  | 0              | 0                | 0  | 1  | -31        |

| :  | :  | :              | :                | :  | :  | :          |

| 1  | 1  | 1              | 1                | 1  | 1  | -1         |

#### TABLE 1. POSITION INPUTS AND BIT DISPLACEMENT

#### TABLE 2. WIDTH INPUTS AND BIT FIELD

|    |                | Inputs         | Bit Field      |                |    |

|----|----------------|----------------|----------------|----------------|----|

| W4 | W <sub>3</sub> | W <sub>2</sub> | W <sub>1</sub> | W <sub>0</sub> | w  |

| 0  | 0              | 0              | 0              | 0              | 32 |

| 0  | 0              | 0              | 0              | 1              | 1  |

| 0  | 0              | 0              | 1              | 0              | 2  |

| :  | :              | :              | :              | 1              | :  |

| 1  | 1              | 1              | 1              | 1              | 31 |

Whenever the width of the operand is less than 32-bits, all unselected bits from the inputs of the ALU are passed to the output without any modification. Depending upon the instruction type, unselected bits are taken from different sources. For example in all single operand instructions, bits from the source operand (from either A or B input) are passed in unselected bit positions. For two operand instructions, bits from the B'input are passed in unselected bit positions. There are some exceptions which are explained in the instruction set section.

The processor has a 32-bit status register to indicate the status of different operations performed. The status register is loaded at the rising edge of the clock with new status unless the HOLD signal is HIGH. The bit position for each status bit is given in the functional description. The least significant byte of the status register holds the six position bits ( $PR_0 - PR_5$ ). The two most significant bits of this byte may be read or loaded but are otherwise unused by the ALU. The second byte (bits 8 to 15) consists of the five width bits ( $WR_0 - WR_4$ ) and three read-only bits that are a combinational function of other status bits, and which indicate useful branch conditions. The third byte consists of ALU status bits plus bits for high-speed multiply and divide. The most significant byte holds intermediate nibble carries for BCD operations. An extract-status instruction is provided which allows a Boolean value to be formed from any

selected bit. This is particularly useful in machines employing a stack architecture. Instructions to save and restore the status register are provided. As the entire status of each instruction is stored in the status register, interrupts at any microinstruction boundary are feasible.

The processor has a 32-bit wide priority encoder to support floating-point and graphics operations. The priority encoder supports all byte aligned data types – the result is dependent upon the byte width specified. The result of a priority encode is also loaded into the position bits of the status register. The result of the prioritize operation can then be used in the following clock cycle, e.g., to normalize a floating-point number or to help detect the edge of a polygon in graphics applications.

To support system diagnostics, the Am29332 has a special "Master-Slave" mode. To use this mode, two chips are connected in parallel, and hence receive the same instructions and data. The master chip is used for the normal data path. However, in the slave chip, all outputs becomes inputs. The slave compares the outputs of the master with its own internally generated result. If the two do not match, the slave will activate an error signal.

As a further diagnostic aid, byte-wise parity checking is performed at both the A and B data inputs. The "parity" signal is activated if an error is detected. Parity bits (one per byte) are generated for the 32-bit output bus.

#### FUNCTIONAL DESCRIPTION

A detailed description of each functional block is given in the following paragraphs.

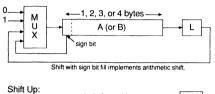

#### 64-Bit Funnel Shifter

The 64-bit funnel shifter is a combinatorial network. The 64-bit input is formed from a combination of the A and B inputs. This may be left-shifted by up to 31 bits before being used by the ALU. The output of the shifter is the most significant 32 bits of the result. The 64-bit shifter can be used on either the A or B operands to perform barrel shifts (either up or down) or rotates. The operation is controlled by positioning operands properly at the input of the 64-bit up-shifter.

The number "n" by which the operand is shifted comes from two sources: the microprogram memory via the  $P_0-P_5$  pins or the internal register (byte 0 of the status register),  $\mathsf{PR}_0-\mathsf{PR}_5,$  as selected by an instruction bit.

In general, the 6-bit position input,  $P_0 - P_5$ , takes a 6-bit two's complement number representing upshifts from 0 to 31 places (positive numbers) or downshifts from 1 to 32 places (negative numbers).

#### Mask Generator

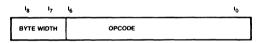

The mask generator logic provides the ability to generate the appropriate mask for an operand of given width and position. The generation of the mask depends upon two types of instructions. The first type has byte boundary aligned operands (widths of either 1, 2, 3 or 4 bytes) with the least significant bit aligned to bit 0. The width of an operand is specified by the byte width inputs ( $I_8$  and  $I_7$ ) as shown in Table 3. The second type of instruction has operands of variable width (1 to 32 bits) and position. The operand is specified by the byte width inputs ( $V_0 - V_4$ ) and the position inputs ( $P_0 - P_5$ )

indicating the least significant bit position of the operand. Thus, in this type of instruction the operand may or may not be least significant bit aligned. Depending upon the type of instruction, the mask generator first generates a fence of all zeros starting from the least significant bit with the width specified either by the byte width or the width input fields. This fence can be upshifted by up to 31 bits by the 32-bit mask shifter. Whenever the mask is moved up over the 32-bit boundary, it does not wrap around. Instead, ONE's are inserted from the least significant end. This configuration provides the ability to operate on a contiguous field located anywhere in a word, or across a word boundary.

The mask generator can be used as a pattern generator by allowing the mask to pass through ALU (by using the PASS-MASK instruction). For example, a single-bit wide mask can be generated and by shifting it up by different amounts can give walking ONE or walking ZERO patterns for memory tests.

| I <sub>8</sub> | 17 | Width in Bytes |

|----------------|----|----------------|

| 0              | 0  | 4              |

| 0              | 1  | 1              |

| 1              | 0  | 2              |

| 1              | 1  | 3              |

TABLE 3.

#### Arithmetic and Logical Unit

The ALU is a three input unit which uses the mask as a second or third operand in every instruction. The mask is used to merge two operands. For all selected bits (wherever the mask is 0), the desired operation specified by the instruction input is performed, and for all unselected bits either corresponding destination bits or zeros are passed through. The status of each operation (carry, negative, zero, overflow, link) applies to the result only over the specified width. For all byte aligned arithmetic and logical operations (first three quarters of the instruction set), the status is extracted from the appropriate byte boundary. For all field operations (last quarter of the instruction set), the operand width is assumed to be 32 bits for status generation. The ZERO flag always indicates the status of all bits selected by the mask.

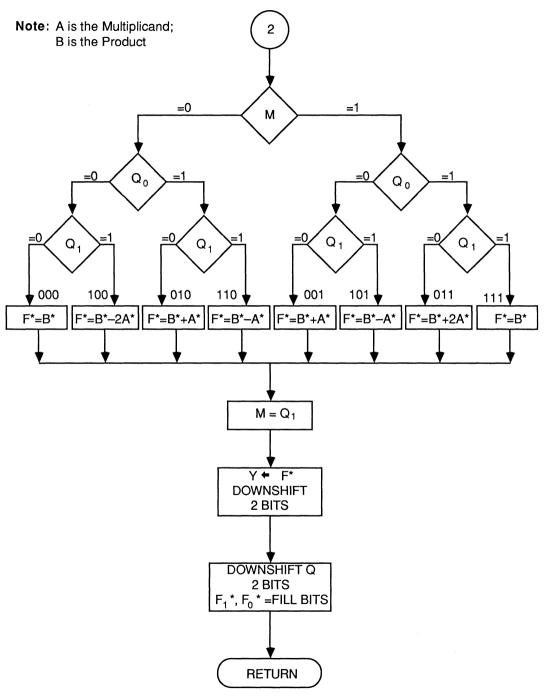

The actual width of the ALU is 34 bits. There are two extra bits used for the high speed signed and unsigned multiplication instructions. These two bits are automatically concatenated to the most-significant end of the ALU depending upon the width specified for the operation. Since the modified Booth algorithm requires a two-bit down-shift each cycle, these ALU bits generate the two most-significant bits of the partial product.

The ALU is capable of shifting data down by two bits for the multiplication algorithm, up by one bit for the divide algorithm and single-bit-up-shifts.

The processor is capable of performing BCD arithmetic on packed BCD operations. This logic generates nibble carries (BCD digit carry) from propagate and generates signals formed from the A and B operands. In order to simplify the hardware while maintaining throughput, the BCD add and subtract operations are performed in two cycles. In the first cycle, ordinary binary addition or subtraction is performed and BCD nibble carries are generated. These are blocked from affecting the result at this stage, but are saved in the status register to be used later for BCD correction (NC<sub>g</sub>-NC<sub>y</sub>). In the second cycle all BCD numbers are adjusted by

examining the previously generated nibble carries. Since all the necessary information is stored in the status register, the processor can be interrupted after the first BCD cycle.

#### **Priority Encoder**

The priority encoder is provided to support floating-point arithmetic and some graphics primitives. The priority encoder takes up to 32bits as input and generates a 5-bit wide binary code to indicate location of the most significant one in the operand. Input to the priority endcoder comes from the input multiplexer, which masks all bits that the user does not want to participate in the prioritization. The priority encoder supports 8, 16, 24, and 32-bit operations depending upon the byte width specified. For each data type the priority encoder generates the appropriate binary weighted code. For example, when a byte width of two is specified  $(I_1 - I_2 = 10)$ , the output of the encoder is zero when bit 15 is HIGH. However, if byte width of four is specified  $(I_{s} - I_{z} = 00)$ , the output of the encoder is 16 (decimal) if bit 15 is HIGH and bits 31 - 16 are LOW. Table 4 shows the output for each data type. If none of the inputs are HIGH or the most significant bit of the data type specified is HIGH, then the output is zero. The difference between these two cases is indicated by the Z-flag of the status register which is HIGH only if all inputs are zero.

#### **Q-Register**

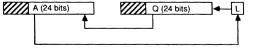

The Q-register holds dividend and quotient bits for division, and multiplier and product bits for multiplication. During division, the contents of the Q-register are shifted left, a bit at a time, with quotient bits inserted into bit 0. During multiplication, the contents of the Q-register are shifted right, two bits at a time, with product bits inserted into the most-significant two bits (according to the selected byte width). The Q-register may be loaded from the A or B inputs and read onto the Y bus.

#### Master-Slave Comparator

All ALU outputs (except MSERR) employ three-state buffers. The master-slave comparator compares the input and output of each buffer. Any difference causes the MSERR signal to be made true. In Slave mode, all output buffers are disabled. Outputs from a second ALU may then be connected to the equivalent pins of the first. The comparator in the slave will then detect any difference in the results generated by the two. When the Y bus is three-stated by making Output-Enable false, the Y bus master-slave comparators are disabled.

#### **Parity Logic**

For each byte of the DA and DB inputs there is an associated parity bit (8 in all). If a parity error is detected on any byte, the Parity-Error signal is made true. Four parity signals (one per byte) are also generated for the Y bus outputs. EVEN parity is employed for the Am29332.

#### Status Register

All necessary information about operations performed in the ALU is stored in the 32-bit wide status register after every microcycle. Since the register can be saved, an interrupt can occur after any cycle. The status register can be loaded from either the A or B input of the chip and can be read out on the Y bus for saving in an external register file. For loading, the byte width indicates how many bytes are to be updated. The status register is only updated if the HOLD input is inactive.

Each byte of the status register holds different types of information (see Figure 3). The least significant byte (bits 0 to 7) holds eight position bits ( $PR_0 - PR_7$ ) for the data shifter.

The two most significant bits are not used. The next most significant byte (bits 8 to 15) holds the 5-bit width field (WR<sub>0</sub> – WR<sub>4</sub>) for the mask generator. The three most-significant bits of that byte (bits 13 to 15) are read-only bits that represent three different conditions extracted from the other bits of the status register. They are C + Z,  $N \oplus V$ , and ( $N \oplus V$ ) + Z for bits 13, 14 and 15 respectively. These bits can be read on the  $Y_0$  pin by the extract-status instruction. The next byte contains all the necessary information generated by an ALU operation. The least-significant four bits (bits 16 to 19) hold carry, negative, overflow and zero flags. Bit 20 holds link information for single bit shifts and bits 21 and 22 are used by

| the multiply and divide instructions. The M flag holds the      |

|-----------------------------------------------------------------|

| multiplier bit for the modified Booth algorithm or it holds the |

| sign comparison result for the divide algorithm. The S flag     |

| holds the sign of the partial remainder for unsigned division.  |

| Both the flags (M and S) are provided as a part of the status   |

| register so that multiply and divide instructions can be inter- |

| rupted at microinstruction boundaries. The most significant     |

| byte of the status register holds nibble carries for BCD        |

| arithmetic. Since BCD arithmetic is performed in two cycles,    |

| the nibble carries are saved in the first cycle and used in the |

| second cycle. Since all the information is stored, BCD instruc- |

| tions are also interruptible at the microinstruction boundary.  |

| ہ<br>Status                                              | §0_7∶                                                                                                                                                                                                                                                                                                                                                                                 | Position Register |     |                 |                 | I               |                 |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----------------|-----------------|-----------------|-----------------|

| PR7                                                      | PR <sub>6</sub>                                                                                                                                                                                                                                                                                                                                                                       | PR <sub>5</sub>   | PR4 | PR <sub>3</sub> | PR <sub>2</sub> | PR <sub>1</sub> | PR <sub>0</sub> |

| 7                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                     | 5                 | 4   | 3               | 2               | 1               | 0               |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$     |                                                                                                                                                                                                                                                                                                                                                                                       |                   |     | Read            | Only            |                 |                 |

| SIGNED<br>LE                                             | SIGNED<br>LT                                                                                                                                                                                                                                                                                                                                                                          | UNSIGNED<br>LE    | WR4 | WR3             | WR <sub>2</sub> | WR <sub>1</sub> | WR0             |

| 15                                                       | 14                                                                                                                                                                                                                                                                                                                                                                                    | 13                | 12  | 11              | 10              | 9               | 8               |

| Status<br>Status<br>Status<br>Status<br>Status<br>Status | atus <sub>16</sub> :         Carry           atus <sub>17</sub> :         Negative           atus <sub>18</sub> :         Overflow           atus <sub>19</sub> :         Zero           atus <sub>20</sub> :         Link           atus <sub>21</sub> :         Multiply (and divide) Bit           atus <sub>22</sub> :         Sign Flag           atus <sub>23</sub> :         0 |                   |     |                 |                 |                 |                 |

| 0                                                        | s                                                                                                                                                                                                                                                                                                                                                                                     | м                 | L   | z               | v               | N               | с               |

| 23                                                       | 22                                                                                                                                                                                                                                                                                                                                                                                    | 21                | 20  | 19              | 18              | 17              | 16              |

| Statu                                                    | Status <sub>24-31</sub> : Nibble Carries                                                                                                                                                                                                                                                                                                                                              |                   |     |                 |                 |                 |                 |

| NC7                                                      | NC <sub>6</sub>                                                                                                                                                                                                                                                                                                                                                                       | NC5               | NC4 | NC3             | NC2             | NC1             | NC <sub>0</sub> |

| 31                                                       | 30                                                                                                                                                                                                                                                                                                                                                                                    | 29                | 28  | 27              | 26              | 25              | 24              |

| Note: C                                                  | Note: Overflow is defined as follows:                                                                                                                                                                                                                                                                                                                                                 |                   |     |                 |                 |                 |                 |

| TABLE 4.                                                                                |                            |  |  |  |

|-----------------------------------------------------------------------------------------|----------------------------|--|--|--|

| Highest Priority<br>Active Bit                                                          | Encoder<br>Output          |  |  |  |

| I <sub>7</sub> - I <sub>8</sub> = 00 (32-bit)<br>None<br>31<br>30<br>29<br>28           | 0<br>0<br>1<br>2<br>3      |  |  |  |

| 1<br>0                                                                                  |                            |  |  |  |

| I <sub>7</sub> - I <sub>8</sub> = 01 (8-bit)<br>None<br>7<br>6<br>5<br>1<br>0           | 0<br>0<br>1<br>2<br>6<br>7 |  |  |  |

| I <sub>7</sub> - I <sub>8</sub> = 10 (16-bit)<br>None<br>15<br>14<br>13<br>12<br>1<br>0 | 0<br>0<br>1<br>2<br>3      |  |  |  |

| I <sub>7</sub> - I <sub>8</sub> = 11 (24-bit)<br>None<br>23<br>22<br>21<br>20<br>1<br>0 | 0<br>0<br>1<br>2<br>3      |  |  |  |

### Am29332 INSTRUCTION SET

#### Data Types

The Am29332 supports the following data types:

- 1. Integer

- 2. Binary-coded decimal

- 3. Variable-length bit field

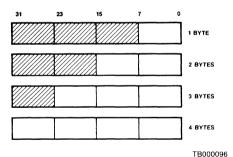

The first two data types fall into the category of byte boundary aligned operands (Figure 4). The size of the operand could be 1 byte, 2 bytes, 3 bytes or 4 bytes. All operands are least significant bit (bit 0) aligned. The byte width is determined by bits  $|_{a}$  and  $|_{7}$  of the instruction as shown in Table 5.

| ſ | Ά | В | L | Ε | 5. |

|---|---|---|---|---|----|

|---|---|---|---|---|----|

| 18 | 17 | Width in<br>Bytes |

|----|----|-------------------|

| 0  | 0  | 4                 |

| 0  | 1  | 1                 |

| 1  | 0  | 2                 |

| 1  | 1  | 3                 |

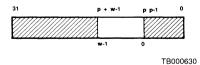

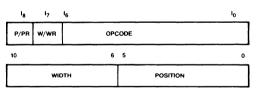

The third data type has operands of variable width (1 to 32 bits) as shown in Figure 4. The operand is specified by width inputs ( $W_0 - W_4$ ) and position inputs ( $P_0 - P_5$ ). The position inputs indicate the least significant bit position of the operand. Depending on bits  $I_8$  and  $I_7$  of the instruction, the width and position inputs can be selected from either the Status Register or the Width and Position Pins as shown in Table 6.

Byte Boundary Aligned Operands

Variable-Length Bit Field

p = Bit displacement of the least significant field with respect to bit 0.

w = Width of bit field.

| TABLE | 6. |

|-------|----|

|-------|----|

|    |    | Position |     | Wi   | dth |

|----|----|----------|-----|------|-----|

| I8 | 17 | Pins     | Reg | Pins | Reg |

| 0  | 0  | х        |     | x    |     |

| 0  | 1  | х        |     |      | х   |

| 1  | 0  |          | х   | Х    |     |

| 1  | 1  |          | X   |      | х   |

| Data Type | Size         | Range                   |                     |  |

|-----------|--------------|-------------------------|---------------------|--|

| Integer   |              | Signed                  | Unsigned            |  |

| 1 byte    | 8 bits       | -128 to +127            | 0 to 255            |  |

| 2 bytes   | 16 bits      |                         | 0 to                |  |

|           |              | $+2^{15}-1$             |                     |  |

| 3 bytes   | 24 bits      | $-2^{23}$ to $2^{23}-1$ |                     |  |

| 1         |              |                         | 2 <sup>24</sup> – 1 |  |

| 4 bytes   | 32 bits      | $-2^{31}$ to $2^{31}-1$ |                     |  |

|           |              |                         | 2 <sup>32</sup> – 1 |  |

| BCD       | 1 to 4 bytes | Numeric, 2 digits       | s per byte.         |  |

|           | (8 digits)   | Most-significant        | digit may be        |  |

|           |              | used for sign.          |                     |  |

| Variable  | 1 to 32 bits | Dependent on p          | osition and         |  |

|           |              | width inputs.           |                     |  |

#### Instruction Format

The Am29332 has two types of Instruction Formats:

1. Byte Boundary Aligned Instructions (FORMAT 1):

TB000098

#### 2. Variable-Length Field Bit Instructions (FORMAT 2):

TB000099

For instructions that allow a field to be shifted up or down,  $P_0 - P_5$  is a two's-complement number in the range -32 to +31 representing the direction and magnitude of the shift. For instructions that assume a fixed field position,  $P_0 - P_4$  represent the position of the least-significant bit of the field and  $P_5$ is ignored.

#### Instruction Classification

ALU instructions can be classified as follows:

- A. Byte Boundary Aligned Operand Instructions:

- 1. Arithmetic

- Binary, BCD

- Multiply steps

- Division steps (single and multiple precision)

- 2. Prioritize

- 3. Logical

- 4. Single-bit shifts

- 5. Data movement

B. Variable-Length Bit Field Operand Instructions:

- 1. N-bit shifts and rotates

- 2. Bit manipulations

- 3. Field logical operations (aligned, non-aligned, extract)

- 4. Mask generation

Three-fourths of the ALU instructions apply to operands that are byte boundary aligned. For these instructions, two orthogonal issues are the width of the operand (in bytes) and the contents of the high order unselected bytes on the Y bus. As mentioned earlier, the width of the operand is specified by Ig and I<sub>7</sub>. With the exception of a few instructions, the unselected bytes are assigned values as follows: for single operand instructions, unselected bytes are passed unchanged from the source (A or B). For two operand instructions, unselected bytes are passed unchanged from the destination (B input).

In the last quarter of the instruction set, the width of the operand is from 1 to 32 bits (based on the width input) for field operations, 32 bits for N-bit shift operations and 1-bit for bit-oriented operations. In the case of field-aligned and single-bit operands, the position bits ( $P_0 - P_4$ ) determine the least significant bit of the operand. In the case of N-bit shifts and field non-aligned operands, the position bits  $P_0 - P_5$  is a 6-bit signed integer determining the magnitude and direction of the shift.

#### Flags

#### **Byte-Aligned Instructions**

The zero flag always looks only at the selected bytes:

$Z \leftarrow$  (Y and bytemask (byte width) = 0)

Similarly, N  $\leftarrow$  sign bit (Y, byte width), where the function ''sign-bit'' returns bit 7, 15, 23, or 31 of the first argument for byte widths 01, 10, 11, or 00 respectively.

Also,  $C \leftarrow$  carry (byte width) returns the carry from the appropriate byte boundary, and:

$V \leftarrow$  overflow (byte width) = (carry into MSB)  $\oplus$  (carry out of MSB)

returns the overflow from the appropriate byte boundary.

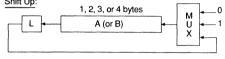

The link (L) flag is generally loaded with the bit moved out of the highest selected byte in the case of upshifts, or the bit moved out of the least significant byte for downshifts. Figure 5 shows the shift operation using link bit. Other status flags have specialized uses, explained in the following sections.

DF006190

#### Figure 5. Upshift/Downshift Using Link Bit

#### Variable-Length Field Instruction:

Generally, only N and Z are affected. N takes the mostsignificant bit of the 32-bit result (i.e.,  $N \leftarrow Y_{31}$ ). Z detects zeros in the selected field of the result (i.e.,  $Z \leftarrow (Y \text{ and} bitmask (position, width) = 0)).$

#### **Output Select**

The Register Status pin, RS, may be used to switch the C, Z, N, V, and L output pins between the direct output of the ALU and the outputs of the corresponding bits in the status register. If the direct status output is selected, then for instructions that do not affect a particular flag (e.g., carry for logical arithmetic) that output will reflect the state of its corresponding bit in the status register. Similarly, when the HOLD signal is made HIGH, the C, Z, N, V and L pins will be made equal to the Sinput.

| Туре                 | Operation                                                                                                                                                                                                                          | Data Type                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Arithmetic           | <ul> <li>Increment by one, two, four</li> <li>Decrement by one, two, four</li> <li>Add, addc (carry = macro/micro)</li> <li>Sub, subr</li> <li>Subc, subrc (carry/borrow)</li> <li>BCD sum and difference correct steps</li> </ul> | Binary Intege<br>and BCD |

|                      | Negate (two's complement)     Multiply steps (modified Booth)     Divide steps (non-restoring)     (Signed and unsigned)                                                                                                           | Binary Intege            |

| Prioritize           | Prioritize                                                                                                                                                                                                                         | Binary                   |

| Logical              | Not, OR, AND, XOR, XNOR, zero, sign                                                                                                                                                                                                | Binary                   |

| Single-Bit<br>Shifts | Upshift with 0, 1, link fill     Downshift with 0, 1, link, sign fill     (Single and double precision)                                                                                                                            | Binary                   |

| Data<br>Movement     | <ul> <li>Zero extend</li> <li>Sign extend</li> <li>Pass-status, Q-Reg</li> <li>Load-status, Q-Reg</li> <li>Merge</li> </ul>                                                                                                        | Binary                   |

### INSTRUCTION SET SUMMARY

| Operand Size: 32              | Bits                                                                                                                                         |           |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Туре                          | Operation                                                                                                                                    | Data Type |

| N-Bit Shifts<br>N-Bit Rotates | <ul> <li>Upshift by 0 to 31 bits with 0 fill</li> <li>Downshift by 1 to 32 bits with 0, sign fill</li> <li>Rotate by 0 to 31 bits</li> </ul> | Binary    |

| Operand Size: Sin   | Operand Size: Single Bit                                |           |  |  |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------|-----------|--|--|--|--|--|--|--|--|

| Туре                | Operation                                               | Data Type |  |  |  |  |  |  |  |  |

| Bit<br>Manipulation | <ul> <li>Extract</li> <li>Set</li> <li>Reset</li> </ul> | Binary    |  |  |  |  |  |  |  |  |

| Operand Size: Variable Length Bitfield: 1 to 32 Bits |                                      |           |  |  |  |  |  |  |  |

|------------------------------------------------------|--------------------------------------|-----------|--|--|--|--|--|--|--|

| Туре                                                 | Operation                            | Data Type |  |  |  |  |  |  |  |

| Field Logical<br>(aligned and<br>non-aligned)        | • Not, OR, XOR, AND, extract, insert | Binary    |  |  |  |  |  |  |  |

| Mask                                                 | Pass-mask                            | Binary    |  |  |  |  |  |  |  |

#### TABLE 6-1. DATA MOVEMENT INSTRUCTIONS

|           |      |                | Y     | Status    |   |   |   |   |   |   |   |  |  |

|-----------|------|----------------|-------|-----------|---|---|---|---|---|---|---|--|--|

| Mnemonics | Code | Description    | Unsel | Sel       | S | м | L | z | v | N | с |  |  |

| ZERO-EXTA | 00   | Zero Extend    | 0     | A         |   |   |   | * |   | * |   |  |  |

| ZERO-EXTB | 01   |                | 0     | В         |   |   |   | * |   | * |   |  |  |

| SIGN-EXTA | 02   | Sign Extend    | Sign  | А         |   |   |   | * |   | * |   |  |  |

| SIGN-EXTB | 03   |                | Sign  | В         |   |   |   | * |   | * |   |  |  |

| MERGEA-B  | 0E   | Merge A with B | В     | A Merge B |   |   |   | * |   | * |   |  |  |

| MERGEB-A  | 0F   | Merge B with A | A     | B Merge A |   |   |   | * |   | * |   |  |  |

#### **TABLE 6-2. DATA MOVEMENT INSTRUCTIONS**

|           |      |                      | Y Output |     |                 | Status |   |   | s |   |   |   |

|-----------|------|----------------------|----------|-----|-----------------|--------|---|---|---|---|---|---|

| Mnemonics | Code | Description          | Unsel    | Sel | Status Register | s      | м | L | z | v | N | С |

| PASS-STAT | 04   | Pass Status Register | В        | S   |                 |        |   |   |   |   |   |   |

| LDSTAT-A  | 1C   | Load Status Register | S        | A   | A               | +      | + | + | + | + | + | + |

| LDSTAT-B  | 1D   |                      | S        | В   | В               | +      | + | + | + | + | + | + |

#### TABLE 6-3. DATA MOVEMENT INSTRUCTIONS

|           |      |                 | Y Output |     |            | Status |   |   |   |   |   |   |

|-----------|------|-----------------|----------|-----|------------|--------|---|---|---|---|---|---|

| Mnemonics | Code | Description     | Unsel    | Sel | Q Register | s      | м | L | z | v | Ν | с |

| PASS-Q    | 05   | Pass Q Register | В        | Q   |            |        |   |   |   |   |   |   |

| LOADQ-A   | 06   | Load Q          | Q        | Α   | A          |        |   |   | * |   | * |   |

| LOADQ-B   | 07   |                 | Q        | В   | В          |        |   |   | * |   | * |   |

Note: 1. These instructions use the byte aligned instruction format (FORMAT 1).

Legend: Unsel = Unselected Byte(s)

Sel = Selected Byte(s)

A = A Input

B = B Input Q = Q Register

+ = Updated only if byte width is 3 or 4 \* = Updated

Examples:

2, ZERO EXTB

Pass lower two bytes of B to Y with zero fill on upper two bytes

0, LOADQ-A Load all four bytes of A into Q Register pass updated Q Resistor to Y

|           |      |                  | Y Output |                     |   | Status |   |   |   |   |   |  |  |

|-----------|------|------------------|----------|---------------------|---|--------|---|---|---|---|---|--|--|

| Mnemonics | Code | Description      | Unsel    | Sel                 | s | м      | L | z | v | N | с |  |  |

| NOT-A     | 08   | One's Complement | A        | Ā                   |   |        |   | * |   | • |   |  |  |

| NOT-B     | 09   |                  | В        | B                   |   |        |   | * |   | • |   |  |  |

| ZERO      | ЗC   | Pass Zero        | В        | 0                   |   |        |   | 1 |   | 0 |   |  |  |

| SIGN      | ЗD   | Pass Sign        | В        | O(N = 0); -1(N = 1) |   |        |   | N |   |   |   |  |  |

| OR        | ЗE   | OR               | В        | A OR B              |   |        |   | * |   | • |   |  |  |

| XOR       | 3F   | EXOR             | В        | A XOR B             |   |        |   | * |   |   |   |  |  |

| AND       | 40   | AND              | В        | A AND B             |   |        |   | • |   | • |   |  |  |

| XNOR      | 41   | XNOR             | В        | A XNOR B            |   |        |   | * |   | * |   |  |  |

#### **TABLE 7. LOGICAL INSTRUCTIONS**

Note: 1. These instructions use the byte aligned instruction format (FORMAT 1).

Legend: Unsel = Unselected Byte(s)

Sel = Selected Byte(s)

A = A Input B = B Input

Q = Q Register \* = Updated

2, UP1-1F-A

Examples:

- 2, NOT-A Complement low order two bytes of A and output to Y with high order two bytes of A uncomplemented.

- 1, AND

AND first byte of A and B. Output to Y with high three bytes of B.

#### TABLE 8-1. SINGLE-BIT SHIFT INSTRUCTIONS (SINGLE PRECISION)

|           |      |                      |       | Y Output                       |   |   | s | Statu | s |   |   |

|-----------|------|----------------------|-------|--------------------------------|---|---|---|-------|---|---|---|

| Mnemonics | Code | Description          | Unsel | Sel                            | s | м | L | z     | v | N | С |

| DN1-0F-A  | 20   | Downshift, Zero Fill | A     | $Y_i = A_{i+1}, Y_{msb} = 0$   |   |   | * | *     |   | * |   |

| DN1-0F-B  | 21   |                      | В     | $Y_i = B_{i+1}, Y_{msb} = 0$   |   |   | * | *     |   | * |   |

| DN1-1F-A  | 24   | Downshift, One Fill  | A     | $Y_i = A_{i + 1}, Y_{msb} = 1$ |   |   | * | *     |   | • |   |

| DN1-1F-B  | 25   |                      | В     | $Y_i = B_{i+1}, Y_{msb} = 1$   |   |   | * | •     |   | * |   |

| DN1-LF-A  | 28   | Downshift, Link Fill | A     | $Y_i = A_{i+1}, Y_{msb} = L$   |   |   | * | *     |   | * |   |

| DN1-LF-B  | 29   |                      | В     | $Y_i = B_{i+1}, Y_{msb} = L$   |   |   | * | *     |   | * |   |

| DN1-AR-A  | 2C   | Downshift, Sign Fill | A     | $Y_i = A_{i+1}, Y_{msb} = N$   |   |   | * | *     |   | * |   |

| DN1-AR-B  | 2D   |                      | В     | $Y_i = B_{i+1}, Y_{msb} = N$   |   |   | * | *     |   | * |   |

| UP1-0F-A  | 30   | Upshift, Zero Fill   | A     | $Y_i = A_{i-1}, Y_0 = 0$       |   |   | * | *     | * | * |   |

| UP1-0F-B  | 31   |                      | В     | $Y_i = B_{i-1}, Y_0 = 0$       |   |   | * | *     | * | * |   |

| UP1-1F-A  | 34   | Upshift, One Fill    | A     | $Y_i = A_{i-1}, Y_0 = 1$       |   |   | * | *     | * | * |   |

| UP1-1F-B  | 35   |                      | В     | $Y_i = B_{i-1}, Y_0 = 1$       |   |   | * | *     | * | * |   |

| UP1-LF-A  | 38   | Upshift, Link Fill   | Α     | $Y_i = A_{i-1}, Y_0 = L$       |   |   | * | *     | * | * |   |

| UP1-LF-B  | 39   |                      | В     | $Y_i = B_{i-1}, Y_0 = L$       |   |   | * | *     | * | * |   |

Note: 1. These instructions use the byte aligned instruction format (FORMAT 1).

Example:

Shift lower two bytes of A up one bit. Set LSB to 1. Fill unselected bytes to upper two bytes of A.

|           |      |                      |                                       |   |        |   | , |   |   |   |  |  |  |

|-----------|------|----------------------|---------------------------------------|---|--------|---|---|---|---|---|--|--|--|

|           |      |                      | Y Output & Q Register                 |   | Status |   |   |   |   |   |  |  |  |

| Mnemonics | Code | Description          | Selected Bytes                        | s | м      | L | z | v | N | С |  |  |  |

| DN1-0F-AQ | 22   | Downshift, Zero Fill | $0 \rightarrow A \rightarrow Q = 2$   |   |        | * | * |   | * |   |  |  |  |

| DN1-0F-BQ | 23   |                      | $0 \rightarrow B \rightarrow Q  3)$   |   |        | * | * |   | * |   |  |  |  |

| DN1-1F-AQ | 26   | Downshift, One Fill  | $1 \rightarrow A \rightarrow Q = 2$   |   |        | * | * |   | * |   |  |  |  |

| DN1-1F-BQ | 27   |                      | $1 \rightarrow B \rightarrow Q = 3$ ) |   |        | * | * |   | * |   |  |  |  |

| DN1-LF-AQ | 2A   | Downshift, Link Fill | $L \rightarrow A \rightarrow Q = 2$ ) |   |        | * | * |   | * |   |  |  |  |

| DN1-LF-BQ | 2B   |                      | $L \rightarrow B \rightarrow Q = 3$ ) |   |        | * | * |   | * |   |  |  |  |

| DN1-AR-AQ | 2E   | Downshift, Sign Fill | $N \rightarrow A \rightarrow Q = 2$   |   |        | * | * |   | * |   |  |  |  |

| DN1-AR-BQ | 2F   |                      | $N \rightarrow B \rightarrow Q = 3$ ) |   |        | * | * |   | * |   |  |  |  |

| UP1-0F-AQ | 32   | Upshift, Zero Fill   | $A \leftarrow Q \leftarrow 0 = 2$     |   |        | * | * | * | * |   |  |  |  |

| UP1-0F-BQ | 33   |                      | $B \leftarrow Q \leftarrow O  3)$     |   |        | * | * | * | * |   |  |  |  |

| UP1-1F-AQ | 36   | Upshift, One Fill    | $A \leftarrow Q \leftarrow 1 2$       |   |        | * | * | * | * |   |  |  |  |

| UP1-1F-BQ | 37   |                      | $B \leftarrow Q \leftarrow 1  3)$     |   |        | * | * | * | * |   |  |  |  |

| UP1-LF-AQ | ЗA   | Upshift, Link Fill   | $A \leftarrow Q \leftarrow L  2)$     |   |        | * | * | * | * |   |  |  |  |

| UP1-LF-BQ | 3B   |                      | $B \leftarrow Q \leftarrow L = 3$ )   |   |        | * | * | * | * |   |  |  |  |

#### TABLE 8-2. SINGLE-BIT SHIFT INSTRUCTIONS (DOUBLE PRECISION)

Notes: 1. These instructions use the byte aligned instruction format (FORMAT 1). 2. Y Unselected byte from A, Q Unselected byte unchanged. 3. Y Unselected byte from B, Q Unselected byte unchanged.

Legend: Unsel = Unselected Byte(s)

Sel = Selected Byte(s)

- A = A Input

- B = B Input

- Q = Q Register \* = Updated

- - Example:

0, DN1-AR-BQ

Shift 64 bits (all 32 bits of both B and Q) down by one bit. LSB of B fills MSB of Q. MSB of B set to sign bit (bit N of status register).

3, UP1-LF-AQ

Shift 48 bits (24-bits of A and 24-bits of Q) up by one bit. MSB of 24-bit Q fills LSB of A. MSB of 24-bit A sets link status bit. LSB of Q is filled with original link value.

DF006200

|                                                                 |                  |                     |                           |   | Status      |   |   |   |  |  |

|-----------------------------------------------------------------|------------------|---------------------|---------------------------|---|-------------|---|---|---|--|--|

| Mnemonics                                                       | Code             | Description         | Y Output                  | S | S M L Z V N |   | N | с |  |  |

| PRIOR-A                                                         | 0C               | Prioritization      | Location of Highest 1 Bit |   |             | 1 | * |   |  |  |

| PRIOR-B                                                         | 0D               |                     |                           |   |             |   | * |   |  |  |

| Legend: $A = A$ is<br>B = B is<br>Q = Q is<br>* = Upc<br>ample: | nput<br>Register |                     |                           |   |             |   |   |   |  |  |

|                                                                 | 3, PRIO          | R-A Value placed on | Y is 2                    |   |             |   |   |   |  |  |

|                                                                 |                  |                     |                           |   |             |   |   |   |  |  |

|                                                                 |                  | ↓                   |                           |   |             |   |   |   |  |  |

#### TABLE 9. PRIORITIZE INSTRUCTIONS

TABLE 10-1. ARITHMETIC INSTRUCTIONS

|           |      |                   | Y     | Output       |   |   | S | tatu | IS |   |   |

|-----------|------|-------------------|-------|--------------|---|---|---|------|----|---|---|

| Mnemonics | Code | Description       | Unsel | Sel          | s | м | L | z    | v  | N | С |

| NEG-A     | 0A   | Two's Complement  | A     | Ā + 1        |   |   |   | *    | *  | * | * |

| NEG-B     | 0B   |                   | В     | <b>B</b> + 1 |   |   |   | *    | *  | * | * |

| INCR-A    | 12   | Increment by One  | A     | A + 1        |   |   |   | *    | *  | * | * |

| INCR-B    | 13   |                   | В     | B + 1        |   |   |   | *    | *  | * | * |

| INCR2-A   | 16   | Increment by Two  | A     | A + 2        |   |   |   | *    | *  | * | * |

| INCR2-B   | 17   |                   | В     | B + 2        |   |   |   | *    | *  | * | * |

| INCR4-A   | 1A   | Increment by Four | A     | A + 4        |   |   |   | *    | *  | * | * |

| INCR4-B   | 1B   |                   | В     | B + 4        |   |   |   | *    | *  | * | * |

| DECR-A    | 10   | Decrement by One  | A     | A – 1        |   |   |   | *    | *  | * | * |

| DECR-B    | 11   |                   | В     | B – 1        |   |   |   | *    | *  | * | * |

| DECR2-A   | 14   | Decrement by Two  | A     | A – 2        |   |   |   | *    | *  | * | * |

| DECR2-B   | 15   |                   | В     | B – 2        |   |   |   | *    | *  | * | * |

| DECR4-A   | 18   | Decrement by Four | Α     | A – 4        |   |   |   | *    | *  | * | * |

| DECR4-B   | 19   |                   | В     | B – 4        |   |   |   | *    | *  | * | * |

Notes: 1. These instructions use the byte aligned instruction format (FORMAT 1).

Borrow, rather than carry, is generated if BOROW is HIGH (borrow = carry).

Nibble bits are set by these instructions. NEG-A (or NEG-B) and DIFF-CORR may be used to form 10's complement of a BCD number. Use SUM-CORR (for increment) or DIFF-CORR (for

decrement) to increment or decrement a BCD number.

Legend: Unsel = Unselected Byte(s)

2,

Sel = Selected Byte(s)

A = A Input

- B = B Input Q = Q Register \* = Updated

Example:

DECR4-A Decrement lower two bytes of A by 4

|             |      |                     | Y Output |                                      |   |   | S | tatu | JS |   |   |

|-------------|------|---------------------|----------|--------------------------------------|---|---|---|------|----|---|---|

| Mnemonics   | Code | Description         | Unsel    | Sel                                  | s | м | L | z    | ۷  | N | с |

| ADD         | 42   | Add                 | В        | A + B                                |   |   |   | *    | *  | * | * |

| ADDC        | 43   | Add with Carry      | В        | A + B + C 6)                         |   |   |   | *    | *  | * | * |

| SUB         | 44   | Subtract            | В        | A + B + 1                            |   |   |   | *    | *  | * | * |

| SUBR        | 46   |                     | В        | B + Ā + 1                            |   |   |   | *    | *  | * | * |

| SUBC        | 45   | Subtract with Carry | В        | $A + \overline{B} + 1 + C + 2) = 6)$ |   |   |   | *    | *  | * | * |

| SUBRC       | 47   |                     | В        | B + Ā + 1 + C 2) 6)                  |   |   |   | *    | *  | * | * |

| SUM-CORR-A  | 48   | Correct BCD Nibbles | А        | Corrected A 3)                       |   |   |   | *    | *  | * | * |

| SUM-CORR-B  | 49   | for Addition        | В        | Corrected B 3)                       |   |   |   | *    | *  | * | * |

| DIFF-CORR-A | 4A   | Correct BCD Nibbles | A        | Corrected A 3)                       |   |   |   | *    | *  | * | * |

| DIFF-CORR-B | 4B   | for Subtraction     | В        | Corrected B 3)                       |   |   |   | *    | *  | * | * |

#### TABLE 10-2. ARITHMETIC INSTRUCTIONS

Notes: 1. These instructions use the byte aligned instruction format (FORMAT 1).

2. BOROW is LOW. For subtract operations, a borrow rather than a carry is stored in STATUS if BOROW is HIGH. Carry is always generated for ADD regardless of BOROW.

S First, the nibble carries NC<sub>0</sub>-NC<sub>7</sub> are tested. Any nibble carry/borrow that is set to 1 generates "6" internally as a correction word and then the correction word is added (SUM-CORR-) or subtracted (DIFF-CORR-) from the a correction word and then the correction word is added (SUM-COr operand, NC<sub>0</sub> – NC<sub>7</sub> are not affected by this operation. 4. Use SUM-CORR or DIFF-CORR to add or subtract a BCD number.

5. Use ADDC, SUBC, or SUBRC to perform operations on integers longer than 32 bits.

6. Carry bit is obtained from MCin if M/m is HIGH. Otherwise, carry is obtained from the C status bit.

Legend: Unsel = Unselected Byte(s) Sel = Selected Byte(s)

A = A Input

B = B Input

Q = Q Register

\* = Updated only if byte width is 3 or 4

Example:

0, ADD Add two 32-bit two's-complement integers

|               | 16-10         |                                       | Source for<br>Unselected |                                         |   |   | s | tatu | s |   |   |

|---------------|---------------|---------------------------------------|--------------------------|-----------------------------------------|---|---|---|------|---|---|---|

| Name          | Code          | Description                           | Bytes                    | Output                                  | s | м | L | z    | ۷ | N | с |

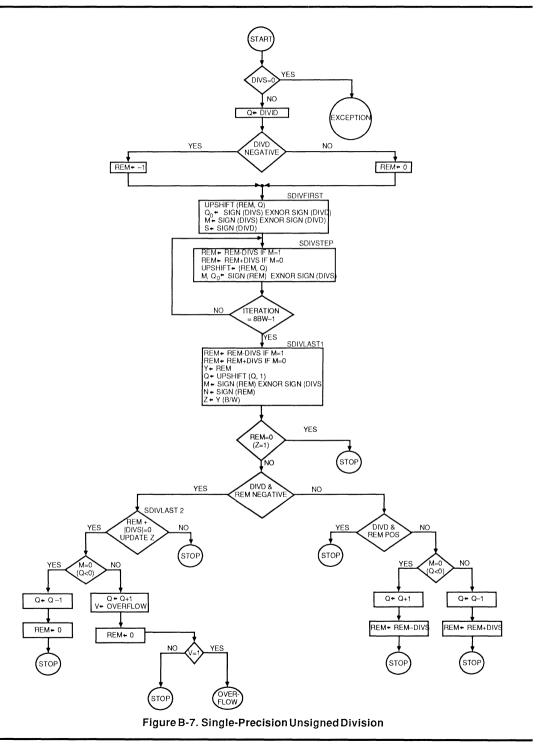

| Signed Divid  | e Steps       |                                       |                          |                                         |   |   |   |      |   |   |   |

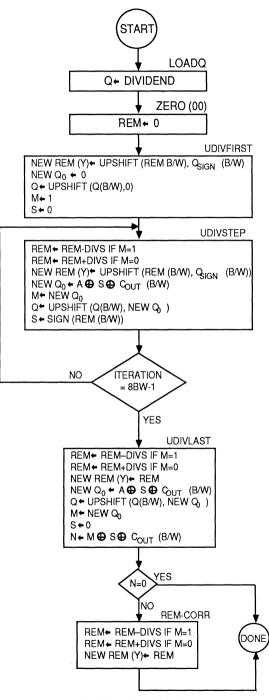

| SDIVFIRST     | 4 E           | First Instruction for Signed Divide   | В                        | Y, Q                                    | * | * | * | *    |   | * |   |

| SDIVSTEP      | 50            | Iterate Step (#bits - 1 times)        | В                        | Y, Q                                    |   | * | * | *    |   | * | * |

| SDIVLAST1     | 5 1           | Last Divide Instruction Unless        | В                        | Y, Q                                    |   | * |   | *    |   | * | * |

| SDIVLAST2     | 5 A           | Dividend & Remainder Negative         | В                        | Y                                       |   |   |   | *    |   |   |   |

| Unsigned Div  | vide Steps    | · · · · · · · · · · · · · · · · · · · |                          | • • • • • • • • • • • • • • • • • • • • | • |   |   |      |   |   | _ |

| UDIVFIRST     | 4 F           | First Instruction for Unsigned Divide | В                        | Y, Q                                    |   |   | * | *    |   | * | _ |

| UDIVSTEP      | 54            | Iterate Step (#bits - 1 times)        | В                        | Y, Q                                    | * | * | * | *    |   |   | * |

| UDIVLAST      | 55            | Last Instruction                      | В                        | Y, Q                                    | 0 | ٠ |   | *    |   | * | * |

| Multiprecisio | n Divide Step | 05                                    |                          |                                         |   |   |   |      |   |   | _ |

| MPDIVSTEP1    | 52            | First Instruction                     | В                        | Y, Q                                    |   |   |   |      |   |   |   |

| MPDIVSTEP2    | 56            | Executed 0 Times for Double           | В                        | Y, Q                                    |   |   |   |      |   |   |   |

| MPSDIVSTEP3   | 53            | Last Instruction of Inner Loop        | В                        | Y, Q                                    |   |   |   |      |   |   |   |

| MPUDIVŞTP3    | 57            | Used for Unsigned Divide              | В                        | Y, Q                                    |   |   |   |      |   |   | _ |

| Correction S  | teps          |                                       |                          |                                         |   |   |   |      |   | · |   |

| REMCORR       | 58            | Correct Remainder After Divide        | В                        | Y                                       |   |   |   |      |   |   | * |

| QUOCORR       | 59            | Correct Quotient After Divide         | В                        | Y                                       |   |   |   |      | * |   | * |

#### TABLE 11-1. DIVIDE INSTRUCTIONS (Aligned Format)

#### TABLE 11-2. EXAMPLE CODING FORM (Signed Division)

|        | Am2933 | 31             |              |     | Am293      | 32    |          |      | Am29334 | L     | Am29332 Y-Out |

|--------|--------|----------------|--------------|-----|------------|-------|----------|------|---------|-------|---------------|

| ОР     | Branch | Cond<br>Select | Multi<br>Sel | B/W | ОР         | Width | Position | A-IN | B-IN    | Y-OUT | ŌE            |

| CONT   |        |                |              | 2   | LOADQ-A    |       |          | R2   |         |       | 1             |

| CONT   |        |                |              | 0   | SIGN       |       |          |      |         | R3    | 0             |

| FOR_D  | 15     |                |              | 2   | SDIVFIRST  |       |          | R4   | R3      | R3    | 0             |

| DJMP_S |        |                |              | 2   | SDIVSTEP   |       |          | R4   | R3      | R3    | 0             |

| CONT   |        |                |              | 2   | SDIVLAST1  |       |          | R4   | R3      | R3    | 0             |

| BRCC_D | DONE   | Z              |              |     |            |       |          |      |         |       | 1             |

| CONT   |        |                |              | 2   | SDIVLAST2A |       |          | R4   | R3      | R3    | 0             |

| CONT   |        |                |              | 2   | PASS-Q     |       |          |      |         | R1    | 0             |

| CONT   |        |                |              | 2   | QUOCORR    |       |          |      | R1      | R1    | 0             |

| CONT   |        |                |              | 2   | REMCORR    |       |          | R4   | R3      | R3    | 0             |

Note: Divisor in A, Dividend in A Quotient in Q, Remainder in B

Legend: A = A Input B = B Input

S = S input S = Status Register Q = Q Register

R1 = Quotient R2 = Dividend

R3 = RemainderR4 = Divisor

|              |                                 |                                  |                                     |                  |   |   | _ |      |   |   |   |

|--------------|---------------------------------|----------------------------------|-------------------------------------|------------------|---|---|---|------|---|---|---|

|              | 1 <sub>6</sub> – 1 <sub>0</sub> |                                  | Source for<br>Unselected<br>Bytes O |                  |   |   | S | tatu | s |   |   |

| Name         | Code                            | Description                      |                                     | Output           | s | м | L | z    | ۷ | N | С |

| Signed Multi | ply Steps                       |                                  |                                     |                  |   |   |   |      |   |   | ٦ |

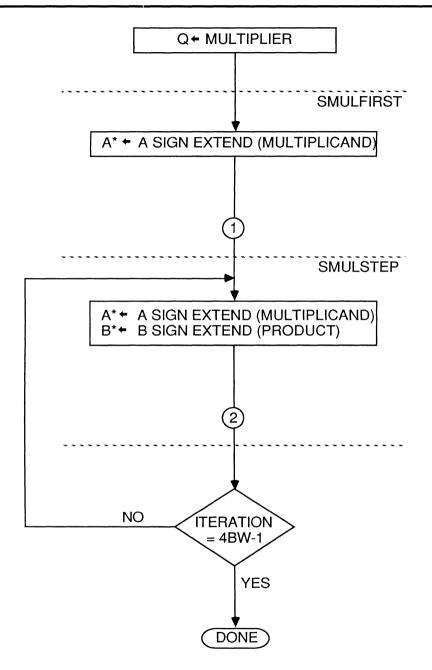

| SMULFIRST    | 5 F                             | First multiply instruction       | В                                   | Y <sup>(1)</sup> |   |   |   |      |   |   | ٦ |

| SMULSTEP     | 5 E                             | Iterate step (#bits/2 - 1 steps) | В                                   | Y <sup>(1)</sup> |   |   |   |      |   |   | ٦ |

| Unsigned Mu  | ltiply Steps                    |                                  |                                     |                  |   |   |   |      |   |   |   |

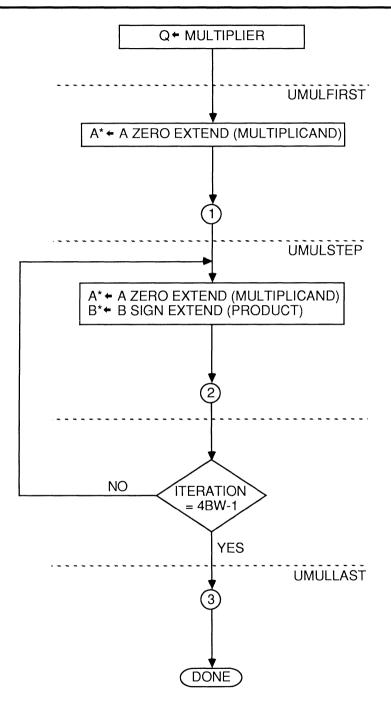

| UMULFIRST    | 5 B                             | First multiply instruction       | В                                   | Y <sup>(1)</sup> |   | * |   |      |   |   |   |

| UMULSTEP     | 5 C                             | Iterate step (#bits/2 - 1 steps) | В                                   | Y <sup>(1)</sup> |   | * |   |      |   |   |   |

| UMULLAST     | 5 D                             | Last multiply instruction        | В                                   | Y <sup>(1)</sup> |   |   |   | *    |   |   |   |

#### TABLE 12-1. MULTIPLY INSTRUCTIONS (Aligned Format)

### TABLE 12-2. EXAMPLE CODING FORM (Unsigned Multiply)

|        | Am2933 | 1              |              |     | Am29333    | 2     |          |      | Am29334 | L     | Am29332 Y-Out |

|--------|--------|----------------|--------------|-----|------------|-------|----------|------|---------|-------|---------------|

| OP     | Branch | Cond<br>Select | Multi<br>Sel | B/W | ОР         | Width | Position | A-IN | B-IN    | Y-OUT | ŌE            |

| CONT   |        |                |              | 3   | ZERO       |       |          |      | R3      | R3    | 0             |

| CONT   |        |                |              | 3   | LOADQ-A    |       |          | R1   |         |       | 1             |

| FOR_D  | 1110   |                |              | 3   | ULMULFIRST |       |          | R2   | R3      | R3    | 0             |

| DJMP_S |        |                |              | 3   | UMULSTEP   |       |          | R2   | R3      | R3    | 0             |

| CONT   |        |                |              | 3   | UMULLAST   |       |          | R2   | R3      | R3    | 0             |

| CONT   |        |                |              | 3   | PASS-Q     |       |          |      |         | R4    | 0             |

Note: 1. Put ALU output in B.

2. Multiplicand in A, Multiplier in Q Product (HIGH) in B, Product (LOW) in Q

Legend: A = A Input B = B Input

S = Status Register

Q = Q Register

R1 = Multiplier

R2 = Multiplicand R3 = Product (HIGH) R4 = Product (LOW)

|           |      |                        |                        |    | Status |   |   |   |   |   |   |

|-----------|------|------------------------|------------------------|----|--------|---|---|---|---|---|---|

| Mnemonics | Code | Description            | Y Output               |    | s      | м | L | z | v | N | с |

| NB-0F-SHA | 62   | Field Shift, Zero Fill | $Y_{i+p} = A_{i}, 0$   | 2) |        |   |   | * |   | * |   |

| NB-0F-SHB | 63   |                        | $Y_{i+p} = B_{i}, 0$   | 2) |        |   |   | * |   | * |   |

| NB-SN-SHA | 60   | Field Shift, Sign Fill | $Y_{i+p} = A_i, N$     | 2) |        |   |   | * |   | * |   |

| NB-SN-SHB | 61   |                        | $Y_{i+p} = B_i$ , N    | 2) |        |   |   | * |   | * |   |

| NBROT-A   | 64   | Field Rotate           | $Y_i = A_{(i-p)mod32}$ | 3) |        |   |   | * |   | * |   |

| NBROT-B   | 65   |                        | $Y_i = B_{(i-p)mod32}$ | 3) |        |   |   | * |   | * |   |

#### TABLE 13. SHIFT/ROTATE INSTRUCTIONS

Notes: 1. These instructions use the field instruction format (FORMAT 2).

2. "p" stands for bit displacement from  $P_0 - P_5$  or from  $PR_0 - PR_5$  ( $-32 \le p \le 31$ ). If p is positive,  $Y_{p-1}$  to  $Y_0$  are equal to the fill bit. If p is negative,  $Y_{31}$  to  $Y_{31+p+1}$  are equal to the fill bit. 3. The sign of the position input is ignored for this instruction and  $P_0 - P_4$  are treated as a positive magnitude for a circular upshift.

| Legend: | A = A Input | Q = Q Register |

|---------|-------------|----------------|

| Ū.      | B = B Input | * = Updated    |

Examples: \* NB-0F-SHA,4

Shift A up 4 bits and zero fill

NB-0F-SHB,,-17 Shift B down 17 bits and sign fill

\*Width field not used

|             |      |             |       |                                                                                                  |    |   | S | tatu | JS |   |   |   |

|-------------|------|-------------|-------|--------------------------------------------------------------------------------------------------|----|---|---|------|----|---|---|---|

| Mnemonics   | Code | Description | Unsel | Sel                                                                                              |    | s | м | L    | z  | ٧ | Ν | С |

| SETBIT-A    | 68   | Bit Set     | A     | $Y_i = A_i, Y_p = 1$                                                                             |    |   |   |      | *  |   | * |   |

| SETBIT-B    | 69   |             | В     | $Y_i = B_i, Y_p = 1$                                                                             |    |   |   |      | *  |   | * |   |

| RSTBIT-A    | 6A   | Bit Reset   | A     | $Y_i = A_i, Y_p = 0$                                                                             |    |   |   |      | *  |   | * |   |

| RSTBIT-B    | 6B   |             | В     | $Y_i = B_i, Y_p = 0$                                                                             |    |   |   |      | *  |   | * |   |

| EXTBIT-A    | 66   | Bit Extract | 0     | $\begin{array}{l} \mbox{if } p>0, \ Y_0=A_p \\ \mbox{if } p<0, \ Y_0=\overline{A}_p \end{array}$ | 2) |   |   | *    | *  |   |   |   |

| EXTBIT-B    | 67   |             | 0     | $\begin{array}{l} \mbox{if } p>0, \ Y_0=B_p \\ \mbox{if } p<0, \ Y_0=\overline{B}_p \end{array}$ | 2) |   |   | *    | *  |   |   |   |

| EXTBIT-STAT | 7E   |             | 0     | $\begin{array}{l} \mbox{if } p>0, \ Y_0=S_p \\ \mbox{if } p<0, \ Y_0=\overline{S}_p \end{array}$ | 2) |   |   | *    |    |   |   |   |

#### TABLE 14-1. BIT-MANIPULATION INSTRUCTIONS

Notes: 1. These instructions use the field instruction format (FORMAT 2).

2. Y<sub>31</sub> to Y<sub>1</sub> are set to zero. "p" stands for the bit displacement from P<sub>0</sub> - P<sub>4</sub> or from PR<sub>0</sub> - PR<sub>5</sub>. The sign of the position input is ignored.

TABLE 14-2. BIT-MANIPULATION INSTRUCTIONS

|             |      |                |                    |          |   | Status |   |   | atus |   |   |  |

|-------------|------|----------------|--------------------|----------|---|--------|---|---|------|---|---|--|

| Mnemonics   | Code | Description    | Status Register    | Y Output | s | м      | L | z | v    | Ν | с |  |

| SETBIT-STAT | 6C   | Status Bit Set | S <sub>p</sub> = 1 | S        | * | *      | * | * | *    | * | * |  |

| RSTBIT-STAT | 6D   |                | S <sub>p</sub> = 0 | S        | * | *      | * | * | *    | * | * |  |

Notes: 1. These instructions use the Field instruction format (FORMAT 2).

2. "p" stands for the bit displacement from P0 - P5 or from PR0 - PR5.

| Legend: | Unsel = Unselected field | Q = Q Register |

|---------|--------------------------|----------------|

| 5       | Sel = Selected field     | * = Updated    |

|         | A = A Input              |                |

|         |                          |                |

B = B Input

Examples:

RSTBIT-B,,3 EXTBIT-STAT,,-4 3rd bit is set to 0 in B 4th bit in status register is extracted and inverted.

Figure 6. Field Logical Operations

|            |      |                  |       |       | Y Output                                                                                                                                                    |   |   | St | atı | IS |   |   |

|------------|------|------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|-----|----|---|---|

| Mnemonics  | Code | Description      |       | Unsel | Sel                                                                                                                                                         | s | м | L  | z   | ٧  | N | с |

| PASSF-AL-A | 73   | Field Pass       | 3)    | В     | $Y_i = A_i$                                                                                                                                                 |   |   |    | *   |    | • |   |

| PASSF-AL-B | 6F   |                  | 3)    | В     | Y <sub>i</sub> = B <sub>i</sub>                                                                                                                             |   |   |    | *   |    | ٠ |   |

| PASSF-A    | 72   |                  | 4)    | В     | $ \begin{array}{l} \text{if } p \geqslant 0, \ Y_i = A_{i-p} \\ \text{if } p < 0, \ Y_{i- p } = A_i \end{array} $                                           |   |   |    | *   |    | * |   |

| NOTF-AL-A  | 71   | Field Complement | 3)    | В     | $Y_j = \overline{A}_j$                                                                                                                                      |   |   |    | *   |    | * |   |

| NOTF-AL-B  | 6E   |                  | 3)    | В     | $Y_i = \overline{B}_i$                                                                                                                                      |   |   |    | *   |    | * |   |

| NOTF-A     | 70   |                  | 4)    | В     | if $p \ge 0$ , $Y_i = \overline{A}_{i-p}$<br>if $p < 0$ , $Y_{i- p } = \overline{A}_i$                                                                      |   |   |    | *   |    | * |   |

| ORF-AL-A   | 75   | Field OR         | 3)    | В     | Y <sub>i</sub> = A <sub>i</sub> OR B <sub>i</sub>                                                                                                           | T |   |    | *   |    | * |   |

| ORF-A      | 74   |                  | 4)    | В     | if $p \ge 0$ , $Y_i = A_{i-p}$ OR $B_i$<br>if $p < 0$ , $Y_{i- p } = A_i$ OR $B_{i- p }$                                                                    |   |   |    | *   |    | * |   |

| XORF-AL-A  | 77   | Field XOR        | 3)    | В     | Y <sub>i</sub> = A <sub>i</sub> XOR B <sub>i</sub>                                                                                                          | T | 1 |    | *   |    | * |   |

| XORF-A     | 76   |                  | 4)    | В     | $\begin{array}{l} \text{if } p \geqslant 0, \ Y_i = A_{i-p} \ \text{XOR} \ B_i \\ \text{if } p < 0, \ Y_{i- p } = A_i \ \text{XOR} \ B_{i- p } \end{array}$ |   |   |    | *   |    | * |   |

| ANDF-AL-A  | 79   | Field AND        | 3)    | В     | Y <sub>i</sub> = A <sub>i</sub> AND B <sub>i</sub>                                                                                                          |   |   |    | *   |    | * |   |

| ANDF-A     | 78   |                  | 4)    | В     | if $p \ge 0$ , $Y_i = A_{i-p}$ AND $B_i$<br>if $p < 0$ , $Y_{i- p } = A_i$ AND $B_{i- p }$                                                                  |   |   |    | *   |    | * |   |

| EXTF-A     | 7A   | Field Extract    | 4) 5) | 0     | $ \begin{array}{l} \text{if } p \geqslant 0, \ Y_i = A_{i-p} \\ \text{if } p < 0, \ Y_{i- p } = A_i \end{array} $                                           |   |   |    | •   |    | * |   |

| EXTF-B     | 7B   |                  | 4) 5) | 0     | if $p \ge 0$ , $Y_i = B_{i-p}$<br>if $p < 0$ , $Y_{i- p } = B_i$                                                                                            |   |   |    | *   |    | * |   |

| EXTF-AB    | 7C   |                  |       | 0     | 6)                                                                                                                                                          |   | T |    | ٠   |    | * |   |

| EXTF-BA    | 7D   |                  |       | 0     | 7)                                                                                                                                                          | 1 | T |    | *   |    | * |   |

TABLE 15. FIELD LOGICAL INSTRUCTIONS

Notes: 1. These instructions use the field instruction format (FORMAT 2).

2.  $p \le i \le p + w - 1$ . "p" stands for position displacement from P<sub>0</sub> - P<sub>5</sub> or from PR<sub>0</sub> - PR<sub>5</sub> and "w" for the width of the bit field from  $W_0 - W_4$  or  $WR_0 - WR_4$ . Whenever p + w > 32, operation takes place only over the portion of the field up to the end of the word. No wraparound occurs.

3. This instruction uses the aligned format (see Figure 6).

4. This instruction uses the unaligned field format (see Figure 6).

p≥0: Case 1

p < 0: Case 2

5. If p is positive, the input is LSB aligned and Y output aligned at position.

If p is negative, the input is aligned at |p| and Y output at LSB.