### PRELIMINARY

# Am79C974

PCnet<sup>™</sup>-SCSI Combination Ethernet and SCSI Controller for PCI Systems

# **DISTINCTIVE CHARACTERISTICS**

### **PCI Features**

- Direct glueless interface to 33 MHz, 32-bit PCI local bus

- 132 Mbyte/s burst DMA transfer rate

- Compliant to PCI local bus Specification Revision 2.0

#### **Ethernet Features**

- Supports ISO 8802-3 (IEEE/ANSI 802.3) and Ethernet Standards

- High-performance Bus Master architecture with integrated DMA Buffer Management Unit for low CPU and bus utilization

- Individual 136-byte transmit and 128-byte receive FIFOs provide frame buffering for increased system latency

- Microwire<sup>™</sup> EEPROM interface supports jumperless design

- Integrated Manchester Encoder/Decoder

- Provides integrated Attachment Unit Interface (AUI) and 10BASE-T transceiver with automatic port selection

- Automatic Twisted-Pair receive polarity detection and automatic correction of the receive polarity

- Dynamic transmit FCS generation programmable on a frame-by-frame basis

- Internal/external loopback capabilities

- Supports the following types of network interfaces:

- AUI to external 10BASE2, 10BASE5, 10BASE-T or 10BASE-F MAU

- Internal 10BASE-T transceiver with Smart .

Squelch to Twisted-Pair medium

# **SCSI Features**

- Compliant to ANSI standards X3.131 1986 (SCSI-1) and X3.131 – 199X (SCSI-2)

- Fast 8-bit SCSI-2 10 Mbyte/s synchronous or 7 Mbyte/s asynchronous data transfer rate

- SCSI specific Bus Mastering DMA engine (32-bit address/data)

- 96-byte DMA FIFO for low bus latency

- On-chip state machine to control the SCSI sequences in hardware

- Integrated industry standard Fast SCSI-2 core

- Single-Ended 48 mA outputs to drive the SCSI bus directly

- Support for Scatter-Gather DMA data transfers

- Hooks in silicon and software to enable disk drive spin down for power savings

### **General Features**

- Software compatible with AMD's Am79C960 PCnet-ISA, Am79C961 PCnet-ISA+, Am79C965 PCnet-32, Am79C970 PCnet-PCI register and descriptor architecture

- Plug-in and software compatible with AMD's PCscsi family of SCSI controllers for PCI

- NAND Tree test mode for connectivity testing on printed circuit boards

- Single +5 V power supply operation

- Low-power, CMOS design with sleep modes for both Ethernet and SCSI controllers allows reduced power consumption for critical battery powered applications and 'Green PCs'

- Fully static design for low frequency and power operation

- 132-pin PQFP package

# **GENERAL DESCRIPTION**

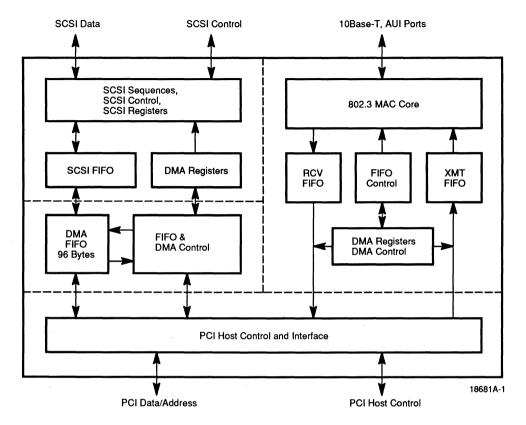

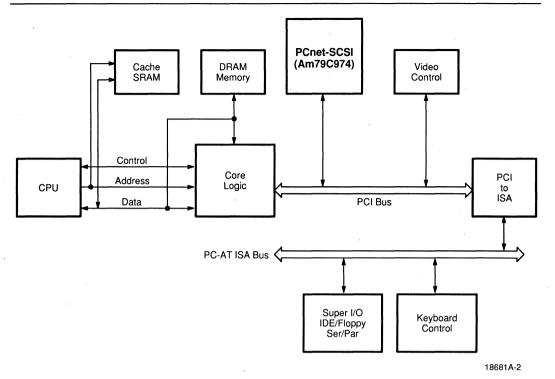

The PCnet-SCSI combination Ethernet and 8-bit Fast SCSI controller with a 32-bit PCI bus interface is a highly integrated Ethernet-Fast SCSI system solution designed to address high-performance system application requirements. This single-chip is a flexible bus-mastering device that can be used in many applications, includ-

ing network- and SCSI-ready PCs, printers, fax modems, and bridge/router designs. The bus-master architecture provides high data throughput in the system and low CPU and system bus utilization. The PCnet-SCSI controller is fabricated with AMD's advanced low-power CMOS process to provide low oper-

| This document contains information on a product under development at Advanced Micro Devices, Inc. The information is intended       | Publication# 18681  | Rev. A | Amendment/0 |  |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|-------------|--|

| to help you to evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice. | Issue Date: January | / 1994 |             |  |

Advanced Micro Devices ating and standby current for power sensitive applications.

The PCnet-SCSI is part of AMD's PCI product family of plug-in and software compatible SCSI and Ethernet controllers. This product compatibility ensures a low cost system upgrade path and lower motherboard manufacturing costs.

### **Ethernet Specific**

The PCnet-SCSI controller includes a complete Ethernet node integrated into a single VLSI device. It contains a bus interface unit, a DMA buffer management unit, an IEEE 802.3-defined Media Access Control (MAC) function, individual 136-byte transmit and 128-byte receive FIFOs, an IEEE 802.3-defined Attachment Unit Interface (AUI) and Twisted-Pair Transceiver Media Attachment Unit (10BASE-T MAU), and a Microwire EEPROM interface. The PCnet-SCSI controller is also register compatible with the LANCE (Am7990) Ethernet controller, the C-LANCE (Am79C90) Ethernet controller, the ILACC (Am79C900) Ethernet controller, and all Ethernet controllers in the PCnet Family, including the PCnet-ISA controller (Am79C960), the PCnet-ISA+ controller (Am79C961), and the PCnet-32 controller (Am79C965). The buffer management unit supports the LANCE, ILACC, and PCnet descriptor software models. The PCnet-SCSI controller is software compatible with the Novell NE2100 and NE1500 Ethernet adapter card architectures. In addition, a Sleep function has been incorporated to provide low standby current, excellent for notebooks and Green PCs.

The 32-bit multiplexed bus interface unit provides a direct interface to the PCI local bus applications, simplifying the design of an Ethernet node in a PC system. With its built-in support for both little and big endian byte alignment, this controller also addresses proprietary non-PC applications.

The PCnet-SCSI controller supports auto configuration in the PCI configuration space. Additional PCnet-SCSI controller configuration parameters, including the unique IEEE physical address, can be read from an external non-volatile memory (serial EEPROM) immediately following system RESET.

The controller also has the capability to automatically select either the AUI port or the Twisted-Pair transceiver. Only one interface is active at any one time. The individual transmit and receive FIFOs optimize system overhead, providing sufficient latency during frame transmission and reception, and minimizing intervention during normal network error recovery. The integrated Manchester encoder/decoder (MENDEC) eliminates the need for an external Serial Interface Adapter (SIA) in the system. In addition, the device provides programmable on-chip LED drivers for transmit, receive, collision, receive polarity, link integrity or jabber status.

### **SCSI Specific**

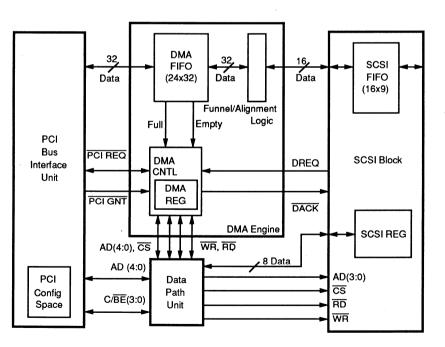

The PCnet-SCSI controller also includes a highperformance Fast SCSI controller with a glueless interface to the PCI local bus. The PCnet-SCSI integrates its own 32-bit bus mastering DMA engine with an industry standard Fast SCSI-2 block. The DMA engine and accompanying 96 byte DMA FIFO allow 32-bit burst data transfers across the high bandwidth PCI bus at speeds of up to 132 Mbyte/s. Full support for scatter-gather DMA transfers optimize performance in multi-tasking system applications.

The PCnet-SCSI's on-chip state machine controls SCSI bus sequences in hardware and is coupled with the bus mastering DMA engine to eliminate the need for an onchip RISC processor. This results in a smaller die size giving the Am79C974 superior price/performance versus competitive offerings.

AMD supports the Am79C974 with a total system solution which includes:

- A full suite of licensable SCSI drivers and utilities fully tested under the following operating system environments:

- DOS 5.0 6.0

- Windows 3.1

- Windows NT

- --- OS/2 2.x

- Netware 3.x, 4.x

- SCO UNIX 3.2.4, ODT 2.0

- An INT13h Compatible SCSI ROM BIOS

- ASPI Compatibility

- Complete hardware reference design kit

For more detailed information on the PCnet-SCSI refer to the technical manual, PID #18738A.

AMD 🎝

# HIGH LEVEL BLOCK DIAGRAM

# TABLE OF CONTENTS

| DISTINCTIVE CHARACTERISTICS 1                                                   |

|---------------------------------------------------------------------------------|

| GENERAL DESCRIPTION 1                                                           |

| HIGH LEVEL BLOCK DIAGRAM                                                        |

| RELATED PRODUCTS 11                                                             |

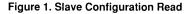

| CONNECTION DIAGRAM                                                              |

| <b>ORDERING INFORMATION</b>                                                     |

| PIN DESIGNATIONS                                                                |

| Listed By Pin Number                                                            |

| Listed By Pin Name                                                              |

| Listed By Driver Type                                                           |

| LOGIC SYMBOL                                                                    |

| PIN DESCRIPTION                                                                 |

| PCI Bus Interface                                                               |

| Ethernet Controller Pins                                                        |

| Board Interface                                                                 |

| Microwire EEPROM Interface 23                                                   |

| Attachment Unit Interface                                                       |

| Twisted-Pair Interface                                                          |

| SCSI Controller Pins                                                            |

| Miscellaneous                                                                   |

| Power Supply                                                                    |

| BASIC FUNCTIONS                                                                 |

| System Bus Interface Function                                                   |

| Software Interface       26         Ethernet Interfaces       26                |

| SCSI Interfaces                                                                 |

| DETAILED FUNCTIONS                                                              |

| Bus Interface Unit (BIU)                                                        |

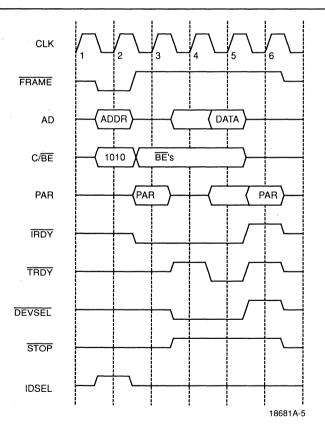

| Slave Configuration Transfers                                                   |

| Slave I/O Transfers                                                             |

| Bus Acquisition                                                                 |

| Bus Master DMA Transfers       32         Target Initiated Termination       37 |

| Master Initiated Termination                                                    |

| Ethernet Controller                                                             |

| Buffer Management Unit (BMU)                                                    |

| Initialization                                                                  |

| Re-Initialization 43                                                            |

| Buffer Management                                                               |

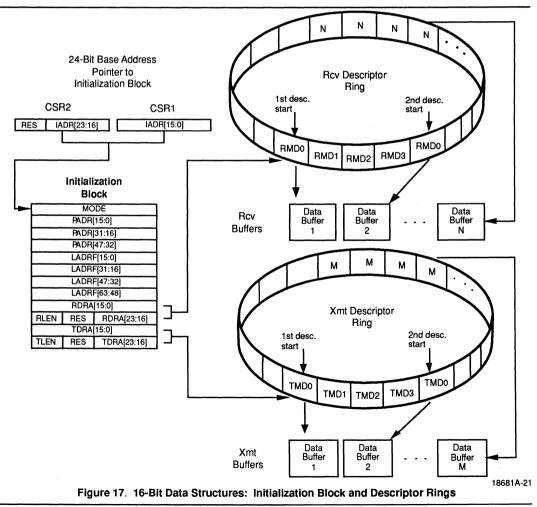

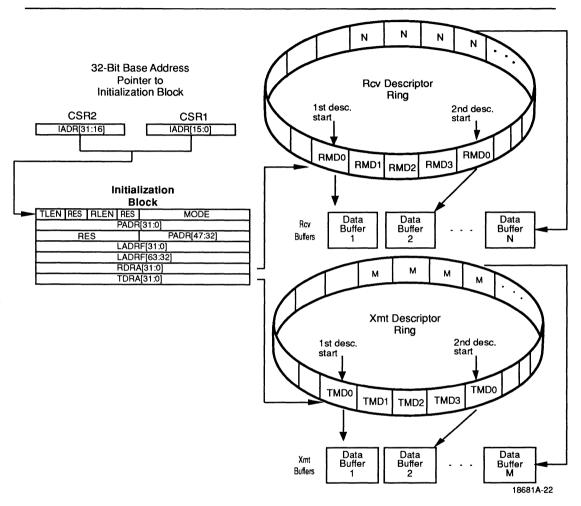

| Descriptor Rings                                                                |

| Descriptor Ring Access Mechanism       44         Polling       46              |

| Transmit Descriptor Table Entry (TDTE)                                          |

| Receive Descriptor Table Entry (RDTE) 48                                        |

| Media Access Control                                                                                                                                                                                                 | 3                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Transmit and Receive Message Data Encapsulation       48         Media Access Management       50                                                                                                                    |                       |

| Manchester Encoder/Decoder (MENDEC) 52                                                                                                                                                                               | 2                     |

| External Crystal Characteristics52External Clock Drive Characteristics52MENDEC Transmit Path52Transmitter Timing and Operation52Receiver Path53                                                                      | 222                   |

| Input Signal Conditioning53Clock Acquisition53PLL Tracking54Carrier Tracking and End of Message54Data Decoding54Differential Input Terminations54Collision Detection55Jitter Tolerance Definition55                  | 3<br>4<br>4<br>5<br>5 |

| Attachment Unit Interface (AUI)                                                                                                                                                                                      |                       |

| Twisted-Pair Transceiver (T-MAU)       55         Twisted-Pair Transmit Function       55         Twisted-Pair Receive Function       55                                                                             | 5                     |

| Link Test Function                                                                                                                                                                                                   | 5                     |

| Collision Detect Function       57         Signal Quality Error (SQE) Test (Heartbeat) Function       57         Jabber Function       57         Power Down       57         10BASE-T Interface Connection       57 | 7<br>7<br>7           |

| Ethernet Power Savings Modes 58                                                                                                                                                                                      | 3                     |

| Software Access                                                                                                                                                                                                      | 3                     |

| Ethernet PCI Configuration Registers       58         I/O Resources       59         I/O Register Access       61                                                                                                    | )                     |

| Hardware Access                                                                                                                                                                                                      | ł                     |

| PCnet-SCSI Controller Master Accesses       64         Slave Access to I/O Resources       64         EEPROM Microwire Access       66                                                                               | ţ                     |

| Transmit Operation                                                                                                                                                                                                   | )                     |

| Transmit Function Programming       69         Automatic Pad Generation       69         Transmit FCS Generation       70         Transmit Exception Conditions       70                                             | )<br>)                |

| Receive Operation                                                                                                                                                                                                    | ł                     |

| Receive Function Programming71Automatic Pad Stripping71Receive FCS Checking72Receive Exception Conditions72                                                                                                          | 1<br>2<br>2           |

| Loopback Operation                                                                                                                                                                                                   |                       |

| LED Support                                                                                                                                                                                                          | 3                     |

| AMD | 1 |

|-----|---|

| H_RESET, S_RESET, and STOP                                                                                                                                                                                                                              | 74                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| H_RESET<br>S_RESET<br>STOP                                                                                                                                                                                                                              | 74                   |

| SCSI Controller                                                                                                                                                                                                                                         |                      |

| SCSI Specific DMA Engine                                                                                                                                                                                                                                |                      |

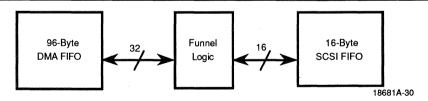

| DMA FIFO<br>DMA Blast Command<br>Funneling Logic<br>SCSI DMA Programming Sequence                                                                                                                                                                       | 76<br>76<br>76<br>76 |

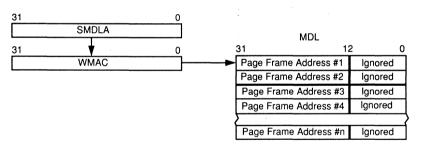

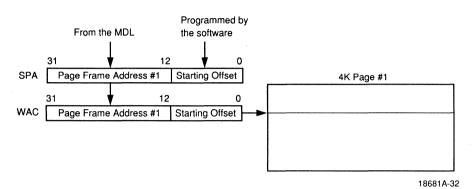

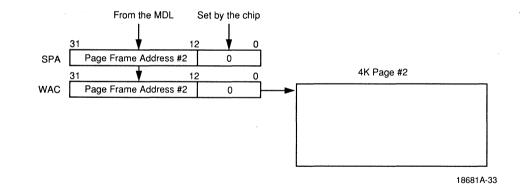

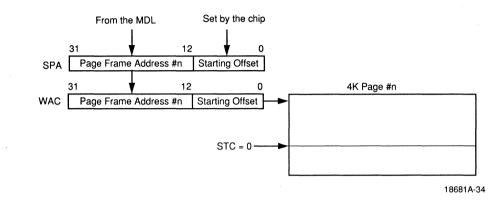

| MDL Based DMA Programming                                                                                                                                                                                                                               | 78                   |

| Memory Descriptor List (MDL)<br>DMA Scatter-Gather Operation (4k aligned elements)<br>DMA Scatter-Gather Operation (Non-4k aligned elements MDL not set)                                                                                                | 78                   |

| Interrupts                                                                                                                                                                                                                                              | 81                   |

| The Fast SCSI Block                                                                                                                                                                                                                                     | 81                   |

| SCSI Block ID<br>SCSI FIFO Threshold<br>Data Transmission<br>REQ/ACK Control<br>Parity                                                                                                                                                                  | 81<br>81<br>81       |

| Parity Checking on the SCSI Bus                                                                                                                                                                                                                         |                      |

| Parity Generating on the SCSI Bus                                                                                                                                                                                                                       |                      |

| Reset Levels                                                                                                                                                                                                                                            | 82                   |

| Hard Reset: (H)                                                                                                                                                                                                                                         | 82<br>82             |

| Device Commands                                                                                                                                                                                                                                         | 83                   |

| Command Stacking<br>Invalid Commands<br>Command Window<br>Initiator Commands                                                                                                                                                                            | 84<br>84             |

| Information Transfer Command<br>Initiator Command Complete Steps<br>Message Accepted Command<br>Transfer Pad Bytes Command<br>Set ATN Command<br>Reset ATN Command                                                                                      | 85<br>85<br>85<br>85 |

| Idle State Commands                                                                                                                                                                                                                                     | 86                   |

| Select Without ATN Steps Command         Select With ATN Steps Command         Select With ATN and Stop Steps Command         Enable Selection/Reselection Command         Disable Selection/Reselection Command         Select With ATN3 Steps Command | 86<br>86<br>86<br>87 |

| General Commands                                                                                                                                                                                                                                        |                      |

| No Operation Command<br>Clear FIFO Command<br>Reset Device Command<br>Reset SCSI Bus Command                                                                                                                                                            | 87<br>87<br>87       |

| SCSI Power Management Features                                                |

|-------------------------------------------------------------------------------|

| SCSI Activity Pin                                                             |

| Reduced Power Mode                                                            |

| Power Down Pin (PWDN Pin)                                                     |

| Software Disk Spin-Down                                                       |

| NAND Tree Testing                                                             |

| ABSOLUTE MAXIMUM RATINGS                                                      |

| OPERATING RANGES                                                              |

| DC CHARACTERISTICS: PCI Bus and Board Interface                               |

| DC CHARACTERISTICS: Attachment Unit Interface                                 |

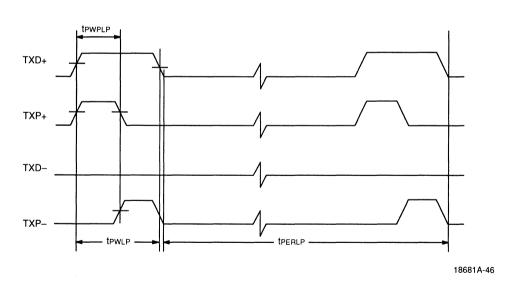

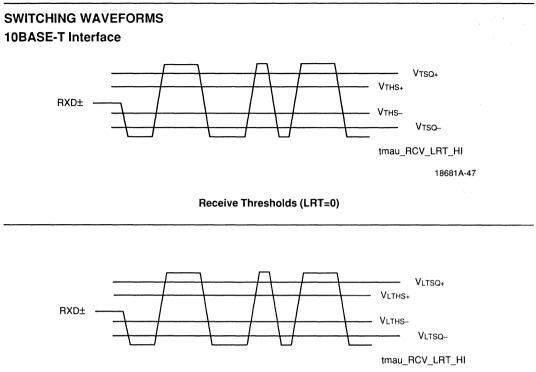

| DC CHARACTERISTICS: 10BASE-T Interface                                        |

| DC CHARACTERISTICS: SCSI Interface                                            |

| DC CHARACTERISTICS: Capacitance, ESD, and Latch Up                            |

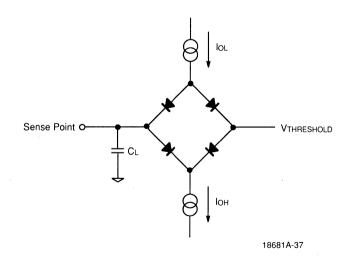

| AC SWITCHING CHARACTERISTICS: PCI Bus and Board Interface                     |

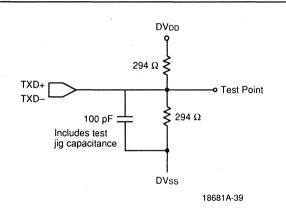

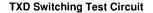

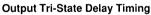

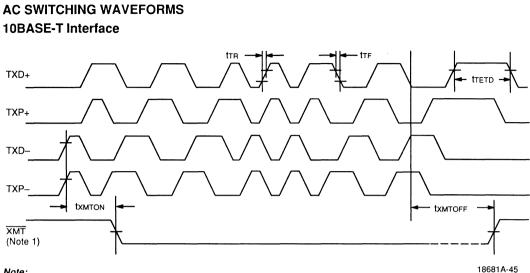

| AC SWITCHING CHARACTERISTICS: 10BASE-T Interface                              |

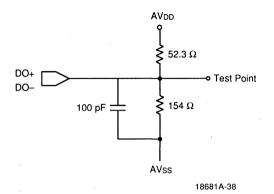

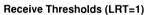

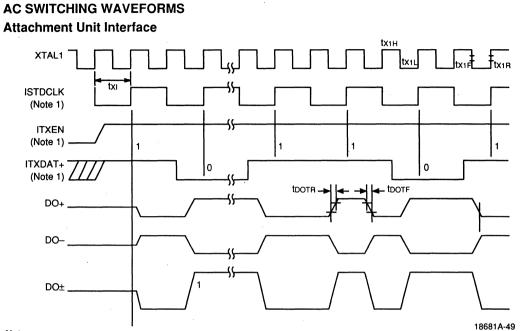

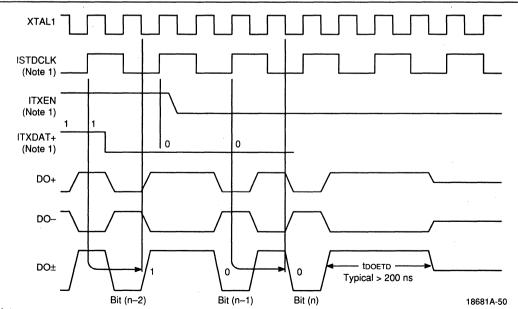

| AC SWITCHING CHARACTERISTICS: Attachment Unit Interface                       |

| AC SWITCHING CHARACTERISTICS: SCSI Interface                                  |

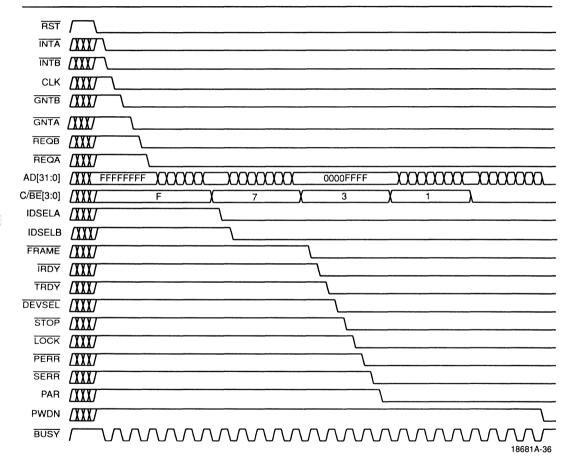

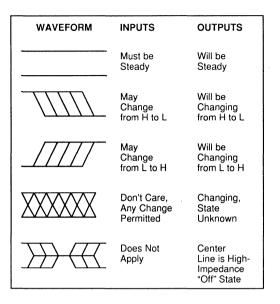

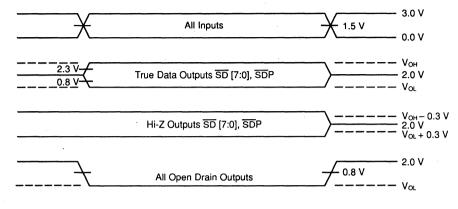

| KEY TO SWITCHING WAVEFORMS         101                                        |

| <b>AC SWITCHING TEST CIRCUITS</b>                                             |

| AC SWITCHING WAVEFORMS: System Bus Interface                                  |

| AC SWITCHING WAVEFORMS: 10BASE-T Interface                                    |

| AC SWITCHING WAVEFORMS: Attachment Unit Interface                             |

| AC SWITCHING WAVEFORMS: SCSI Interface                                        |

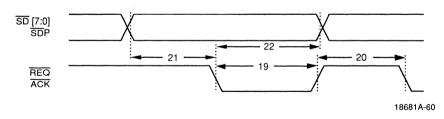

| PHYSICAL DIMENSIONS                                                           |

| APPENDIX A – Register Summary 113                                             |

| Ethernet Controller                                                           |

| Control and Status Registers                                                  |

| SCSI Controller                                                               |

| SCSI Register Map                                                             |

| APPENDIX B – PCnet-SCSI Compatible Media Interface Modules                    |

| APPENDIX C – Recommendation for Power and Ground Decoupling 121               |

| APPENDIX D – Alternative Method for Initialization of Ethernet Controller 123 |

| APPENDIX E – SCSI System Considerations                                       |

| APPENDIX F – Designing a Single Motherboard for AMD PCI Family                |

# LIST OF FIGURES

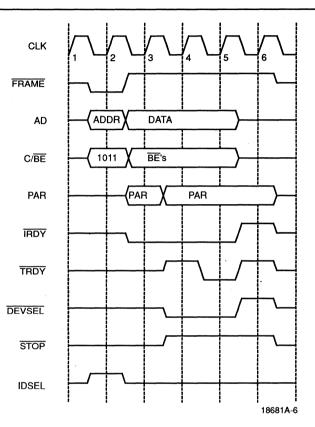

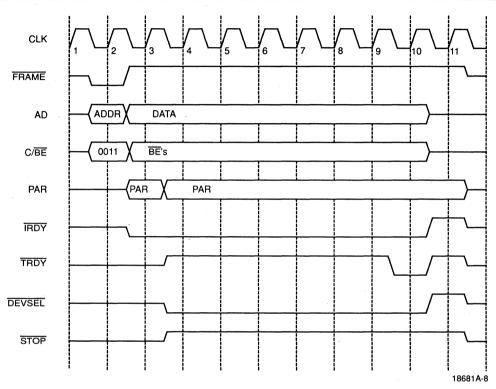

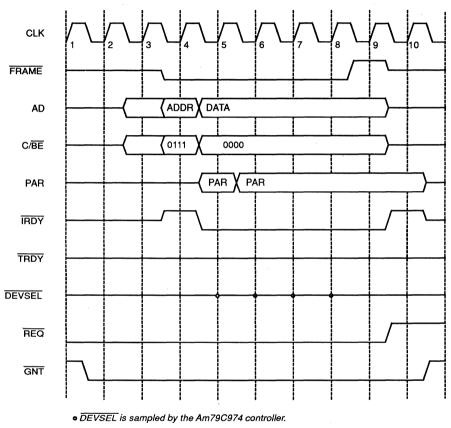

| Figure 1. Slave Configuration Read 27                                        |

|------------------------------------------------------------------------------|

| Figure 2. Slave Configuration Write                                          |

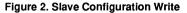

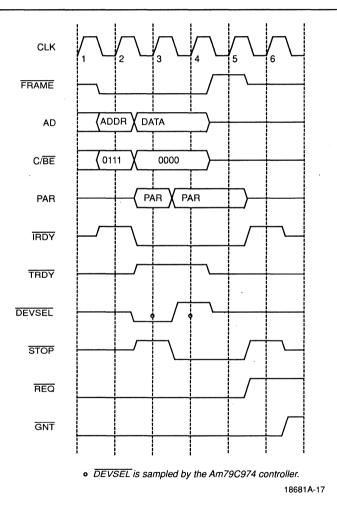

| Figure 3. Slave I/O Read                                                     |

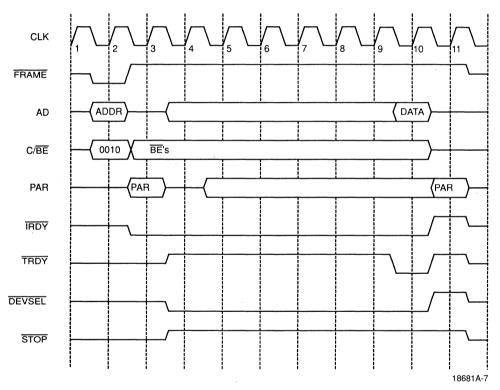

| Figure 4. Slave I/O Write                                                    |

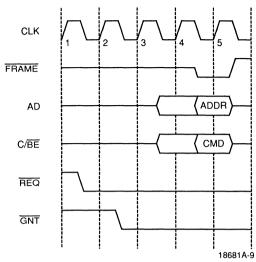

| Figure 5. Bus Acquisition                                                    |

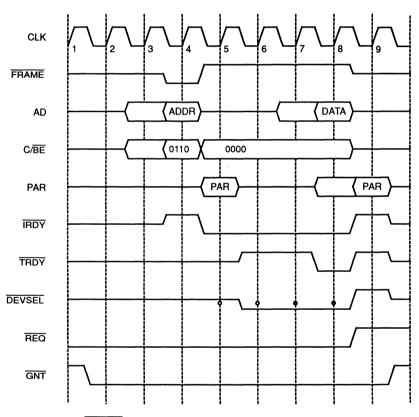

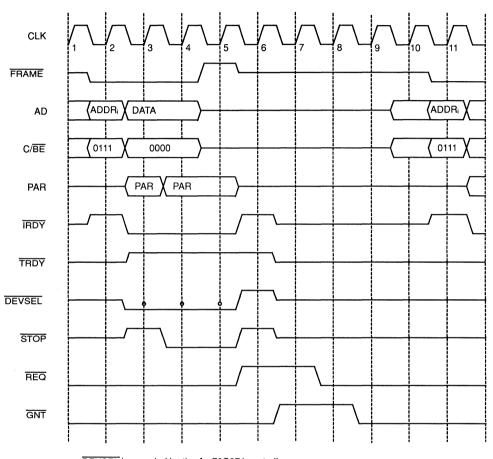

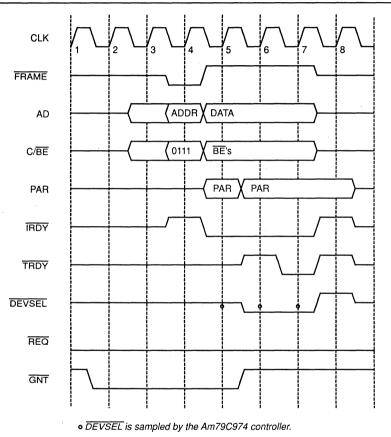

| Figure 6. Non-Burst Read Cycles With Wait States                             |

| Figure 7. Non-Burst Read Cycles Without Wait States                          |

| Figure 8. Non-Burst Read Cycles With and Without Wait States                 |

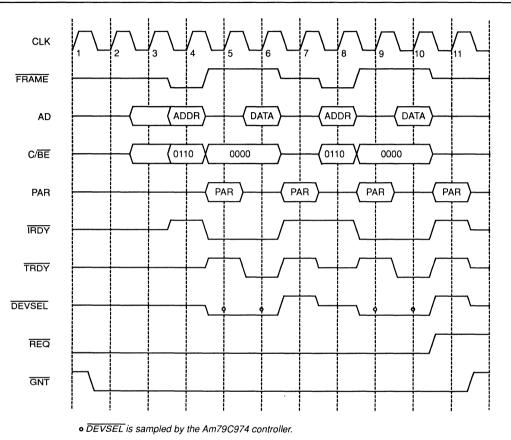

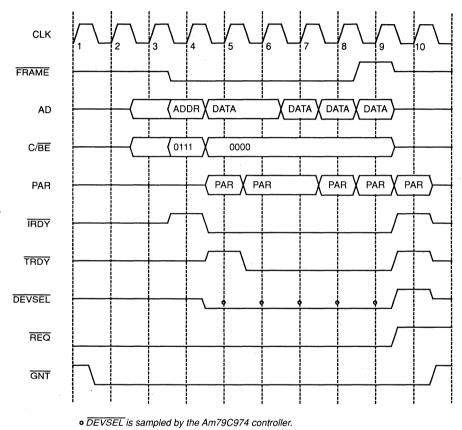

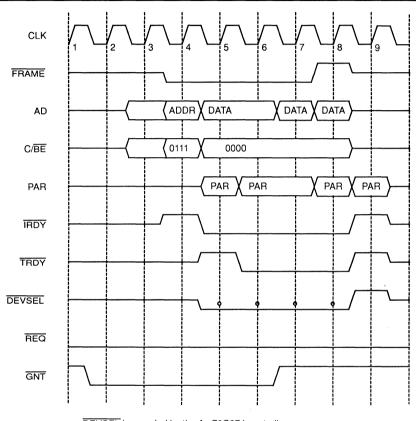

| Figure 9. Burst Read Cycles                                                  |

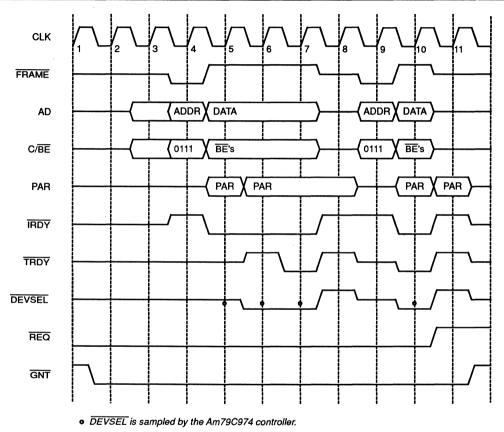

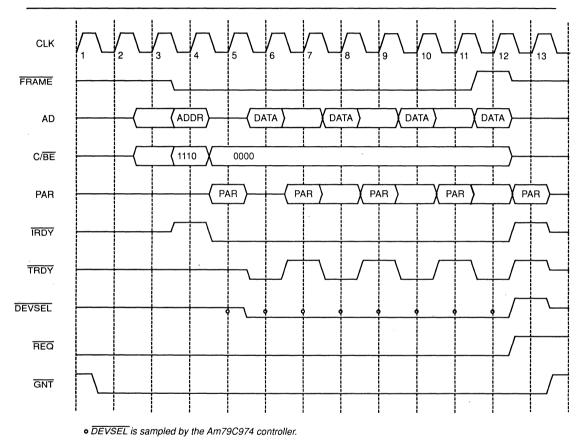

| Figure 10. Burst Write Cycles                                                |

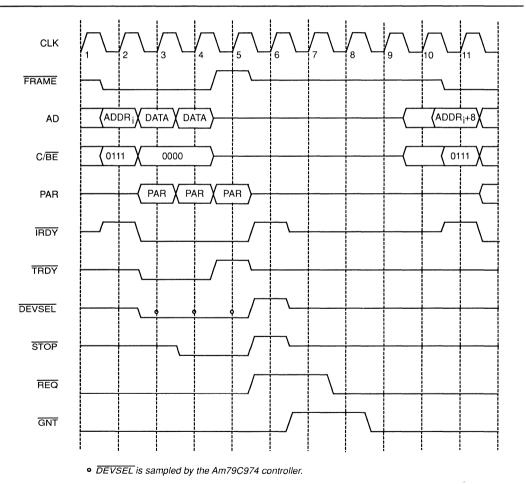

| Figure 11. Disconnect With Data Transfer                                     |

| Figure 12. Disconnect Without Data Transfer                                  |

| Figure 13. Target Abort                                                      |

| Figure 14. Preemption When FRAME is Deasserted 40                            |

| Figure 15. Preemption When FRAME is Asserted                                 |

| Figure 16. Master Abort                                                      |

| Figure 17. 16-Bit Data Structures: Initialization Block and Descriptor Rings |

| Figure 18. 32-Bit Data Structures: Initialization Block and Descriptor Rings |

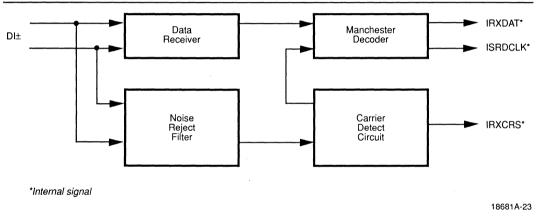

| Figure 19. Receiver Block Diagram 53                                         |

| Figure 20. Differential Input Termination                                    |

| Figure 21. 10BASE-T Interface Connection 57                                  |

| Figure 22. ISO 8802-3 (IEEE/ANSI 802.3) Data Frame                           |

| Figure 23. 802.3 Frame and Length Field Transmission Order                   |

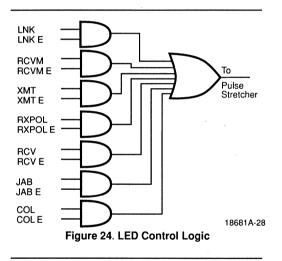

| Figure 24. LED Control Logic                                                 |

| Figure 25. PCI BIU – DMA Engine – SCSI Block                                 |

| Figure 26. DMA FIFO to SCSI FIFO Interface                                   |

| Figure 27. Am79C974 NAND Tree Test Structure    89                           |

| Figure 28. NAND Tree Waveform                                                |

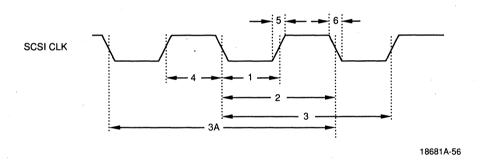

| Figure 29. SCSI Clock Input 110                                              |

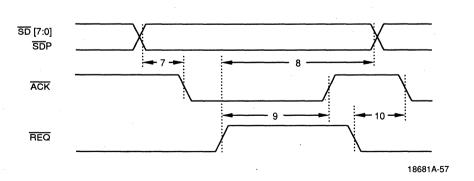

| Figure 30. Asynchronous Initiator Transmit 110                               |

| Figure 31. Asynchronous Initiator Receive 111                                |

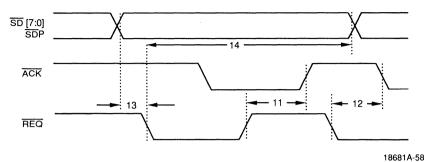

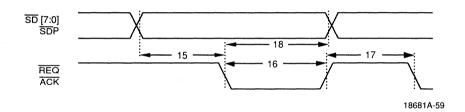

| Figure 32. Synchronous Initiator Transmit 111                                |

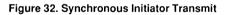

| Figure 33. Synchronous Initiator Receive 111                                 |

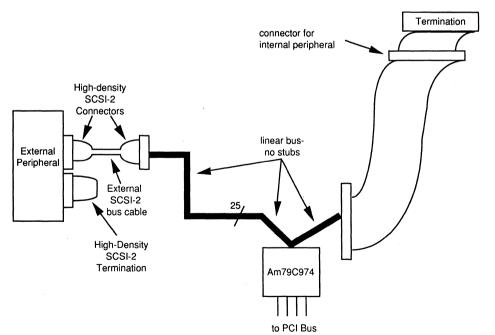

| Figure E-1. Ideal Routing Scheme for SCSI 124                                |

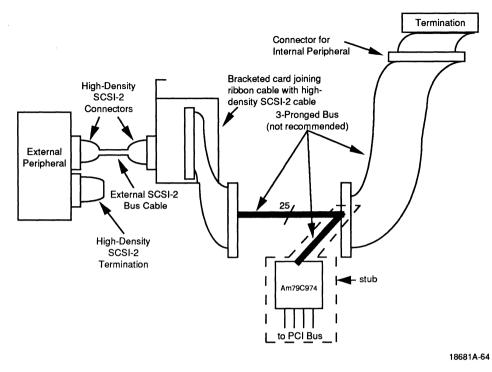

| Figure E-2. A Poor Routing Scheme for SCSI 125                               |

| Figure E-3. Motherboard Layout – Approach #1 126                             |

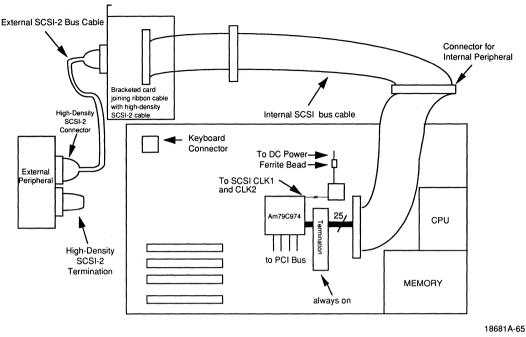

| Figure E-4. Motherboard Layout – Approach #2 127                             |

| Figure E-5. Decoupling Capacitor Placement 129                               |

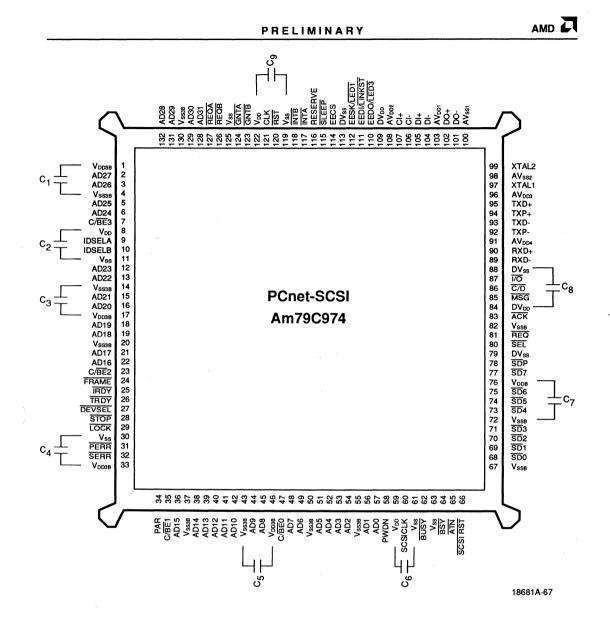

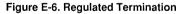

| Figure E-6. Regulated Termination 130                                        |

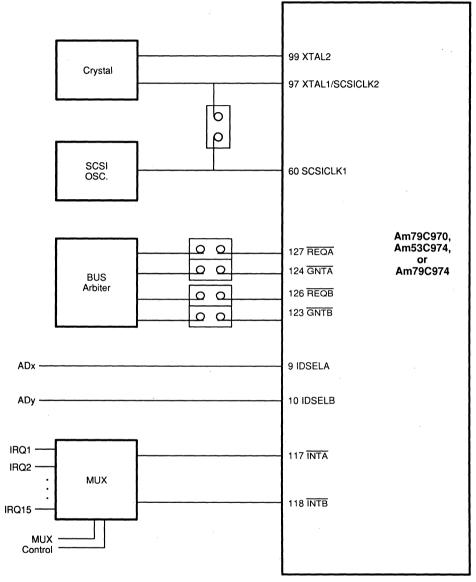

| Figure F-1. PCI Family Connections                                           |

# LIST OF TABLES

| Table 1. Crystal Specifications      | 52 |

|--------------------------------------|----|

| Table 2. Clock Drive Characteristics | 52 |

| Table 3. Bus Master Accesses         | 64 |

| Table 4. Bus Slave Accesses          | 65 |

| Table 5. EEPROM Contents             | 68 |

| Table 6. The DMA Registers           | 77 |

| Table 7. Summary of SCSI Commands    | 83 |

| Table 8. NAND Tree Configuration     | 90 |

# **RELATED PRODUCTS**

ş

| Part No.    | Description                                                                         |

|-------------|-------------------------------------------------------------------------------------|

| Am33C93A    | Synchronous SCSI Controller                                                         |

| Am386*      | High-Performance 32-Bit Microprocessor                                              |

| Am486™      | High-Performance 32-Bit Microprocessor                                              |

| Am53C94/96  | High-Performance SCSI Controller                                                    |

| Am53C974    | PCscsi <sup>™</sup> Bus Mastering Fast SCSI Controller for PCI Systems              |

| Am53CF94/96 | Enhanced Fast SCSI-2 Controller                                                     |

| Am79C90     | CMOS Local Area Network Controller for Ethernet (C-LANCE)                           |

| Am79C98     | Twisted-Pair Ethernet Transceiver (TPEX)                                            |

| Am79C100    | Twisted-Pair Ethernet Transceiver Plus (TPEX+)                                      |

| Am79C900    | Integrated Local Area Communications Controller™ (ILACC™)                           |

| Am79C940    | Media Acces Controller for Ethernet (MACE <sup>™</sup> )                            |

| Am79C960    | PCnet-ISA Single-Chip Ethernet Controller (for ISA bus)                             |

| Am79C961    | PCnet-ISA* Single-Chip Ethernet Controller (with Microsoft* Plug n' Play support)   |

| Am79C965    | PCnet-32 Single-Chip 32-Bit Ethernet Controller (for 386DX, 486 and VL buses)       |

| Am79C970    | PCnet-PCI Single-Chip Ethernet Controller for PCI Local Bus                         |

| Am79C981    | Integrated Multiport Repeater Plus™ (IMR+™)                                         |

| Am79C987    | Hardware Implemented Management Information Base <sup>™</sup> (HIMIB <sup>™</sup> ) |

| Am7990      | Local Area Network Controller for Ethernet (LANCE)                                  |

| Am7996      | IEEE 802.3/Ethernet/Cheapernet Tap Transceiver                                      |

| Am85C30     | Enhanced Serial Communication Controller                                            |

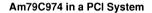

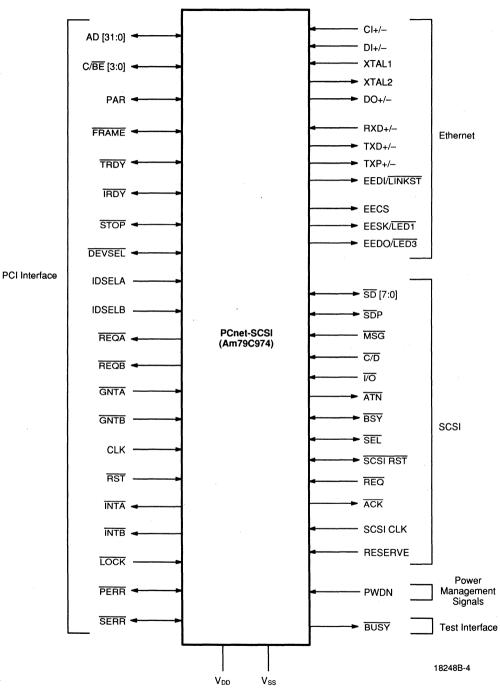

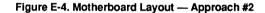

# **CONNECTION DIAGRAM**

Pin 1 is marked for orientation. RESERVE = Don't Connect.

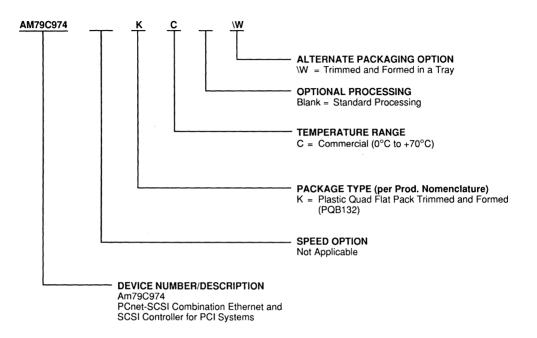

# **ORDERING INFORMATION**

# **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |  |  |  |  |  |  |

|--------------------|--|--|--|--|--|--|

| AM79C974 KC\W      |  |  |  |  |  |  |

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# PIN DESIGNATIONS Listed by Pin Number

| Pin No. | Pin Name          |

|---------|-------------------|---------|-------------------|---------|-------------------|---------|-------------------|

| 1       | V <sub>DD3B</sub> | 34      | PAR               | 67      | V <sub>SSB</sub>  | 100     | AV <sub>SS1</sub> |

| 2       | AD27              | 35      | C/BE1             | 68      | SD0               | 101     | DO-               |

| 3       | AD26              | 36      | AD15              | 69      | SD1               | 102     | DO+               |

| 4       | V <sub>SS3B</sub> | 37      | V <sub>SS3B</sub> | 70      | SD2               | 103     | AV <sub>DD1</sub> |

| 5       | AD25              | 38      | AD14              | 71      | SD3               | 104     | DI-               |

| 6       | AD24              | 39      | AD13              | 72      | V <sub>SSB</sub>  | 105     | DI+               |

| 7       | C/BE3             | 40      | AD12              | 73      | SD4               | 106     | CI–               |

| 8       | V <sub>DD</sub>   | 41      | AD11              | 74      | SD5               | 107     | CI+               |

| 9       | IDSELA            | 42      | AD10              | 75      | SD6               | 108     | AV <sub>DD2</sub> |

| 10      | IDSELB            | 43      | V <sub>SS3B</sub> | 76      | VDDB              | 109     | $DV_{DD}$         |

| 11      | V <sub>SS</sub>   | 44      | AD9               | 77      | SD7               | 110     | EEDO/LED3         |

| 12      | AD23              | 45      | AD8               | 78      | SDP               | 111     | EEDI/LNKST        |

| 13      | AD22              | 46      | V <sub>DD3B</sub> | 79      | DVss              | 112     | EESK/LED1         |

| 14      | V <sub>SS3B</sub> | 47      | C/BE0             | 80      | SEL               | 113     | DVss              |

| 15      | AD21              | 48      | AD7               | 81      | REQ               | 114     | EECS              |

| 16      | AD20              | 49      | AD6               | 82      | V <sub>SSB</sub>  | 115     | SLEEP             |

| 17      | V <sub>DD3B</sub> | 50      | V <sub>SS3B</sub> | 83      | ACK               | 116     | RESERVE           |

| 18      | AD19              | 51      | AD5               | 84      | DVDD              | 117     | INTA              |

| 19      | AD18              | 52      | AD4               | 85      | MSG               | 118     | INTB              |

| 20      | V <sub>SS3B</sub> | 53      | AD3               | 86      | C/D               | 119     | Vss               |

| 21      | AD17              | 54      | AD2               | 87      | 1/0               | 120     | RST               |

| 22      | AD16              | 55      | V <sub>SS3B</sub> | 88      | DVss              | 121     | CLK               |

| 23      | C/BE2             | 56      | AD1               | 89      | RXD-              | 122     | V <sub>DD</sub>   |

| 24      | FRAME             | 57      | AD0               | 90      | RXD+              | 123     | GNTB              |

| 25      | IRDY              | 58      | PWDN              | 91      | AV <sub>DD4</sub> | 124     | GNTA              |

| 26      | TRDY              | 59      | V <sub>DD</sub>   | 92      | TXP-              | 125     | Vss               |

| 27      | DEVSEL            | 60      | SCSICLK           | 93      | TXD-              | 126     | REQB              |

| 28      | STOP              | 61      | Vss               | 94      | TXP+              | 127     | REQA              |

| 29      | LOCK              | 62      | BUSY              | 95      | TXD+              | 128     | AD31              |

| 30      | Vss               | 63      | Vss               | 96      | AV <sub>DD3</sub> | 129     | AD30              |

| 31      | PERR              | 64      | BSY               | 97      | XTAL1             | 130     | V <sub>SS3B</sub> |

| 32      | SERR              | 65      | ATN               | 98      | AV <sub>SS2</sub> | 131     | AD29              |

| 33      | V <sub>DD3B</sub> | 66      | SCSI RST          | 99      | XTAL2             | 132     | AD28              |

# PIN DESIGNATIONS Listed by Pin Name

| Pin Name | Pin No. | Pin Name          | Pin No. | Pin Name | Pin No. | Pin Name          | Pin No. |

|----------|---------|-------------------|---------|----------|---------|-------------------|---------|

| ACK      | 83      | ATN               | 65      | GNTB     | 123     | STOP              | 28      |

| AD0      | 57      | AV <sub>DD1</sub> | 103     | IDSELA   | 9       | TRDY              | 26      |

| AD1      | 56      | AV <sub>DD2</sub> | 108     | IDSEL    | 10      | XTAL1             | 97      |

| AD2      | 54      | AV <sub>DD3</sub> | 96      | INTA     | 117     | XTAL2             | 99      |

| AD3      | 53      | AV <sub>DD4</sub> | 91      | INTB     | 118     | TXD-              | 93      |

| AD4      | 52      | AV <sub>SS1</sub> | 100     | 1/0      | 87      | TXD+              | 95      |

| AD5      | 51      | AV <sub>SS2</sub> | 98      | IRDY     | 25      | TXP-              | 92      |

| AD6      | 49      | BSY               | 64      | LOCK     | 29      | TXP+              | 94      |

| AD7      | 48      | BUSY              | 62      | MSG      | 85      | VDD               | 8       |

| AD8      | 45      | C/BE0             | 47      | PAR      | 34      | V <sub>DD</sub>   | 59      |

| AD9      | 44      | C/BE1             | 35      | PERR     | 31      | V <sub>DD</sub>   | 122     |

| AD10     | 42      | C/BE2             | 23      | PWDN     | 58      | VDDB              | 76      |

| AD11     | 41      | C/BE3             | 7       | REQ      | 81      | V <sub>DD3B</sub> | 1       |

| AD12     | 40      | C/D               | 86      | REQA     | 127     | V <sub>DD3B</sub> | 17      |

| AD13     | 39      | CLK               | 121     | REQB     | 126     | V <sub>DD3B</sub> | 33      |

| AD14     | 38      | CI-               | 106     | RESERVE  | 116     | V <sub>DD3B</sub> | 46      |

| AD15     | 36      | CI+               | 107     | RST      | 120     | Vss               | 11      |

| AD16     | 22      | DEVSEL            | 27      | RXD-     | 89      | Vss               | 30      |

| AD17     | 21      | DI-               | 104     | RXD+     | 90      | Vss               | 61      |

| AD18     | 19      | DI+               | 105     | SCSICLK  | 60      | Vss               | 63      |

| AD19     | 18      | DO-               | 101     | SCSI RST | 66      | Vss               | 119     |

| AD20     | 16      | DO+               | 102     | SD0      | 68      | Vss               | 125     |

| AD21     | 15      | DV <sub>DD</sub>  | 84      | SD1      | 69      | V <sub>SSB</sub>  | 67      |

| AD22     | 13      | DV <sub>DD</sub>  | 109     | SD2      | 70      | V <sub>SSB</sub>  | 72      |

| AD23     | 12      | DVss              | 79      | SD3      | 71      | V <sub>SSB</sub>  | 82      |

| AD24     | 6       | DVss              | 88      | SD4      | 73      | V <sub>SS3B</sub> | 4       |

| AD25     | 5       | DVss              | 113     | SD5      | 74      | V <sub>SS3B</sub> | 14      |

| AD26     | 3       | EECS              | 114     | SD6      | 75      | V <sub>SS3B</sub> | 20      |

| AD27     | 2       | EEDI/LNKST        | 111     | SD7      | 77      | V <sub>SS3B</sub> | 37      |

| AD28     | 132     | EEDO/LED3         | 110     | SDP      | 78      | V <sub>SS3B</sub> | 43      |

| AD29     | 131     | EESK/LED1         | 112     | SEL      | 80      | V <sub>SS3B</sub> | 50      |

| AD30     | 129     | FRAME             | 24      | SERR     | 32      | V <sub>SS3B</sub> | 55      |

| AD31     | 128     | GNTA              | 124     | SLEEP    | 115     | V <sub>SS3B</sub> | 130     |

# **PIN DESIGNATIONS**

# **Quick Reference Pin Description**

| Pin Name                                  | Description                                          | Туре | Driver | # Pins |

|-------------------------------------------|------------------------------------------------------|------|--------|--------|

| PCI Bus Interface                         |                                                      |      |        |        |

| AD[31:00]                                 | D[31:00] Address/Data Bus                            |      | TS3    | 32     |

| C/BE[3:0]                                 |                                                      |      | TS3    | 4      |

| CLK                                       | Bus Clock                                            | 1    | NA     | 1      |

| DEVSEL                                    | Device Select                                        | 10   | TS6    | 1      |

| FRAME                                     | Cycle Frame                                          | 10   | TS6    | 1      |

| GNTA, GNTB                                | Bus Grant                                            | I    | NA     | 1      |

| IDSELA, IDSELB                            | Initialization Device Select                         | I    | ns     | 1      |

| ÎNTĂ, ÎNTB                                | Interrupt                                            | 10   | OD6    | 1      |

| IRDY                                      | Initiator Ready                                      | IO   | TS6    | 1 -    |

| LOCK                                      | Bus Lock                                             | 10   | TS6    | 1      |

| PAR                                       | Parity                                               | IO   | TS6    | 1      |

| PERR                                      | Parity Error                                         | IO   | TS6    | 1      |

| REQA, REQB                                | Bus Request                                          | IO   | TS3    | 1      |

| RST                                       | Reset                                                | 1    | NA     | 1      |

| SERR                                      | System Error                                         | 10   | OD6    | 1      |

| STOP                                      | Stop                                                 | IO   | TS6    | 1      |

| TRDY                                      | Target Ready                                         | IO   | TS6    | 1      |

| ETHERNET SPEC                             | IFIC                                                 |      |        |        |

| Board Interface                           |                                                      |      |        |        |

| EECS                                      |                                                      |      | O8     | 1      |

| EEDI/LNKST                                | DI/LNKST Microwire Serial EEPROM Data In/Link Status |      | LED    | 1      |

| EEDO/LED3                                 |                                                      |      | LED    | 1      |

| ESK/LED1 Microwire Serial PROM Clock/LED1 |                                                      | 10   | LED    | 1      |

| SLEEP                                     | Sleep Mode                                           | 1    | NA     | 1      |

| XTAL1-2                                   | Crystal Input/Output                                 | 10   | NA     | 2      |

| Attachment Unit I                         | nterface (AUI)                                       |      |        |        |

| CI+/CI-                                   | AUI Collision Differential Pair                      | 1    | NA     | 2      |

| DI+/DI-                                   | AUI Data In Differential Pair                        | 1    | NA     | 2      |

| DO+/DO-                                   | AUI Data Out Differential Pair                       | 0    | DO     | 2      |

| 10BASE-T Interfac                         | Ce                                                   |      |        |        |

| RXD+/RXD-                                 | Receive Differential Pair                            | 1    | NA     | 2      |

| TXD+/TXD- Transmit Differential Pair      |                                                      | 0    | TDO    | 2      |

| TXP+/TXP-                                 | Transmit Pre-distortion Differential Pair            | 0    | TPO    | 2      |

| LNKST/EEDI                                | Link Status/Microwire Serial EEPROM Data In          | 0    | LED    | 1      |

# **PIN DESIGNATIONS (continued)**

# Quick Reference Pin Description

| Pin Name                             | Description              | Туре | Driver | # Pins |

|--------------------------------------|--------------------------|------|--------|--------|

| SCSI SPECIFIC                        | ;                        |      |        |        |

| SCSI Interface                       |                          |      |        |        |

| SD [7:0]                             | SCSI Data                | 10   | OD48   | 8      |

| SDP                                  | SCSI Data Parity         | 10   | OD48   | 1      |

| MSG                                  | Message                  | 1    |        | 1      |

| C/D                                  | Command/Data             | 1    |        | 1      |

| 1/0                                  | Input/Output             | l    |        | 1      |

| ATN                                  | Attention                | 0    | OD48   | 1      |

| BSY                                  | Busy                     | 10   | OD48   | 1      |

| SEL                                  | Select IO OD48           |      | OD48   | 1      |

| SCSI RST                             | SCSI Bus Reset           | 10   | OD48   | 1      |

| REQ                                  | Request                  | l    |        | 1      |

| ACK                                  | Acknowledge              | 0    | OD48   | 1      |

| Miscellaneous                        |                          |      |        |        |

| SCSI CLK                             | SCSI Core Clock          | I    |        | 1      |

| RESERVE                              | Reserved, DO NOT CONNECT | I    |        | 1      |

| Power Manage                         | ment                     |      |        |        |

| PWDN                                 | Power Down Indicator     | 1    |        | 1      |

| Test Interface                       |                          |      | -      |        |

| BUSY                                 | NAND Tree Test Output    | 0    | O3     | 1      |

| Power Supplies                       | 8                        |      |        |        |

| AVDD                                 | Analog Power             | Р    | NA     | 4      |

| AV <sub>SS</sub>                     | Analog Ground            | Р    | NA     | 2      |

| V <sub>DD</sub>                      | Digital Power            | Р    | NA     | 6      |

| V <sub>SS</sub>                      | Digital Ground           | Р    | NA     | 12     |

| V <sub>DDB</sub> , V <sub>DD3B</sub> | I/O Buffer Power         | Р    | NA     | 4      |

| V <sub>SSB</sub> , V <sub>SS3B</sub> | I/O Buffer Ground        | Р    | NA     | 8      |

# Listed by Driver Type

The following table describes the various types of drivers that are implemented in the PCnet-SCSI controller. Current is given as milliamperes:

| Name | Туре       | I <sub>OL</sub> (mA) | I <sub>он</sub> (mA) | pF |

|------|------------|----------------------|----------------------|----|

| TS3  | Tri-State™ | 3                    | -0.4                 | 50 |

| TS6  | Tri-State  | 6                    | -0.4                 | 50 |

| O3   | Totem Pole | 3                    | -0.4                 | 50 |

| O6   | Totem Pole | 6                    | -0.4                 | 50 |

| O8   | Totem Pole | 8                    | -0.4                 | 50 |

| OD6  | Open Drain | 6                    | NA                   | 50 |

| OD48 | Open Drain | 48                   | NA                   | -  |

| LED  | LED        | 12                   | -0.4                 | 50 |

# LOGIC SYMBOL

### **PIN DESCRIPTION**

### PCI Bus Interface

### AD[31:00] Address and Data Input/Output, Active High

These signals are multiplexed on the same PCI pins. During the first clock of a transaction AD[31:00] contain the physical byte address (32 bits). During the subsequent clocks AD[31:00] contain data. Byte ordering is little endian by default. AD[07:00] are defined as least significant byte and AD[31:24] are defined as the most significant byte. For FIFO data transfers, the PCnet-SCSI controller can be programmed for big endian byte ordering. See CSR3, bit 2 (BSWP) for more details.

During the address phase of the transaction, when the PCnet-SCSI controller is a bus master, AD[31:2] will address the active DWORD (double-word). The PCnet-SCSI controller always drives AD[1:0] to '00' during the address phase indicating linear burst order. When the PCnet-SCSI controller is not a bus master, the AD[31:00] lines are continuously monitored to determine if an address match exists for I/O slave transfers.

During the data phase of the transaction, AD[31:00] are driven by the PCnet-SCSI controller when performing bus master writes and slave read operations. Data on AD[31:00] is latched by the PCnet-SCSI controller when performing bus master reads and slave write operations.

When  $\overline{\text{RST}}$  is active, AD[31:0] are inputs for NAND tree testing.

### C/BE [3:0] Bus Command and Byte Enables Input/Output, Active Low

These signals are multiplexed on the same PCI pins. During the address phase of the transaction, C/BE[3:0] define the bus command. During the data phase C/BE[3:0] are used as Byte Enables. The Byte Enables define which physical byte lanes carry meaningful data. C/BE0 applies to byte 0 (AD[07:00]) and C/BE3 applies to byte 3 (AD[31:24]). The function of the Byte Enables is independent of the byte ordering mode (CSR3, bit 2).

When  $\overline{\text{RST}}$  is active, C/BE[3:0] are inputs for NAND tree testing.

####

### Input

This signal provides timing for all the transactions on the PCI bus and all PCI devices on the bus including the PCnet-SCSI controller. All bus signals are sampled on the rising edge of CLK and all parameters are defined with respect to this edge. The PCnet-SCSI controller operates over a range of 0 to 33 MHz.

When  $\overrightarrow{\text{RST}}$  is active, CLK is an input for NAND tree testing.

### DEVSEL

#### Device Select Input/Output, Active Low

This signal when actively driven by the PCnet-SCSI controller as a slave device signals to the master device that the PCnet-SCSI controller has decoded its address as the target of the current access. As an input it indicates whether any device on the bus has been selected.

When  $\overline{\text{RST}}$  is active,  $\overline{\text{DEVSEL}}$  is an input for NAND tree testing.

### FRAME

#### Cycle Frame Input/Output, Active Low

This signal is driven by the PCnet-SCSI controller when it is the bus master to indicate the beginning and duration of the access. FRAME is asserted to indicate a bus transaction is beginning. FRAME is asserted while data transfers continue. FRAME is deasserted when the transaction is in the final data phase.

When RST is active, FRAME is an input for NAND tree testing.

### GNTA

# Bus Grant

Input, Active Low

This signal indicates that the access to the bus has been granted to the Am79C974's SCSI controller.

When  $\overline{\text{RST}}$  is active,  $\overline{\text{GNTA}}$  is an input for NAND tree testing.

### GNTB Bus Grant Input, Active Low

This signal indicates that the access to the bus has been granted to the Am79C974's Ethernet controller. The Am79C974 controller supports bus parking. When the PCI bus is idle and the system arbiter asserts GNT without an active REQ from the Am79C974 controller, the Am79C974 will actively drive the AD, C/BE and PAR lines.

When  $\overrightarrow{\text{RST}}$  is active,  $\overrightarrow{\text{GNTB}}$  is an input for NAND tree testing.

# IDSELA

#### Initialization Device Select Input, Active High

This signal is used as a SCSI controller selection for the Am79C974 in lieu of the 24 address lines during configuration read and write transaction.

When  $\overline{\text{RST}}$  is active, IDSELA is an input for NAND tree testing.

# IDSELB

### Initialization Device Select Input, Active High

This signal is used as an Ethernet controller selection for the PCnet-SCSI controller during configuration read and write transaction.

When RST is active, IDSELB is an input for NAND tree testing.

# INTA

#### Interrupt Request Output, Active Low

This signal combines the interrupt requests from both the SCSI DMA engine and the SCSI core. The interrupt source can be determined by reading the SCSI DMA Status Register. It is cleared when the Status Register is read.

When  $\overline{\text{RST}}$  is active,  $\overline{\text{INTA}}$  is an input for NAND tree testing. This is the only time  $\overline{\text{INTA}}$  is an input.

### INTB Interrupt Request Input/Output, Active Low

An asynchronous attention signal which indicates that one or more of the following status flags is set: BABL, MISS, MERR, RINT, IDON, RCVCCO, RPCO, JAB, MPCO, or TXSTRT. Each status flag has a mask bit which allows for suppression of INTB assertion. The flags have the following meaning:

| BABL   | Babble                           |  |

|--------|----------------------------------|--|

| RCVCCO | Receive Collision Count Overflow |  |

| RPCO   | Runt Packet Count Overflow       |  |

| JAB    | Jabber                           |  |

| MISS   | Missed Frame                     |  |

| MERR   | Memory Error                     |  |

| MPCO   | Missed Packet Count Overflow     |  |

| RINT   | Receive Interrupt                |  |

| IDON   | Initialization Done              |  |

| TXSTRT | Transmit Start                   |  |

When  $\overrightarrow{\text{RST}}$  is active,  $\overrightarrow{\text{INTB}}$  is an input for NAND tree testing. This is the only time  $\overrightarrow{\text{INTB}}$  is an input.

### IRDY Initiator Ready Input/Output, Active Low

This signal indicates PCnet-SCSI controller's ability, as a master device, to complete the current data phase of the transaction. IRDY is used in conjunction with the TRDY. A data phase is completed on any clock when both IRDY and TRDY are asserted. During a write IRDY indicates that valid data is present on AD[31:00]. During a read IRDY indicates that data is accepted by the PCnet-SCSI controller as a bus master. Wait states are inserted until both IRDY and TRDY are asserted simultaneously.

When  $\overline{\text{RST}}$  is active,  $\overline{\text{IRDY}}$  is an input for NAND tree testing.

# LOCK

# Lock

Input, Active Low

LOCK is used by the current bus master to indicate an atomic operation that may require multiple transfers.

As a slave device, the PCnet-SCSI controller can be locked by any master device. When another master attempts to access the PCnet-SCSI while it is locked, the PCnet-SCSI controller will respond by asserting DEVSEL and STOP with TRDY deasserted (PCI retry).

The PCnet-SCSI controller will never assert  $\overline{\text{LOCK}}$  as a master.

When  $\overrightarrow{\text{RST}}$  is active,  $\overrightarrow{\text{LOCK}}$  is an input for NAND tree testing.

# PAR

# Parity

# Input/Output, Active High

Parity is even parity across AD[31:00] and C/BE[3:0]. When the PCnet-SCSI controller is a bus master, it write data H\_RESET (HARDW) ses. When for a minimum of 30

generates parity during the address and write data phases. It checks parity during read data phases. When the PCnet-SCSI controller operates in slave mode and is the target of the current cycle, it generates parity during read data phases. It checks parity during address and write data phases.

When  $\overrightarrow{\text{RST}}$  is active, PAR is an input for NAND tree testing.

### PERR

#### Parity Error Input/Output, Active Low, Open Drain

This signal is asserted for one CLK by the PCnet-SCSI controller when it checks for parity detects an error during any data phase when its AD[31:00] lines are inputs. The PERR pin is only active when PERREN (bit 6) in the PCI command register is set.

The PCnet-SCSI controller monitors the PERR input during a bus master write cycle. It will assert the Data Parity Reported bit in the Status register of the Configuration Space when a parity error is reported by the target device.

When RST is active, PERR is an input for NAND tree testing.

### REQA

#### Bus Request Input/Output, Active Low

The Am79C974's SCSI controller asserts REQA pin as a signal that it wishes to become a bus master. Once asserted, REQA remains active until GNT has become active.

When  $\overline{RST}$  is active,  $\overline{REQA}$  is an input for NAND tree testing. This is the only time  $\overline{REQA}$  is an input.

### REQB

#### Bus Request Input/Output, Active Low

The Am79C974's Ethernet controller asserts REQB pin as a signal that it wishes to become a bus master. Once asserted, REQB remains active until GNT has become active, independent of subsequent assertion of SLEEP or setting of the STOP bit or access to the S\_RESET port (offset 14h).

When  $\overrightarrow{\text{RST}}$  is active,  $\overrightarrow{\text{REQB}}$  is an input for NAND tree testing. This is the only time  $\overrightarrow{\text{REQB}}$  is an input.

# RST

#### Reset Input, Active Low

When RST is asserted low, then the PCnet-SCSI controller performs an internal system reset of the type H\_RESET (HARDWARE\_RESET). RST must be held for a minimum of 30 CLK periods. While in the H\_RE-SET state, the PCnet-SCSI controller will disable or deassert all outputs. RST may be asynchronous to the CLK when asserted or deasserted. It is recommended that the deassertion be synchronous to guarantee a clean and bounce free edge.

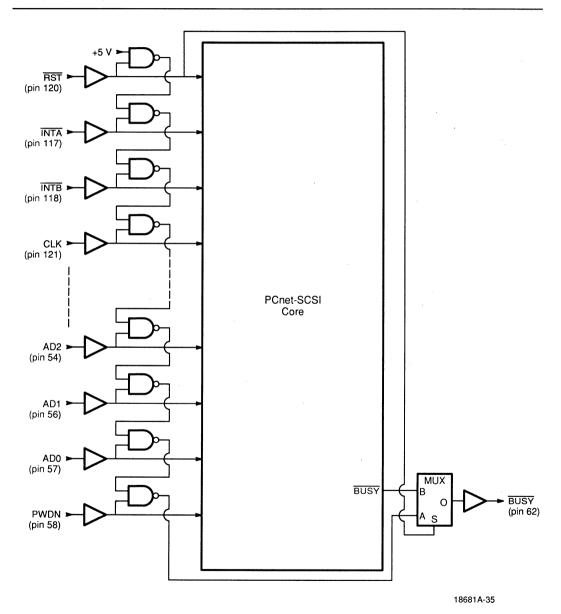

When  $\overline{\text{RST}}$  is active, NAND tree testing is enabled. All PCI interface pins are in input mode. The result of the NAND tree testing can be observed on the  $\overline{\text{BUSY}}$  output (pin 62).

### SERR

#### System Error

### Input/Output, Active Low, Open Drain

This signal is asserted for one CLK by the PCnet-SCSI controller when it detects a parity error during the address phase when its AD[31:00] lines are inputs.

The SERR pin is only active when SERREN (bit 8) and PERREN (bit 6) in the PCI command register are set.

When  $\overline{\text{RST}}$  is active,  $\overline{\text{SERR}}$  is an input for NAND tree testing.

# STOP

### Stop

### Input/Output, Active Low

In the slave role, the PCnet-SCSI controller drives the STOP signal to inform the bus master to stop the current transaction. In the bus master role, the PCnet-SCSI controller receives the STOP signal and stops the current transaction.

When  $\overline{\text{RST}}$  is active,  $\overline{\text{STOP}}$  is an input for NAND tree testing.

### TRDY

#### Target Ready Input/Output, Active Low

This signal indicates that the PCnet-SCSI controller's ability as a selected device to complete the current data phase of the transaction. TRDY is used in conjunction with the IRDY. A data phase is completed on any clock both TRDY and IRDY are asserted. During a read TRDY indicates that valid data is present on AD[31:00]. During a write, TRDY indicates that data has been accepted. Wait states are inserted until both IRDY and TRDY are asserted simultaneously.

When  $\overline{\text{RST}}$  is active,  $\overline{\text{TRDY}}$  is an input for NAND tree testing.

# Ethernet Controller Pins Board Interface

#### LED1 LED1 Output

This pin is shared with the EESK function. As LED1, the function and polarity of this pin are programmable through BCR5. By default, LED1 is active LOW and it indicates receive activity on the network. The LED1 output from the PCnet-SCSI controller is capable of sinking the 12 mA of current necessary to drive an LED directly.

The LED1 pin is also used during EEPROM Auto-detection to determine whether or not an EEPROM is present at the PCnet-SCSI controller Microwire interface. At the trailing edge of the RST pin, LED1 is sampled to determine the value of the EEDET bit in BCR19. A sampled HIGH value means that an EEPROM is present, and EEDET will be set to ONE. A sampled LOW value means that an EEPROM is not present, and EEDET will be set to ZERO. See the EEPROM Auto-detection section for more details.

If no LED circuit is to be attached to this pin, then a pull up or pull down resistor must be attached instead, in order to resolve the EEDET setting.

### LED3 LED3 Output

This pin is shared with the EEDO function of the Microwire serial EEPROM interface. When functioning as LED3, the signal on this pin is programmable through BCR7. By default, LED3 is active LOW and it indicates transmit activity on the network. Special attention must be given to the external circuitry attached to this pin. If an LED circuit were directly attached to this pin, it would create an IOL requirement that could not be met by the serial EEPROM that would also be attached to this pin.

Therefore, if this pin is to be used as an additional LED output while an EEPROM is used in the system, then buffering is required between the LED3 pin and the LED circuit. If no EEPROM is included in the system design, then the LED3 signal may be directly connected to an LED without buffering. The LED3 output from the PCnet-SCSI controller is capable of sinking the 12 mA of details regarding LED connection, see the section on LEDs.

### LNKST LINK Status Output

This pin provides 12 mA for driving an LED. By default, it indicates an active link connection on the 10BASE-T interface. This pin can also be programmed to indicate other network status (see BCR4). The LNKST pin polarity is programmable, but by default, it is active LOW. Note that this pin is multiplexed with the EEDI function.

# SLEEP

#### Sleep Input

nput

When SLEEP is asserted (active LOW), the PCnet-SCSI controller performs an internal system reset of the S\_RESET type and then proceeds into a power savings mode. (The reset operation caused by SLEEP assertion will not affect BCR registers.) The PCI interface section is not effected by SLEEP. In particular, access to the PCI configuration space remains possible. None of the configuration registers will be reset by SLEEP. All I/O accesses to the PCnet-SCSI controller will result in a PCI target abort response. The PCnet-SCSI controller will not assert REQ while in sleep mode. When SLEEP is asserted, all non-PCI interface outputs will be placed in their normal S RESET condition. All non-PCI interface inputs will be ignored except for the SLEEP pin itself. De-assertion of SLEEP results in wake-up. The system must refrain from starting the network operations of the PCnet-SCSI device for 0.5 seconds following the deassertion of the SLEEP signal in order to allow internal analog circuits to stabilize.

Both CLK and XTAL1 inputs must have valid clock signals present in order for the SLEEP command to take effect. If SLEEP is asserted while REQ is asserted, then the PCnet-SCSI controller will wait for the assertion of GNT. When GNT is asserted, the REQ signal will be deasserted and then the PCnet-SCSI controller will proceed to the power savings mode.

The SLEEP pin should not be asserted during power supply ramp-up. If it is desired that SLEEP be asserted at power up time, then the system must delay the assertion of SLEEP until three CLK cycles after the completion of a valid pin RST operation.

The SLEEP pin does not affect the SCSI section.

### XTAL1 Crystal Oscillator Input Input

### XTAL2 Crystal Oscillator Output Output

The crystal frequency determines the network data rate. The PCnet-SCSI controller supports the use of quartz crystals to generate a 20 MHz frequency compatible with the ISO 8802-3 (IEEE/ANSI 802.3) network frequency tolerance and jitter specifications. See the section External Crystal Characteristics (in section Manchester Encoder/Decoder) for more detail.

The network data rate is one-half of the crystal frequency. XTAL1 may alternatively be driven using an external CMOS level source, in which case XTAL2 must be left unconnected. Note that when the PCnet-SCSI controller is in coma mode, there is an internal 22 K $\Omega$  resistor from XTAL1 to ground. If an external source drives XTAL1, some power will be consumed driving this resistor. If XTAL1 is driven LOW at this time power consumption will be minimized. In this case, XTAL1 must remain active for at least 30 cycles after the assertion of SLEEP and deassertion of REQ.

### **Microwire EEPROM Interface**

### EESK EEPROM Serial Clock Input/Output

The EESK signal is used to access the external ISO 8802-3 (IEEE/ANSI 802.3) address PROM. This pin is designed to directly interface to a serial EEPROM that uses the Microwire interface protocol. EESK is connected to the Microwire EEPROM's Clock pin. It is controlled by either the PCnet-SCSI controller directly during a read of the entire EEPROM, or indirectly by the host system by writing to BCR19, bit 1.

The EESK pin is also used during EEPROM Auto-detection to determine whether or not an EEPROM is present at the PCnet-SCSI controller Microwire interface. At the trailing edge of the RST signal, LED1 is sampled to determine the value of the EEDET bit in BCR19. A sampled HIGH value means that an EEPROM is present, and EEDET will be set to ONE. A sampled LOW value means that an EEPROM is not present, and EEDET will be set to ZERO. See the EEPROM Auto-detection section for more details.

EESK is shared with the LED1 function. If no LED circuit is to be attached to this pin, then a pull up or pull down resistor must be attached instead, in order to resolve the EEDET setting.

#### EEDO EEPROM Data Out Input

The EEDO signal is used to access the external ISO 8802-3 (IEEE/ANSI 802.3) address PROM. This pin is designed to directly interface to a serial EEPROM that uses the Microwire interface protocol. EEDO is connected to the Microwire EEPROM's Data Output pin. It is controlled by the EEPROM during reads. It may be read by the host system by reading BCR19 bit 0.

EEDO is shared with the LED3 function.

### EECS EEPROM Chip Select Output

The function of the EECS signal is to indicate to the Microwire EEPROM device that it is being accessed. The EECS signal is active high. It is controlled by either the PCnet-SCSI controller during command portions of a read of the entire EEPROM, or indirectly by the host system by writing to BCR19 bit 2.

### EEDI EEPROM Data In Output

The EEDI signal is used to access the external ISO 8802-3 (IEEE/ANSI 802.3) address PROM. EEDI functions as an output. This pin is designed to directly interface to a serial EEPROM that uses the Microwire interface protocol. EEDI is connected to the Microwire EEPROM's Data Input pin. It is controlled by either the PCnet-SCSI controller during command portions of a read of the entire EEPROM, or indirectly by the host system by writing to BCR19 bit 0.

EEDI is shared with the LNKST function.

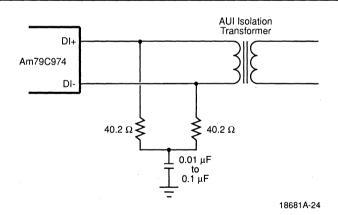

### Attachment Unit Interface

### Cl± Collision In Input

A differential input pair signaling the PCnet-SCSI controller that a collision has been detected on the network media, indicated by the Cl± inputs being driven with a 10 MHz pattern of sufficient amplitude and pulse width to meet ISO 8802-3 (IEEE/ANSI 802.3) standards. Operates at pseudo ECL levels.

# DI± Data In

### Input

A differential input pair to the PCnet-SCSI controller carrying Manchester encoded data from the network. Operates at pseudo ECL levels.

# DO± Data Out

# Output

A differential output pair from the PCnet-SCSI controller for transmitting Manchester encoded data to the network. Operates at pseudo ECL levels.

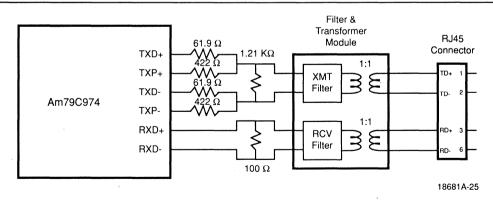

# Twisted-Pair Interface

RXD± 10BASE-T Receive Data Input

10BASE-T port differential receivers.

# **TXD**±

10BASE-T Transmit Data Output

10BASE-T port differential drivers.

# **TXP**±

### 10BASE-T Pre-Distortion Control Output

These outputs provide transmit pre-distortion control in conjunction with the 10BASE-T port differential drivers.

# SCSI Controller Pins

SCSI Bus Interface Signals SCSI Bus Pins

**SD** [7:0] SCSI Data Input/Output, Active Low, Open Drain/Active Negation, Schmitt Trigger These pins are defined as bi-directional SCSI data bus.

# SDP

SCSI Data Parity Input/Output, Active Low, Open Drain/Active Negation, Schmitt Trigger This pin is defined as bi-directional SCSI data parity.

# MSG

### Message

Input, Active Low, Schmitt Trigger It is a Schmitt trigger input in the initiator mode.

# C/D

Command/Data Input, Schmitt Trigger It is a Schmitt trigger input in the initiator mode.

# Ī/O

Input/Output Input, Schmitt Trigger It is a Schmitt trigger input in the initiator mode.

# ATN

#### Attention Output. Active Low

This signal is a 48 mA output in the initiator mode. This signal will be asserted when the device detects a parity error; also, it can be asserted via certain commands.

# BSY

# Busy

# Input/Output, Active Low, Schmitt Trigger, Open Drain

As a SCSI input signal it has a Schmitt trigger and as an output signal it has a 48 mA drive.

## SEL

# Select

# Input/Output, Active Low, Schmitt Trigger, Open Drain

As a SCSI input signal it has a Schmitt trigger and as an output signal it has a 48 mA drive.

# SCSI RST

#### Reset

Input/Output, Active Low, Schmitt Trigger, Open Drain

As a SCSI input signal it has a Schmitt trigger and as an output signal it has a 48 mA drive.

# REQ

### Request

### Input, Active Low, Schmitt Trigger

This is a SCSI input signal with a Schmitt trigger in the initiator mode.

# ACK

### Acknowledge

**Output, Active Low, Open Drain/Active Negation** This is a SCSI output signal with a 48 mA drive in the initiator mode.

# SCSI Clock

### Input

The SCSI clock signal is used to generate all internal device timings. The maximum frequency of this input is 40 MHz and a minimum of 10 MHz is required to maintain the SCSI bus timings.

### Note:

A 40 MHz clock must be supplied at this input to achieve 10 Mbyte/s Synchronous Fast SCSI transfers.

### PWDN

#### Power Down Indicator Input. Active High

This signal, when asserted, sets the PWDN status bit in the DMA status register and sends an interrupt to the host.

### **Test Interface**

# BUSY

#### NAND Tree Out Output. Active Low

This signal is logically equivalent to the SCSI bus signal BSY. It is duplicated so that external logic can be connected to monitor SCSI bus activity.

The results of the NAND tree testing can be observed on the  $\overline{\text{BUSY}}$  pin where  $\overline{\text{RST}}$  is asserted; otherwise,  $\overline{\text{BUSY}}$  will reflect the state of the SCSI Bus Signal line  $\overline{\text{BSY}}$  (pin 64).

# Miscellaneous

# RESERVED

### Reserved\_DO NOT CONNECT Input

This pin (#116) is reserved for internal test logic. It **MUST NOT BE CONNECTED** to anything for proper chip operation. It's use is subject to change in future products.

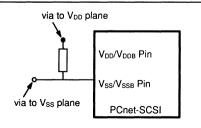

### **Power Supply Pins**

## **Analog Power Supply Pins**

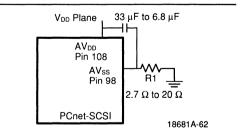

### AV<sub>DD</sub> Analog Power (4 Pins) Power

There are four analog +5 V supply pins. Special attention should be paid to the printed circuit board layout to avoid excessive noise on these lines. Refer to Appendix C and the *Technical Manual* (PID #18738A) for details.

### AVss

### Analog Ground (2 Pins) Power

There are two analog ground pins. Special attention should be paid to the printed circuit board layout to avoid excessive noise on these lines. Refer to Appendix C and the *Technical Manual* (PID #18738A) for details.

# **Digital Power Supply Pins**

#### V<sub>DD</sub> Digital Power (6 Pins) Power

There are 6 power supply pins that are used by the internal digital circuitry. All  $V_{DD}$  pins must be connected to a +5 V supply.

### VDDB

### I/O Buffer Power (4 Pins) Power

There are 4 power supply pins that are used by the PCI bus Input/Output buffer drivers. All  $V_{\text{DDB}}$  pins must be connected to a +5 V supply.

### Vss

#### Digital Ground (12 Pins) Ground

There are 12 ground pins that are used by the internal digital circuitry.

### V<sub>SSB</sub> I/O Buffer Ground (8 Pins)

### Ground

There are 8 ground pins that are used by the PCI bus Input/Output buffer drivers.

# **BASIC FUNCTIONS**

### **System Bus Interface Function**

During normal operations the Am79C974 operates as a bus master with a few slave I/O accesses for status and control functions.

The Ethernet controller is initialized through a combination of PCI Configuration Space accesses, I/O space Bus Slave accesses, Memory Space Bus Master accesses, and optional reads of an external serial EEPROM. The EEPROM is read through the Microwire interface either automatically by the Am79C974 or indirectly by a series of bus slave accesses to one of the Ethernet Bus Configuration Registers (BCRs). The EEPROM normally contains the ISO 8802-3 (IEEE/ ANSI 802.3) Ethernet node address and data to be loaded into some of the Ethernet BCRs.

The SCSI controller is initialized by bus slave writes to SCSI Core and SCSI DMA registers.

### Software Interface

The Am79C794 uses four address spaces: Ethernet PCI configuration space, SCSI PCI configuration space, I/O space, and memory space.

SCSI PCI configuration space is selected when the IDSELA pin is active. Ethernet PCI configuration space is selected when the IDSELB pin is active. The way that IDSELA and IDSELB are controlled depends on external hardware. Section 3.6.4.1 of the PCI Specification recommends two methods of generating configuration cycles called Configuration Mechanism #1 and Configuration Mechanism #2.

The PCI Configuration Spaces are used by system software to identify the SCSI and Ethernet controllers and to set up device configuration without the use of jumpers. Certain PCI configuration registers have read-only information about the devices resource requirements. Other registers are used as mail boxes that system configuration software uses to inform other software what resources have been allocated to the device. The only PCI Configuration Registers that affect the operation of the Am79C794 are the SCSI and Ethernet Base Address Registers, which are found at offset 10h in each of the two configuration spaces, and the Command Registers at offset 4. Writing to these registers establishes the base address of the SCSI I/O space and the base address of the Ethernet I/O space.

The SCSI controller registers occupy 96 bytes of I/O space that starts on whatever 128-byte boundary that is programmed into the Base Address Register at offset 10h in the SCSI PCI Configuration Space. The Ethernet controller registers occupy 32 bytes of I/O space that starts on whatever 32-byte boundary that is programmed into the Base Address Register at offset 10h in the Ethernet PCI Configuration Space. These

registers are used to set up controller operating modes, to enable or disable various features, to start certain operations, and to monitor operating status.

In addition to the registers in the I/O space, the Ethernet controller uses certain data structures that are set up (typically by the host computer) in normal memory space. These data structures are (1) the initialization block that contains configuration data that the Ethernet controller automatically loads into its Configuration and Status Registers (CSRs), (2) the Receive and Transmit Descriptor Rings, that contain pointers to receive and transmit buffers and status and control information about these buffers, and (3) the receive and transmit buffers. The Ethernet controller uses bus master accesses to read the locations of the buffers, to store frames received from the network into the receive buffers, and to transmit the contents of the transmit buffers.

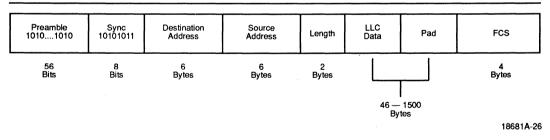

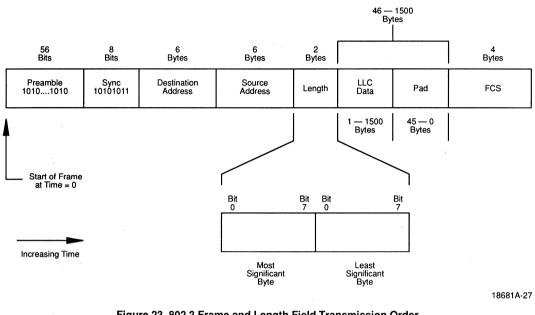

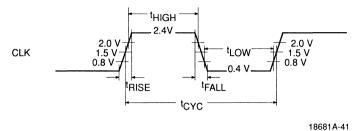

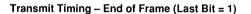

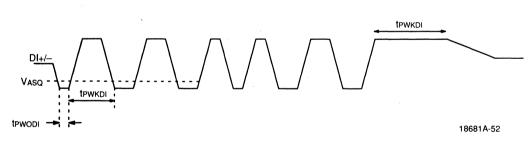

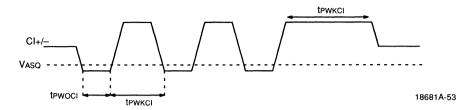

### **Ethernet Interfaces**