### **Data Communication Products**

1992 Data Book/Handbook

Advanced Micro Devices

AMD's Marketing Communications Department specifies environmentally sound agricultural inks and recycled papers, making this book highly recyclable.

# **Data Communication Products**

١

1992 Data Book/Handbook

ADVANCED MICRO DEVICES 🖉

#### © 1991 Advanced Micro Devices, Inc.

#### Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### Trademarks

AMD is a registered trademark of Advanced Micro Devices, Inc.

Am386 is a trademark of Advanced Micro Devices, Inc.

Ethernet is a registered trademark of Xerox Corporation.

IBM and PC/AT are registered trademarks of International Business Machines Corporation.

LocalTalk is a trademark of Apple Computer, Inc.

MULTIBUS is a trademark of Intel Corporation.

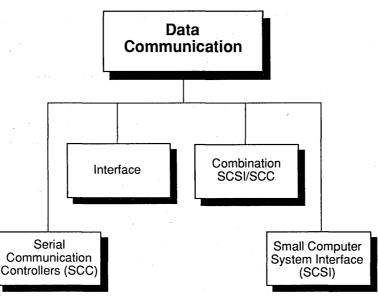

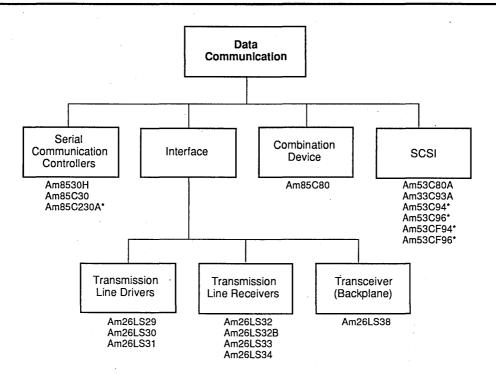

Advanced Micro Devices offers a complete line of Data Communications products. Optimized for industry standard protocols, these products allow CPU hosts to communicate with peripherals. Our Data Communication product family includes Small Computer System Interface (SCSI) Controllers, Enhanced Serial Communication Controllers (ESCC), Combination devices containing both SCSI and SCC blocks, and Interface Line Drivers and Receivers.

AMD's sub-micron CMOS process technology, advanced packaging programs and continued commitment to industry leading quality and reliability ensures that you are designing with high-value added ICs.

Remember, our partnership helps you gain and keep the competitive edge. We are not your competition.

Fud J. Roeder

Fred J. Roeder Vice President Standard Products Division

### **TABLE OF CONTENTS**

| Chapter 1  | Small Computer System Interface (SCSI) Controllers       1–1         Am33C93A Enhanced SCSI-Bus Interface Controller       1–3         Am53C80A SCSI Interface Controller       1–52         Am53C94/Am53C96 High Performance SCSI Controller       1–85                                                                                                                                                                                                                                |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

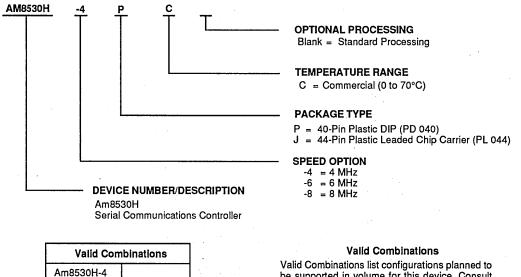

| Chapter 2  | Serial Communication Controllers       2–1         Am8530H Serial Communication Controller       2–3         Am85C30 Enhanced Serial Communications Controller       2–34         Am85C230A Enhanced Serial Communications Controller       2–82         with LocalTalk Support (ESCC/LT)       2–82         Interfacing the Am8530H and Am85C30 Serial Communications       2–83         Controllers to the 80186 Microprocessor Application Note       2–83                           |

| Chapter 3  | Combination SCSI/SCC Controller       3–1         Am85C80 Combined SCSI Controller and Serial Communication       3–3         Controller       3–3                                                                                                                                                                                                                                                                                                                                      |

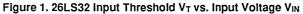

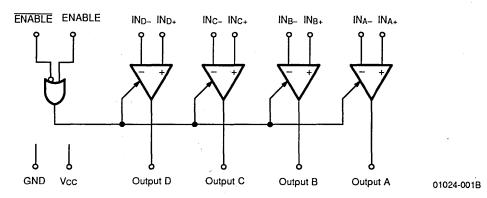

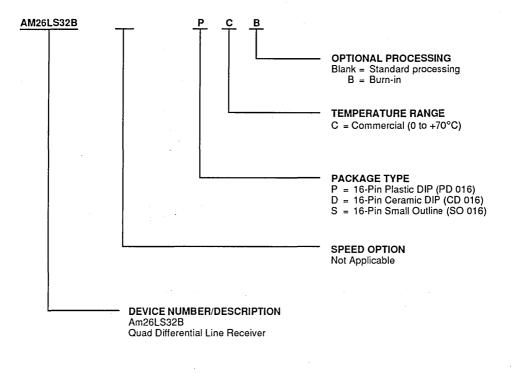

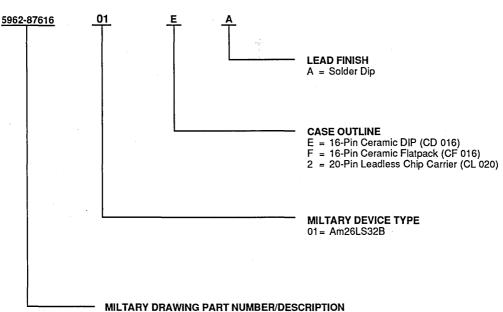

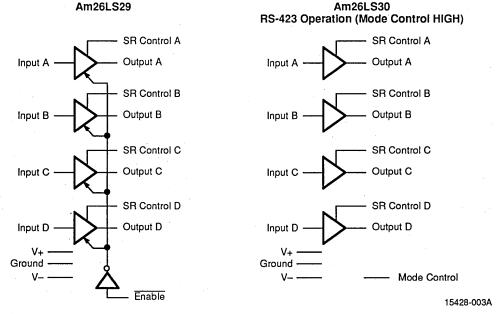

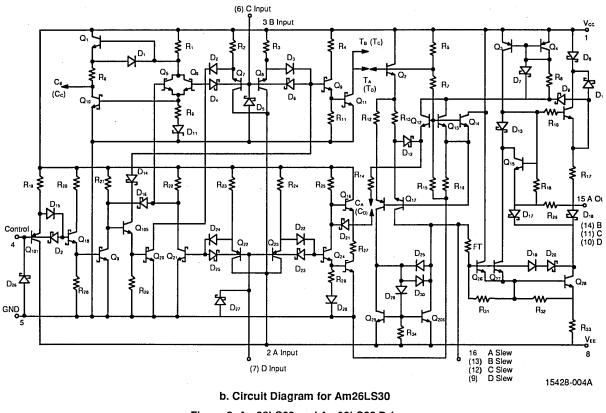

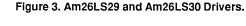

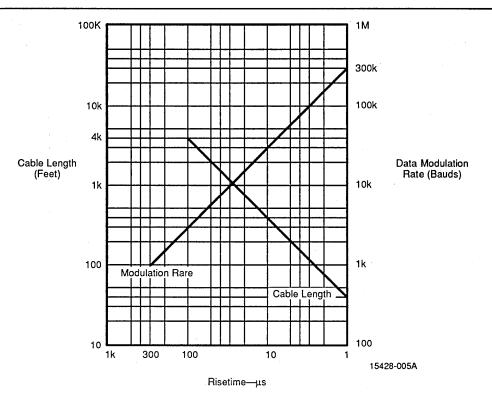

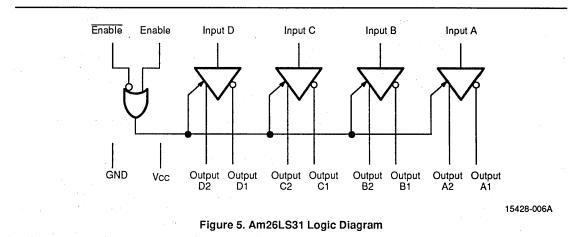

| Chapter 4  | Interface Products4–1Am26LS29 Quad Three-State Single Ended RS-4234–3Line Driver4–3Am26LS30 Dual Differential RS-422 Party Line/Quad Single Ended4–14RS-423 Line Driver4–14Am26LS31 Quad High Speed Differential Line Driver4–28Am26LS32/Am26LS33 Quad Differential Line Receiver4–39Am26LS32B Quad Differential Line Receiver4–51Am26LS34 Quad Differential Line Receiver4–63Am26LS38 Quad Differential Backplane Transceiver4–75Use of the Am26LS29/30/31/32 Quad Driver/Receiver4–89 |

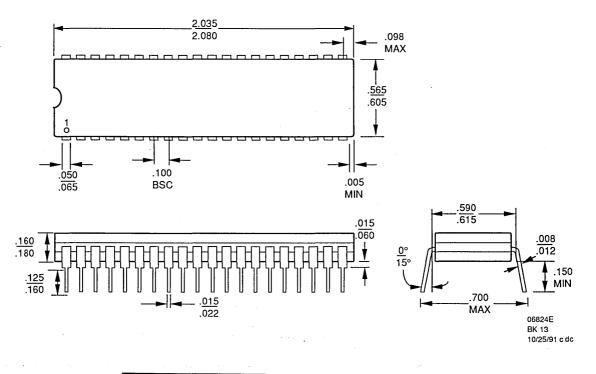

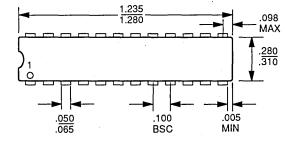

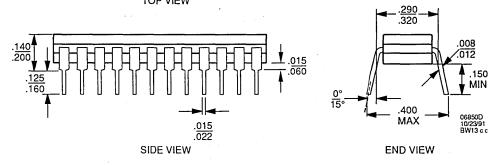

| Chapter 5  | Physical Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Appendix A | Am33C93A Qualification Information                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Appendix B | Am53C80A Qualification Information                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Appendix C | Am85C30 Qualification Information                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix D | Am85C80 Qualification Information                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

iv

### NUMERICAL DEVICE INDEX

| Am26LS29  | Quad Three-State Single Ended RS-423<br>Line Driver                              |

|-----------|----------------------------------------------------------------------------------|

| Am26LS30  | Dual Differential RS-422 Party Line/Quad Single Ended<br>RS-423 Line Driver 4–14 |

| Am26LS31  | Quad High Speed Differential Line Driver                                         |

| Am26LS32  | Quad Differential Line Receiver 4–39                                             |

| Am26LS33  | Quad Differential Line Receiver 4-39                                             |

| Am26LS32B | Quad Differential Line Receiver 4–51                                             |

| Am26LS34  | Quad Differential Line Receiver                                                  |

| Am26LS38  | Quad Differential Backplane Transceiver                                          |

| Am33C93A  | Enhances SCSI-Bus Interface Controller 1–3                                       |

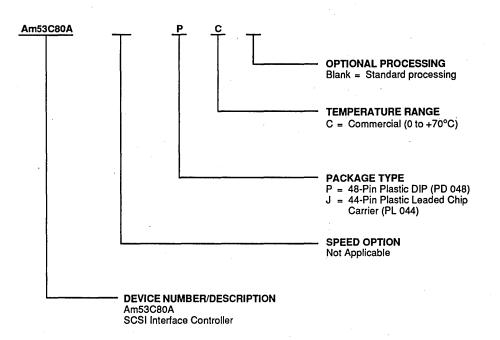

| Am53C80A  | SCSI Interface Controller 1–52                                                   |

| Am53C94   | High Performance SCSI Controller 1–85                                            |

| Am53C96   | High Performance SCSI Controller 1–85                                            |

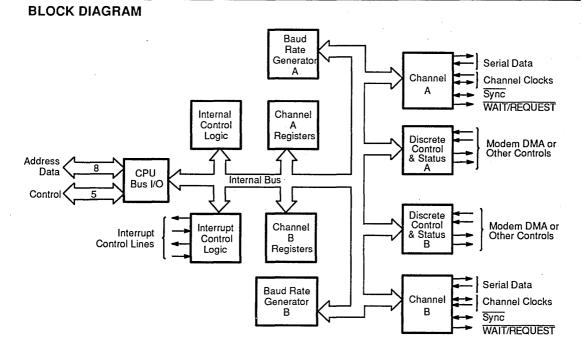

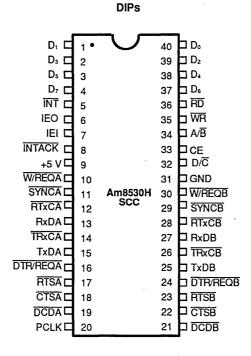

| Am8530H   | Serial Communication Controller 2–3                                              |

| Am85C30   | Enhanced Serial Communications Controller                                        |

| Am85C230A | Enhanced Serial Communications Controller<br>with LocalTalk Support (ESCC/LT)    |

| Am85C80   | Combined SCSI Controller and Serial Communication                                |

# **Data Communication Products**

### Introduction

AMD offers a complete line of Data Communications products which allow CPU hosts to communicate with peripherals using various industry standard protocols. AMD's Data Communications product family includes Small Computer System Interface (SCSI) Controllers, Serial Communications Controllers (SCC), Combination devices containing both SCC and SCSI blocks, and Interface Line Drivers and Receivers.

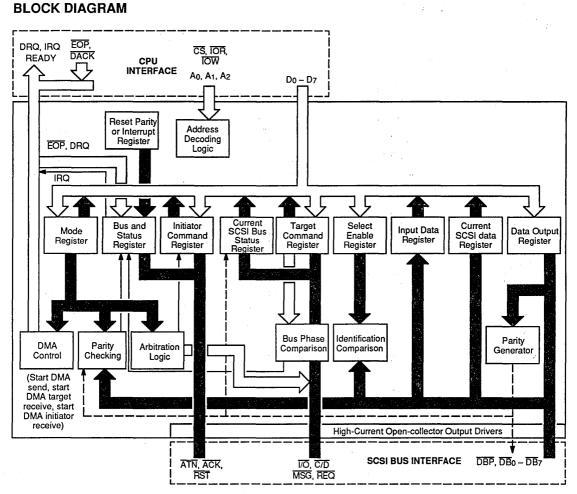

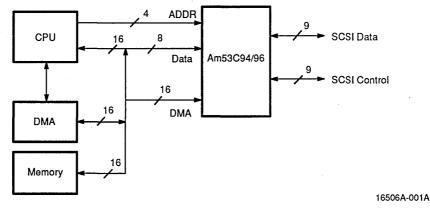

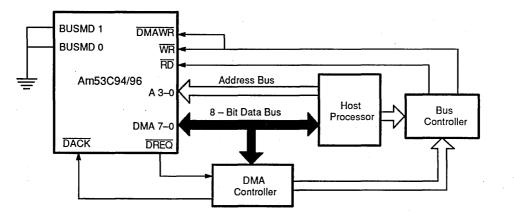

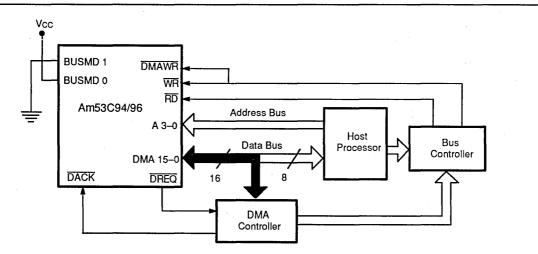

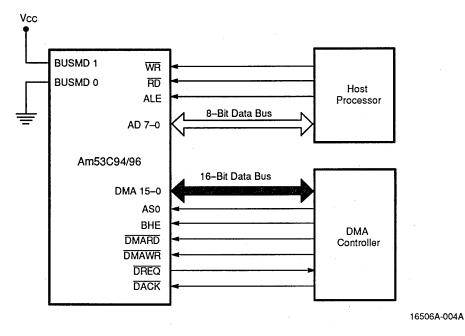

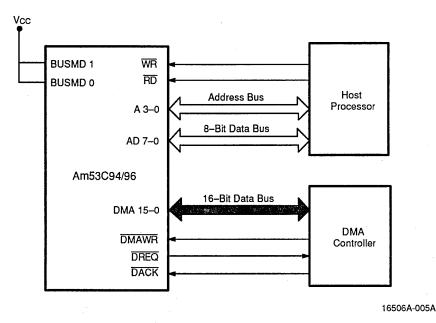

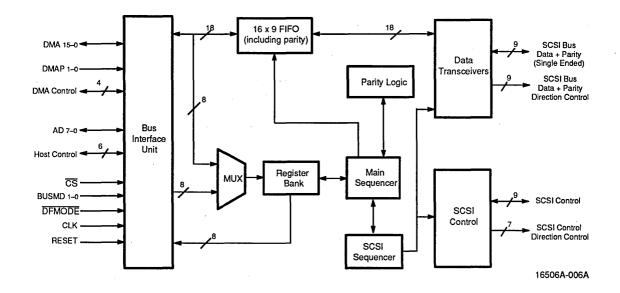

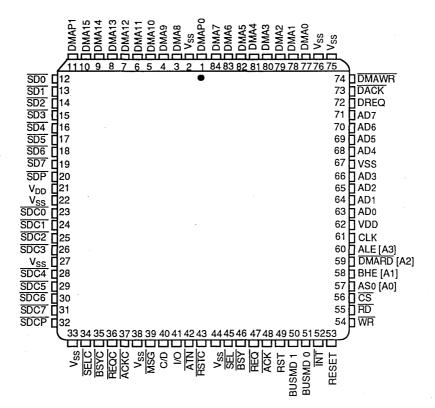

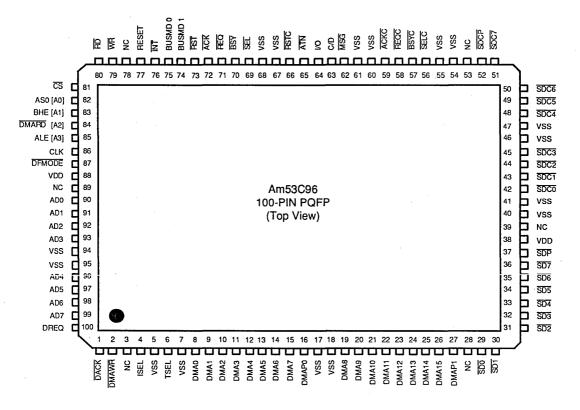

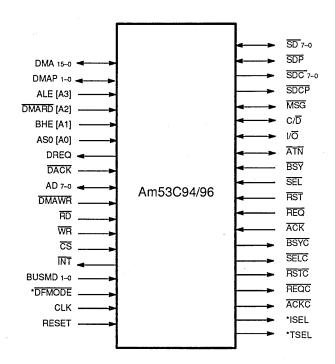

The Am53C94 and Am53C96 High Performance SCSI Controllers (HPSC) are plug-in replacements for the industry standard 53C94 and 53C96, respectively. The HPSC has a flexible three bus architecture. It has a 16 bit DMA interface, an 8 bit host data interface and an 8 bit SCSI data interface. The HPSC is designed to minimize host intervention by implementing common SCSI sequences in hardware. An on-chip state machine reduces protocol overheads by performing the required sequences in response to a single command from the host. Many SCSI-2 features are supported including Selection, Reselection, and Disconnection commands, which are directly supported.

Due to a popular move towards SCSI, AMD has second-sourced Western Digital's 33C93A second generation SCSI controller, enhancing it by fabricating the device on a submicron CMOS process technology. The 33C93A is the only second sourced SCSI controller in this category, allowing peripheral and host system manufacturers to build state-of-the-art systems, at low cost, while taking advantage of the 33C93A's 5MByte/second synchronous transfer rate.

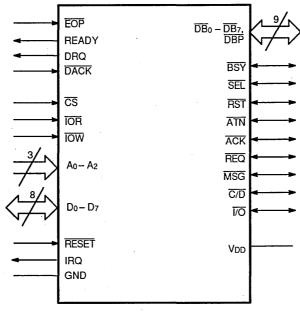

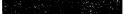

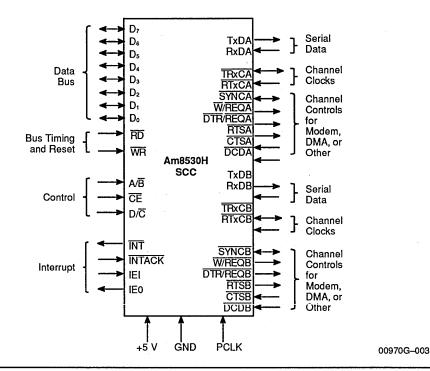

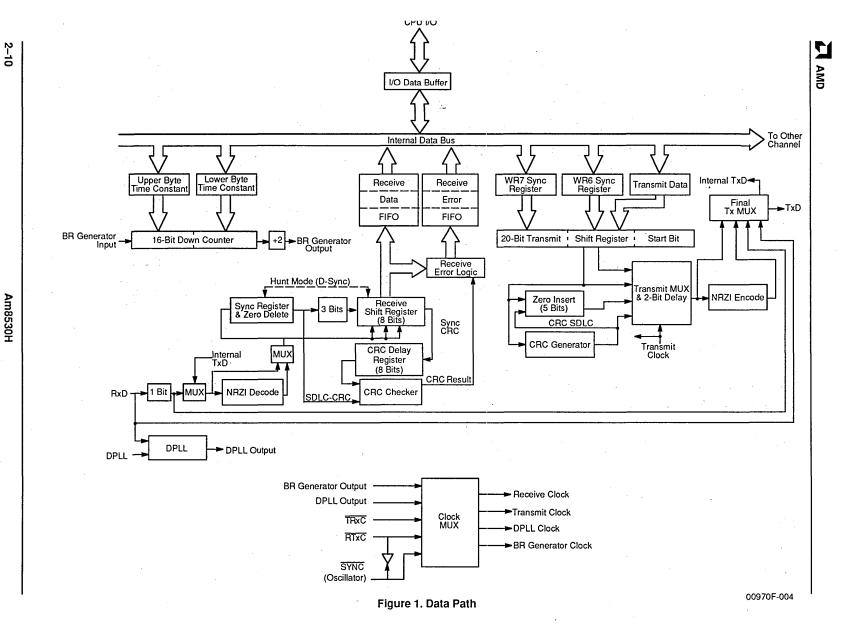

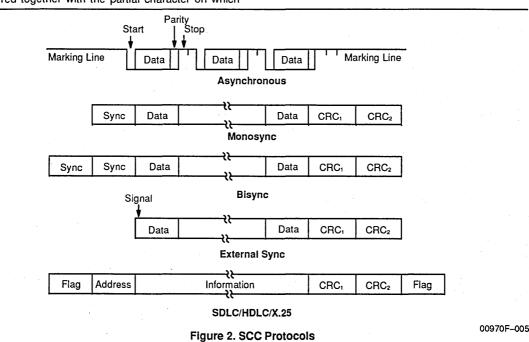

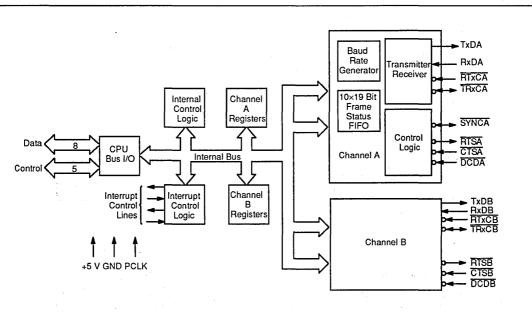

The 53C80A first generation SCSI device has been improved by AMD with the addition of enhanced ESD protection and with proprietary "glitch eating" circuitry on the SCSI bus inputs, which increases the reliability of systems by filtering out noise Con the SCSI bus due to inadequate termination and high current swings. The Am8530H is the first generation of the serial communication controller family. It is designed for the use with the 8- and 16-bit microprocessors. The SCC is dual-channel and can be software configured to satisfy a wide variety of serial communication applications.

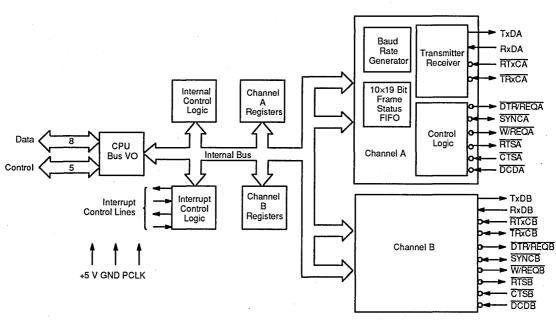

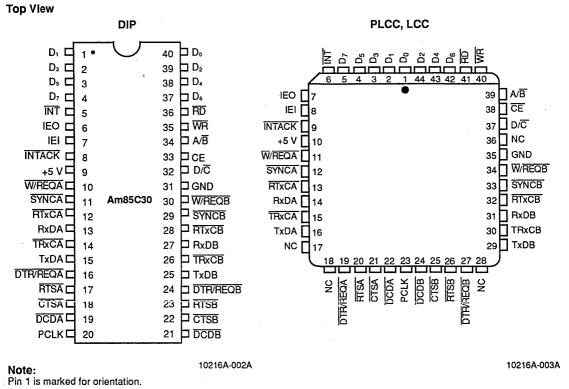

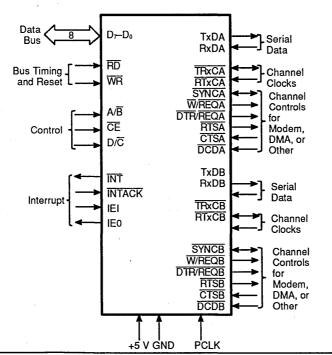

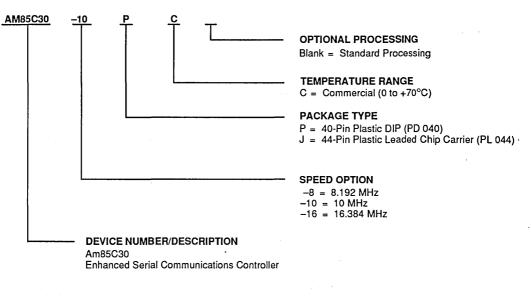

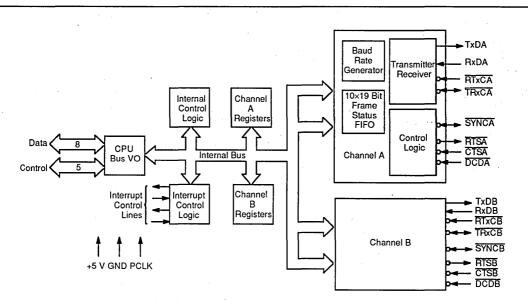

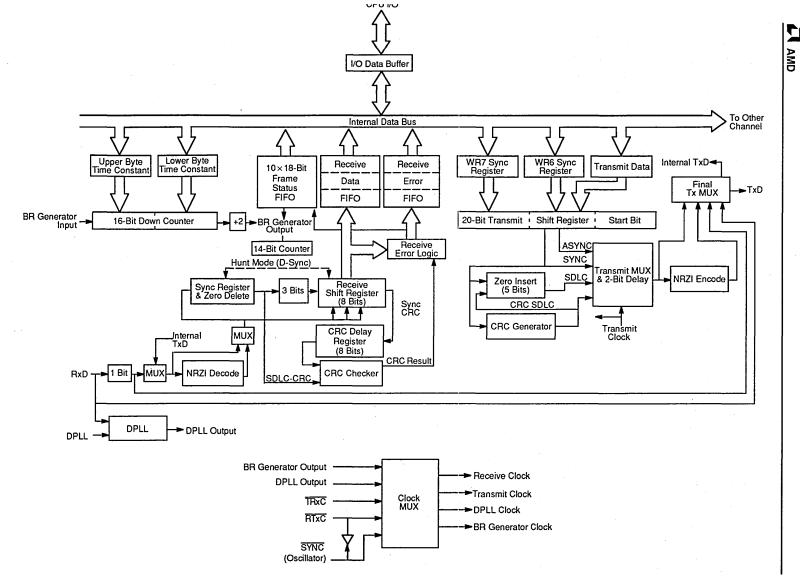

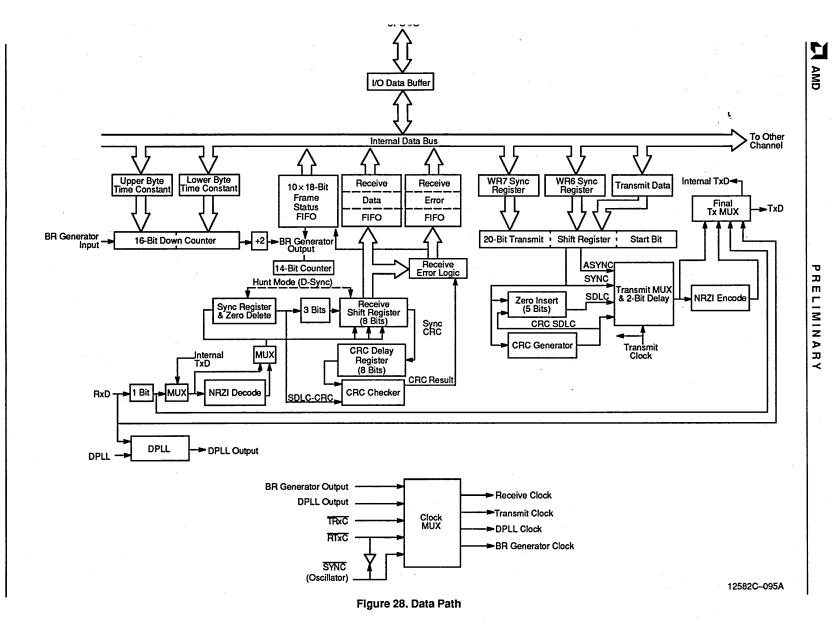

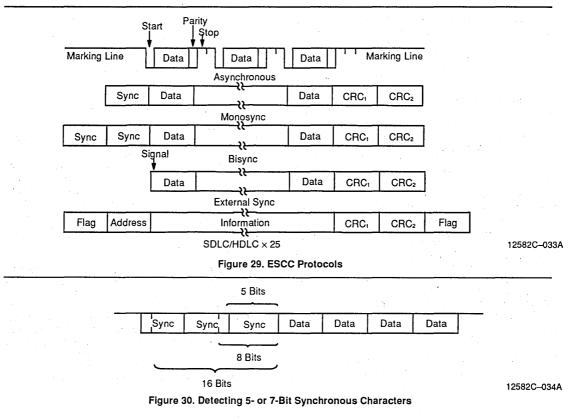

The Am85C30 ESCC is a high performance version of the industry-standard 8530 architecture. AMD's version incorporates enhancements which make CPU interfacing much easier, reducing software overhead, and increasing performance. As a result, the Am85C30 has become an industry standard serial interface on engineering workstations and many other high performance platforms.

The next generation of the SCC family is the Am85C230A. The Enhanced Serial Communication Controller with LocalTalk support. The Am85C230A is not only plug compatible to Z85230, it is a functional superset with LocalTalk enhancements; 4 deep transmit FIFO extension (total of 8 bytes), sleep mode, quieter Rx and Tx clock inputs, die revision information and ready signal to reflect write recovery time.

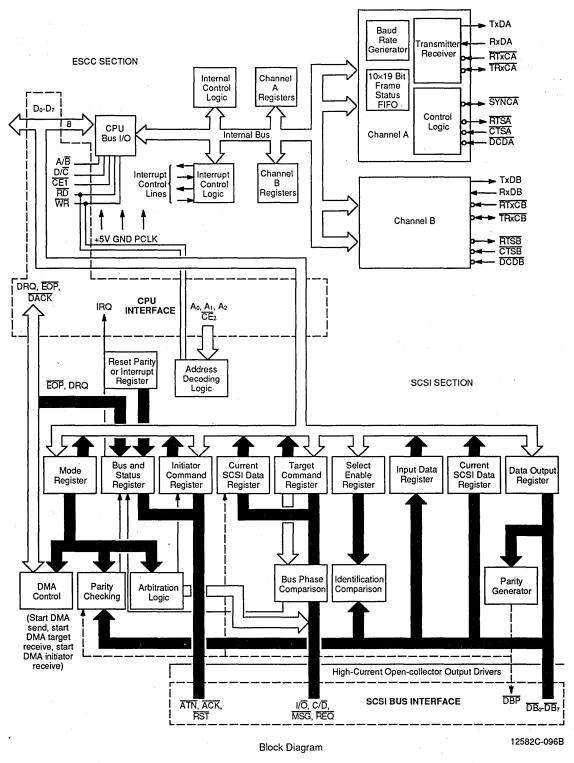

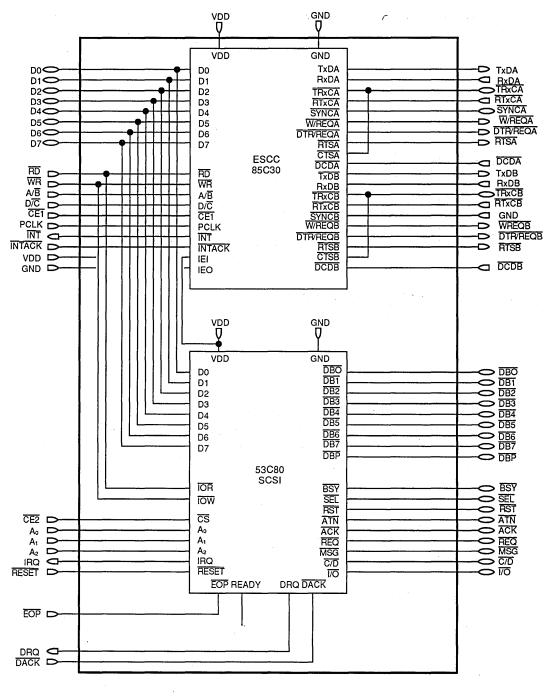

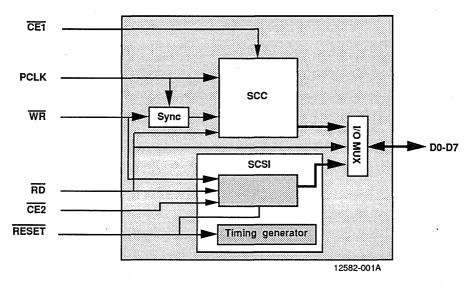

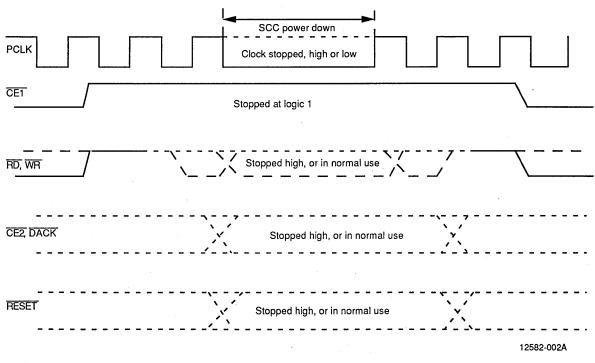

The Am85C80 Combination SCSI/SCC Controller is a unique device which incorporates an Am85C30 SCC and an Am53C80A SCSION ONE CHIP. This integration allows designers using both of these I/O functions to save valuable board space, power consumption, and manufacturing cost. Additionally, due to its fully-static CMOS design, the Am85C80 may be "put to sleep" when used with battery-powered systems, allowing a power consumption reduction of over 2000X, as compared with using two separate components.

AMD is the industry's leading supplier of standard interface devices including transmission line receivers, line drivers and backplane tranceivers.

| Combination<br>Am85C80<br>SCSI<br>Am53C80A<br>Am33C93A | SCSI/SCC<br>CMOS SCSI/SCC Combo Chip<br>CMOS SCSI Interface Controller<br>(NCR Alternate Source)<br>Enhanced CMOS SCSI Bus Interface |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| SCSI<br>Am53C80A                                       | CMOS SCSI Interface Controller<br>(NCR Alternate Source)                                                                             |

| Am53C80A                                               | (NCR Alternate Source)                                                                                                               |

| Am53C80A                                               | (NCR Alternate Source)                                                                                                               |

|                                                        | (NCR Alternate Source)                                                                                                               |

| Am33C93A                                               | Enhanced CMOS SCSI Bus Interface                                                                                                     |

|                                                        | Controller (Western Digital Second Source)                                                                                           |

| Am53C94*                                               | High Performance CMOS SCSI Controller<br>(Single-Ended; NCR Alternate Source)                                                        |

| Am53C96*                                               | High Performance CMOS SCSI Controller                                                                                                |

|                                                        | (Single-Ended and Differential; NCR<br>Alternate Source)                                                                             |

| Am53CF94*                                              | CMOS Fast SCSI-2 Chip (Emulex FAS216<br>Alternate Source; NCR Alternate Source)                                                      |

| Am53CF96*                                              | CMOS Fast SCSI-2 Chip (Emulex FAS236                                                                                                 |

|                                                        | Alternate Source; NCR Alternate Source)                                                                                              |

|                                                        |                                                                                                                                      |

|                                                        |                                                                                                                                      |

|                                                        |                                                                                                                                      |

|                                                        |                                                                                                                                      |

|                                                        | Am53C96*<br>Am53CF94*                                                                                                                |

' In development

1

.

### CHAPTER 1 Small Computer System Interface (SCSI) Controllers

| Am33C93A Enhanced SCSI-Bus Interface Controller    | 1–3 |

|----------------------------------------------------|-----|

| Am53C80A SCSI Interface Controller 1               | -52 |

| Am53C94/Am53C96 High Performance SCSI Controller 1 | -85 |

# Am33C93A

### **Enhanced SCSI-Bus Interface Controller**

### DISTINCTIVE CHARACTERISTICS

- Implements full SCSI bus features: arbitration, disconnect, reconnect, parity generation/checking on both data ports, soft reset, and synchronous data transfers

- Synchronous offset selectable from 1 to 12 bytes, with selectable transfer period up to 5 Mbytes/s

- Compatible with most microprocessors through an 8-bit data bus; supports both multiplexed and nonmultiplexed address/data bus systems. Host bus data parity checking and generation is an optional feature

- Can be used as a host adapter (SCSI Initiator) or peripheral adapter (SCSI Target)

- Data transfer options include programmed I/O, single-byte DMA, burst (multibyte) DMA, or direct bus access (DBA Bus) transfers

### **GENERAL DESCRIPTION**

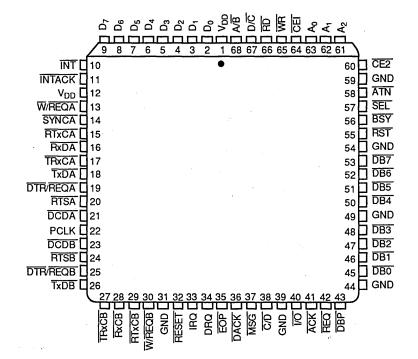

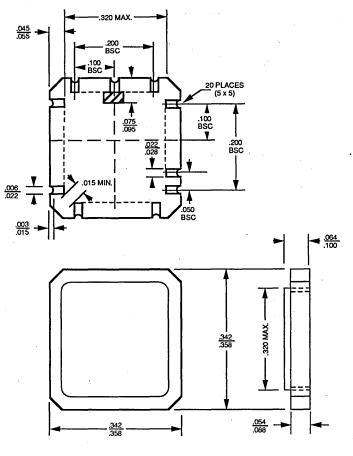

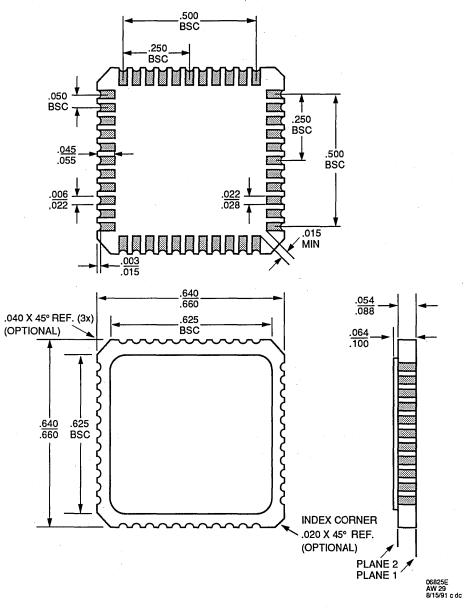

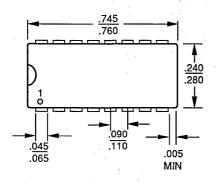

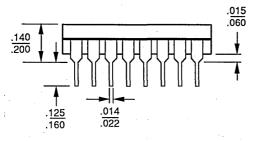

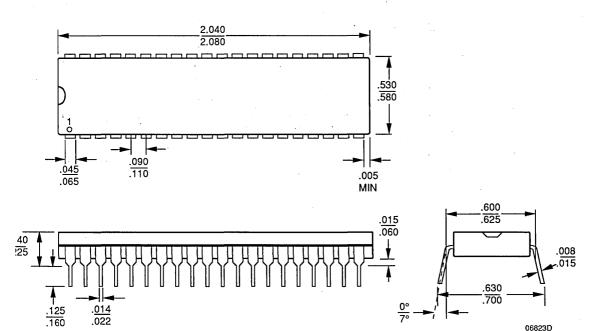

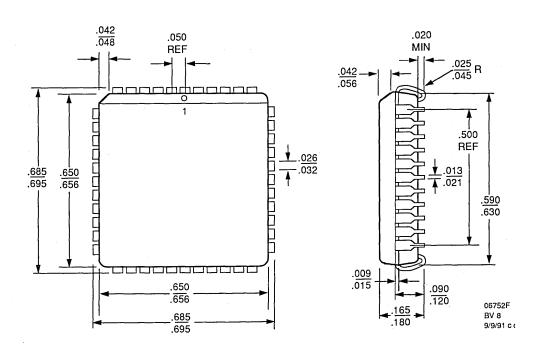

The Am33C93A is a MOS/VLSI device implemented in Advanced Micro Devices' CMOS process. It operates from a single 5-Volt supply and is available in either a 44-pin chip carrier or a 40-pin dual-in-line package. All inputs and outputs are TTL compatible.

The Am33C93A is intended for use in systems which interface to the Small Computer System Interface (SCSI) Bus. The Am33C93A can operate in both the initiator (typically, a host computer system) and the target (typically, a peripheral device) SCSI bus roles.

When used in the host system, the Am33C93A interfaces to both the host bus and the SCSI bus. To perform a SCSI operation, the host processor issues a command to the Am33C93A to select the desired Target. The Am33C93A then arbitrates for the SCSI bus and selects the peripheral unit. If it fails to get the bus because of a device with higher priority, it continues trying and notifies the host when it has succeeded by generating an interrupt. At this point, the Am33C93A is operating in the initiator role. When the peripheral requests a SCSI command from the host, the Am33C93A receives the request and generates another interrupt to the host. The host responds to this interrupt by issuing a

- Includes 48-mA drivers for direct connection to the SCSI bus

- 24 bit transfer counter

- Programmable timeout for selection and reselection

- "Combination" commands greatly reduce interrupthandling responsibilities

- Special "Translate Address" command performs the Logical- to-Physical address translation

- Single +5 V supply

- Available in 44-pin chip carrier or 40-pin DIP

- Low power CMOS design

"Transfer Info" command and supplying SCSI command bytes to the Am33C93A. The Am33C93A transfers the SCSI command to the peripheral, and then waits for the next bus phase request. This process continues until all SCSI information including data, status, and messages have been transferred.

The Am33C93A also offers high-level Select-and-Transfer commands which eliminate the interrupt handling otherwise required between each SCSI bus phase.

When the Am33C93A is used in a peripheral system, the Am33C93A will operate primarily in a Target role. It interfaces with a local processor and the SCSI bus in this environment just as it does when used as a host adapter. The Target-role command set enables the Am33C93A to request each SCSI bus phase individually or to sequence the SCSI bus phases automatically through the use of combination commands.

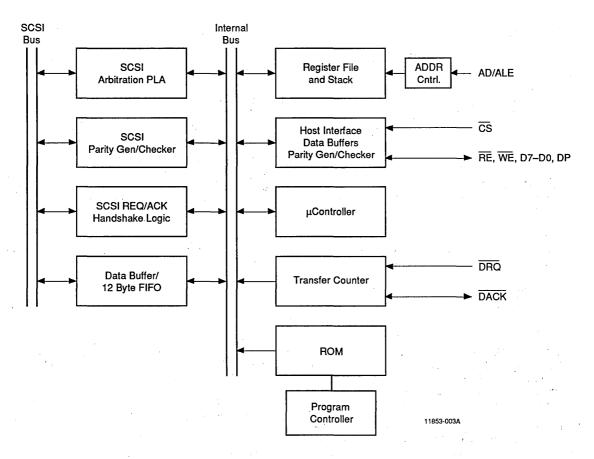

The Am33C93A has an internal microcontroller, a register task file, and SCSI interface logic. This architecture supports both tight control of the protocol for nonstandard SCSI implementations, as well as a handsfree mode for standard SCSI applications.

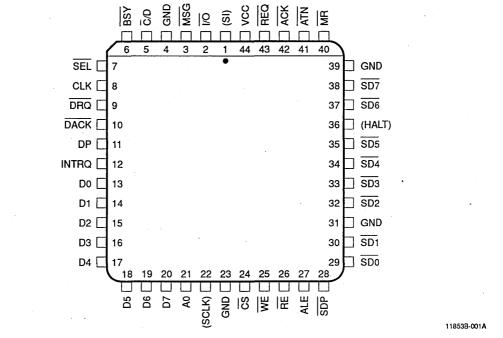

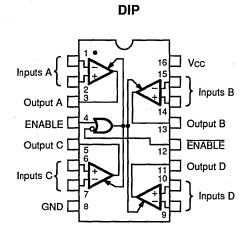

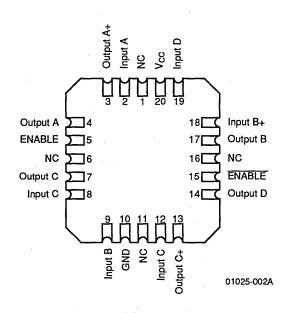

### **CONNECTION DIAGRAMS**

### **44-PIN CHIP CARRIER**

Note: Pins in parentheses are for test purposes only, and should be left unconnected for normal chip operation.

### **40-PIN DIP**

|        |    | _    | -     |

|--------|----|------|-------|

| 1/0    | 1. | 40   |       |

| MSG    | 2  | 39   |       |

| GND [  | 3  | 38   |       |

| Ē/D [_ | 4  | 37   |       |

| BSY [  | 5  | 36   | MR    |

| SEL    | 6  | 35   | GND   |

| CLK 🗌  | 7  | . 34 | SD7   |

| DRQ    | 8  | 33   | SD6   |

| DACK   | 9  | 32   | SD5   |

| INTRQ  | 10 | 31   | SD4   |

| DO 🗌   | 11 | 30   | SD3   |

| D1 🗌   | 12 | 29   | SD2   |

| D2 🗌   | 13 | 28   | GND   |

| D3 🗌   | 14 | . 27 | □ SD1 |

| D4 🗌   | 15 | 26   |       |

| D5 🗌   | 16 | 25   | SDP   |

| D6 🗌   | 17 | 24   |       |

| D7 🗌   | 18 | 23   | RE    |

| A0 🗌   | 19 | 22   | 🗌 WE  |

| GND    | 20 | 21   |       |

11853B-002A

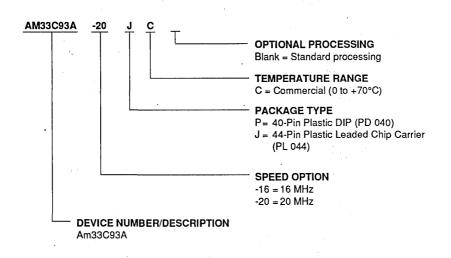

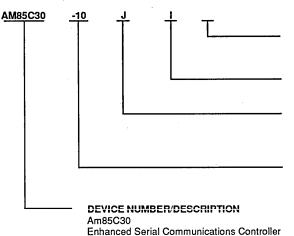

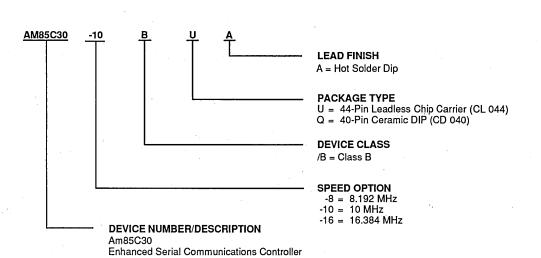

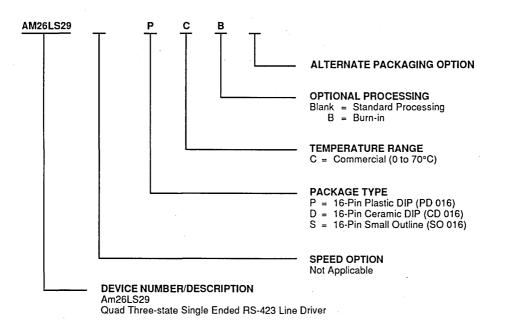

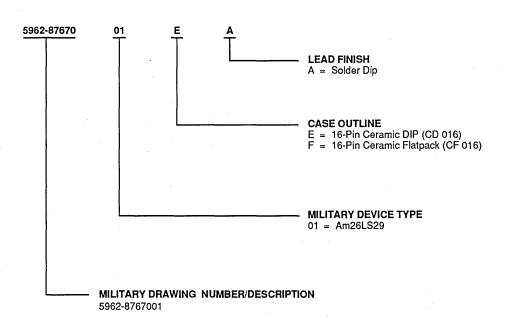

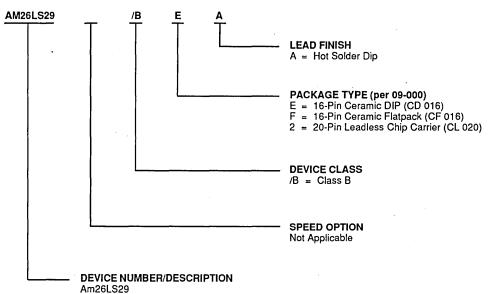

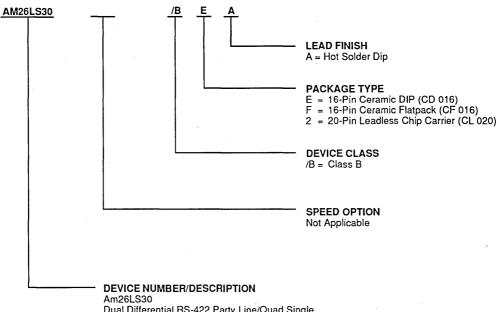

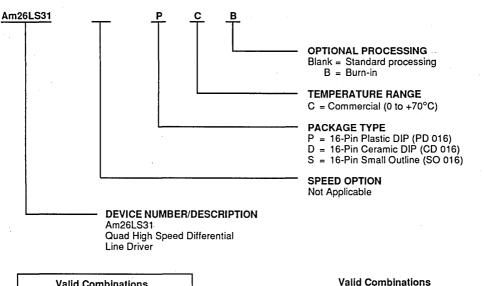

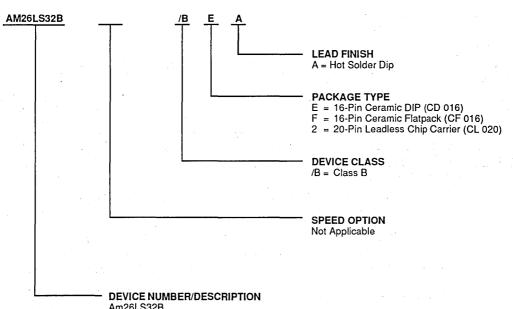

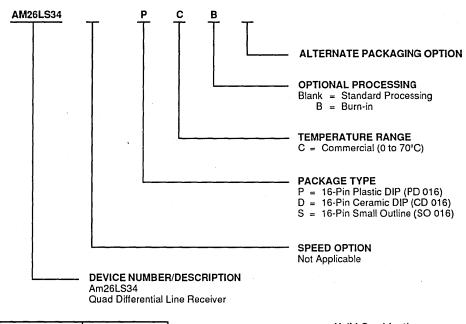

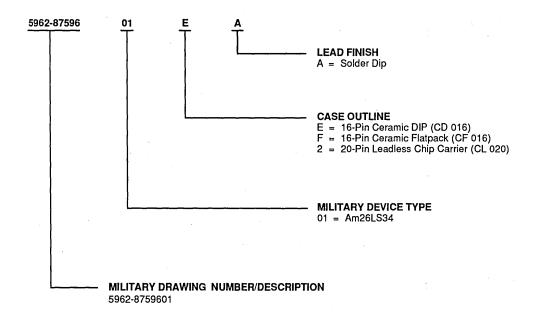

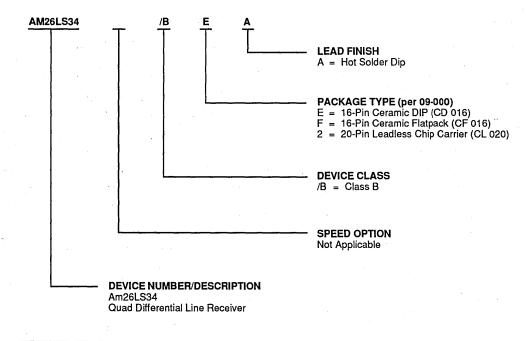

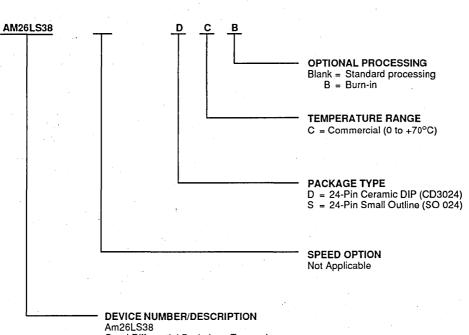

### ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid combination) is formed by a combination of:

| Valid Combinations |        |  |  |

|--------------------|--------|--|--|

| AM33C93A-16        | 10, 50 |  |  |

| AM33C93A-20        | JC, PC |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations.

### **PIN DESCRIPTIONS**

### **Processor/DMA Interface**

| Name          | I/O   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLK           |       | 8-20 MHz square wave clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

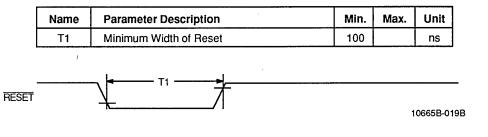

| MR            | I     | Reset is an active-low input which forces the Am33C93A into an idle state. All SCSI signals a forced to the negated state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

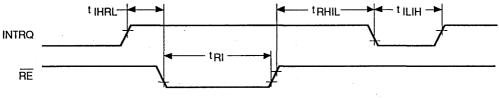

| INTRQ         | 0     | Interrupt Request to external microprocessor indicates a command completion/termination or a<br>need to service the SCSI interface. Reading the SCSI STATUS register clears this bit.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

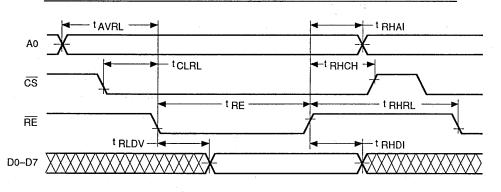

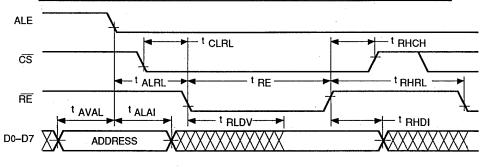

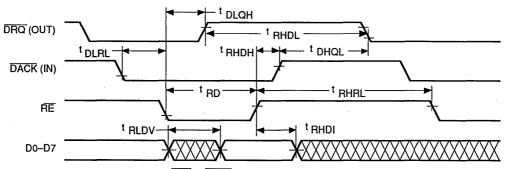

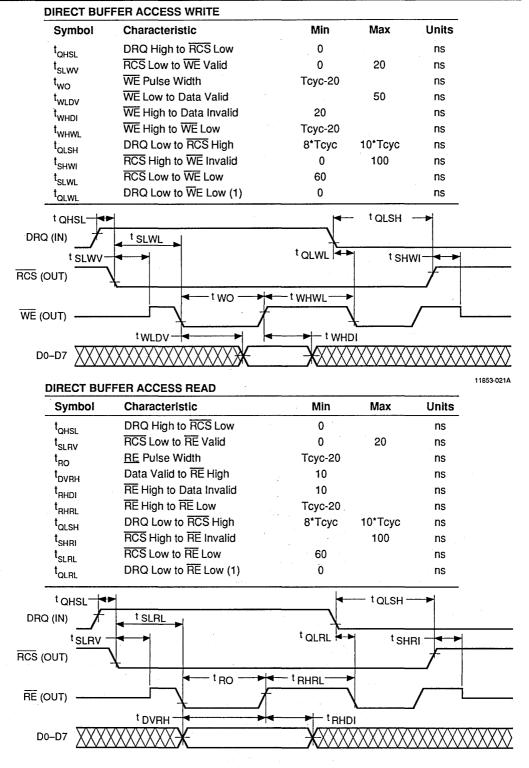

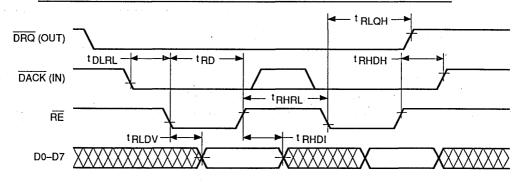

| RE            | I/O   | Read Enable is an active-low input which is used with $\overline{CS}$ to read a register or with $\overline{DACK}$ to access the DATA register in DMA mode. In DBA Bus mode, it is used as an output to read data from a sector buffer. (TRI-STATE)                                                                                                                                                                                                                                                                                                                                       |  |  |  |

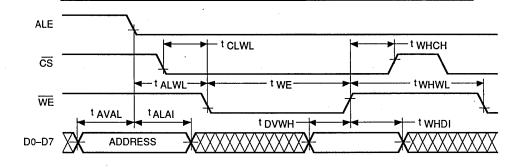

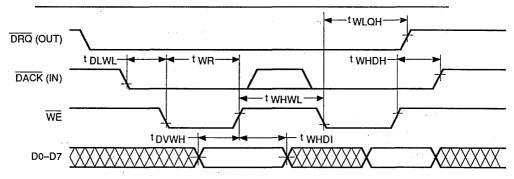

| WE            | I/O   | Write Enable is an active-low input which is used with $\overline{\text{CS}}$ to write a register or with $\overline{\text{DACK}}$ to access the DATA register in DMA mode. In DBA Bus mode, it is used as an output to write data to a secto buffer. (TRI-STATE)                                                                                                                                                                                                                                                                                                                         |  |  |  |

|               | 1     | Chip Select is an active-low input which qualifies RE and WE when accessing a register. This sig nal must be inactive during a DMA cycle (DACK active in DMA and Burst DMA mode, or DRC active in DBA Bus mode).                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Ao            | . I   | Address pin A0 is used to access the internal registers for non-multiplexed address/data busses<br>(i.e. the ALE pin is grounded). The address of the desired register is loaded into the ADDRESS<br>register during a write cycle with A0=0. The selected register is then accessed when A0=1.                                                                                                                                                                                                                                                                                           |  |  |  |

| ALE           | I     | Address Latch Enable is used for multiplexed address/data busses to load the address of the<br>desired Am33C93A register from the data bus. If indirect addressing is to be used, the ALE pir<br>should be grounded. See the description of the ADDRESS register for a complete discussion o<br>direct and indirect addressing.                                                                                                                                                                                                                                                           |  |  |  |

| DACK<br>(RCS) | I/O   | DMA acknowledge input used for interfacing to an external DMA controller (e.g. 8237). Wh<br>DACK is low, all bus transfers are to/from the DATA register regardless of the contents of the<br>ADDRESS register. In DBA Bus mode, this pin functions as a RAM chip select output to allow the<br>Am33C93A to access a sector buffer. RE and WE are outputs when RCS (RAM Chip Select)<br>active. Since this pin can be an open drain output, a pullup resistor may be required wh<br>operating in DBA Bus mode.                                                                            |  |  |  |

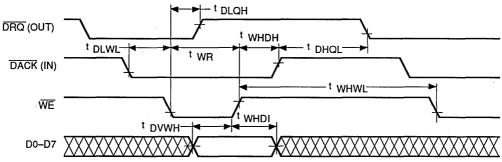

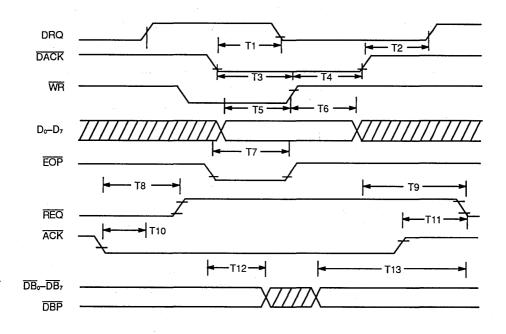

| DRQ<br>(DRQ)  | . 1/0 | Data request is an output when interfacing to an external DMA controller, and an input when i DBA Bus mode. When used with an external DMA controller, DRQ and DACK form the handshak for the data-byte transfers. In Burst mode, DRQ remains low as long as there is data to transfer. I DBA Bus mode, the Am33C93A performs burst transfers while DRQ is high, and when DRQ is low data transfers are inhibited, RCS is false, and the RE and WE outputs are disabled. Since this pi can be an open drain output, a pullup resistor may be required when operating in DMA or Burs mode. |  |  |  |

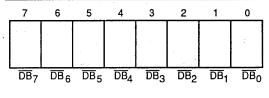

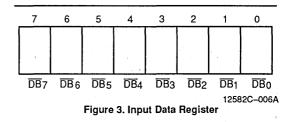

| D7-D0         | I/O   | Processor data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| DP            | I/O   | Data Parity, used only for checking/generating parity during data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

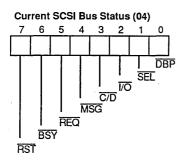

| SCSI Inte     | rface | The second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Name          | I/O   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

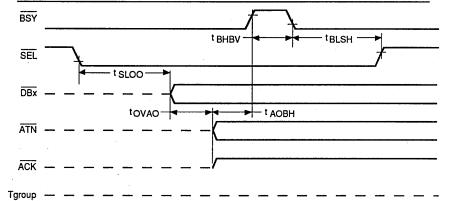

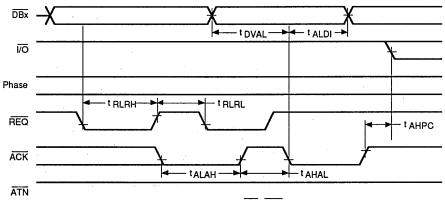

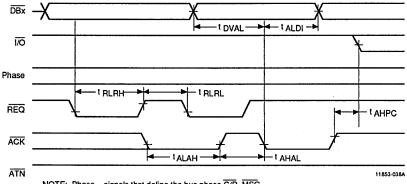

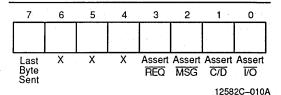

| ATN           | I/O   | ATN is an output in the initiator role and an input in the target role. It is used to indicate th ATTENTION condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ACK           | I/O   | ACK is an output in the initiator role and an input in the target role. It is used to indicate a acknowledgement for a REQ/ACK data transfer handshake.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| MSG           | I/O   | MSG is an input in the initiator role and an output in the target role. It is asserted during a MESSAGE phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

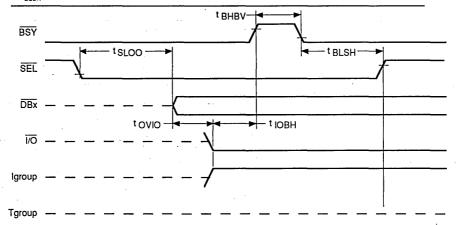

| Ċ/D           | I/O   | $\overline{C}/D$ is an input in the initiator role and an output in the target role. It is used to indicate whether CONTROL or DATA information is on the SCSI data bus.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| REQ           | I/O   | $\overline{EQ}$ is an input in the initiator role and an output in the target role. It indicates a request for a REQ/ CK data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

### SCSI Interface (Cont.)

| Name    | I/O   | Function                                                                                                                                                              |  |  |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1/0     | I/O   | 1/O is an input in the initiator role and an output in the target role. It controls the direction of data movement on the SCSI data bus with respect to an Initiator. |  |  |

| SD0-SD7 | · I/O | SCSI data bus.                                                                                                                                                        |  |  |

| SDP     | 1/0   | SCSI data bus parity signal.                                                                                                                                          |  |  |

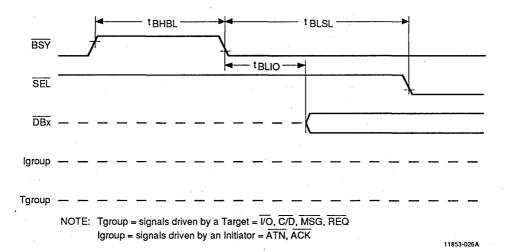

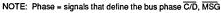

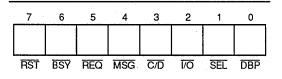

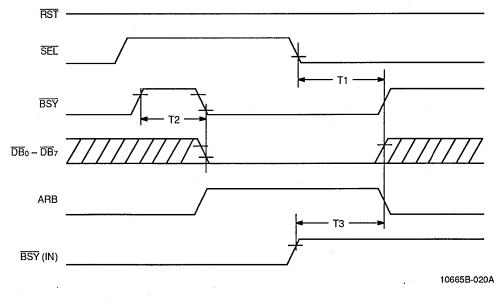

| BSY     | I/O   | $\overline{\text{BSY}}$ is asserted when the Am33C93A is attempting to arbitrate for the SCSI bus or when connected as a Target.                                      |  |  |

| SEL     | 1/0   | SEL is asserted when the Am33C93A is attempting to select or reselect another SCSI device.                                                                            |  |  |

Note: All pins have open-drain output drivers.

### Am33C93A REGISTERS

### **Register Map**

| AO      | R/W        | Register Accessed                         | Address<br>(HEX) |

|---------|------------|-------------------------------------------|------------------|

| 0       | R          | AUXILIARY STATUS REGISTER                 | XX               |

| 0       | W          | ADDRESS REGISTER                          | XX               |

| 1       | R/W        | OWN ID REGISTER /CDB SIZE                 | 00               |

| 1       | R/W        | CONTROL REGISTER                          | 01               |

| 1       | R/W        | TIMEOUT PERIOD REGISTER                   | 02               |

| 1       | R/W        | TOTAL SECTORS REGISTER /CDB 1ST           | 03               |

| 1       | R/W        | TOTAL HEADS REGISTER /CDB 2ND             | 04               |

| 1       | R/W        | TOTAL CYLINDERS REGISTER (MSB) /CDB 3RD   | 05               |

| 1       | R/W        | TOTAL CYLINDERS REGISTER (LSB) /CDB 4TH   | 06               |

| 1       | R/W        | LOGICAL ADDRESS (MSB) /CDB 5TH            | 07               |

| 1       | R/W        | LOGICAL ADDRESS (2ND) /CDB 6TH            | 08               |

| · 1 ·   | R/W        | LOGICAL ADDRESS (3RD) /CDB 7TH            | 09               |

| 1       | R/W        | LOGICAL ADDRESS (LSB) /CDB 8TH            | 0A               |

| 1 .     | R/W        | SECTOR NUMBER REGISTER /CDB 9TH           | 0B               |

| 1       | R/W        | HEAD NUMBER REGISTER /CDB 10TH            | 0C               |

| 1       | R/W        | CYLINDER NUMBER (MSB) REGISTER /CDB 11TH  | 0D               |

| 1       | R/W        | CYLINDER NUMBER (LSB) REGISTER /CDB 12TH  | 0E               |

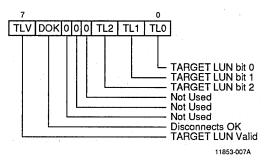

| 1       | R/W        | TARGET LUN REGISTER                       | OF               |

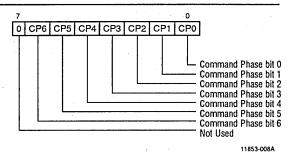

| 1       | R/W        | COMMAND PHASE REGISTER                    | 10               |

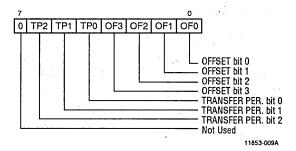

| 1       | R/W        | SYNCHRONOUS TRANSFER REGISTER             | 11               |

| 1       | R/W        | TRANSFER COUNT REGISTER (MSB)             | 12               |

| 1       | R/W        | TRANSFER COUNT REGISTER (2ND BYTE)        | 13               |

| 1       | R/W        | TRANSFER COUNT REGISTER (LSB)             | 14               |

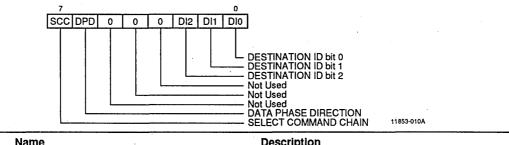

| 1       | R/W        | DESTINATION ID REGISTER                   | - 15             |

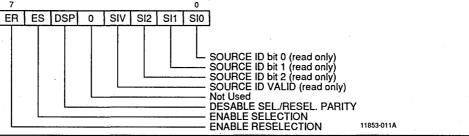

| 1       | R/W        | SOURCE ID REGISTER                        | 16               |

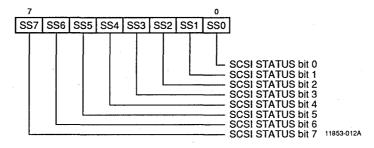

| · 1 ··· | . <b>R</b> | SCSI STATUS                               | 17               |

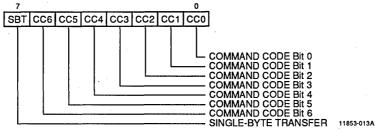

| 1       | R/W        | COMMAND REGISTER                          | 18               |

| 1       | R/W        | DATA REGISTER                             | 19               |

| -1      | R          | AUXILIARY STATUS (DIRECT ADDRESSING MODE) | 1F               |

Notes: 1. All unused bits of a defined register are reserved and must be zero.

2. Reading an undefined or unavailable register results in an all-ones data bus output.

3. Register addresses are determined by the ADDRESS register bits AR7 through AR0.

4. When using a multiplexed address/data bus with ALE, the A0 pin is ignored and the ADDRESS register is loaded with ALE. In this mode, the AUXILIARY STATUS register is mapped at hex 1F.

5. See Page 14 for a description of how reset affects the internal registers.

### **Register Descriptions**

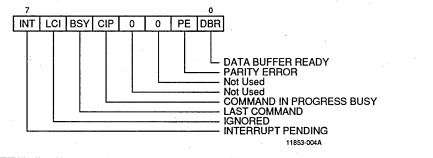

### AUXILIARY STATUS REGISTER (Address Hex 1F)

The AUXILIARY STATUS register is a read-only register which contains general status information not directly associated with the interrupt condition. The AUXILIARY

STATUS register may be accessed at any time, except during DMA accesses (DACK asserted in DMA/Burst mode or DRQ asserted in DBA bus mode).

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DBR  | DATA BUFFER READY is used during programmed I/O to indicate to the processor whether<br>or not the DATA register is available for reading or writing. During Send or Transfer<br>commands which transmit data over the SCSI bus, the DBR bit is set when the Am33C93A<br>is ready to take a byte from the host; the bit is reset when the processor writes the byte to the<br>DATA register. During Receive or Transfer commands which receive data over the SCSI<br>bus, the DBR is set when a byte is received; it is reset when the processor reads the byte<br>from the DATA register. |

| 1   | PE   | PARITY ERROR status indicates that even parity was detected on a data byte received during an information transfer. Parity is checked on data received from the host bus during transfers out to the SCSI bus and is checked on data received from the SCSI bus during transfers out to the host bus. Detection of a parity error will set the PE status bit regardless of the state of the HHP or HSP bits in the CONTROL register. The PE bit is cleared when a new command is issued.                                                                                                   |

| 4   | CIP  | COMMAND IN PROGRESS, when set, indicates that the Am33C93A is interpreting the last<br>command entered into the COMMAND register and therefore this register is unavailable.<br>When this bit is reset, a command may be written to the COMMAND register.                                                                                                                                                                                                                                                                                                                                  |

| 5   | BSY  | BUSY indicates that a Level II command is currently executing and therefore only the COMMAND register (when CIP = 0), the DATA register, and the AUXILIARY STATUS register are accessible by the host. A Level II command may not be written to the COMMAND register when this bit is one.                                                                                                                                                                                                                                                                                                 |

| 6   | LCI  | LAST COMMAND IGNORED indicates that a command was issued by the host just prior to<br>or concurrent with a pending interrupt, and therefore the command will be ignored.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7   | INT  | INTERRUPT PENDING indicates that the INTRQ pin is asserted. The host should read the SCSI STATUS register to clear INTRQ prior to issuing any commands.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### ADDRESS REGISTER (Address XX Hex)

The ADDRESS register is a write-only register which contains the address of the register to be accessed. Registers in the Am33C93A may be accessed in one of two ways:

- Direct addressing (multiplexed address/data busses). In direct addressing, the falling edge of the ALE signal is used to latch the address into the ADDRESS register. The A0 pin should be connected to ground when using this method. The ALE is typically then followed by the CS and WE or RE signals that access the selected register. Also, in direct addressing, the AUXILIARY STATUS register is located at address 1F hex.

- · Indirect addressing (separate address/data busses). In indirect addressing, the register access is performed in two separate cycles. This method is enabled by attaching ALE to ground. First, the ADDRESS register is loaded by performing a write of the desired address to the Am33C93A (WE and CS asserted) with A0=0. Then the register is accessed by asserting  $\overline{CS}$  and  $\overline{WE}$  or  $\overline{RE}$ , with A0=1. Also, following every access with A0=1, the AD-DRESS register will automatically increment to point at the next register, with the exception of the following locations: AUXILIARY STATUS register, DATA register, and the COMMAND register. In indirect addressing, the AUXILIARY STATUS register is accessed by performing a read (CS and RE asserted) with A0=0.

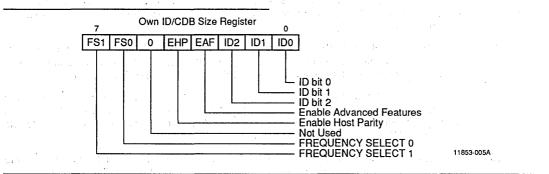

### OWN ID/CDB SIZE REGISTER (Address 00 Hex)

The OWN ID/CDB SIZE register, in its first mode, contains both the encoded ID of the Am33C93A on the SCSI bus and several control bits that are used to initially configure the device during the "Reset" command. These bits control 'advanced feature' selection, host bus parity enable, and selection of the divisor for the input clock. In its second mode (when advanced features are enabled, see p.16), this register is used during the combination commands to specify the SCSI CDB size if the command group is unknown to the Am33C93A.

In the first mode, this register (as defined below) is sampled and becomes effective only after a "Reset" command is issued to the device. This register must be initialized, and a "Reset" command must then be issued, following a hardware reset to set the SCSI bus ID, the clock divisor, and the operating modes before any other commands are issued.

In the second mode, bits 3-0 of this register are used during the Select-and-Transfer and Wait-for-Select commands to specify the SCSI Command Descriptor Block size if it is not a group 0, group 1, or group 5 command. This mode is enabled only when advanced features are enabled (see p.16).

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0-2 | IDn  | SCSI ID Bits 0-2 set the SCSI bus ID number that the Am33C93A will use during arbitration and selection.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 3   | EAF  | ENABLE ADVANCED FEATURES, when set to one, causes the Am33C93A to enable certain advanced features (see Page 16). When this bit is zero, those features are disabled.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 4   | EHP  | ENABLE HOST PARITY, when set to one, enables odd parity checking on the host bus; the PE bit in the AUXILIARY STATUS register will indicate parity errors detected on the host bus, and the HHP bit in the CONTROL register will be used. When this bit is zero, no checking is performed on the host bus; the PE bit is not set when a parity error is detected on the host bus, and the HHP bit must be set to zero. NOTE: Parity is always generated on the host data parity bit (DP), regardless of the state of this bit. |  |  |  |

| Bit | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    |                                                                                                                                                                                                                     |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–7 | FSn             | clock is used for data transfe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | er timing an ranges and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nd for SCSI bus art<br>d the corresponding                                                                         | to the input clock. The resulting<br>pitration timing. The table below<br>divisors. The correct divisor for<br>ions may not be met.                                                                                 |

|     |                 | INPUT CLOCK<br>FREQUENCY<br>(MHZ) FS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RESULTING<br>DIVISOR                                                                                               |                                                                                                                                                                                                                     |

|     |                 | 8-10 0<br>12-15 0<br>16-20 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0<br>1<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2<br>3<br>4                                                                                                        |                                                                                                                                                                                                                     |

|     |                 | xx 1<br>Note that an 11 MHZ clock ra<br>resulting SCSI bus clear delay r<br>The formula for computing the m<br>is:                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | may violate S<br>naximum SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SCSI specifications.<br>SI data transfer rate                                                                      |                                                                                                                                                                                                                     |

|     |                 | Maximum SCSI Transfer Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ck Fequency<br>Divisior                                                                                            | e/sec]                                                                                                                                                                                                              |

|     | n condition, ir | er is used to enable/disable ce<br>terrupt handling, and data trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | sfer modes           0           A           HSP           HA           HSP           HA           HA      < |                                                                                                                    | NNECT INT<br>INTERRUPT                                                                                                                                                                                              |

| Bit | Name            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                        |                                                                                                                                                                                                                     |

| 0   | HSP             | Receive or Transfer comman<br>the Initiator role, termination<br>active state in order to inh<br>facilitates error handling wit                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ERROR bi<br>nd if a parity<br>due to a S<br>ibit any ad<br>th the Targ<br>the remain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t enables the Am33<br>y error is detected o<br>CSI parity error cau<br>Iditional data transi<br>jet. Synchronous d | C93A to immediately terminate a<br>n an incoming SCSI data byte. In<br>uses the ACK pin to be left in the<br>fers (REQs) by the Target; this<br>ata transfers check parity every<br>whichever is less. Asynchronous |

| 1   | HA              | Send or Receive command<br>Initiator detected a parity err<br>tested before the start of a da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | if the ATN<br>ror while re<br>ata transfer,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | input is asserted.<br>ceiving data from th<br>every 4096 bytes if                                                  | es the Am33C93A to terminate a<br>This normally indicates that the<br>ne Am33C93A. The ATN input is<br>the transfer count is greater than<br>apply to both synchronous and                                          |

| 2   | IDi             | The INTERMEDIATE DISCONNECT INTERRUPT bit, when set, enables the Am33C93A to generate an 85H interrupt and complete a Select-and-Transfer command if the Target disconnects according to the defined SCSI protocol. When this bit is reset, no interrupt is generated by a valid disconnect. This feature, when used with the Resume Select-and-Transfer command, provides support for overlapped SCSI operations. IDI is also used to select execution options in Target mode Combination commands that serve to reduce host system overhead. (Refer to COMMANDS, p. 15 for more details.) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    |                                                                                                                                                                                                                     |

system overhead. (Refer to COMMANDS, p.15 for more details.)

| Bit | Name | ·                                  |                                 |                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------|------------------------------------|---------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | EDI  | follows th<br>comman<br>used in    | ne COMI<br>d will be<br>the Tar | VAND C<br>suppre<br>get mod      | ONNECT INTERRUPT bit is set, the 16H interrupt which normally<br>OMPLETE message during the execution of a Select-and-Transfe<br>ssed until the Target disconnects from the SCSI bus. EDI is also<br>de Combination commands to enable chaining between those<br>duced host system overhead. Refer to COMMANDS p.15 for more                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4   | HHP  | a Send c<br>parity en<br>halt on a | r Transf<br>ors are<br>host pa  | er comm<br>checked<br>rity error | RITY ERROR bit enables the Am33C93A to immediately terminat<br>and if a parity error is detected on an incoming host data byte. Hos<br>according to the rules for checking SCSI parity errors. However,<br>will not hold the ACK signal asserted when an error occurs. Hos<br>ned at the same intervals as SCSI parity checking.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5-7 | DMx  | describe                           | s the ho                        | st bus tra                       | its 2-0 are used to select the DMA mode of operation, which<br>insfer mode used during Data In or Data Out phases. The following<br>ent DMA modes, and the state of these bits to select them:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |      | DM2                                | DM1                             | DM0                              | DMA Mode Selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |      | 0                                  | 0                               | 0                                | POLLED MODE, or no DMA enabled. All data phase transfers ar performed by polling for DBR in the AUXILIARY STATUS register, an then writing (reading) the data to (from) the DATA register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |      | 0                                  | 0                               | 1                                | BURST MODE selects a demand-mode DMA interface. In this mode<br>the DRQ signal will be active as long as there is data/space in th<br>internal FIFO to allow the transfer to continue. The DMA controlle<br>responds by asserting DACK and RE/WE as long as DRQ is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |      |                                    |                                 |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |      | 0                                  | <b>1</b>                        | 0                                | DBA BUS MODE is selected when the Am33C93A is connected to<br>DBA Bus. This mode also can be called Direct Buffer Access (DBA<br>mode. In this mode, the Am33C93A acts as a bus master, and all dat<br>access signals reverse their direction: The DRQ output signal become<br>the DRQ input, which enables the Am33C93A to drive the buffer bu<br>control signals. The DACK output signal becomes the RCS input, which<br>is asserted as a chip select for the buffer. The RE and WE inputs become<br>outputs which drive the read and write functions of the RAM buffer. A<br>long as the DRQ signal is asserted, transfers will continue in a burs<br>manner, until the transfer is complete or it decides to pause the transfe<br>by negating the DRQ signal; one more transfer may occur after thi<br>transition, and then the DACK, RE, and WE signals are negated. |

### TIMEOUT PERIOD REGISTER (Address 02 Hex)

The TIMEOUT PERIOD register is an 8-bit register containing a preset value which determines the timeout period for Select and Reselect commands. This value may be calculated as a function of the input clock frequency and the desired timeout period, as shown in the following equation: