## **Advanced Micro Devices**

# The 8080A/9080A MOS MICROPROCESSOR HANDBOOK

Copyright ©1977 by Advanced Micro Devices, Inc.

Advanced Micro Devices can not assume responsibility for use of any circuitry described other than circuitry entirely embodied in an Advanced Micro Devices' product.

## **TABLE OF CONTENTS**

| CHAPTER                          |                                                                                                                                                       | INTRODUCTION      |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1                                | INTRODUCTION                                                                                                                                          |                   |

|                                  |                                                                                                                                                       | CPU ELEMENTS      |

| 2<br>3<br>4<br>5                 | 8080A/9080A FUNCTIONAL DESCRIPTION<br>8080A/9080A INSTRUCTION SET<br>8080A/9080A INSTRUCTION TIMING<br>Am8224, Am8228/38                              |                   |

|                                  |                                                                                                                                                       | I/O SUPPORT       |

| 6<br>7<br>8<br>9<br>10           | Am8212 INPUT/OUTPUT PORT<br>Am8255/9555 PERIPHERAL INTERFACE<br>Am8251/9551 COMMUNICATION INTERFACE<br>REGISTERS AND BUFFERS<br>ENCODERS AND DECODERS |                   |

|                                  |                                                                                                                                                       | MEMORIES          |

| 11                               | MEMORIES                                                                                                                                              |                   |

|                                  |                                                                                                                                                       | APPLICATION NOTES |

| 12<br>13<br>14<br>15<br>16<br>17 | CLOCK GENERATION<br>MEMORY SYSTEM DESIGN<br>PROCESSOR/MEMORY TIMING<br>INTRODUCTION TO INTERRUPTS<br>BASIC TIME DELAYS<br>MULTIPLICATION              |                   |

|                                  |                                                                                                                                                       | APPENDICES        |

| APPENDIX                         |                                                                                                                                                       |                   |

|                                  |                                                                                                                                                       |                   |

| Α | 8080A/9080A INSTRUCTION SUMMARIES |

|---|-----------------------------------|

| В | ASCII CODE TABLE                  |

| С | AMD TECHNICAL PUBLICATIONS        |

### Chapter 1 INTRODUCTION

Of all the results of the development of large-scale integrated (LSI) circuit technology, none is having as much impact as the microprocessor. Since the introduction of the first 8-bit monolithic microprocessor in 1972, the influence of these devices has become increasingly pervasive. The trends clearly indicate that we can look forward to the appearance of microprocessors in more and more applications.

Advances in both bipolar and metal-oxide-semiconductor (MOS) processing and technology have resulted in the evolution of two distinct types of microprocessor circuit elements. The monolithic MOS devices, such as the 8080A/9080A, provide moderate performance, high density and low power usually in the form of a fixed instruction architecture. Bipolar devices, like the Am2901, on the other hand, make use of the very high performance available to implement microprogrammed architectures, with their concomitant flexibility. Density and power constraints have led to the development of "bitslice" bipolar devices which use multiple chips to obtain the data word length required by a specific application.

Advanced Micro Devices occupies a unique position in the industry in that both mainstream microprocessor chip sets are supported by the company. The 8080A/9080A, industry standard, 8-bit MOS microprocessor family of devices is described in this handbook. Other publications available from AMD describe the widely used Am2900 bipolar family.

Despite the wide publicity being given to the microprocessor, and despite the tremendous amount of material being published, there is a surprising lack of detailed technical information available to the system designer. Unfortunately, many designers have found that the sort of information which they need is not readily available. That is the area which this handbook addresses. It is not another introduction to microprocessors, for which the reader is referred to the many publications addressing that general requirement. Rather, it is an attempt to introduce the microcomputer system designer to the 8080A/9080A family of devices and offer some detailed design information to the designer already familiar with these circuits. Soon after the microprocessor was introduced, it became clear that one key to their application lay in support circuits. Early microcomputer designs required so many additional devices to make them useful that a substantial portion of the potential benefit was lost. Since that time, much work has been done in developing support circuits which greatly reduce the package count in microcomputer systems. It is this development, which is continuing at a rapid pace, as much as the dramatic decrease in the price of microprocessors, which has fueled the explosive growth in their utilization.

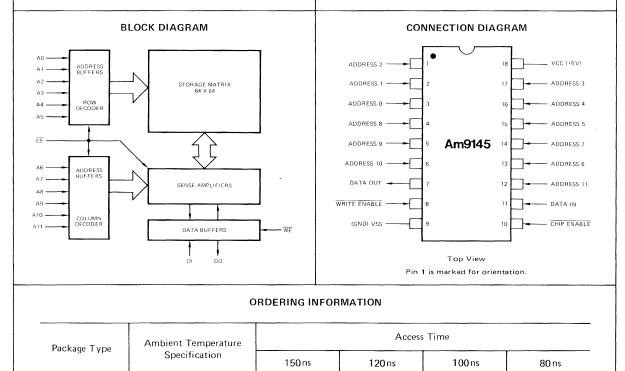

In addition to the standard 8080A/9080A family support circuits shown at the end of this chapter, Advanced Micro Devices is a leading manufacturer of standard Low-power Schottky MSI circuits. These products seem likely to have as profound an impact on microprocessor system design as they have had in TTL logic design. They offer further reduction in package count and power dissipation with no sacrifice in performance. Several of these devices which are particularly well suited to microcomputer design are included in the table and described in more detail later in the handbook. Another product area of critical importance to the microcomputer system designer is memories. Several configurations of 1K and 4K static read/write memories (RAMs) are available in addition to dynamic types. Also described are various read only memories, both mask programmed and erasable.

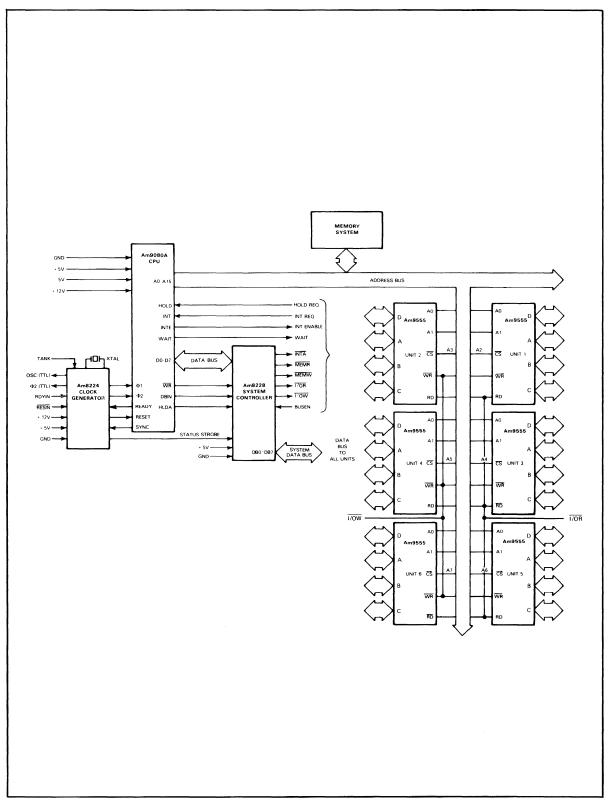

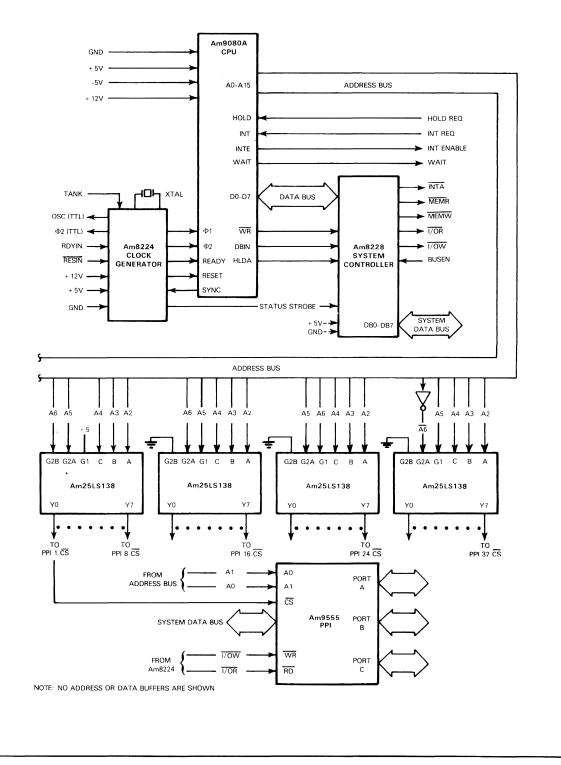

Presented in the following chapters of this handbook are detailed descriptions of the Am9080A central processing unit and the associated clock generator and system controllers. Three important input/output interfaces are then presented followed by two groups of support circuits. Following these will be found a chapter on memory devices and a selection of application notes.

Additional technical information regarding all AMD products may be obtained from local Field Applications Engineers or from factory Applications Groups.

### **MICROPROCESSOR & SUPPORT CIRCUITS**

| AMD Part Number  | Description                                          | Availability |

|------------------|------------------------------------------------------|--------------|

|                  | CPU                                                  |              |

| Am9080A/-2/-1/-4 | 0 to + 70°C                                          | Now          |

| Am9080A/-2/-1    | -25 to +85°C                                         | Now          |

| Am9080A/-2       | -55 to +125°C                                        | Now          |

| STATIC REA       | D/WRITE RANDOM ACCESS                                | MEMORIES     |

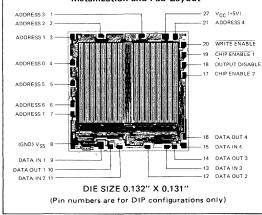

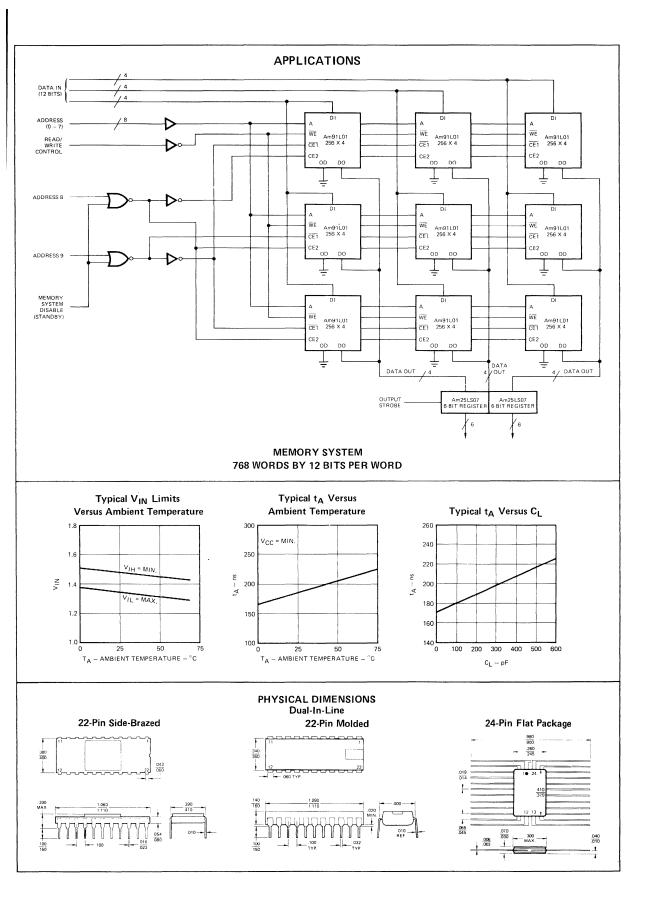

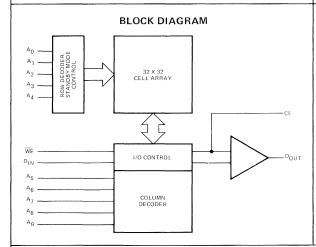

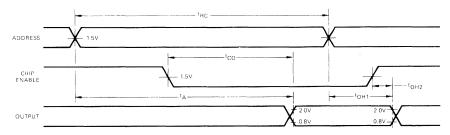

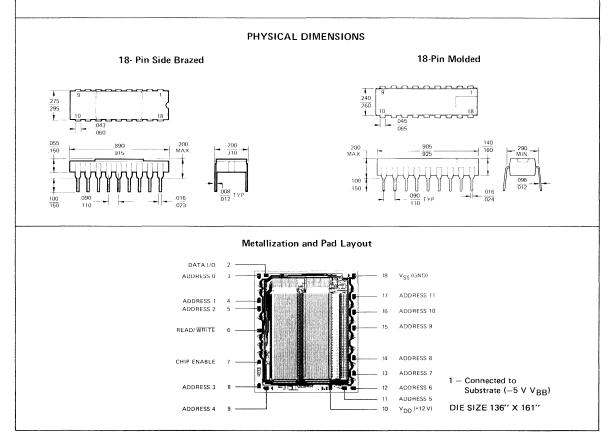

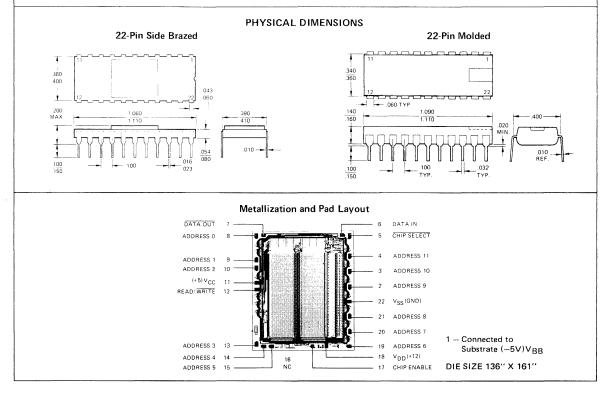

| Am91,01A/B/C/D   | 256 x 4, 22 Pin                                      | Now          |

| Am91L01A/B/C     | 256 x 4, 22 Pin                                      | Now          |

| Am9102A/B/C/D    | 1K x 1, 16 Pin                                       | Now          |

| Am91L02A/B/C     | 1K x 1, 16 Pin                                       | Now          |

| Am9111A/B/C/D    | 256 x 4, 18 Pin                                      | Now          |

| Am91L11A/B/C     | 256 x 4, 18 Pin                                      | Now          |

| Am9112A/B/C/D    | 256 x 4, 16 Pin                                      | Now          |

| Am91L12A/B/C     | 256 x 4, 16 Pin                                      | Now          |

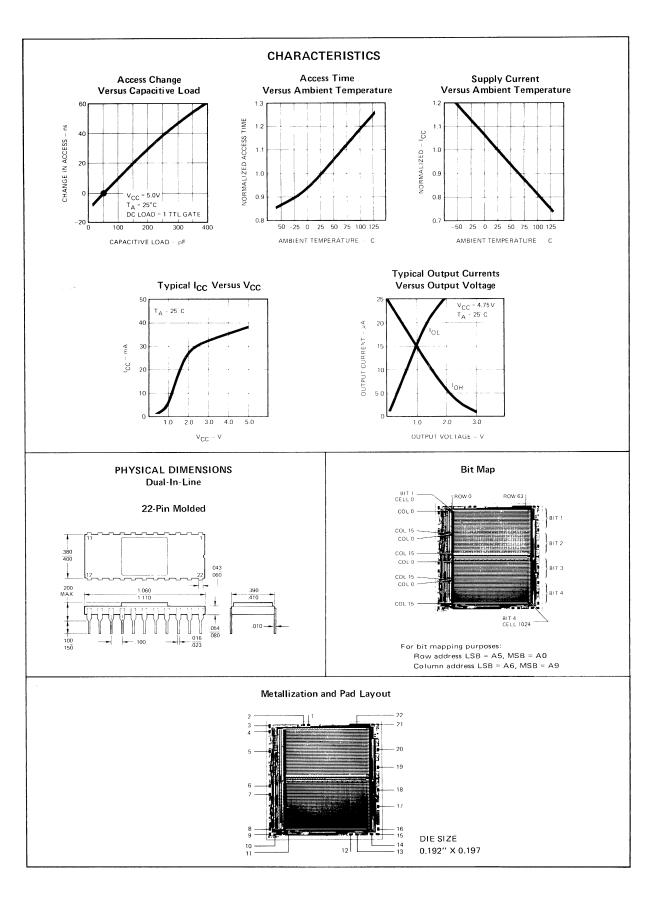

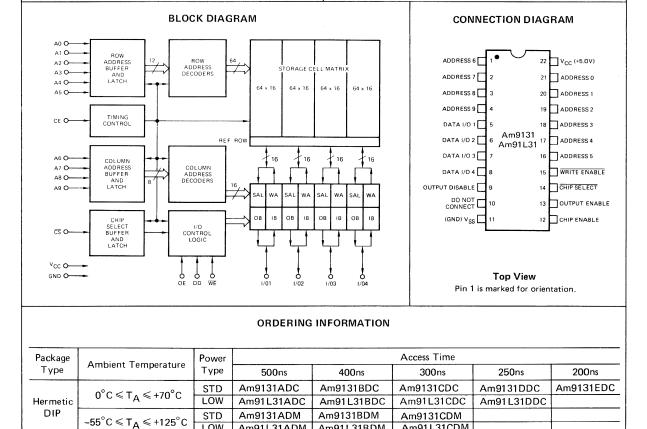

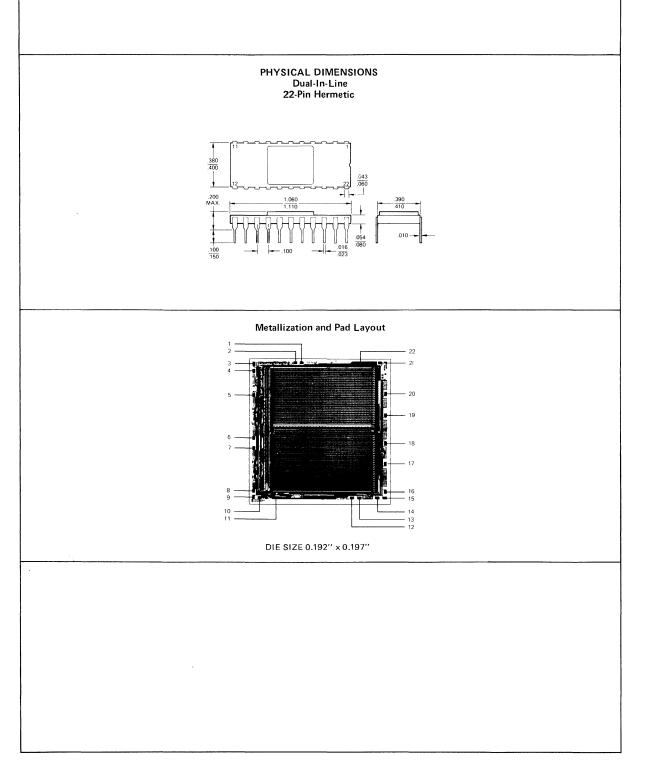

| Am9131A/B/C/D/E  | 1K x 4, 22 Pin                                       | Now          |

| Am91L31A/B/C/D   | 1K x 4, 22 Pin                                       | Now          |

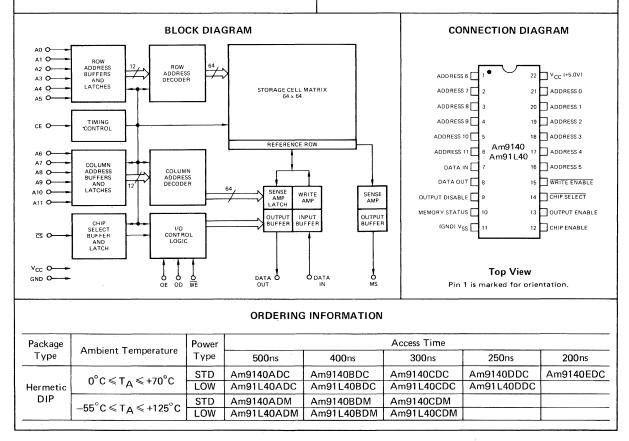

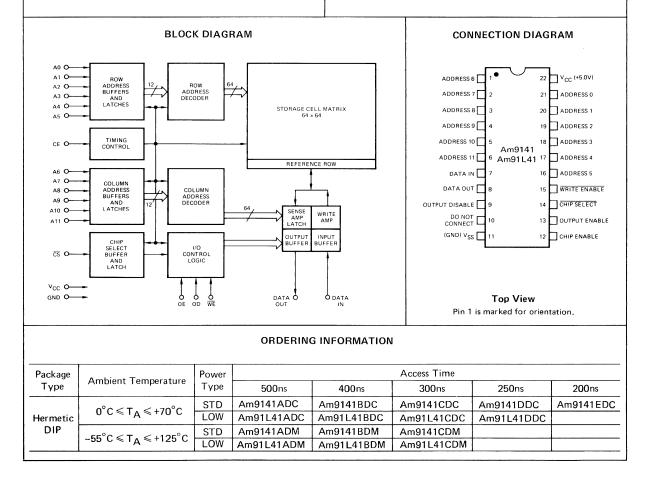

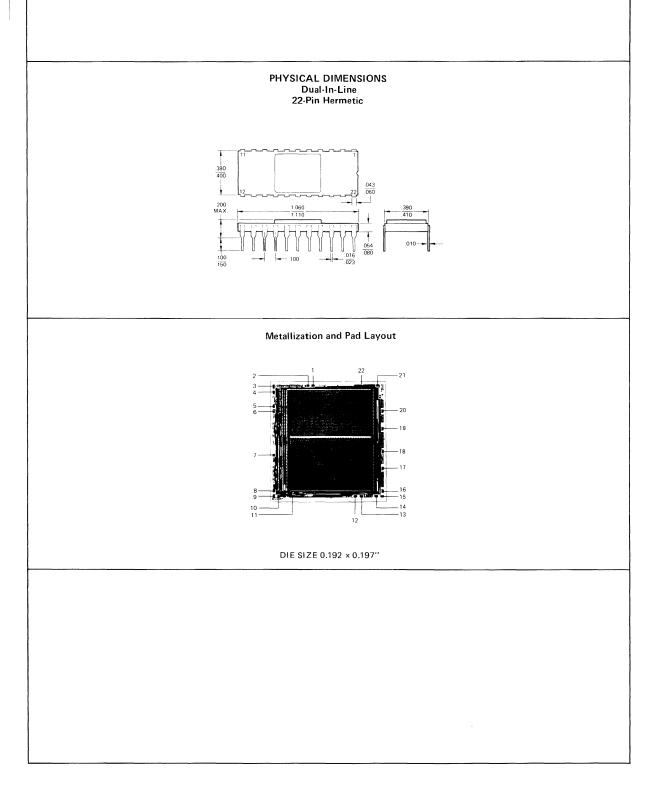

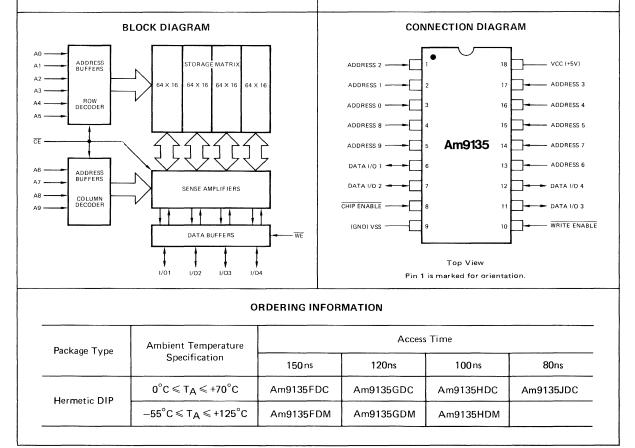

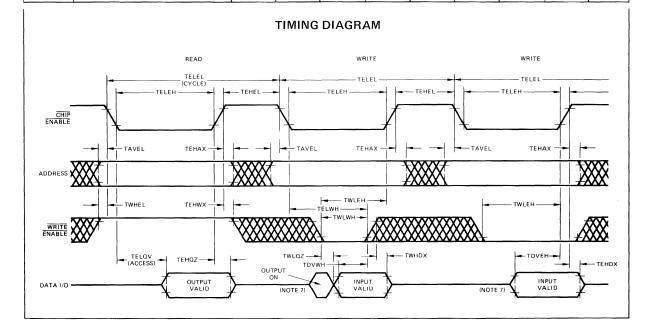

| Am9141A/B/C/D/E  | 4K x 1, 22 Pin                                       | Now          |

| Am91L41A/B/C/D   | 4K x 1, 22 Pin                                       | Now          |

| DYNAMIC RE       | AD/WRITE RANDOM ACCES                                | S MEMORIES   |

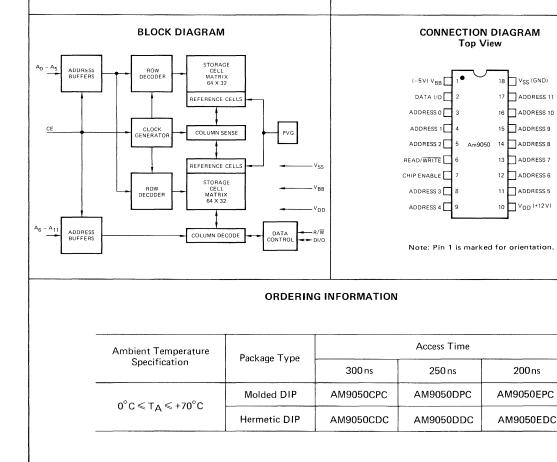

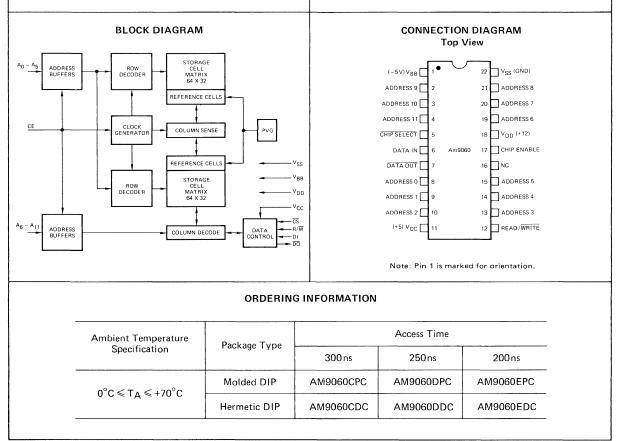

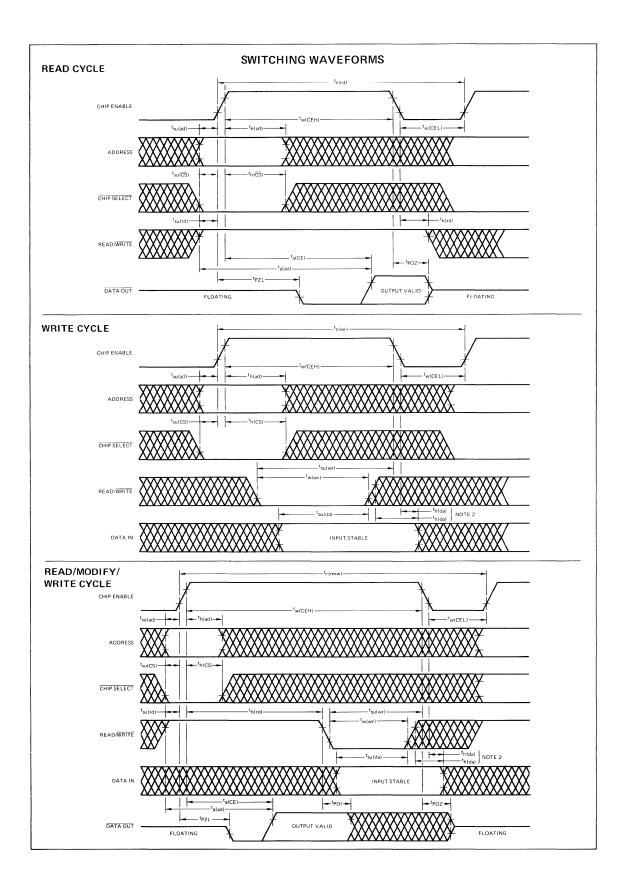

| Am9050C/D/E      | 4K x 1. 18 Pin                                       | Now          |

| Am9060C/D/E      | 4K x 1, 22 Pin                                       | Now          |

| MASK PRO         | OGRAMMABLE READ-ONLY                                 | MEMORIES     |

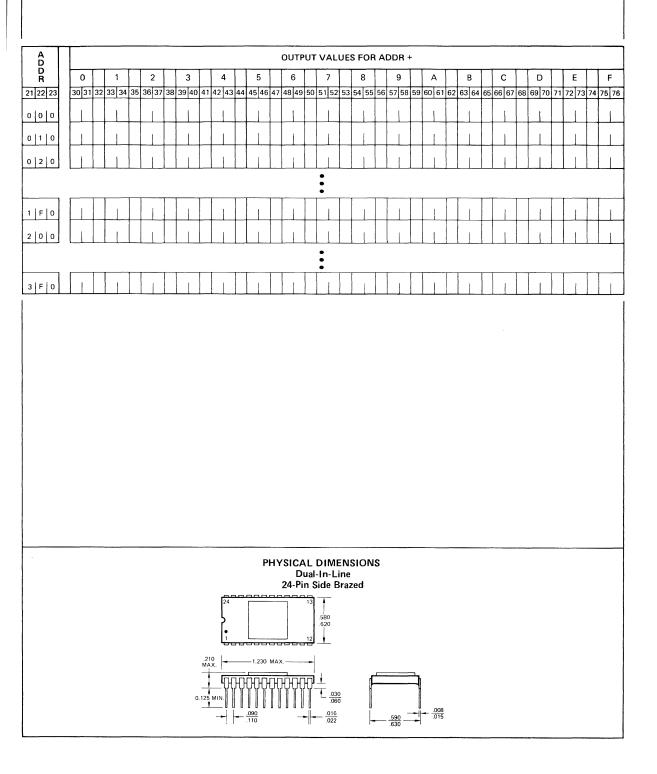

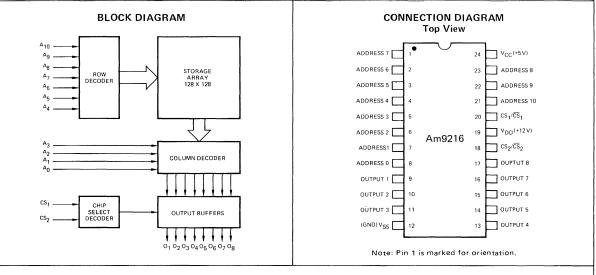

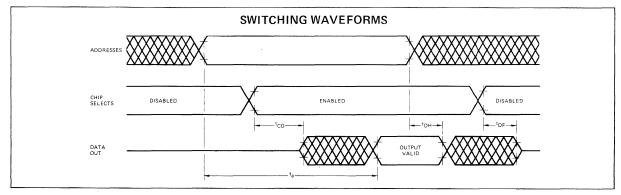

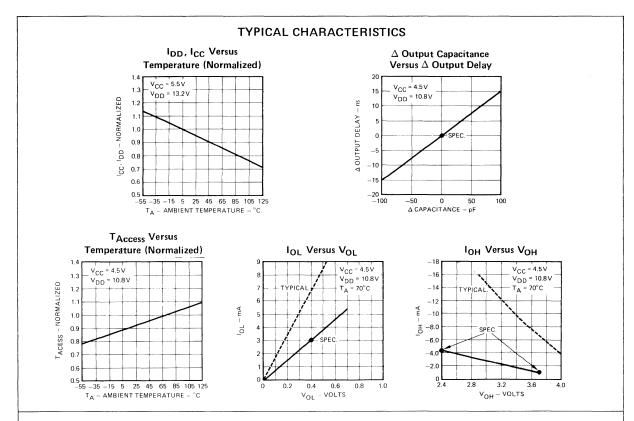

| Am9208B/C/D      | 1K x 8, 250 nsec max                                 | Now          |

| Am9216B/C        | 2K x 8, 300 nsec max                                 | Now          |

| Am8316A          | 2K x 8, 850 nsec max                                 | Now          |

| Am8316E          | 2K x 8, 550 nsec. max.                               | Now          |

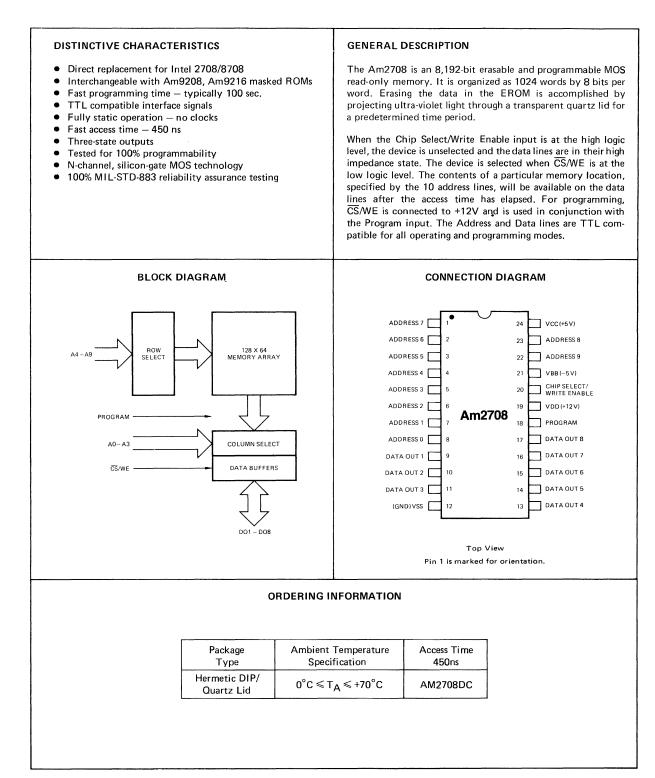

| ER               | ASABLE READ-ONLY MEMO                                | RIES         |

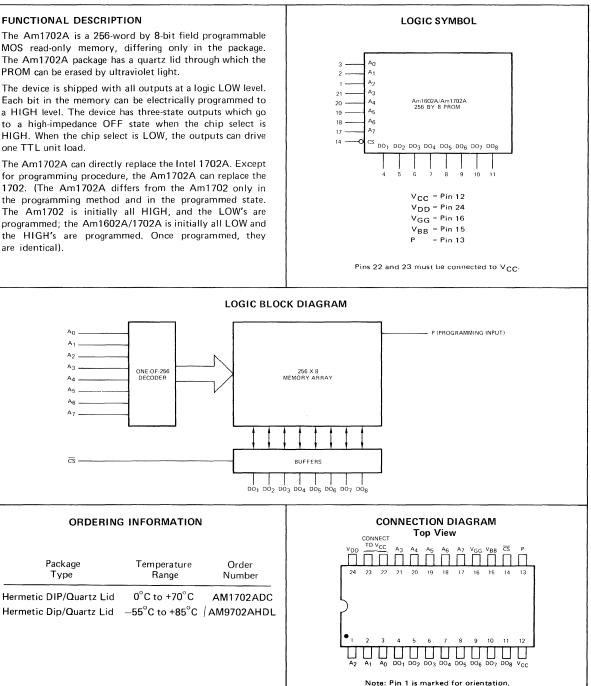

| Am1702A          | 256 x 8.10 µsec                                      | Now          |

| Am2708           | 1K x 8, 450 nsec                                     | 1st Q 197    |

|                  | ec 2 = 380 nsec -1 = 320<br>8=400 nsec C=300 nsec D= |              |

| AMD Part Num | ber Description                | A           | vailability |

|--------------|--------------------------------|-------------|-------------|

|              | SECOND SOURCE SUPP             | ORT         |             |

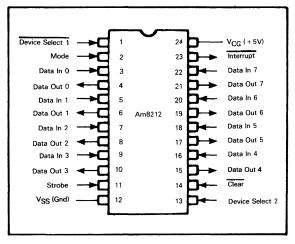

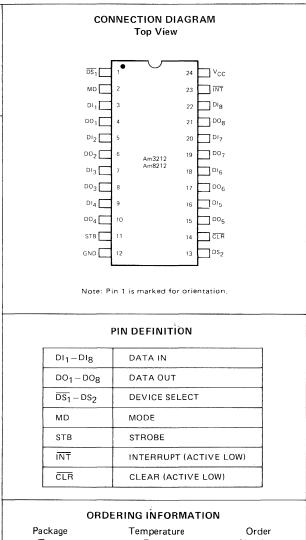

| Am8212       | 8-bit I/O Port                 |             | Now         |

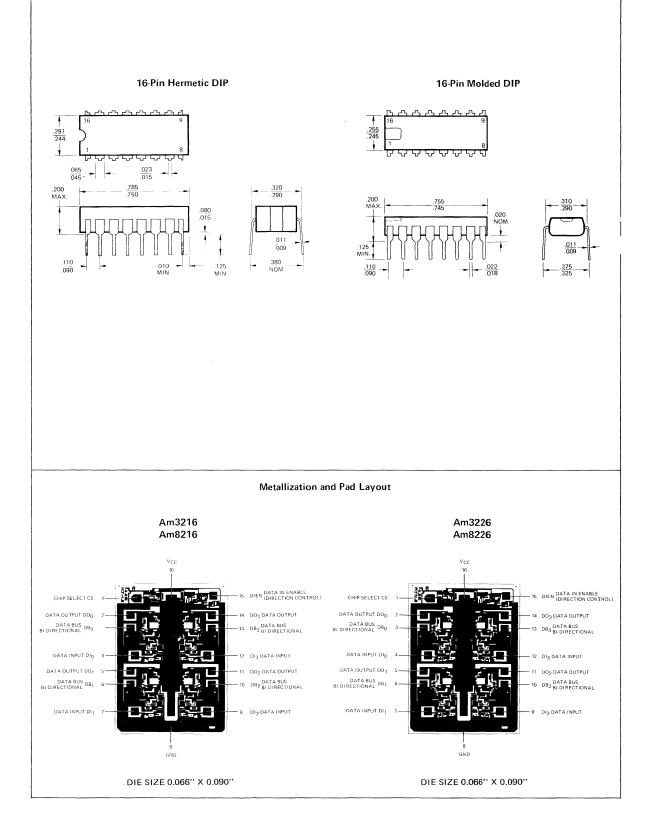

| Am8216       | Non-Inverting Bus Transceiver  |             | Now         |

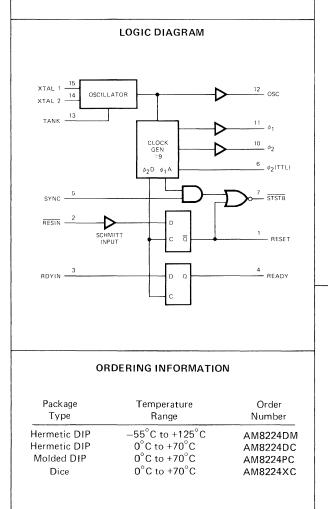

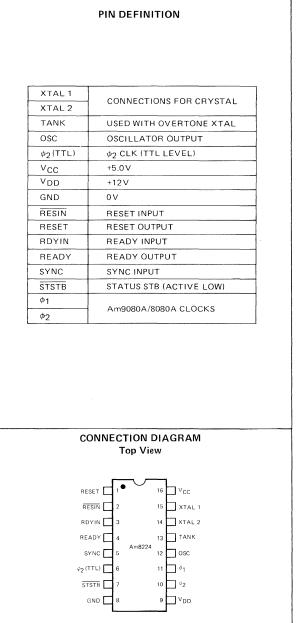

| Am8224       | Clock Generator                |             | Now         |

| Am8226       | Inverting Bus Transceiver      |             | Now         |

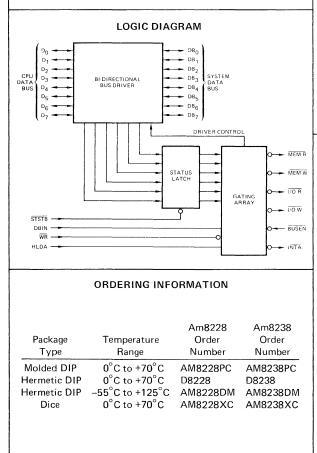

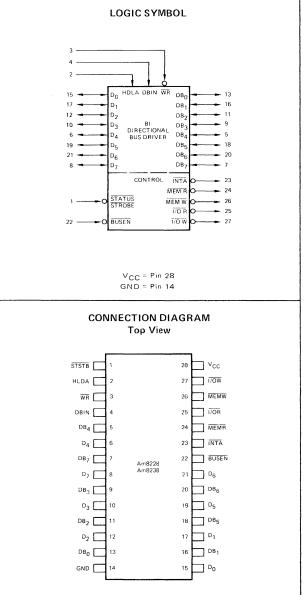

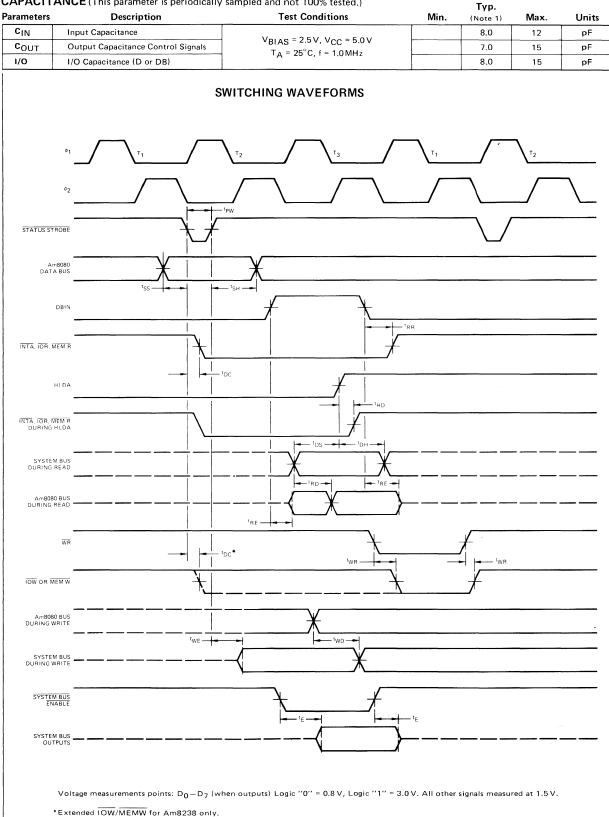

| Am8228       | System Controller              |             | Now         |

| Am8238       | Extended Write System Control  | ler         | Now         |

| Am8251       | Prog. Communications Interface | 9           | Now         |

| Am8255       | Prog Peripheral Interface      |             | Now         |

| Am8257       | er                             | 3rd Q 197   |             |

|              | IMPROVED SUPPOR                | Γ           |             |

|              |                                | REPLACES    |             |

| Am8224-4     | High-Speed Generator           | N/A         | Now         |

| Am8238-4     | High-Speed System Controller   | N/A         | Now         |

| Am9511       | Arithmetic Processing Unit     | N/A         | 3rd Q 1977  |

| Am9517       | Multi-mode DMA Controller      | 8257        | 3rd Q 1973  |

| Am9519       | Universal Interrupt Controller | 8259        | 3rd Q 1973  |

| Am9551/-4    | Prog Communications Interface  | 8251        | Now         |

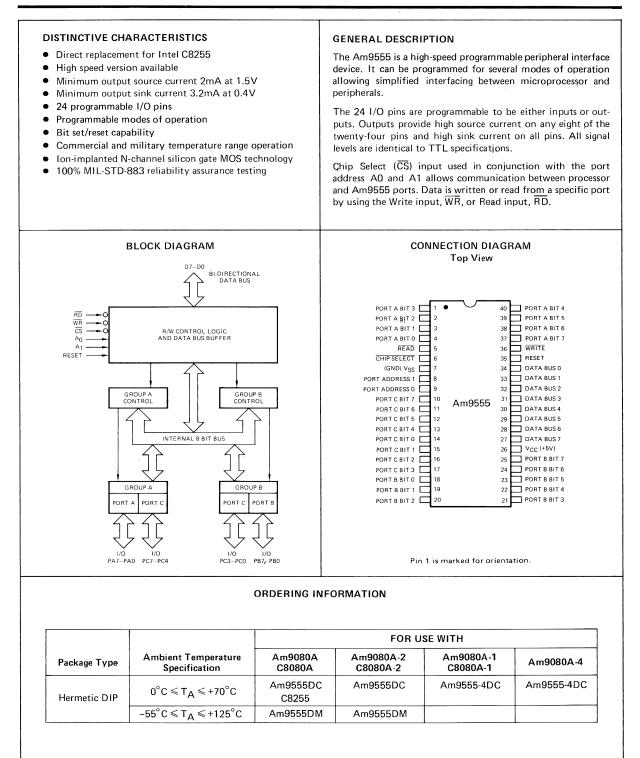

| Am9555/-4    | Prog Peripheral Interface      | 8255        | Now         |

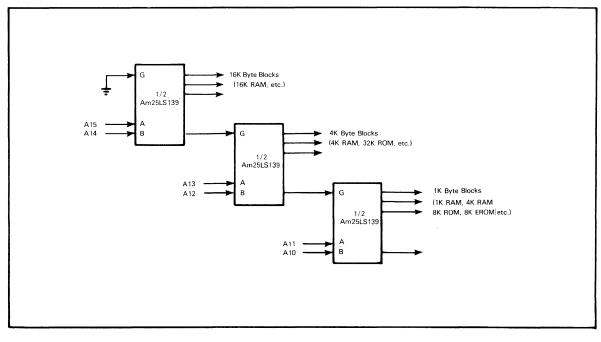

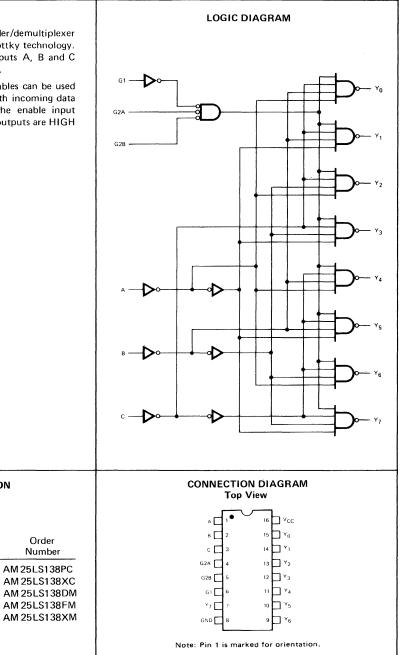

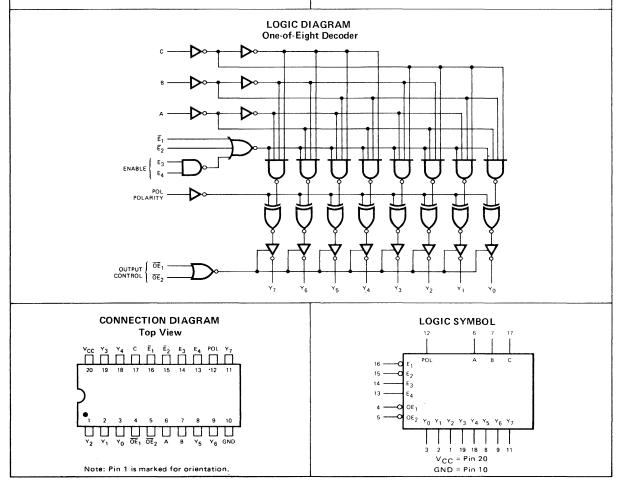

| Am25LS138    | 1-of-8 Decoder                 | 8205        | Now         |

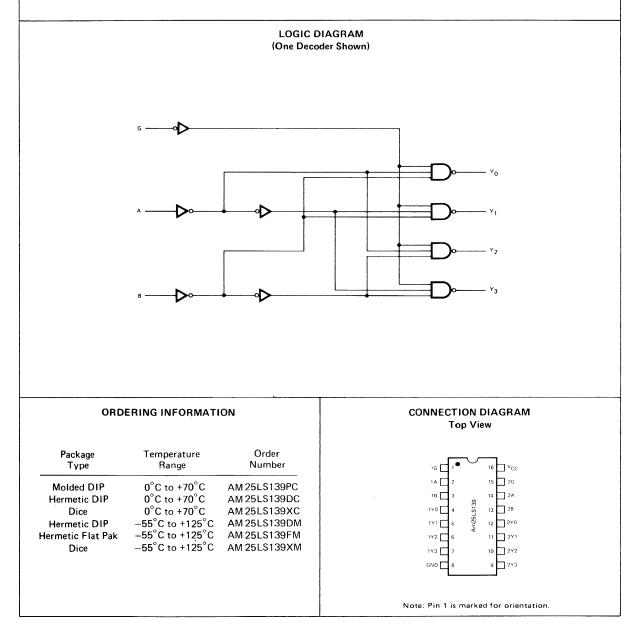

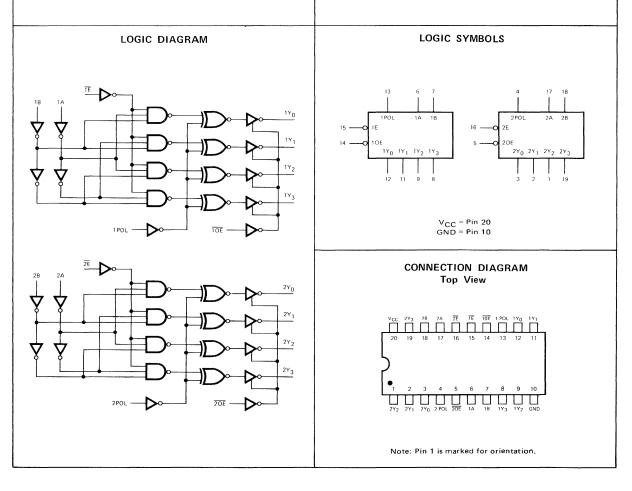

| Am25LS139    | Dual 1-of-4 Decoder            | 8205        | Now         |

| Am25LS273    | 8-bit Common Clear Register    | N/A         | 2nd Q 197   |

| Am25LS373    | 8-bit Transparent Latch        | 8212        | 4th Q 1977  |

| Am25LS374    | 8-bit 3-State Register         | 8212        | Now         |

| Am25LS377    | 8-bit Common Enable Register   | 8212        | 2nd Q 197   |

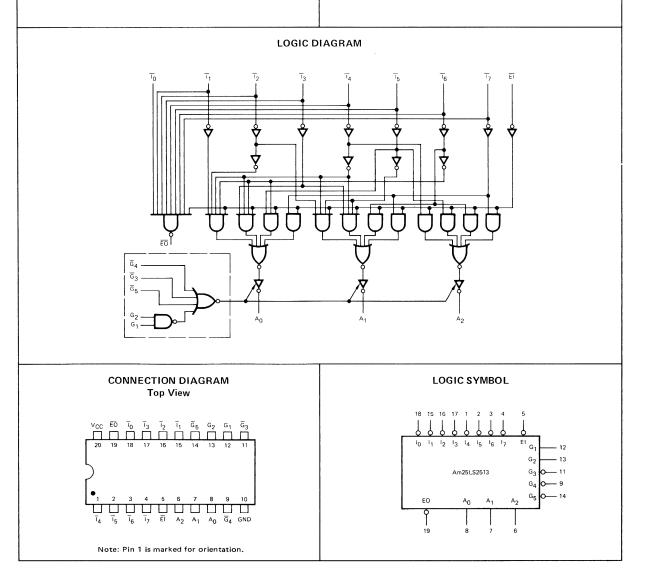

| Am25LS2513   | Priority Encoder               | 8214 & 8212 | Now         |

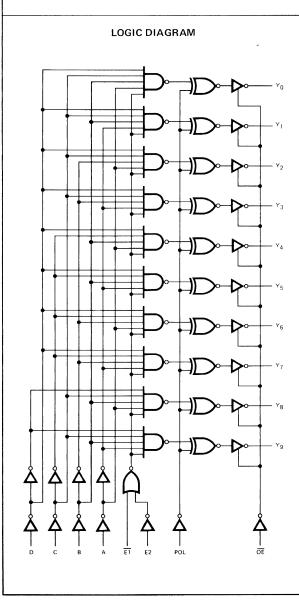

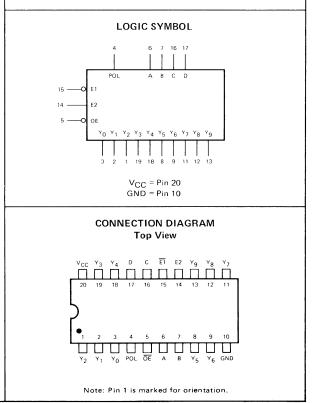

| Am25LS2537   | 1-of-10 3-State Decoder        | 8205 (2)    | Now         |

| Am25LS2538   | 1-of-8 3-State Decoder         | N/A         | Now         |

| Am25LS2539   | Dual 1-of-4 3-State Decoder    | N/A         | Now         |

\*All combine high performance and low power in space saving 20-pin package.

### Chapter 2 8080A/9080A FUNCTIONAL DESCRIPTION

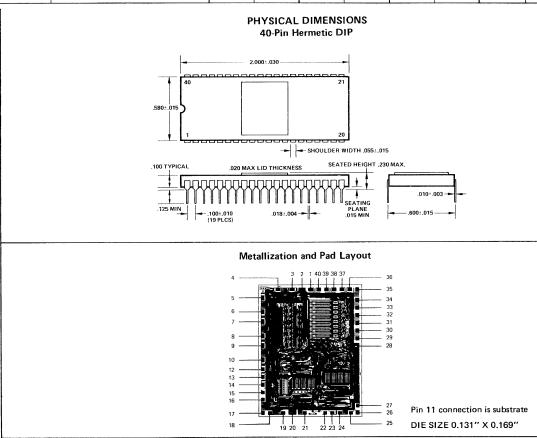

The Am9080A family of devices are complete, general-purpose, monolithic digital processors with a fixed instruction set and 8-bit parallel arithmetic logic and registers. The entire Arithmetic and Logic Unit, internal registers and instruction decoding and execution logic are contained within the microprocessor, which is pin and function compatible with the 8080A. The Am9080A versions feature improvements resulting from the use of the latest in N-channel, silicon gate, lonimplanted Metal-Oxide Semiconductor technology.

Four versions of the Am9080A are currently offered, providing instruction cycle times of 2, 1.5, 1.3 and 1.0  $\mu$ sec. In addition to providing the highest speed 8080A compatible device available, the improved processing technology provides significantly smaller products that dissipate much less power than the original 8080A. Features of the Am9080A microprocessors include:

• Full functional replacement for 8080A, 8080A-1, 8080A-2.

- Maximum power dissipation of 829 milliwatts.

- Instruction cycle times to 1  $\mu$ sec.

- Military versions for full temperature range with a 2.0 and a 1.5 µsec instruction cycle time.

- 3.2 mA of sink current capability on output connections.

- 100% reliability assurance testing to MIL-STD-883 standard on all products, commercial or military.

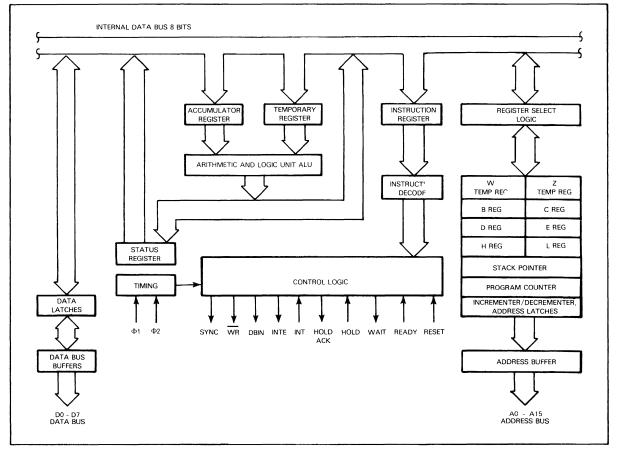

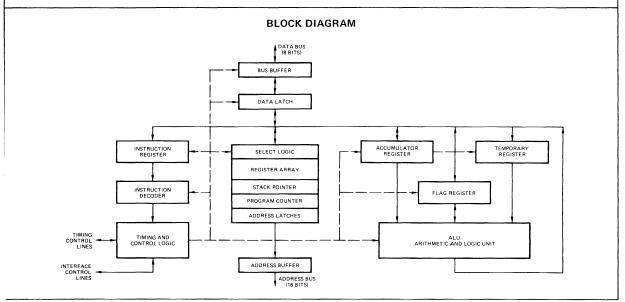

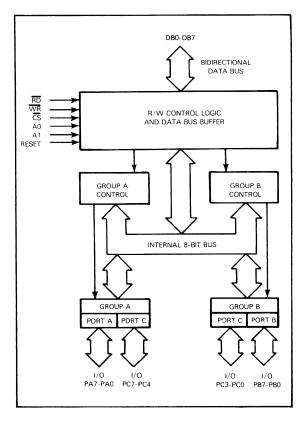

### FUNCTIONAL ORGANIZATION OF THE Am9080A CPU

Three groups of signals are provided by the Am9080A to transmit data and controls between the Central Processing Unit, memory and input/output logic. The first is an 8-bit parallel Data Bus; its function is to transmit both instructions and data to and from the CPU. A 16-bit Address Bus identifies any one of 65,536 (64K) memory locations during a memory access operation. The Address Bus may also be used to address peripheral devices during the execution of input/output

FIGURE 2-1 Am9080A FUNCTIONAL BLOCK DIAGRAM

instructions. The third group of signals includes ten control lines to synchronize the operation of the CPU with memory and input/output logic.

As illustrated in Figure 2-1, the 9080A microprocessor contains control and data processing logic.

#### Control Logic

Control logic coordinates the sequences of operations that are performed on a step-by-step basis as clock pulses are applied to the microprocessor. The data processing functions operate on the data in accordance with whatever instruction is being executed by the microprocessor.

The Instruction Register, Instruction Decoder, Timing, and Control Unit comprise the control logic of the microprocessor.

The Instruction Register receives those contents of the Data Bus which are obtained from memory during the first machine cycle of every new instruction. This 8-bit value is interpreted as the operation code (opcode) of an instruction. The Instruction Decoder monitors the outputs of the Instruction Register and establishes the sequence of events that follow. This sequence of events constitutes execution of the remainder of the instruction. For example, if the byte loaded into the Instruction Register during the first machine cycle is interpreted as the first byte of a 2-byte instruction, then the necessary control sequences will be established to cause a second memory access during the next machine cycle, to obtain the second byte of the instruction. The Instruction Decoder will then cause the contents of the data byte obtained during the second machine cycle to be routed to the appropriate internal logic so as to cause the desired function to be executed. The Timing and Control Logic generates the internal and external timing sequences necessary for controlling operations of the CPU.

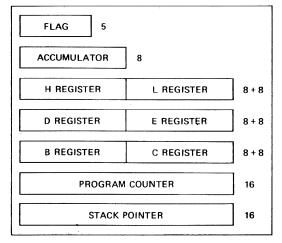

#### Registers

The register section of the processor consists of:

- An 8-bit Accumulator

- A Status Register

- Two Temporary Registers, W and Z

- $\bullet$  Three register pairs consisting of Registers B and C, D and E, H and L

- A Stack Pointer

- A Program Counter

The Accumulator is the primary source and destination for data being operated on by the Arithmetic and Logic Unit (ALU). ALU operations also modify Status Register bits; Status Register bits can be tested by the program being executed in order to define subsequent conditional logic.

The Temporary Registers hold values used during the execution of certain instructions. They are transparent to the programmer in that no instructions specifically address these registers as a source or destination.

Some instructions access the general register pairs independently as 8-bit registers; other instructions link them together as 16-bit register pairs (B and C, D and E, H and L).

The 16-bit Stack Pointer allows the programmer to reserve any area within the 64K bytes of Memory Space for use as a Last In/First Out (LIFO) stack memory. This permits efficient handling of program subroutines and intermediate storage of data. The Stack Pointer maintains the address of the next available stack location in memory. Whenever information is pushed onto the stack, the Stack Pointer is incremented, and when information is removed from the stack, the Stack Pointer is decremented. This organization of the Stack in general purpose memory allows the programmer to construct system software with an indefinite number and depth of stacks. The Stack program memory and data memory usually share a memory space; however, it is possible to create a separate addressable memory space solely for the use of the stack.

The Program Counter provides a 16-bit address that always points to a memory location from which the next instruction object code byte will be obtained. The Program Counter is automatically incremented after each instruction byte is fetched, thereby pointing to the next sequential memory location. Some instructions modify the Program Counter contents by inserting a new 16-bit address, thereby causing the next instruction byte to be obtained from a non-sequential location.

#### Arithmetic and Logic Unit (ALU)

The Arithmetic and Logic Unit contains all logic which performs operations on data. Registers whose data contents are operated on are included within the Arithmetic and Logic Unit; these include the Accumulator, the Status Register, an Accumulator latch and a Temporary Register.

The Accumulator is a programmable register which has been described; it is the primary source and destination for data operated on by the ALU; however, actual data operations are performed on the contents of Accumulator latches. The Temporary Register holds operands that are not stored in an addressable register.

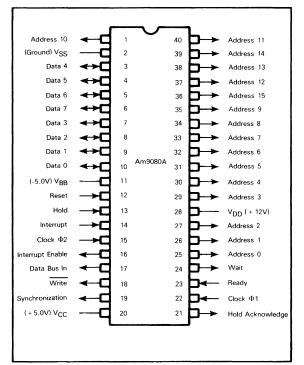

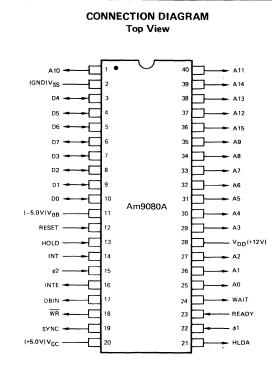

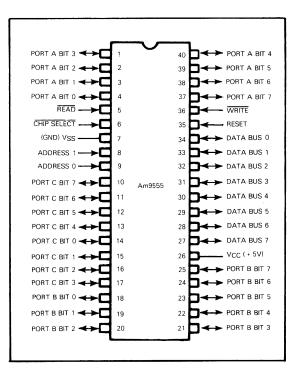

#### INTERFACE SIGNALS

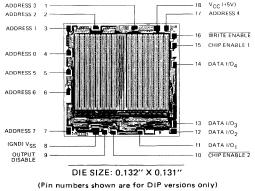

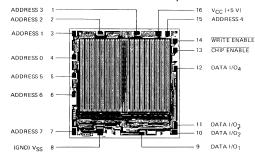

FIGURE 2-2 8080A/9080A CONNECTION DIAGRAM

The interface signals and connections to the Am9080A are shown in Figure 2-2.

#### Power

Four connections are provided for applying power to the Am9080A CPU:

| VSS | Pin 2  | 0 Volts    |

|-----|--------|------------|

| VBB | Pin 11 | -5 Volts   |

| Vcc | Pin 20 | + 5 Volts  |

| VDD | Pin 28 | + 12 Volts |

#### Inputs

#### Clocks ( $\Phi$ 1, $\Phi$ 2; Input)

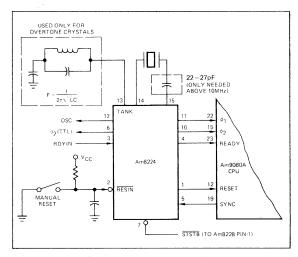

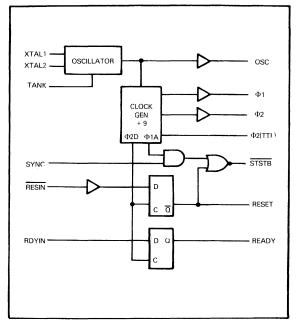

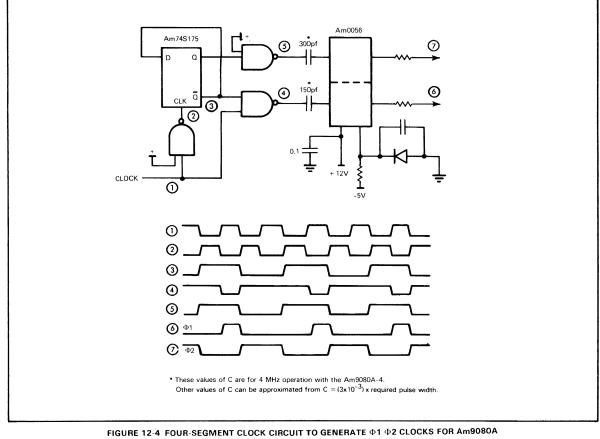

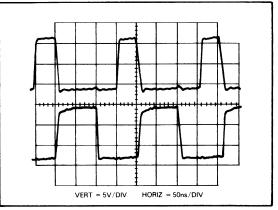

A two-phase nonoverlapping clock system is used to provide the basic timing for the Am9080A CPU. These are the only high level signals required by the processor and are conveniently provided by the Am8224 Clock Generator.

#### Reset (RESET, Input)

The Reset signal is used to initialize the microprocessor by performing the following seven functions:

1) Suspends all normal internal operations.

- 2) Clears the Program Counter.

- 3) Clears the Instruction Register.

- 4) Clears the INTE flip-flop.

- 5) Clears the HLDA flip-flop, thereby removing the microprocessor from a Hold state.

- 6) Clears the Halt state.

- 7) Forces the timing generator to assume the M1, T1 state when Reset is removed.

General registers within the CPU are not cleared when Reset is activated. The Reset line must be activated for a minimum of three full clock periods.

#### Hold (HOLD, Input)

The HOLD signal causes the CPU to enter the Hold state. The Hold state places Data and Address Busses in the high impedance state. This allows external circuits such as Direct Memory Access controllers to utilize the Data and Address Busses for purposes of transferring information to or from memory or I/O circuits, without CPU intervention.

#### Interrupt (INT, Input)

INT is the interrupt request signal. This signal can be used by external devices to notify the CPU that they require service.

#### Ready (READY, Input)

The READY input provides a means for the Central Processing Unit to enter a Wait state and allow extra time for external circuits to respond to requests by the processor. The signals applied by the CPU to the Address and Data Busses are maintained during the Wait state. The Ready signal may be held at the low level indefinitely, the processor remaining in the Wait state until the end of the  $\Phi$ 1 clock cycle after Ready becomes active.

#### Data 0 - Data 7 (DO - D7, Bidirectional)

The eight data lines, D0 through D7, are multiplexed bidirectional data lines over which both data and controls are transferred between the CPU and external circuits. The Data Bus drivers within the CPU are placed in the high impedance state before data are transmitted from external devices to the CPU.

#### Outputs

#### Address 0 - Address 15 (A0 - A15, Output)

The 16 address lines A0 through A15, provide for accessing up to 65,536 (64K) possible memory locations. The low order eight bits, A0 through A7, and the high order eight bits, A8 through A15, are used also for addressing one of 256 input or output ports. When the Input or Output instructions are executed, an 8-bit I/O port address appears at both the low and high order eight bits.

#### Interrupt Enable (INTE, Output)

The INTE signal indicates the state of the interrupt enable flipflop contained in the CPU logic. It indicates whether the CPU will recognize interrupts or not. A high output indicates that the internal interrupt mechanism is enabled.

#### Data Bus In (DBIN, Output)

DBIN is an active high signal; it indicates that the Data Bus is conditioned to read from the external circuits into the CPU. DBIN is used by external logic to gate data from an external source onto the Data Bus.

#### Write (WR, Output)

The  $\overline{WR}$  signal indicates to external memory and I/O circuits that the CPU has placed eight bits of data on the Data Bus during the current cycle. This signal is an active low logic level.

#### Synchronization (SYNC, Output)

The positive-going SYNC pulse appears during the first clock period of each new instruction cycle executed by the CPU. It indicates that the processor status is available on the Data Bus.

#### Hold Acknowledge (HLDA, Output)

HLDA appears in response to the Hold input request signal and indicates that the Data and Address Busses have been placed in their high impedance states.

#### Wait (WAIT, Output)

The WAIT line is activated by the CPU to indicate to external circuits that the CPU has entered the Wait state.

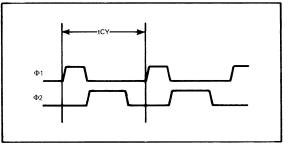

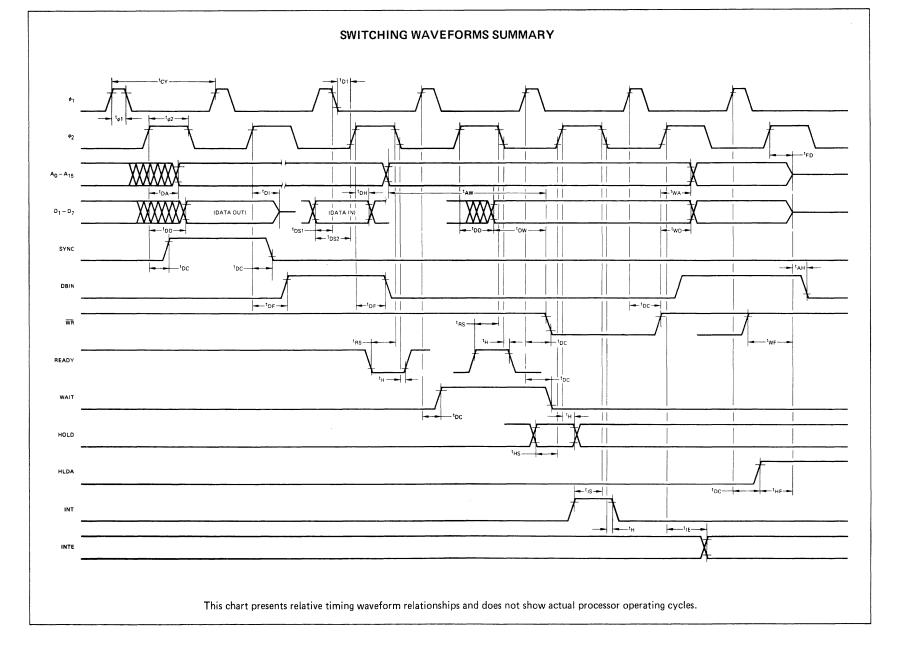

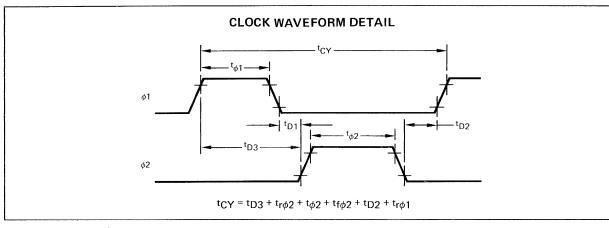

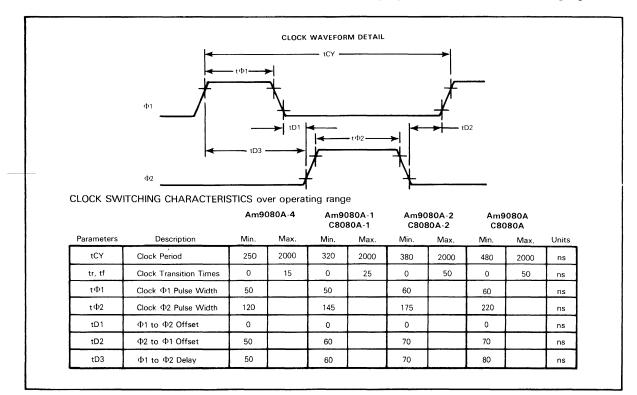

#### CLOCKING

The Am9080A uses a two-phase clock,  $\Phi 1$ ,  $\Phi 2$ , to control the CPU functions. The clock signals  $\Phi 1$  and  $\Phi 2$  are generated externally and applied to the CPU circuit. All other timing functions for the microprocessor are generated within the CPU.

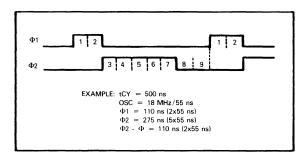

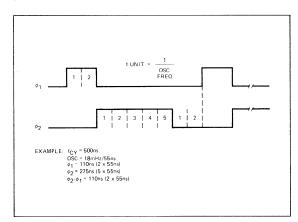

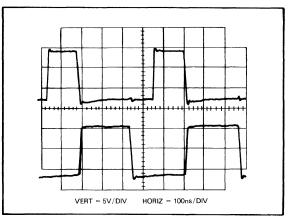

FIGURE 2-3  $\Phi$ 1 AND  $\Phi$ 2

The clock period is measured as the interval of time between the leading edges of successive  $\Phi$ 1 pulses. The  $\Phi$ 2 pulse is generated between  $\Phi$ 1 pulses such that  $\Phi$ 1 and  $\Phi$ 2 are not high concurrently (see Figure 2-3). There is a delay from the end of  $\Phi$ 2 to the start of the next  $\Phi$ 1.

#### **MACHINE CYCLES**

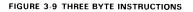

Functions performed by the Am9080A CPU while executing instructions take place in intervals consisting of three, four or five clock periods referred to as a machine cycle. Instructions require at least one, and as many as five machine cycles to complete execution.

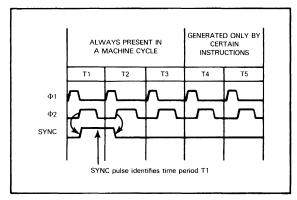

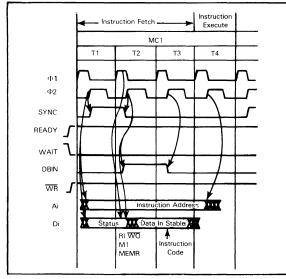

FIGURE 2-4 MACHINE CYCLE TIMING

Figure 2-4 shows consecutive clock periods, T1 through T5, in a machine cycle. The SYNC pulse is generated by the processor from the basic timing inputs. It begins with the leading edge of  $\Phi 2$  during clock period T1 and ends with the leading edge of  $\Phi 2$  in clock period T2.

Clock periods T1, T2 and T3 of the machine cycle are used to execute memory reference operations.

Data is read from, or written to memory during this period. The operation code for the instruction to be executed is always fetched during T1, T2 and T3 in the first machine cycle (M1). In subsequent machine cycles T1, T2 and T3 will be used to read additional bytes of the instruction object code, to read data operands, or to write information to memory. When present, clock periods T4 and T5 are used for internal CPU operations.

#### STATUS

The CPU specifies the operations that are to be performed during a machine cycle by placing status information on the Data Bus during the T1 clock period of each machine cycle. The status information functions as control signals to the rest of the microcomputer system, specifying events that are to occur during the machine cycle.

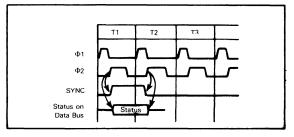

Data Bus status must be stored in external latches and decoded for use by the rest of the system circuits. The strobe signal for reading status is usually generated as the "AND" of SYNC and  $\Phi$ 1. Figure 2-5 shows the timing relationship of the status appearing on the Data Bus, slightly delayed from the leading edge of  $\Phi$ 2 in time period T1. Status remains static on the bus until the leading edge of the next  $\Phi$ 2, which occurs during the T2 clock period.

Table 2-1 shows the status signals which are generated to indicate various types of machine cycle.

FIGURE 2-5 STATUS OUTPUT DURING T1 OF EVERY MACHINE CYCLE

Only those status signals that are used to define the operation to be performed are active during a machine cycle. For example, the  $\overline{WO}$  signal (write pulse) is only active ( $\overline{WO}$ =0) in a machine cycle that requires information to be stored in an external memory location or output port.

#### MACHINE CYCLE OPERATION AND TIMING

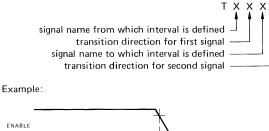

The Am9080A executes eleven different types of machine cycles. One to five of the machine cycles may be executed sequentially to perform operations required by the instruction being executed. Nine of the machine cycles are described in the following paragraphs. Timing diagrams are included with the descriptions and a schematic notation is included in each timing diagram to explain the function performed during each clock period.

TABLE 2-1 Am9080A STATUS

| DATA BUS BIT                          | D0   | D1 | D2    | D3   | D4  | D5         | D6  | D7   |

|---------------------------------------|------|----|-------|------|-----|------------|-----|------|

| STATUS SIGNAL                         | INTA | WO | STACK | HLTA | OUT | <b>M</b> 1 | INP | MEMR |

| Instruction Fetch                     | 0    | 1  | 0     | 0    | 0   | 1          | 0   | 1    |

| Memory Read                           | 0    | 1  | 0     | 0    | 0   | 0          | 0   | 1    |

| Memory Write                          | 0    | 0  | 0     | 0    | 0   | 0          | 0   | 0    |

| Stack Read                            | 0    | 1  | 1     | 0    | 0   | 0          | 0   | 1    |

| Stack Write                           | 0    | 0  | 1     | 0    | 0   | 0          | 0   | 0    |

| Input Read                            | 0    | 1  | 0     | 0    | 0   | 0          | 1   | 0    |

| Output Write                          | 0    | 0  | 0     | 0    | 1   | 0          | 0   | 0    |

| Interrupt Acknowledge                 | 1    | 1  | 0     | 0    | 0   | 1          | 0   | 0    |

| Halt Acknowledge                      | 0    | 1  | 0     | 1    | 0   | 0          | 0   | 1    |

| Interrupt Acknowledge<br>While Halted | 1    | 1  | 0     | 1    | 0   | 1          | 0   | 0    |

| Null                                  | 0    | 1  | 0     | 0    | 0   | 0          | 0   | 0    |

| The following de struction timing: | efinitions are used in the description of in-                                     | rpsl            | Least significant register of source register pair                                                                                                                                             |

|------------------------------------|-----------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А                                  | Accumulator                                                                       | S               | Source location (e.g., $rs = Source register$ ).                                                                                                                                               |

| AB                                 | Address Bus                                                                       | S               | Sign of Result = ALU7                                                                                                                                                                          |

| AC                                 | Auxiliary Carry = Carry propagation bet-<br>ween $2^3$ and $2^4$ stages.          | SR              | Status Register                                                                                                                                                                                |

| ACT                                | Accumulator Temporary Register                                                    | SSS             | Source location binary address                                                                                                                                                                 |

| CY                                 | Carry Status                                                                      | STATUS          | Status Conditions appearing on Data Bus at T2 $\Phi$ 1 time.                                                                                                                                   |

| d                                  | Destination location (e.g., rd = Destination register).                           | STATUS FLAGS    | Condition representing results of an ALU operation.                                                                                                                                            |

| DB                                 | Data Bus                                                                          | TEMP            | Temporary operand register                                                                                                                                                                     |

| ddd                                | Destination location address                                                      | VVV             | 3-bit binary value, 000 to 111 inclusive.                                                                                                                                                      |

| (H,L)                              | Contents of H and L registers, or memory location addressed by H and L registers. | VVVV            | 4-bit binary value, 0000 to 1111 inclusive.                                                                                                                                                    |

| ((H,L))                            | Designates the contents of a memory                                               | W,Z             | Temporary address registers                                                                                                                                                                    |

| ((1, 2))                           | location addressed by the 16-bit contents<br>of the H and L registers.            | Z               | Zero Result = $\overline{ALU7} \cdot \overline{ALU6} \cdot \overline{ALU5} \cdot \overline{ALU4}$<br>$\cdot \overline{ALU3} \cdot \overline{ALU2} \cdot \overline{ALU1} \cdot \overline{ALU0}$ |

| INST                               | Any instruction code byte                                                         | ()              | The contents of                                                                                                                                                                                |

| INTE                               | Interrupt Enable flip-flop                                                        | $\overline{()}$ | Complement of the contents of                                                                                                                                                                  |

| IR                                 | Instruction Register                                                              | (( ))           | The contents of the contents of. The con-                                                                                                                                                      |

| Opcode                             | Instruction operation code byte                                                   |                 | tents of the designated location in the in-                                                                                                                                                    |

| Operand                            | Operand of the instruction                                                        |                 | ner brackets are interpreted as an address<br>to a second location which supplies the 8-                                                                                                       |

| Р                                  | Parity = Odd number of 1s in ALU result.                                          |                 | bit operand used by the instruction.                                                                                                                                                           |

| РСН                                | Eight most significant bits of the Program Counter.                               | ←               | Receives. The notation () $\leftarrow$ means the location designation contained in the inner                                                                                                   |

| PCL                                | Eight least significant bits of the Program Counter.                              |                 | brackets is used as an address to which the operand will be stored.                                                                                                                            |

| port                               | I/O device address                                                                |                 | Goes to                                                                                                                                                                                        |

| r                                  | CPU register                                                                      | +               | Is exchanged with                                                                                                                                                                              |

| rd                                 | Destination register                                                              | +               | Arithmetic Addition                                                                                                                                                                            |

| rs                                 | Source register                                                                   | -               | Arithmetic Subtraction                                                                                                                                                                         |

| rp                                 | Register pair                                                                     | x               | Arithmetic Multiplication                                                                                                                                                                      |

| rpd                                | Destination register pair                                                         | Δ               | Logical AND                                                                                                                                                                                    |

| rps                                | Source register pair                                                              | V               | Logical OR                                                                                                                                                                                     |

| rpsh                               | Most significant register of source register pair                                 | ¥               | Logical Exclusive-OR                                                                                                                                                                           |

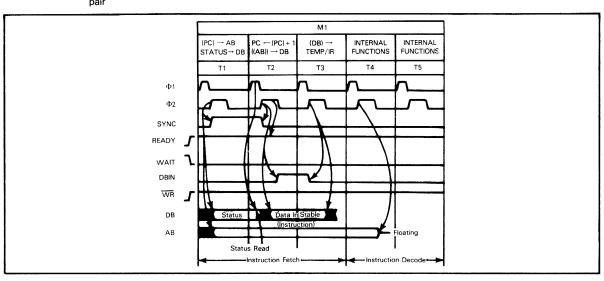

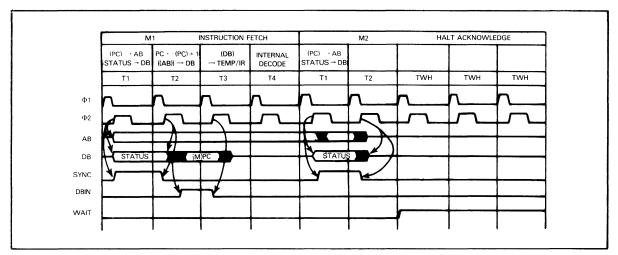

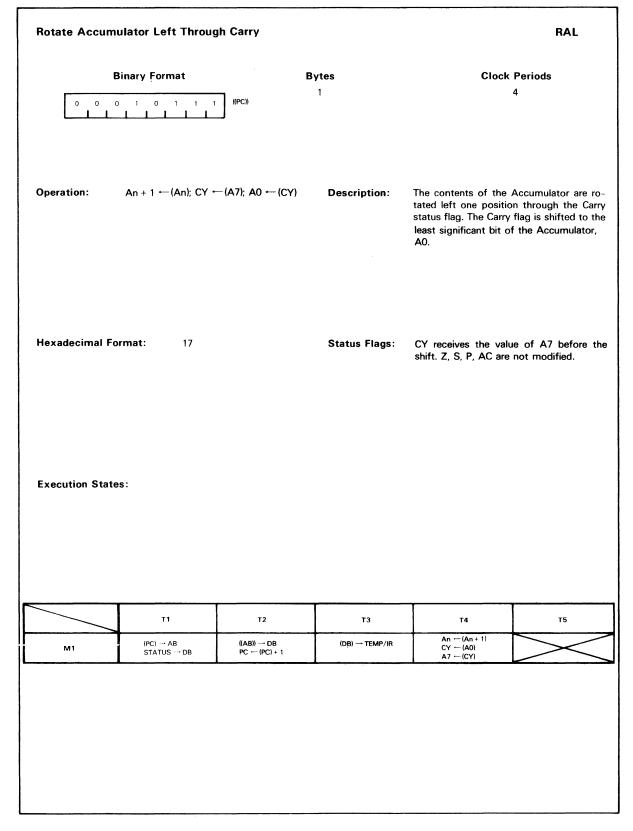

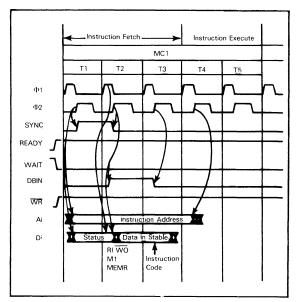

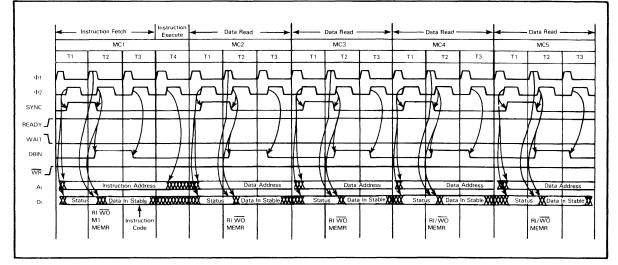

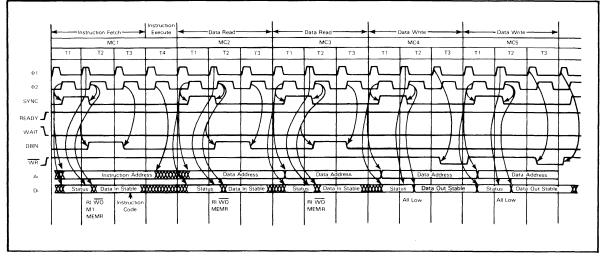

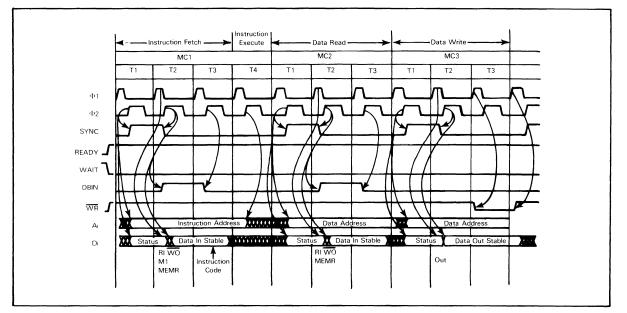

FIGURE 2-6 INSTRUCTION FETCH MACHINE CYCLE

#### **Instruction Fetch**

The first machine cycle during the execution of any instruction is the Instruction Fetch (M1) cycle. Figure 2-6 shows the timing and events that occur for each clock period in the Instruction Fetch machine cycle.

M1 begins with the leading edge of  $\Phi 1$  in clock period T1. SYNC is generated with the leading edge of the first  $\Phi 2$  in clock period T1. Shortly after this time the status information is placed on the Data Bus from the CPU. In order to generate control functions for the external system components, the status information must be latched in external circuits while SYNC is present.

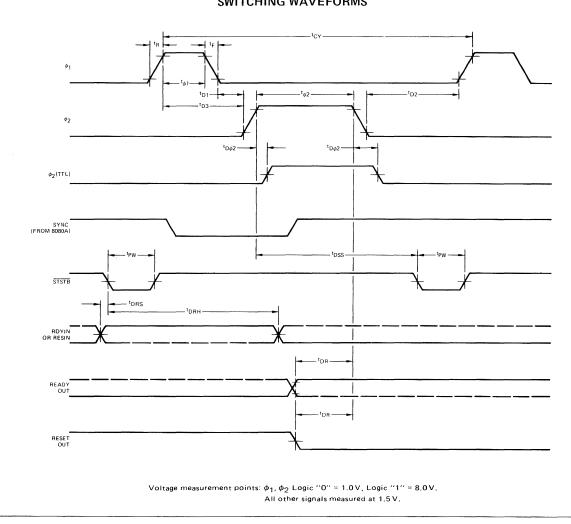

This is conveniently achieved by means of the Status Strobe  $(\overline{\text{STSTB}})$  signal generated by the Am8224. An alternative would be to use  $\Phi 1$  and SYNC to latch the status data.

Since M1 is the Instruction Fetch cycle, the only two status lines active are the M1 status (D5), indicating that this is a first byte instruction fetch, and the MEMR status (D7), indicating that a byte is to be supplied by external memory.

The Address Bus receives the contents of the Program Counter slightly after the leading edge of the  $\Phi 2$  in T1. The address signals remain active at the output of the Address Bus until after T3, when information received from the memory has been strobed into the Instruction Register.

The status signals on the Data Bus are deactivated with the leading edge of  $\Phi 2$  during clock period T2 to allow the instruction byte from memory to be transmitted to the CPU via the Data Bus. Internal decoding of the instruction takes place during clock periods T4 and T5.

Note that in Figure 2-6 the Ready signal is continuously high (active). In the event that slow memory components are used in conjunction with the CPU, the Ready signal can be used to introduce an extra delay between T2 and T3 to allow time for the memories to respond. A more complete discussion of the effect of the Ready signal is contained in the Wait state description.

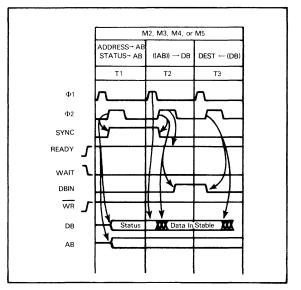

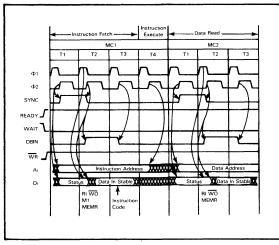

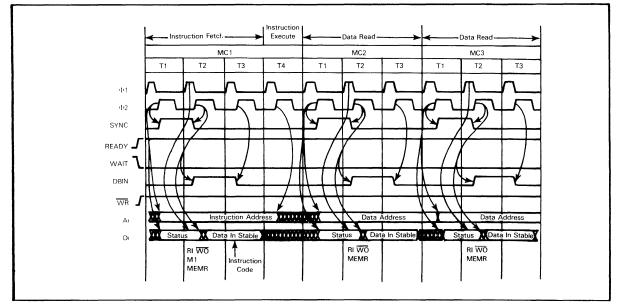

FIGURE 2-7 MEMORY READ MACHINE CYCLE

#### Memory Read

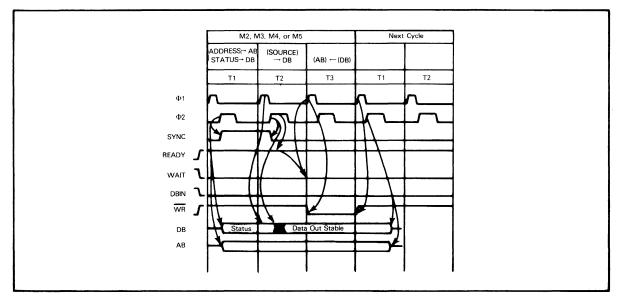

Figure 2-7 shows the timing for the Memory Read machine cycle.

The Memory Read machine cycle is identical to the Instruction Fetch cycle above except that the M1 status signal is not activated. Memory Read only occurs in the M2, M3, M4 or M5 machine cycles. The only active status signal on the Data Bus is the MEMR signal. Table 2-1 shows WO as a binary 1, but that is the inactive state for this signal.

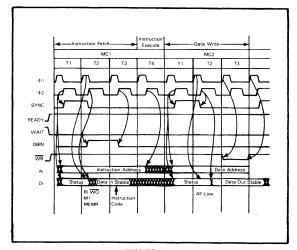

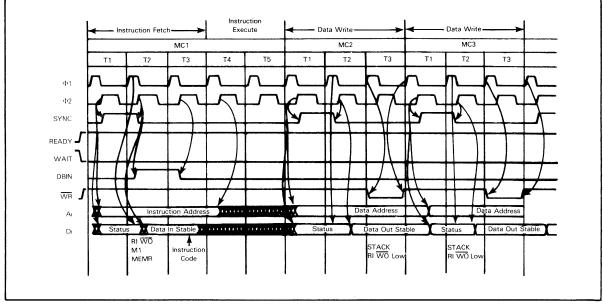

#### **Memory Write**

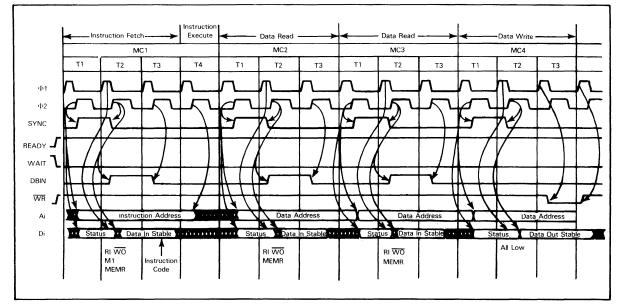

The Memory Write machine cycle differs from the Memory Read machine cycle in that information generated within the CPU is written into the designated memory location. The timing for the Memory Write machine cycle is shown in Figure 2-8.

Figure 2-8 MEMORY WRITE MACHINE CYCLE

Notice that the machine cycle designated in Figure 2-8 can be any machine cycle in which a write operation takes place. The timing waveforms are similar to those for the Instruction Fetch or Memory Read machine cycles except for the operation of the Data Bus. Status appears on the outputs of the Data Bus during clock period T1 and is removed slightly after the leading edge of  $\Phi 2$  in clock period T2. In the Memory Read cycle or Instruction Fetch cycle, the CPU causes the Data Bus drivers to go to the high impedance state. In the Memory Write cycle the data to be written to memory is immediately placed on the Data Bus, remaining present during the entire T3 period.

The Data Bus is returned to the high impedance state with the leading edge of  $\Phi 2$  in clock period T1 of the next machine cycle.

#### Stack Read And Write

The timing for both the Stack Read and Stack Write machine cycles is identical to the Memory Read and Memory Write cycles. However, they are differentiated from standard Memory Read and Memory Write cycles by the presence of the Stack status signal (D2) during the T1 clock period.

The Stack status signal can be used to create a separate addressable memory space. One problem that is sometimes encountered when debugging programs incorporating a stack in main memory is that the stack increases without bound if the program is not functioning as intended. The results are usually rather dramatic and make it difficult to debug the program.

One way to prevent this is to differentiate between the areas of memory allocated to program data storage and stack storage. This can be accomplished by incorporating the Stack status signal into the memory chip select generation circuitry. The Stack status can be used to inhibit chip selects to nonstack areas of memory when a Stack Read or Stack Write machine cycle is being executed.

#### Input Read And Output Write

The waveforms of Figures 2-7 and 2-8 are also applicable to the timing for either an Input Read or Output Write machine cycle. These states are differentiated during the T1 machine period by the presence of the Input status signal (D6) in the case of an I/O read cycle, or the presence of the Out status signal (D4) in the event of the I/O write cycle.

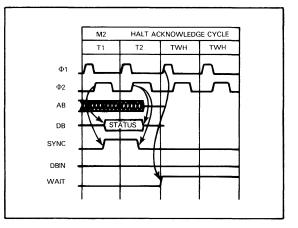

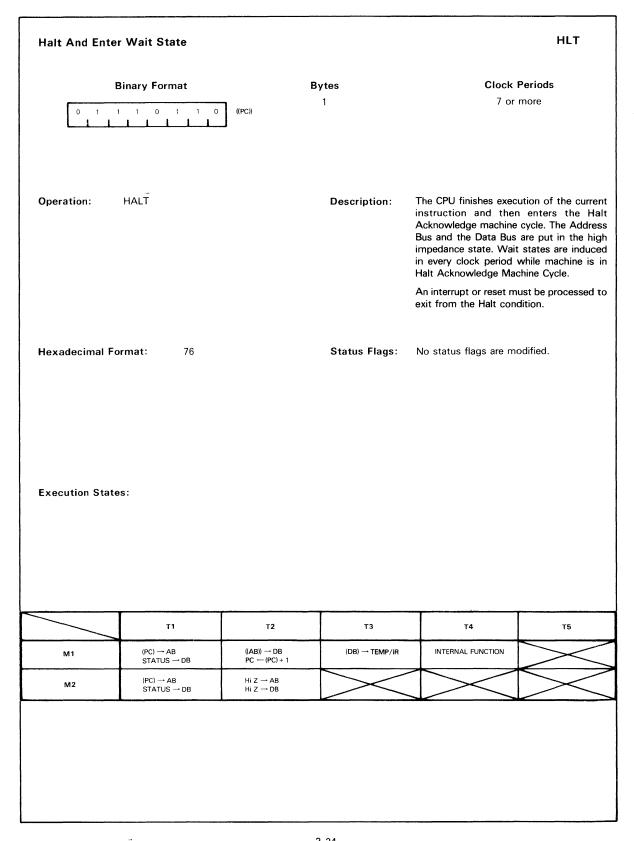

#### Halt Acknowledge

The Halt Acknowledge machine cycle is characterized by the presence of the MEMR (D7) and Halt (D3) status signals. All other status signals are inactive.

Figure 2-9 shows the timing for the Halt Acknowledge.

The Halt Acknowledge machine cycle can be entered only in response to execution of a Halt instruction.

There are three functions which can terminate the Halt Acknowledge machine cycle:

- Activating Reset causes the Am9080A to enter a new Instruction Fetch machine cycle with the Program Counter pointing to location 0.

- Activating the Hold input causes the CPU to enter the Hold state. When Hold is released the CPU will return to the Wait state, and the Halt Acknowledge machine cycle will continue.

- Activating the Interrupt signal when INTE is enabled. This causes the Interrupt Acknowledge machine cycle to be executed. Normal program processing will continue.

FIGURE 2-9 HALT ACKNOWLEDGE MACHINE CYCLE

Notice that the Interrupt Enable flip-flop (INTE) must be active in order to recognize the interrupt request that terminates the Halt Acknowledge state. The only way to terminate Halt if the Interrupt Enable flip-flop is reset when the Halt instruction is executed is to Reset.

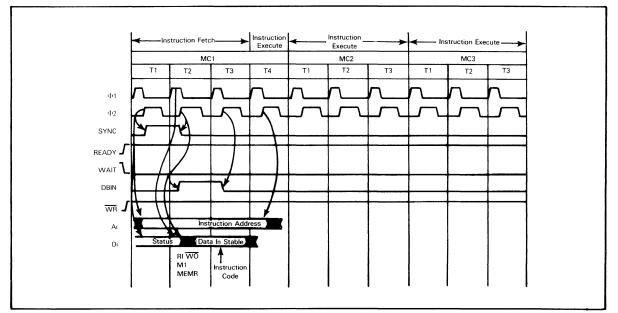

#### Null

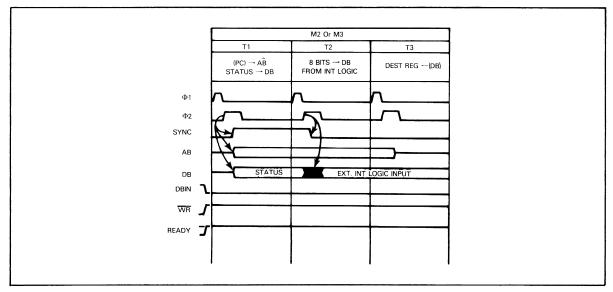

The Null machine cycle is entered only when an interrupt request has been acknowledged by the CPU. The CPU first enters the Interrupt Acknowledge machine cycle, and the external circuits respond by placing an instruction operation code on the Data Bus. If the CPU interprets the opcode as a 2- or 3byte instruction, one or two Null machine cycles respectively are generated. The Null machine cycles allow the interrupting circuit to supply the second and third bytes to the CPU. The instructions which may be used in response to the Interrupt Acknowledge machine cycle are discussed in the paragraphs on interrupt processing.

The operation and timing of the Null machine cycle is identical to the Memory Read machine cycle of Figure 2-7 except for the following:

- The Program Counter is not incremented in T2 of the Null cycle.

- MEMR is not generated; therefore the memory system does not respond.

Figure 2-10 shows the timing diagram for the Null machine cycle. All status bits are inactive.

#### **Am9080A MACHINE STATES**

The Am9080A, like all microprocessors, is a sequential state machine. The operation being performed by any particular clock pulse at any instant in time is determined by the internal control logic and the condition of the input signals applied to the microprocessor. The instantaneous condition of all internal control flip-flops is known as the current machine state. The execution of instructions proceeds as a sequence of machine states that are executed in synchronism with the microprocessor timing to complete the desired operation.

Note that machine states are not the same as machine cycles. States denote the internal conditions of the control flip-flops and may be present only for the duration of a single clock pulse. A machine cycle, on the other hand, is composed of several internal machine states. There are three machine states

FIGURE 2-10 NULL MACHINE CYCLE TIMING

which are important since they affect the operation of memories and other external components used in an Am9080A microcomputer system. These are the Wait, Hold and the Halt machine states.

The principle function of the Wait state is to insert a delay between T2 and T3 clock periods to allow time for slow external devices to respond to a read or write operation. The Hold state is utilized to disconnect the Am9080A CPU circuit from the microcomputer memory and I/O. This permits externally controlled operations such as DMA to gain control of the Address and Data Busses independently of the CPU. The Halt state causes instruction processing to cease.

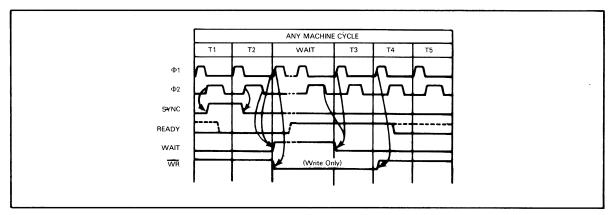

#### Wait State

Dynamic logic is used in the design of the Am9080A. This requires the application of continuous clock pulses with certain frequency and pulse width constraints. The  $\Phi 1$  and  $\Phi 2$  clocks cannot be delayed to accommodate external circuits. Instead, a Wait state is utilized to introduce delays during the execution of instructions. Two possible uses of the Wait state are:

- Insert a delay to accommodate the response time of slow memory or I/O circuits.

- Stop processing during machine cycles within an instruction to permit the functions about to be performed to be examined.

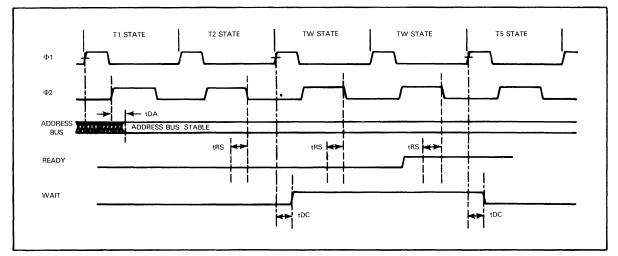

A Wait state will always consist of an integral number of clock periods. Figure 2-11 shows the timing for a Wait state inserted between T2 and T3.

#### **Use Of Ready**

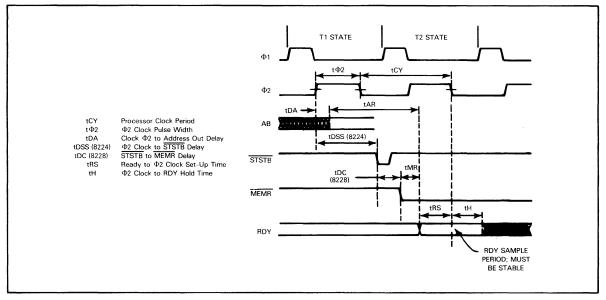

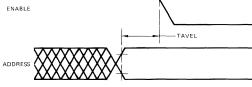

During a Memory Read cycle, the CPU can be forced to enter a Wait state if memory is too slow to provide the data within the required set-up time. The CPU samples the Ready input during a set-up time, tRS, which occurs within the T2 state just prior to the falling edge of  $\Phi 2$ . Therefore, indication of a Wait state requirement must be given via the RDY input, prior to the tRS time. This timing relationship is shown in Figure 2-12 along with associated parameters.

FIGURE 2-11 WAIT STATE TIMING

FIGURE 2-12 READY DECISION TIME

Normally, the earliest indication to the system that a Memory Read cycle is to be performed is when the  $\overline{\text{MEMR}}$  signal is activated. With this in mind, then the time period available for a decision to request a Wait state is:

$$tMR = tCY + t\Phi2-tDSS-tDC-tRS = \frac{tCY}{3} + t\Phi2-tDC-tRS$$

The time from the address being valid and stable to the RDY sample time is given by:

$tAR = tCY + t\Phi 2 - tDA - tRS$

In system designs which do not make use of Ready, memory speed must be such that data is valid at the CPU when required. A detailed discussion of memory timing, including derivation of maximum access times can be found in the application section of this handbook.

Table 2-2 indicates the values of tMR and tAR for the various versions of the Am9080A at different operating speeds.

#### **Hold State**

The Hold state causes the CPU to suspend the function it is executing and places the Address and Data Busses in the high impedance state. This allows DMA or other external functions to gain access to the system busses. The Hold state is activated by means of the Hold input signal to the CPU. The following events occur in response to a Hold request:

- 1) The processor completes execution of the current machine cycle.

- 2) The processor enters the Hold state and acknowledges this condition by activating the HLDA control signal from the CPU. This occurs with the leading edge of  $\Phi 1$  in period T3 if the machine cycle currently executing is not a Stack Write, Memory Write or Output Write cycle. If so, the Hold state is entered with the leading edge of the  $\Phi 1$ in the next clock period following T3.

- The processor places the Address Bus and the Data Bus in the high impedance state.

- The processor enters the Wait state within the Hold state until the Hold request input returns to a low input level.

| PROCESSOR<br>VERSION | tCY | tCY/3 | t Ф2<br>(5/9 tCY) | tDA | tDC | tRS | tMR | tAR |

|----------------------|-----|-------|-------------------|-----|-----|-----|-----|-----|

| Am9080A              | 480 | 160   | 266               | 200 | 60  | 120 | 246 | 426 |

|                      | 500 | 167   | 277               | 200 | 60  | 120 | 264 | 457 |

| Am9080A-2            | 380 | 127   | 211               | 175 | 60  | 90  | 188 | 326 |

|                      | 480 | 160   | 266               | 175 | 60  | 90  | 276 | 481 |

| Am9080A-1            | 320 | 106   | 177               | 150 | 60  | 90  | 133 | 257 |

|                      | 380 | 127   | 211               | 150 | 60  | 90  | 188 | 351 |

#### TABLE 2-2 WAIT STATE TIMING (IN NS)

Note the difference between this and a normal Wait state; the Address and Data Busses are in a high impedance state.

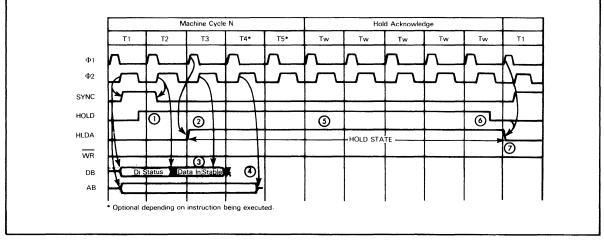

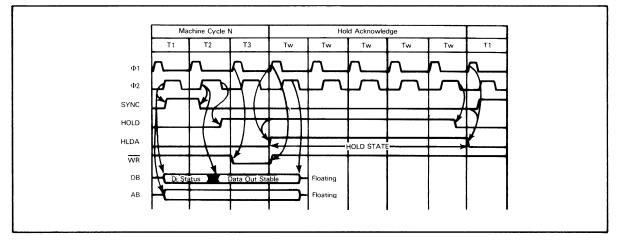

Figure 2-13A shows the timing when the current machine cycle is performing a read function. Notice the following events as indicated by numbers in the diagram:

- The Am9080A specification requires that the Hold signal be active for at least 140 nsec preceding the leading edge of Φ2. This requirement may be met by synchronizing the Hold signal with the trailing edge of Φ2.

- 2) The Hold state is entered with the leading edge of  $\Phi$ 1 in clock period T3. HLDA is activated.

- 3) The Data Bus is placed in the high impedance state by the leading edge of  $\Phi 2$  in T3.

- 4) The Address Bus is released by the leading edge of  $\Phi 2$  in T4.

- Internal functions are completed in T4 and T5 of the machine cycle, and the Wait state is entered and held until the Hold input is returned low.

- Hold is deactivated. The release of the Hold signal may be synchronized with the trailing edge of Φ2.

- The Hold state is terminated and the next machine cycle begins with a T1 period. This machine cycle is not necessarily an Instruction Fetch but could be the next machine cycle in an imcomplete instruction.

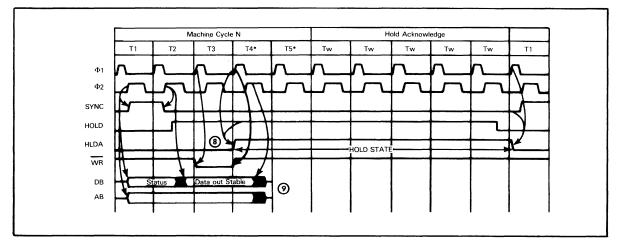

Figure 2-13B shows the Hold timing conditions when a write function is being performed. The two differences occur in events 8 and 9.

- 8) The Hold state is not entered until the leading edge of  $\Phi 1$  in T4.

- 9) Data supplied to the Data Bus remains active through T3. The Data Bus is placed in the high impedance state by  $\Phi 2$  in T4.

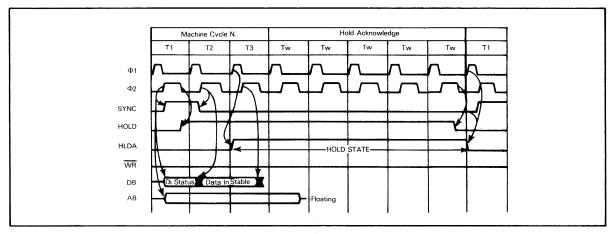

The Hold state for machine cycles requiring three clock periods is shown in Figure 2-14. All timing functions for both machine cycles performing a Read function and those performing a Write function are the same as the timing of Figure 2-13 except that the Wait state will be the next clock period after T3.

FIGURE 2-13A HOLD TIMING DURING FIVE TIME PERIOD READ OPERATIONS

FIGURE 2-13B HOLD TIME PERIOD DURING FIVE TIME PERIOD WRITE OPERATIONS

FIGURE 2-14A HOLD TIMING FOR READ IN A THREE TIME PERIOD READ MACHINE CYCLE

FIGURE 2-14B HOLD TIMING FOR ANY NON-READ OPERATION COMPLETED PRIOR TO ONSET OF HOLD STATE

#### Halt State

The Halt state introduces a delay in instruction processing by inserting Wait states in the Halt Acknowledge machine cycle, after the T2 clock period. The Halt state is differentiated from the Wait state in the following ways:

- The Halt state is initiated by executing the Halt instruction, whereas the Wait state is initiated by setting the Ready input low.

- Wait will occur in any machine cycle between T2 and T3. The Halt state occurs only in a Halt Acknowledge machine cycle. The Halt Acknowledge machine cycle is the M2 machine cycle when the instruction fetched in the M1 cycle is decoded as the Halt instruction.

- The Halt state can be terminated and program processing allowed to continue only if an interrupt is received or a Reset is applied to the processor.

During the Halt state the system bus is not floated; this contrasts with the Hold state during which the system bus is floated. Thus the Hold state can be used by external logic to gain control of the system bus, for example to perform Direct Memory Access operations. The Halt state stops all activity within the microcomputer system.

#### INTERRUPT PROCESSING

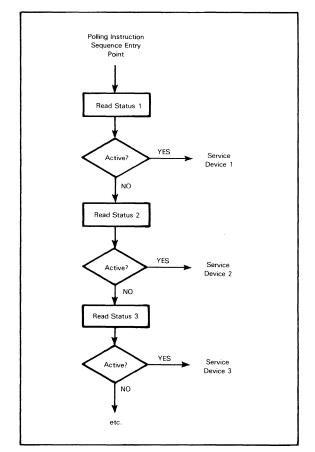

Interrupt capability is included in most microprocessors to increase performance (throughput). If interrupts were not available, the microcomputer program would have to periodically stop the task that it was performing and test each I/O device to determine if service is required. In microcomputers where I/O response time must be short, the rate at which the devices are tested must be much greater than the actual rate at which the I/O devices require service. As a consequence, the application processing capability of the microcomputer would be reduced considerably, especially as the number of devices grows.

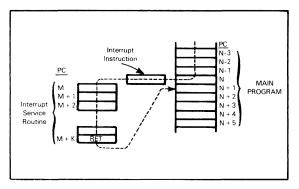

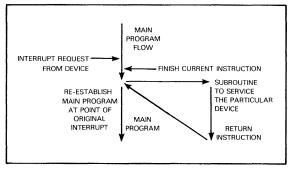

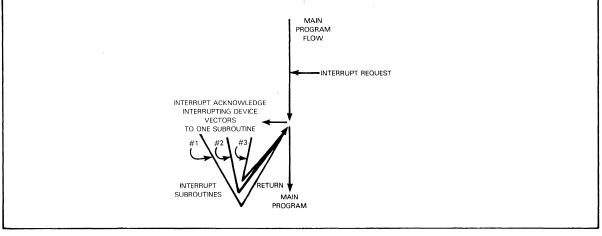

In the Am9080A, an interrupt causes a new instruction to be inserted into the program sequence being executed. This capability is usually used to terminate processing at the location to which the Program Counter was pointing when the interrupt occurred and resume executing instructions at a new location. The program which begins at the new location is called the "Interrupt Service Routine". When the interrupt service routine is completed, control is returned to the main program, and processing continues with the instruction in the interrupted program which would have been executed, had the interrupt not occurred. Figure 2-16 illustrates the interrupt scheme.

Figure 2-15 shows the timing for the Halt state.

FIGURE 2-15 HALT TIMING

FIGURE 2-16 INTERRUPT PROGRAM FLOW

Notice that the Program Counter is used to address instructions both in the main program and in the interrupt service routine. These are the events that occur to transfer control to the interrupt service routine:

- 1) INTE is high, and an active INT input is sensed by the processor during execution of instruction N.

- 2) Execution of instruction N is completed, including incrementing of the Program Counter to point to location N + 1.

- The Interrupt Acknowledge output is generated to signal the interrupting device that the processor has recognized the Interrupt input and is ready to process it.

- 4) INTE is reset.

- 5) The interrupting device supplies a Call or Restart instruction from which the address of the service routine (M) is determined.

- The Program Counter contents (N + 1) are stored on the stack as a consequence of executing the interrupt instruction.

- 7) Address M supplies the first instruction of the service routine and this is loaded into the Program Counter.

When the Interrupt Acknowledge machine cycle is generated, the interrupting external device supplies the instruction to be executed next. Notice that this instruction is not coded in either the application program or the interrupt service routine. It is an extra instruction inserted by external logic which requests the interrupt. Typical microcomputers designed with the Am9080A insert the Restart or one of the Call instructions onto the Data Bus in response to the Interrupt Acknowledge machine cycle; however, any instruction except XTHL can be used.

When the interrupt service routine is complete, control is transferred back to the main program by the following sequence of events:

- A Return instruction is executed at instruction M + K.

- The address of the next main program instruction (N + 1) is pulled from the stack and used to fetch an instruction.

- The instruction address is incremented and the result placed in the Program Counter.

#### Interrupt Control

Three interrupt control signals are provided by the Am9080A. These are:

- INT an input signal used by external devices to request an interrupt.

- INTE an output signal which indicates when the processor is, or is not accepting interrupts.

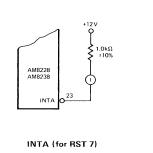

- INTA Interrupt acknowledge signal output in response to INT.

After INT is detected high, the processor will finish executing the current instruction and enter the Interrupt Acknowledge machine cycle. INTE is reset low.

INT may be reset low any time after the Interrupt Acknowledge machine cycle is started, but must be low before interrupts are enabled again. If the INT signal is not reset low before interrupts are re-enabled, it will be interpreted as a new interrupt and the interrupt acknowledge process will be repeated. The INTA signal appears on D0 during the Interrupt Acknowledge machine cycle; it may be used to reset the interrupt request.

Any of the following three conditions will clear INTE, disabling interrupts:

- RESET input being activated.

- The rising edge of  $\Phi 2$  during T1 in the Interrupt Acknowledge machine cycle.

• Executing the Disable Interrupt instruction.

#### Interrupt Acknowledge

The interrupt acknowledge sequence, which was just described, occurs during an Interrupt Acknowledge machine cycle.

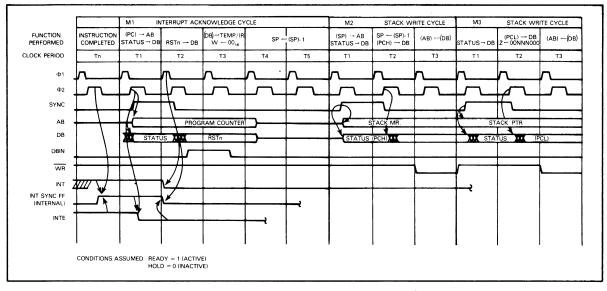

The Interrupt Acknowledge machine cycle is characterized by active INTA (D0) and M1 (D5) status signals during T1. Figure 2-17 shows the timing for the Interrupt Acknowledge machine cycle.

The interrupt service sequence is initiated by an external Interrupt Request (INT) becoming active prior to the end of  $\Phi 2$  in the last machine clock period of an instruction being completed. The next clock period will initiate the Interrupt Acknowledge machine cycle which requests one byte from the interrupting circuit. The byte that is returned to the CPU is loaded into the Instruction Register and interpreted as an instruction opcode. The following events occur during the Interrupt Acknowledge machine cycle:

- 1) The INTE signal is disabled in the T1 clock period, preventing future interrupts from being serviced.

- Although the Program Counter contents are supplied to the Address Bus, the Program Counter is not incremented.

- 3) The MEMR status signal is not activated.

- External logic supplies the interrupt instruction to the Data Bus to be received by the Instruction Register during T3.

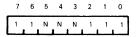

#### **Restart Instruction**

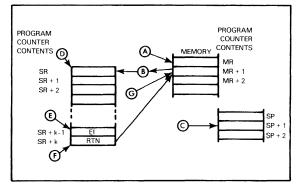

Restart is a one-byte subroutine Call instruction; it saves the Program Counter contents on the stack and provides a subroutine entry address. A 3-bit vector is issued to select one of eight fixed memory locations to which program execution may transfer.

The binary format for the Restart instruction is:

where NNN is the interrupt vector. Table 2-3 lists the eight Restart vectors and the corresponding addresses.

TABLE 2-3 RESTART INSTRUCTION INTERRUPT VECTOR ADDRESS

|             | INTERRUPT     | MEMORY      | ADDRESS |

|-------------|---------------|-------------|---------|

| INSTRUCTION | VECTOR<br>NNN | HEXADECIMAL | OCTAL   |

| RST 0       | 000           | 0000        | 000000  |

| RST 1       | 001           | 0008        | 000010  |

| RST 2       | 010           | 0010        | 000020  |

| RST 3       | 011           | 0018        | 00030   |

| RST 4       | 100           | 0020        | 000040  |

| RST 5       | 101           | 0028        | 000050  |

| RST 6       | 110           | 0030        | 000060  |

| RST 7       | 111           | 0038        | 000070  |

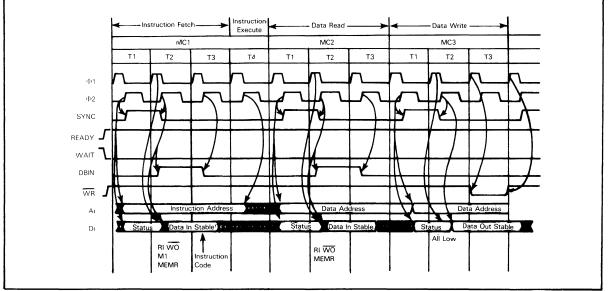

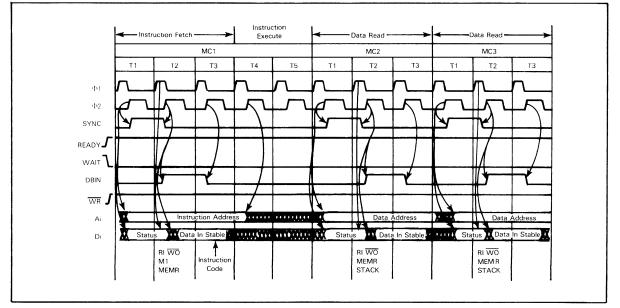

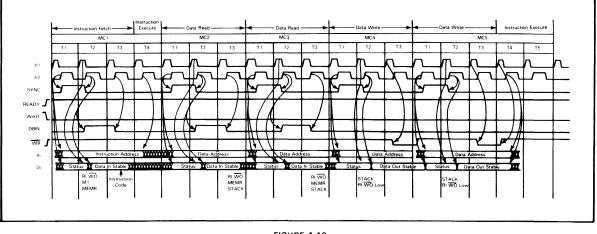

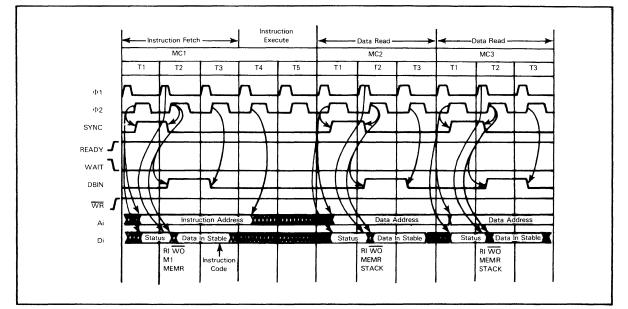

Figure 2-17 shows the complete timing diagram for processing the Restart instruction. M1 is the Interrupt Acknowledge machine cycle. It causes the interrupting circuit to respond by transmitting the Restart instruction back to the CPU. The Restart instruction is decoded in T4 and the Stack Pointer is decremented. Two Stack Write machine cycles are performed in M2 and M3 to store the current Program Counter contents onto the stack and to form a new memory address from the decoded information in the Restart instruction. The new memory address represents the address of the first instruction to be executed in the interrupt subroutine.

FIGURE 2-17 INTERRUPT TIMING, RESTART INSTRUCTION

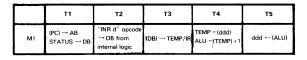

| CYCLE | ТҮРЕ                                  | т1                                               | Т2                                                                | тз           | T4               | Т5              |

|-------|---------------------------------------|--------------------------------------------------|-------------------------------------------------------------------|--------------|------------------|-----------------|

| M1    | INTERRUPT<br>ACKNOWLEDGE              | $(PC) \rightarrow AB$<br>STATUS $\rightarrow DB$ | "CALL" OPCODE<br>→ DB<br>SUPPLIED BY<br>INTERRUPTING<br>DEVICE    | (DB) TEMP/IR | SP –             | (SP)- 1         |

| M2    | NULL                                  | (PC) → AB<br>STATUS → DB                         | LSB (8 BITS)<br>OF CALL ADDRESS<br>→ DB BY<br>INTERRUPTING DEVICE | Z (DB)       | $\times$         | $\left \right>$ |

| M3    | NULL                                  | $(PC) \rightarrow AB$<br>STATUS $\rightarrow DB$ | MSB (8 BITS)<br>OF CALL ADDRESS<br>→ DB BY<br>INTERRUPTING DEVICE | W (DB)       |                  |                 |

| M4    | STACK WRITE                           | (SP) → AB<br>STATUS → DB                         | (PCH) → DB<br>SP ← (SP)-1                                         | (AB) ←-(DB)  |                  | RATED           |

| M5    | STACK WRITE                           | (SP) → AB<br>STATUS → DB                         | (PCL) → DB                                                        | (AB) ← (DB)  | $\ge$            | $\ge$           |

|       | r                                     |                                                  | 1                                                                 | <u> </u>     |                  |                 |

| M1    | INSTRUCTION FETCH<br>NEXT INSTRUCTION | (W,Z) → AB<br>STATUS → DB                        | (AB) → DB<br>PC ← (W,Z) + 1                                       | >            | T3, T4, AND T5 N | IOT GENERATED   |

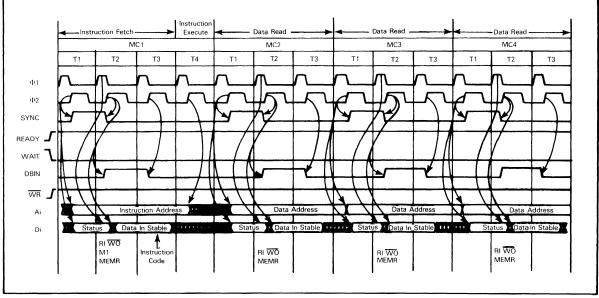

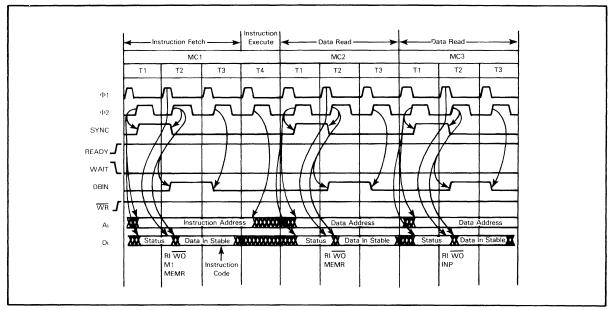

FIGURE 2-18 EXECUTION OF CALL INSTRUCTION DURING INTERRUPT ACKNOWLEDGE

#### **Call Instruction**

The Call instruction saves the Program Counter contents on the stack and provides a subroutine address. The Call instruction is particularly useful as a response to the Interrupt Acknowledge machine cycle. It supplies a full 16-bit subroutine address, allowing direct entry to interrupt service routines located anywhere in memory without first branching to the restart locations. Any number of interrupt locations may be directly addressed by the peripherals rather than only one of the eight restart locations.

The execution of the Call instruction in response to the Interrupt Acknowledge machine cycle is shown in Figure 2-18.

Notice that a Call instruction inserted into the CPU in response to the Interrupt Acknowledge machine cycle (M1 in Figure 2-18) executes as if it were a normal Call instruction except for the following, numbered as in Figure 2-18:

- 1) The Program Counter is not incremented in T2 of any machine cycle.

- Null machine cycles are substituted for the usual Memory Read machine cycle. The Null cycle does not activate the MEMR status bit and thus inhibits the memory system.

- 3) The least significant eight bits of the interrupt subroutine address generated by the external interrupt logic are loaded into the Z Register, and the most significant eight bits are loaded into the W Register.

The conditional Call instructions could be used also; however, since the interrupt may occur after any instruction, the condition codes which determine the branch to the subroutine may be unpredictable.

#### **OTHER INTERRUPT INSTRUCTIONS**

Any Am9080A instruction except XTHL may be used as a response to the Interrupt Acknowledge machine cycle. However, instructions other than the Restart or Call do not cause the Program Counter contents to be saved and do not supply an interrupt service routine address. Therefore, inter-

rupt servicing cannot be distinguished clearly as a separate subroutine.

Also, INTE is disabled when the interrupt is serviced. If an interrupt is not serviced via a separate subroutine, there exists no definite position in the program where the El instruction should be executed. The Enable Interrupt instruction may have to be inserted periodically throughout the program to ensure that interrupts are re-enabled.

Nevertheless, some applications use special instructions in response to the Interrupt Acknowledge machine cycle. For example, an instruction which increments a register or memory location may record an external event such as a clock pulse or limit switch closure and allow the main program to finish executing its task before attention is directed to the event.

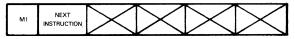

The execution of the INR d inserted in response to an Interrupt Acknowledge machine cycle is shown in Figure 2-19.

FIGURE 2-19 INR d RESPONSE TO INTERRUPT ACKNOWLEDGE

Notice that PC is not incremented in T2 as it is when INR d is executed in response to the usual Instruction Fetch machine cycle.

#### Wait And Hold Conditions During An Interrupt

Interrupts cannot be acknowledged during a Wait or Hold condition. However, it is possible to enter the Wait or Hold state after the Interrupt Acknowledge machine cycle has been generated. This may be useful in logic systems where there is

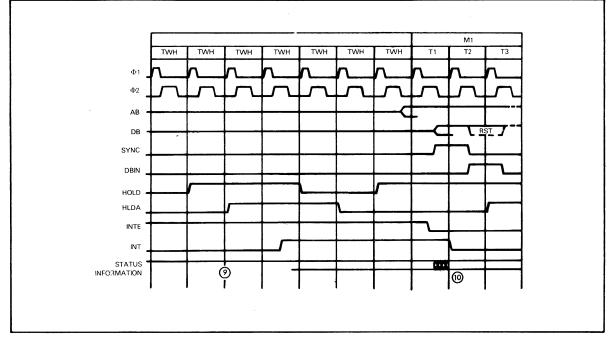

FIGURE 2-20 RELATION BETWEEN HOLD AND INT IN THE HALT STATE

insufficient time in the normal machine cycle to generate an interrupt instruction and place it on the Data Bus for execution by the CPU. The Ready signal can be deactivated to cause the machine to insert the Wait state for one or more clock periods as required until the appropriate duration has elapsed.

When the Am9080A is in the Halt state, an interrupt will cause program processing to continue. However, a Hold state can be superimposed on the Halt state to cause the Data and Address Busses to be released for external control of these busses. While the Hold condition is active, the interrupt will be inhibited. Figure 2-20 shows the relationship between the Hold and INT inputs during the Halt state.

#### Interrupt Acknowledge During A Halt

This machine cycle occurs in response to an interrupt request (INT) when the processor is in the Halt state (HLTA is active). The timing diagram for this state is shown in Figure 2-20. The Interrupt Acknowledge While Halt machine cycle is similar to the Interrupt Acknowledge machine cycle in that the Program Counter is not incremented when this instruction opcode is supplied to the Data Bus.

#### **INPUT/OUTPUT PROCESSING**

This section discusses some general considerations for Input/Output processing. The concept of address space is introduced and methods of I/O addressing are discussed.

#### Maximum Address Space

A microprocessor is capable of accessing any one of a number of external devices or locations with a single instruction. The unique identification of the device which is accessed is contained in the address transmitted by the CPU during the access. The maximum number of addresses which may be generated is the Maximum Address Space of the microprocessor. The Am9080A provides two independent address spaces. The first provides 64K bytes of addressable space for memory. The second is a totally independent addressable space which is used only by the Input/Output instructions of the machine.

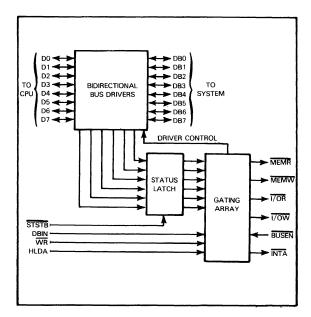

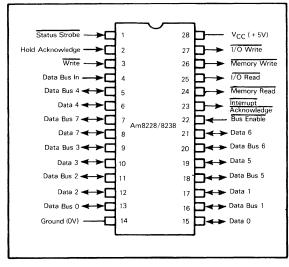

The status signals supplied to the Data Bus by the CPU at the beginning of every machine cycle determine whether the external device access will be to a location in the addressable memory space or to one of the I/O circuits. Table 2-4 shows the type of access that occurs as a result of these status signals. When used in a system with an 8228 or 8238 System Controller, the control lines are latched and decoded even more explicitly as MEMR, MEMW, IOR, IOW.

TABLE 2-4 ADDRESS SPACE ACCESSES AS A FUNCTION OF MACHINE CYCLE STATUS BITS

| STATUS                   | DATA BUS<br>BIT      | ADDRESS<br>SPACE<br>ACCESSED | FUNCTION PERFORMED                                                                                                                                |

|--------------------------|----------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMR<br>WO<br>INP<br>OUT | D7<br>D1<br>D6<br>D4 | MEMORY<br>I/O                | READ FROM MEMORY LOCATION ADDRESSED<br>WRITE TO MEMORY LOCATION ADDRESSED<br>READ FROM INPUT DEVICE ADDRESSED<br>WRITE TO OUTPUT DEVICE ADDRESSED |

#### I/O Addressing

Peripheral devices may be configured in the Am9080A system to function in either the I/O address space or in the memory address space. However, the performance of the CPU in handling I/O transfers through the two addressable memory spaces is different. Each of these is discussed in the following sections.

### Addressing Peripheral Devices With The I/O Instruction

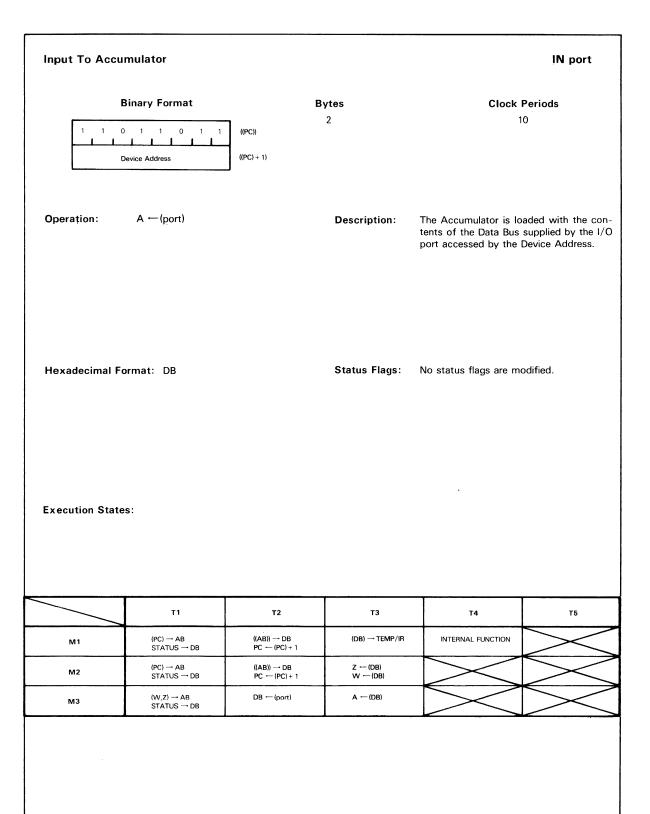

The Input and Output instructions cause the transfer of an 8-

bit value between the Accumulator and an external device. They are two bytes long. The first byte always contains the operation code that defines the instruction as either an Input or Output function. The second byte is always an 8-bit address that defines the location of the external unit which is addressed.

The executions of the Input and Output instructions are defined by the corresponding Input Read and Output Write machine cycles. The status generated during the T1 clock period of these machine cycles causes either the INP or the OUT status signal to be generated. Notice that the corresponding MEMR and  $\overline{WO}$  signals are not active when these machine cycles are generated as shown in Table 2-1. M2 machine cycle accesses byte 2 of the Input or Output instruction for the address of the peripheral device. This address is placed in both the Z and W Temporary registers and made available via the Address Bus. The address appears on address lines A0 through A7 and again on address lines A8 through A15.

### Input/Output Devices As A Function Of Addressable Memory Space

An alternate method of organizing the I/O system in an Am9080A microcomputer is to assign specific memory addresses to the input and output functions. The advantage of using memory space for Input/Output ports is that the full flexibility of all the memory reference instructions can be used for servicing input/output devices. It also greatly expands the number of locations available for I/O.

For example, the exclusive "OR" instruction (XRA M) with an address pointing to a location assigned to an I/O device would cause a byte to be read from the peripheral device and exclusive "OR" ed with the contents of the Accumulator. This would require the execution of at least two instructions using the standard Input instruction. The first instruction reads the contents of the peripheral device and loads it to the Accumulator. The second instruction performs the exclusive "OR" with the contents of a CPU register or a memory location.

The external system distinguishes memory from I/O operations by examining the location being addressed.

In conclusion, addressing I/O devices within a separate I/O space reduces device select logic by limiting select logic input to 8 of the 16 Address Bus lines; however, just two instructions are available to input or output data from or to the I/O devices. If I/O devices are addressed within the memory space of the microprocessor system, then all 16 address lines must be decoded by the device select logic. However, any memory reference instruction can now access the I/O device.

### Chapter 3 8080A/9080A INSTRUCTION SET

The functions performed by a microcomputer are determined by a sequence of instructions, which, taken together, constitute a program.

This section provides a detailed description of every Am9080A instruction.

All instructions are one, two or three bytes in length, the first byte always containing the opcode for the instruction. The instruction formats are shown below.

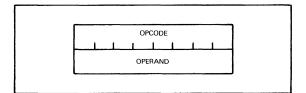

#### **Single Byte Instructions**

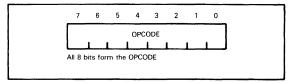

Type 1 Control, Subroutine Return and other Data Manipulation instructions, where the source and destination are implied, use a single, 8-bit opcode, as illustrated in Figure 3-1.

FIGURE 3-1 A TYPE 1, SINGLE BYTE INSTRUCTION OPCODE

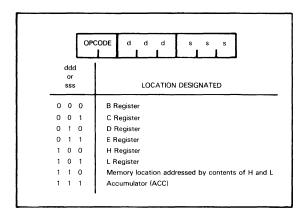

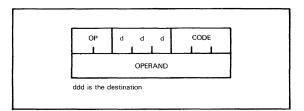

Type 2 instructions utilize a 2-bit opcode and specify the source and destination addresses for operands, as illustrated in Figure 3-2.

FIGURE 3-2 A TYPE 2, SINGLE BYTE INSTRUCTION

When sss or ddd have the value 110, a memory location is addressed. The contents of the H and L registers form a 16-bit binary address which is used to access the desired location.

The general format for Type 2, single byte instructions allows either or both the source and destination locations to be specified. Both source and destination are present only in the MOVE instruction.

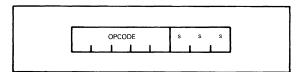

Type 3, single byte instructions of the Arithmetic group, as well as some of the instructions from the logical group, specify only the source address, sss. The remaining five bits of the 1-byte, Type 2 instructions form the opcode, as illustrated in Figure 3-3.

FIGURE 3-3 TYPE 3 SINGLE BYTE INSTRUCTIONS

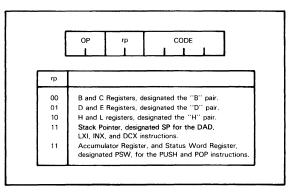

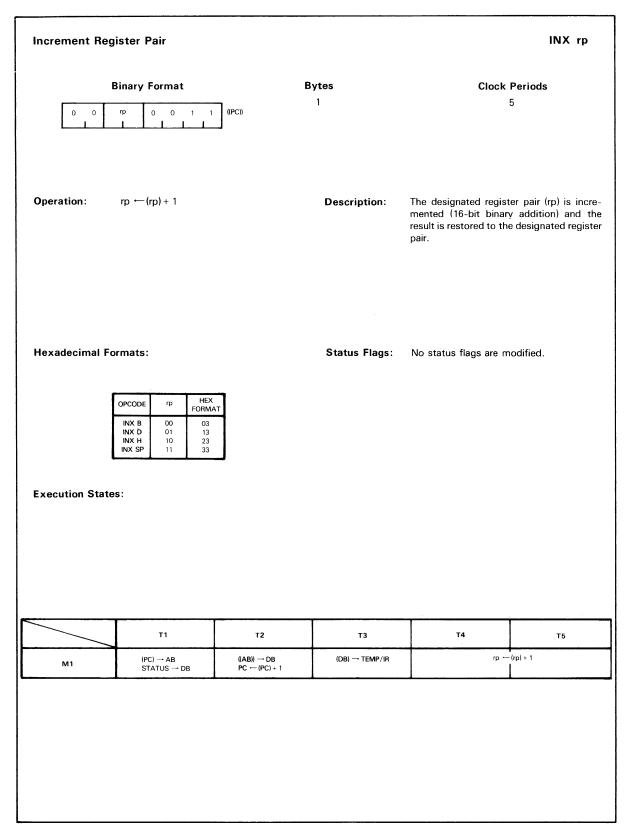

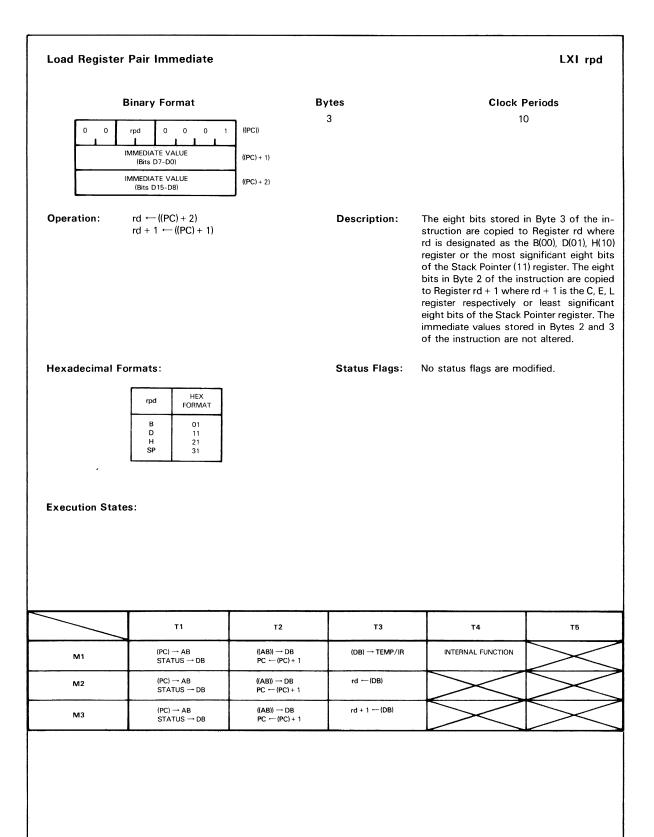

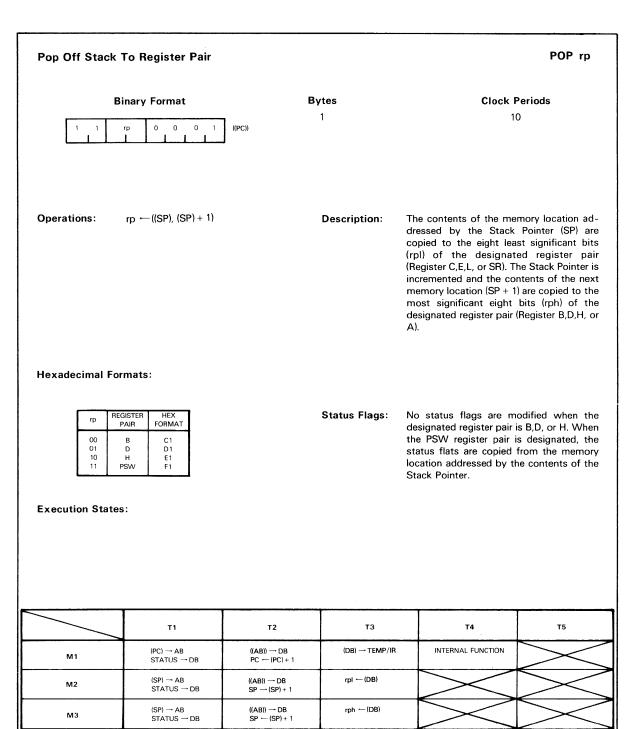

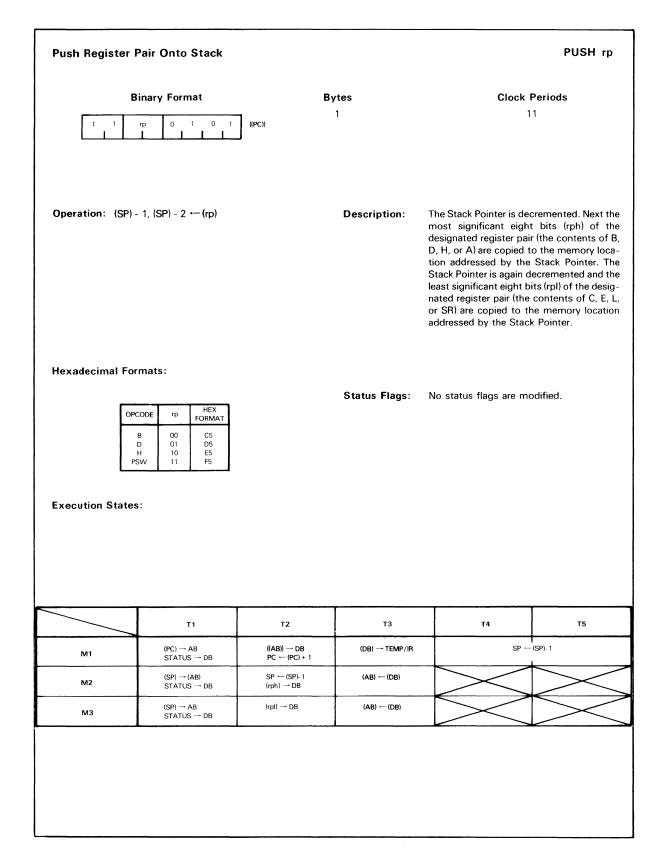

Type 4 instructions treat the contents of pairs of registers as a 16-bit binary value. These instructions include DAD, LXI, INX, DCX, PUSH and POP, as illustrated in Figure 3-4.

FIGURE 3-4 TYPE 4 SINGLE BYTE INSTRUCTIONS

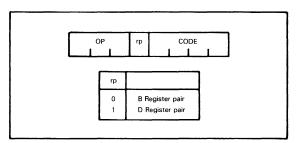

The LDAX rp instruction is a special case in which the designated register pair (rp) is only one bit, as illustrated in Figure 3-5.

FIGURE 3-5 LDAX rp INSTRUCTION

#### **Two Byte Instructions**

Type 1 has both the immediate operand and the destination address contained within the instruction. The only instruction using this format is MOVE IMMEDIATE (MVI).

FIGURE 3-6 TYPE 1, TWO BYTE INSTRUCTIONS

Type 2 has an 8-bit opcode and an 8-bit operand. All instructions with immediate operands, with the exception of the MVI instruction, use this format.

FIGURE 3-7 TYPE 2, TWO BYTE INSTRUCTIONS

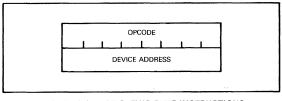

Type 3 has an 8-bit opcode and an 8-bit I/O device address. Input and Output instructions use this format.

FIGURE 3-8 TYPE 3, TWO BYTE INSTRUCTIONS

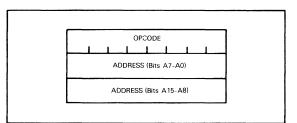

#### **Three Byte Instructions**

These have an 8-bit opcode and a 16-bit address. All Direct Address, Jump and Call instructions use this format.

#### **Unused Opcodes**

There are 12 unused opcodes which are not decoded by the CPU. The hexadecimal opcodes for these instructions are:

| 08 | 20 | 38 | DD |

|----|----|----|----|

| 10 | 28 | СВ | ED |

| 18 | 30 | D9 | FD |

The response of the Am9080A is unpredictable when one of these codes is loaded into the Instruction Register during the Instruction Fetch or Interrupt Acknowledge machine cycle.

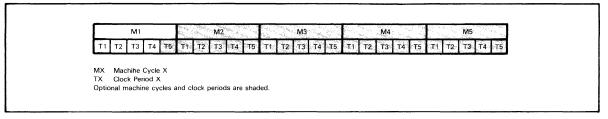

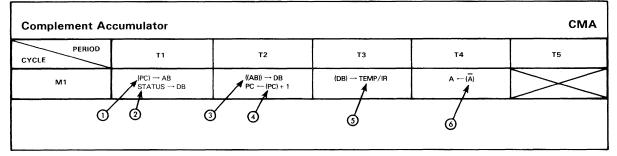

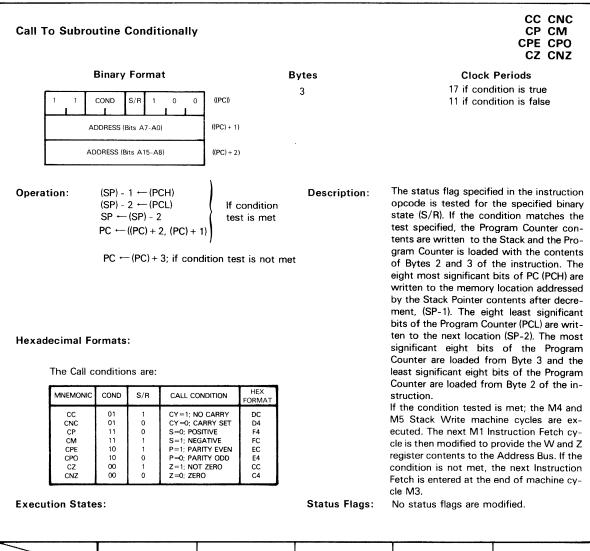

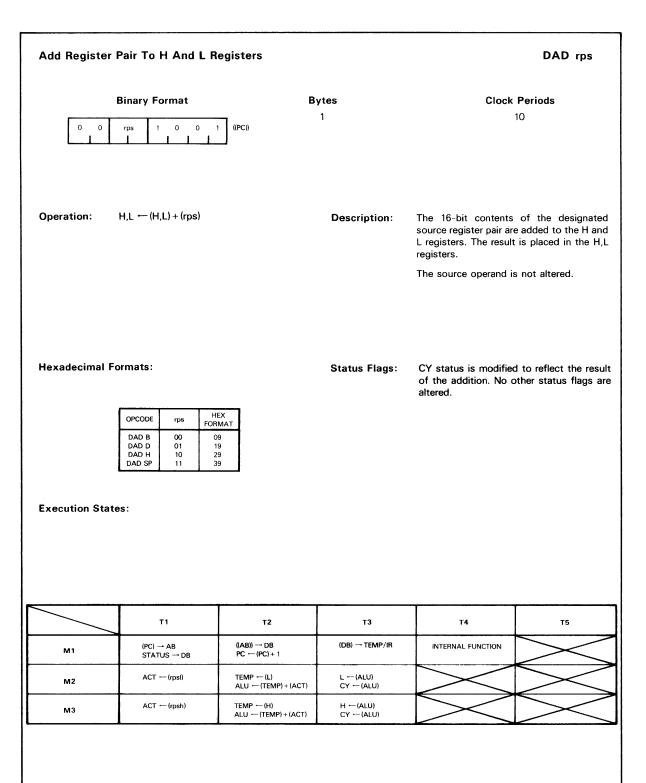

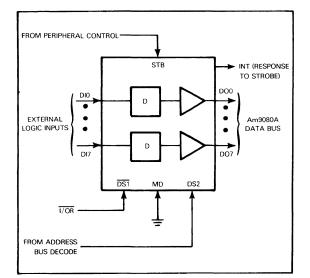

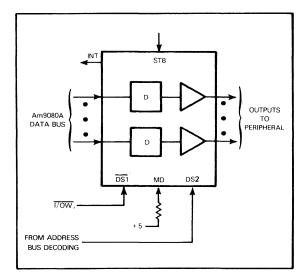

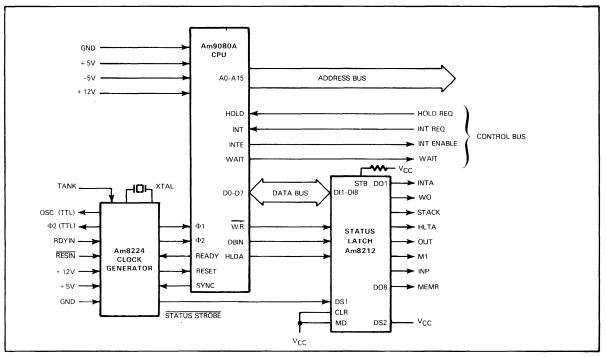

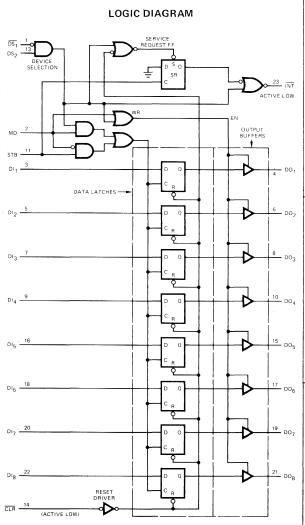

#### INSTRUCTION EXECUTION