# Micro Channel Adapter Design Handbook

August, 1988

# **MICRO CHANNEL ADAPTER DESIGN HANDBOOK**

## **ALTERA CORPORATION**

# **AUGUST, 1988**

## TABLE OF CONTENTS

1. Application Note #14:

IBM PS/2 Add-On Card Interfacing with the EPB2001 & EPB2002

2. Application Note #15:

IBM PS/2 Add-On Card Software Design

3. Application Brief #72:

IBM PS/2 Master and Slave Adapter Design

4. Data Sheet:

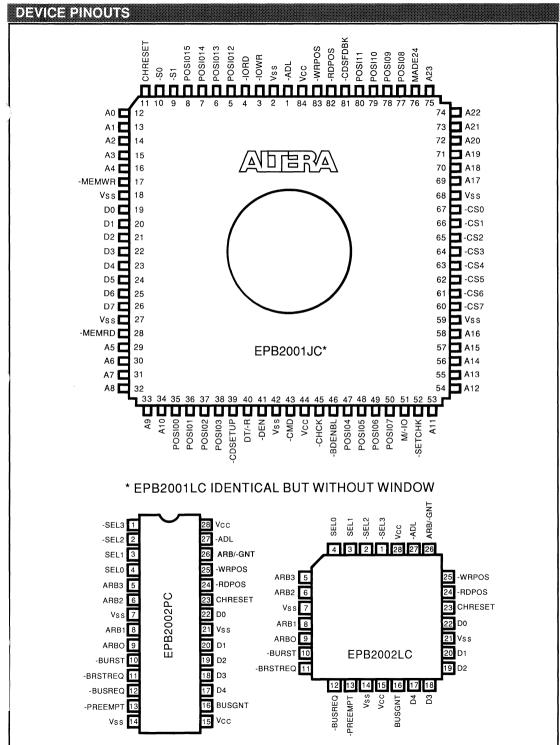

EPB2001 / EPB2002 User-Configurable Adapter Interface Chips for PS/2 Micro Channel

### INTRODUCTION

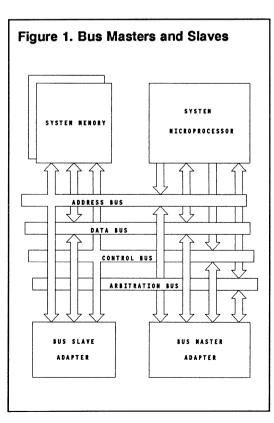

The IBM Personal System/2 (PS/2) architecture announced in early 1987 included a new add-on card bus architecture called the Micro Channel Bus. This architecture, which supports both 16- and 32-bit of includes concepts processors. the high-performance multi-device bus arbitration. level-sensitive interrupts, and Programmable Option Select (POS) registers. The POS registers are intended to replace DIP switches and jumpers on the add-on card, and allow software-configuration of card features. Simultaneously, in order to reduce the overall size of the PS/2 system, the physical size of add-on cards has been reduced by some 40% to only 33 square inches. The net result is а higher-performance, more reliable scheme for the attachment of add-on cards to the PS/2. The cost of these benefits, however, is a more complex interface design problem for the add-on card designer requiring a highly-integrated VLSI approach.

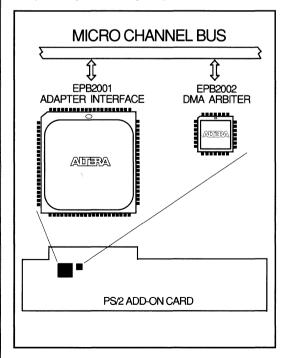

This Application Note illustrates the use of Altera's user- configurable adapter interface chips for the IBM Personal System/2 (PS/2) Micro Channel. A typical application is desribed, consisting of a Multi-Function card including 32K words of static CMOS RAM, a general-purpose output port and two serial ports. The Micro Channel interface EPLDs, the EPB2001 and EPB2002, provide all essential control interfaces between the Micro Channel Bus (MC Bus) and a PS/2 feature adapter (add-on board). Implementation of optional add-on card features, such as wait- state generation, output port and bit-rate prescaler, is also BUSTER EPB1400 EPLD. shown using а User-configurability allows these highly-integrated devices to provide functions typically requiring multiple components.

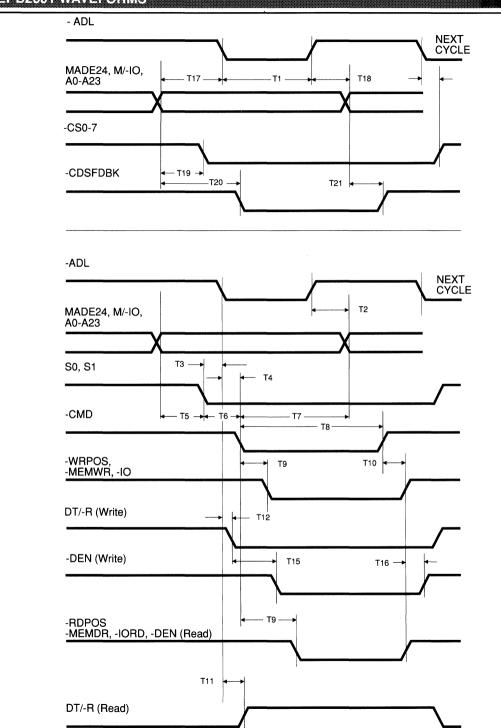

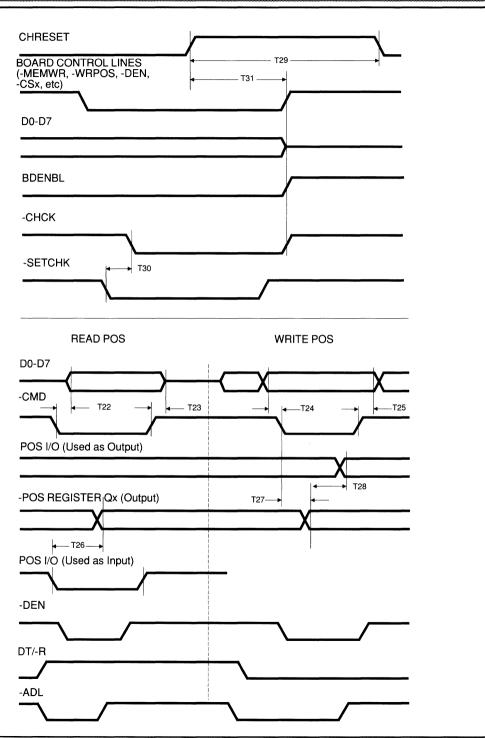

POS I/O pins from the EPB2001 are used to control typical board-level functions: wait-state duration and DMA channel selection and enabling. Board control lines (-DEN, DT/-R, -IOWR, -MEMRD, etc.) are used to control memory and I/O accesses. The EPB2001's chip select block provides all address decoding for board functions. The overall versatility of the EPB2001/2002 is illustrated in a real application.

In addition to this specific application example, a set of general design tips for the EPB2001/2002 is presented at the end of this Note. These tips show ways that the programmable nature of these chips can be exploited to provide optional, board- specific functions, such as latched addresses or card data-size feedback. 32-bit system design considerations are also discussed.

# IBM PS/2 ADD-ON CARD INTERFACING WITH THE EPB2001 & EPB2002

This Application Note assumes the reader is familiar with the basic concepts of the IBM MC Bus. The reader is directed to the references listed at the end of this Note for further information on the basic characteristics of the Micro Channel. Comprehensive functional and parametric information on the EPB2001/EPB2002 may be found in the EPB2001/EPB2002 Data Sheet, available from Altera.

# MULTI-FUNCTION CARD APPLICATION OVERVIEW

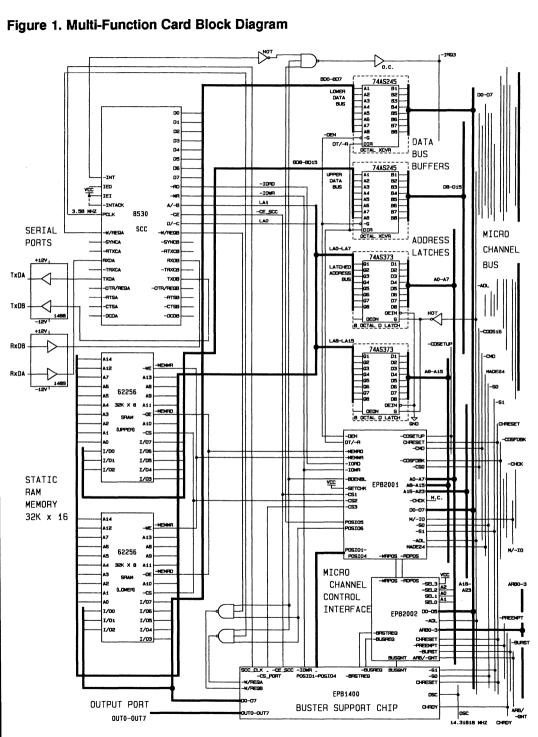

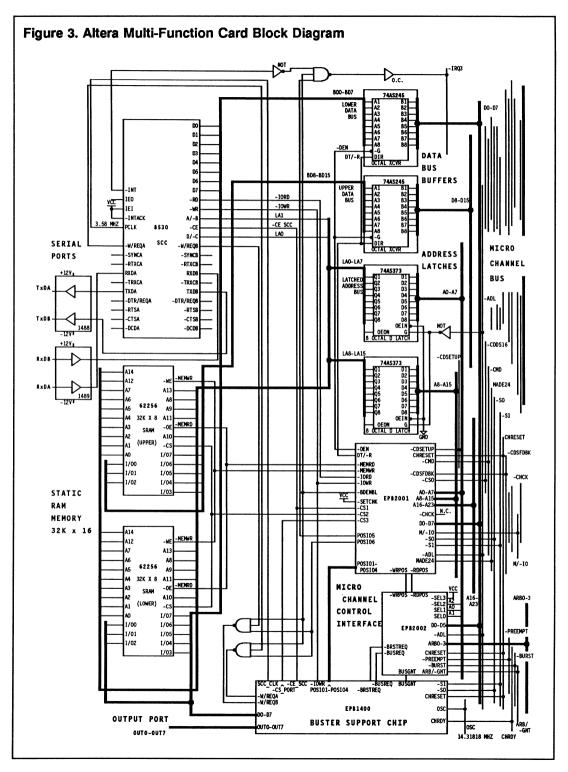

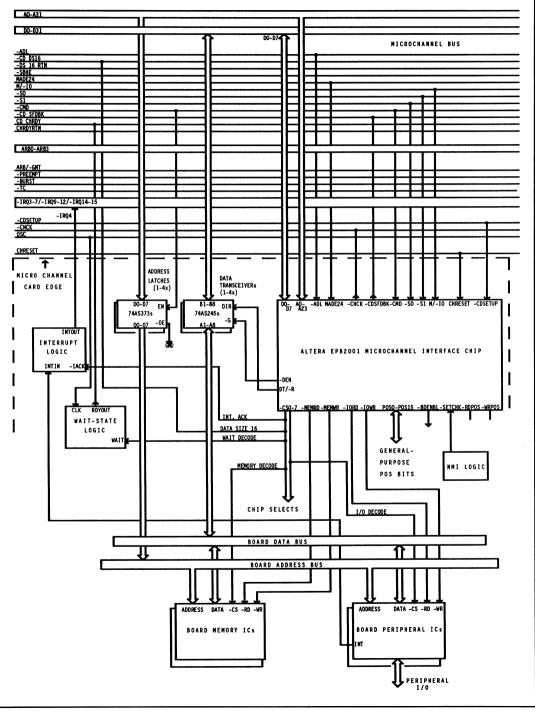

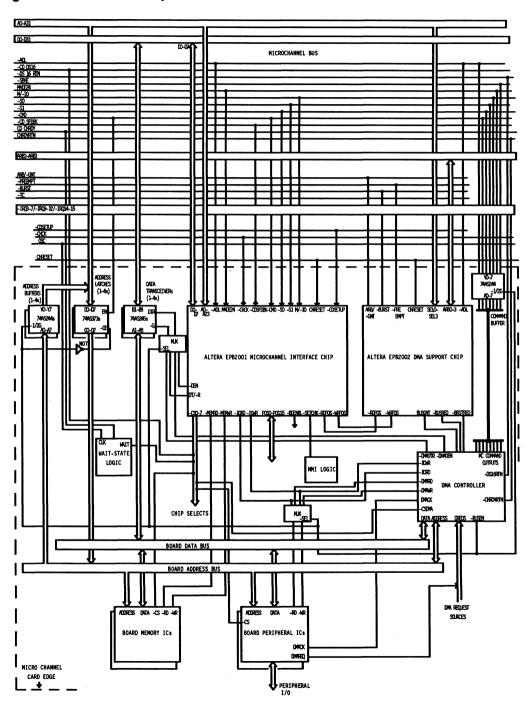

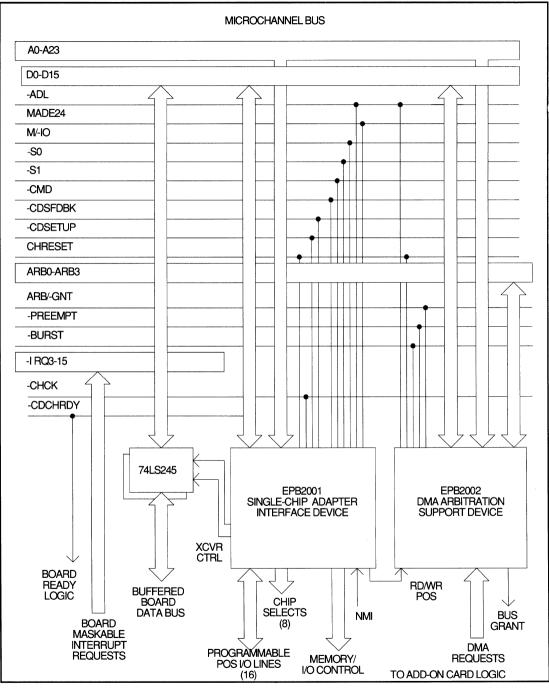

The block diagram in Figure 1 shows the overall structure of the Multi-Function card design. Shown on the right are the MC Bus lines which run to all add-on card slots. The EPB2001 provides mandatory POS register functions required by the specification in any add-on card interface. In addition, board control logic, board I.D. storage and address decoding are integrated onto the chip. The EPB2002, shown at lower right, provides DMA arbitration support. Not all add-on designs require DMA, but where it is needed, the EPB2002 fully supports the IBM bus exchange protocols.

This board design appears to the PS/2 as either an 8-bit I/O peripheral (for accesses to the Z8530 Serial Communications Controller (SCC)), or as a 16-bit memory extension (32K words). The two 74AS245 transceivers shown at upper right buffer data transfers between the Micro Channel and I/O or memory. Memory will always be accessed as words (no byte read/write), and as a result, selective enabling of the buffers using -SBHE from the Micro Channel is not required. Two 74AS373 flow-through latches are used to latch addresses during bus transfers. The -ADL line from the MC Bus controls the latching. Only the 16 low-order address bits need be latched since memory capacity is 64K (2\*\*16). The EPB2001's chip select logic will handle upper-order address decoding for the various I/O and memory chips on the board.

The Z8530 SCC provides two serial channels in a single 40 pin device. This chip supports a variety of synchronous and asynchronous communication modes, on-chip data buffering, and an integral baud-rate generator. The Z8530 includes handshake lines for DMA Request/Acknowledge which interface to the EPB2002. The EPB2002 requests use of the MC Bus via the -PREEMPT line in response to these requests.

The clock for the SCC is provided by a divide-by-four counter, which is driven by the OSC line

on the MC Bus. This clock divider is implemented in a small portion of an EPB1400. The OSC line provides a precision clock input of frequency 14.31818 Megahertz. The clock divider generates a 3.58 MegaHertz output for the SCC. As a result, a local oscillator is not needed for the SCC.

Wait-state logic associated with the Z8530 is also designed into the EPB1400. In a Micro Channel default bus cycle, the width of the -CMD bus transfer strobe may be as narrow as 90 nS. The 4 MegaHertz Z8530 used in this design requires a 250 nS minimum width on -RD and -WR to the device. As a result, the bus cycle must be "stretched" at least 160nS. This is done by inserting wait-states to extend the cycle. This logic will be described in detail later.

The two CMOS SRAM chips used in this design have 100 nS address access times. As such, access to these chips requires no wait-states. This memory will always be accessed as 16-bit words. The 32K block can be used as a general-purpose memory extension. A more elaborate design could use this memory as a transmit / receive buffer if an additional local transfer controller were added to move data between buffer and SCC without external intervention.

The two pairs of serial data lines (RxD and TxD, Channel A & B) from the SCC are connected to 1488/1489 line driver/receivers which in turn form RS-232-compatible interfaces. In this application, the full DCD/CTS/RTS handshake has not been shown. This could be easily added by the addition of buffers between the RS-232 links and the SCC modem control pins. The + 12V/-12V supply required by these drivers is obtained from the Micro Channel edge connector.

# EPB2001 INTERFACE FUNCTIONS

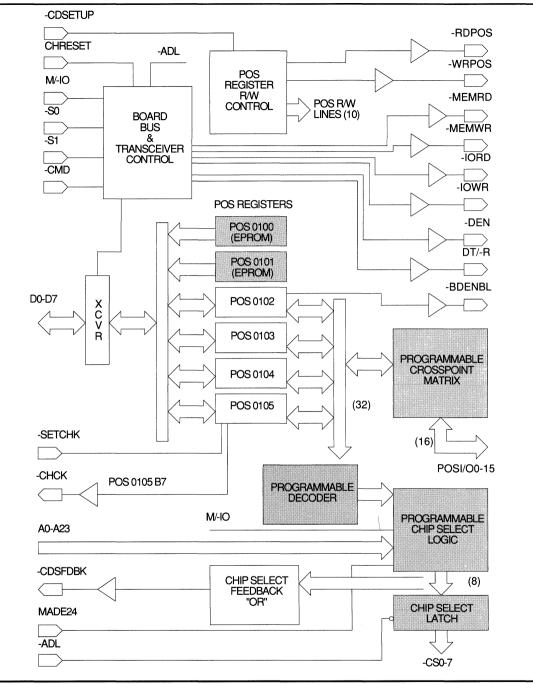

In this Multi-Function application, the EPB2001 provides the primary control interface. The main functional blocks in the EPB2001 and the specific functions provided for this application include:

#### BOARD I.D.

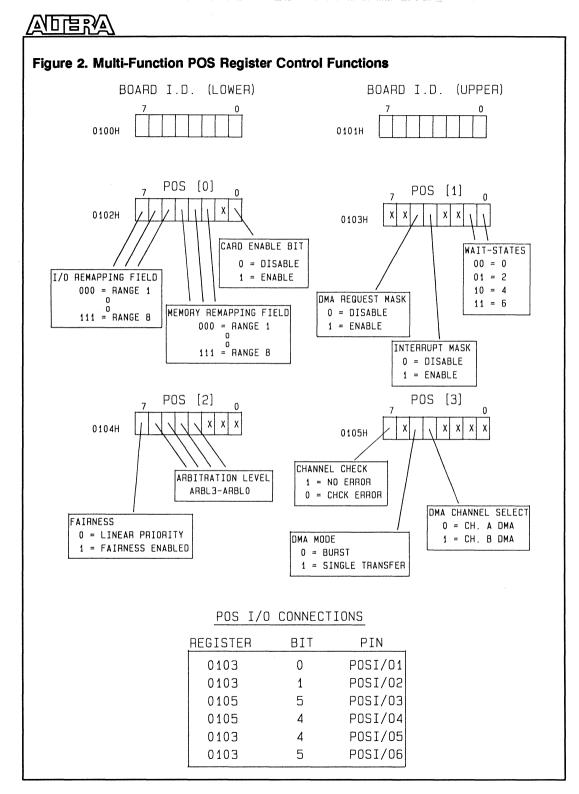

As required for any MC Bus add-on, the EPB2001 provides two CMOS EPROM bytes at location 0100-0101H for the board I.D. These are read-only locations accessible from the MC Bus. These I.D.'s are unique to a given board design and are allocated by IBM to registered Independent Developers. The developer must contact IBM directly for such I.D.'s.

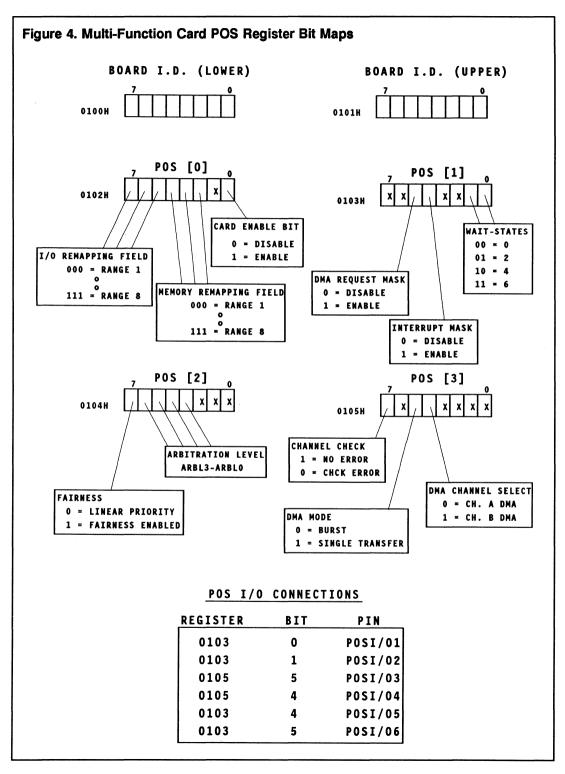

POS REGISTERS

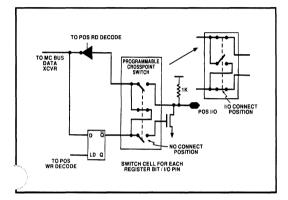

The four required POS registers 0102-0105H are used in this application to control I/O remapping, memory remapping, number of I/O wait-states, DMA request source selection and masking, interrupt masking and DMA arbitration level and Fairness. The latter DMA control functions are also mapped into the satellite POS register bits on the EPB2002. The bit-mapping of these functions is illustrated in Figure 2.

POS bits which are required outside the EPB2001 are brought- out via the POS I/O pins. This mapping is shown in Figure 2 as well.

#### BOARD CONTROL

The board control logic on the EPB2001 provides all required transceiver control (-DEN, DT/-R) and I/O / memory control strobes (-IOWR, -IORD, -MEMWR, -MEMRD). These are generated as bus cycle status decodes timed by the MC Bus -CMD transfer strobe. These signals directly drive the Z8530, SRAM and BUSTER read and write strobes.

The Board Enable (-BDENBL) output of the EPB2001, which reflects POS register 0102H bit 0, is used in this application to mask DMA requests and interrupts prior to enabling the card at system boot time. In addition, this bit is internally factored into the -CSx enable functions to disable chip selects when the board is disabled. This also suppresses generation of the -CDSFDBK line prior to card set-up.

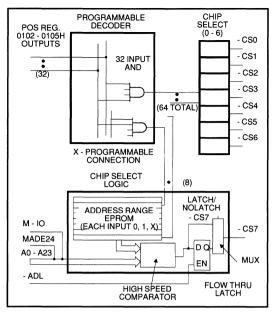

#### CHIP SELECT LOGIC

The chip select block in the EPB2001 provides chip select outputs for the CMOS SRAM, SCC, and BUSTER Output Port. In addition, one of the -CSx outputs is used to drive the -CDDS16 (card data size 16) output to the MC Bus whenever the SRAM (organized as words) is accessed.

In this case, the first three chip select outputs will be latched by -ADL. The -CDDS16 output is not latched.

The -CDSFDBK (card select feedback) line to the MC Bus is an unlatched OR-function of appropriate chip selects. In this example, all -CSx functions with the exception of -CDDS16 will be factored into this signal. This selective ORing is a user-programmable feature of the EPB2001 architecture. Latching of these lines is also programmable. Remaining -CSx outputs could be used to drive other peripheral or memory chips, or supply design- specific board logic as described later.

Each of the chip selects has 8 pre-programmed ranges controlled by the address remapping fields specified in the POS registers. The programmable POS chip select enable decoder provides a unique mechanism for linking the POS registers to the chip

select decode block. In this way the PS/2 can control address response ranges for the card and associated memory / I/O resources as it configures the system. This is used to eliminate address conflicts between cards without mechanical setting of DIP switches or jumpers, an error-prone process. The use of such mechanical arrangements in fact violates the Micro Channel specification.

Due to the structure of the chip select block as defined in the EPB2001/2002 Data Sheet, an address block of 2\*\*N locations must sit on a 2\*\*N address boundary. In other words, as the block size increases, the allowable number of base address positions decreases. For example, a 256K RAM chip select must have a base address which is a multiple of 256K. This is not a severe restriction in most practical applications, but should be kept in mind as alternate address locations are selected.

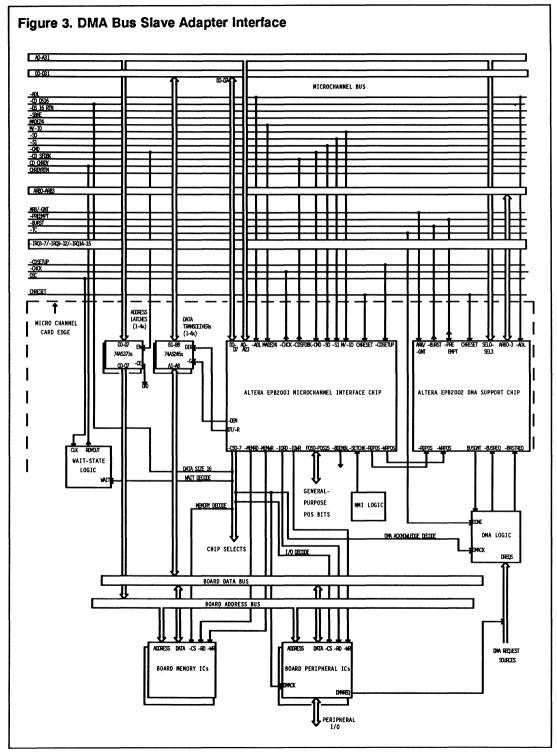

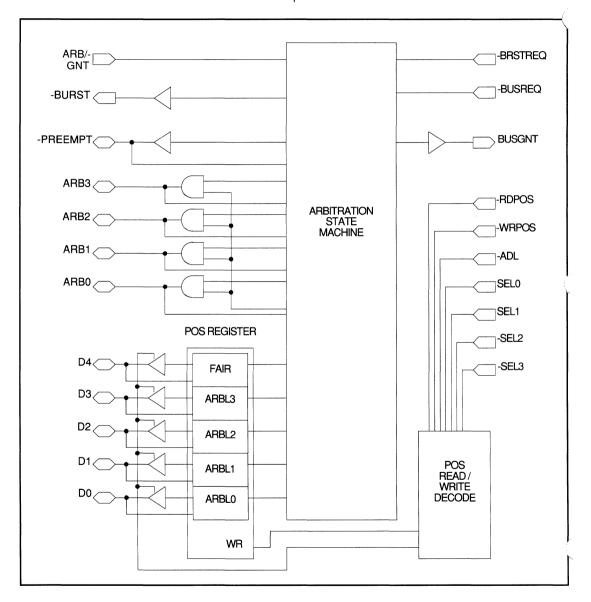

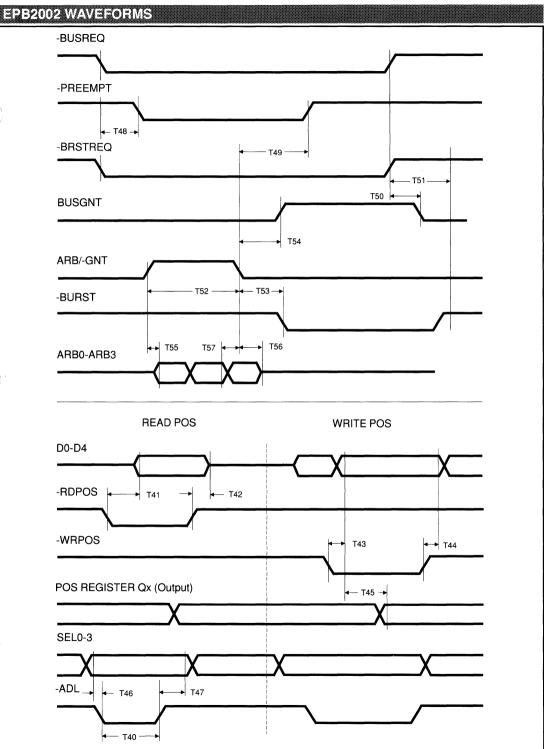

# EPB2002 INTERFACE FUNCTIONS

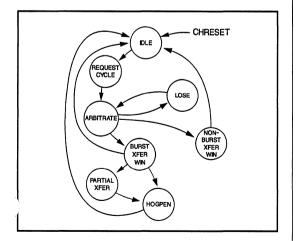

The EPB2002 does not require the degree of programmability that the EPB2001 contains. The EPB2002 implements the bus arbitration protocol defined for the Micro Channel in an asynchronous state machine. POS register bits are included which are readable and writeable from the MC Bus. These bits control the four-bit Arbitration Level for the board (arbitration priority) and enable Fairness (Fairness is a mechanism specified by IBM to eliminate bus "hogging" by bursting DMA devices).

The actual arbitration process is discussed in detail in the EPB2001/2002 Data Sheet and in the IBM documentation listed at the end of this note. The EPB2002 provides direct a.c. and d.c. compatibility with the interface signals required. For more information on this process the reader should consult the referenced documents.

The bit positions and POS register location which these bits will be mapped into is up to the board designer. The MC Bus specification does not define required POS locations for them. Any of POS registers 0102-0105H may be used for this purpose. The EPB2002 allows the remapping of these bits by appropriate connections to the SELx inputs to the chip. This is described in detail in the EPB2001/2002 Data Sheet. By connecting the SELx inputs as shown in Figure 1, these bits have been mapped into POS register 0104H for this application, bit locations D3-D7 on the bus.

Further details on the electrical interface of the EPB2002 to the BUSTER and SCC components will be given in a later section.

# Z8530 INTERFACE CONSIDERATIONS

#### SYSTEM INTERFACE

Basic signals involved in interfacing the Z8530 to an MPU bus (the MC Bus in this case) are shown in Figure 3. These include -CE (Chip Enable), A/-B (Channel A/B designator), D/-C (Data/Command designator), -RD (Read Strobe), -WR (Write Strobe) and the 8-bit data bus, D0-D7. Here we are using the IBM MC Bus specification convention of a leading hyphen to indicate an active-low signal name. The Z8530 includes 9 Read-able and 15 Write-able registers to set device configuration, report status and access data. To reduce address input pin requirements, the Z8530 uses the concept of an address pointer register: any command register access (read or write) must be preceded by a write to the SCC with D/-C low and the address of the register to be accessed on the next cycle as the associated data. After the subsequent access, the pointer register is automatically reset to the address pointer register. Every command register access is thus a two bus cycle process: write address pointer, write or read selected register.

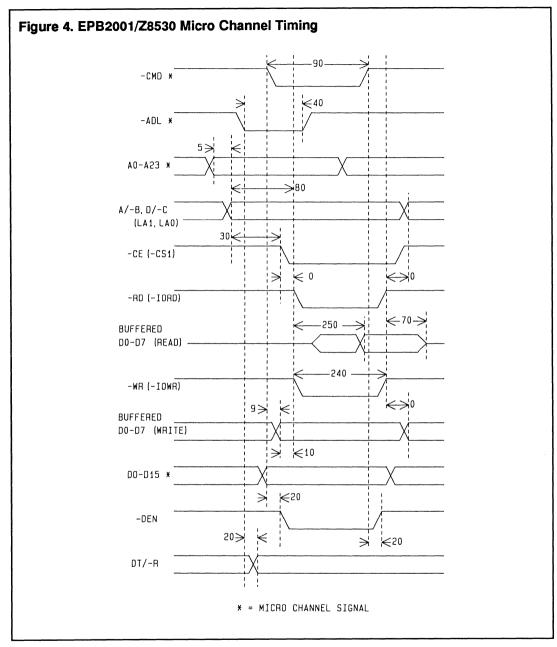

The waveforms shown are for data transfer cycles. Timing for a command cycle is similar, but involves the additional cycle mentioned above. Timing data is for the 4 MegaHertz Z8530. In general, the timing is very straightforward: the Z8530 requires that -CE, D/-C, and A/-B be set-up prior to the strobe (-RD or -WR) going active low. -CE's set-up time is 0 nS, while D/-C and A/-B must be set-up 80 nS prior to the strobe edge. All signals have a 0 nS hold time to the rising (inactive) edge of the strobe.

Data for a write cycle must be set-up 10 nS before the active -WR edge. In a read cycle, the Z8530 will place valid data on its D0-D7 pins within 250 nS of the -RD active edge.

These are the SCC device requirements. The subsequent Figure 4 shows the signals provided by the EPB2001 chip select and board control logic. In this design, the D/-C and A/-B inputs to the SCC will be connected to the latched address inputs provided by the 74AS373 devices. The MC Bus provides a minimum set-up of 85 nS from address valid on the MC Bus to -CMD falling. Using 74AS373's, the delay from input (MC Bus) to output (latched board address bus) is 5 nS. The address is consequently valid at the Z8530 more than 80 nS before the strobe edge, since the strobe is triggered by the -CMD line going active.

The delay from address valid on the A0-A23 inputs to the EPB2001 -CSx outputs valid is 30 nS. The Z8530 requires only 0 nS, so over 55 nS of timing

# 口店的 Figure 3. Z8530/SCC Timing Requirements (4 MHz) A/-B, D/-C-CE <u></u> $\Leftrightarrow$ -RD ←70-250 -D0-D7 (READ) -240 -WR DO-D7 (WRITE) ₩10

margin is available on the -CE path. The EPB2001 latches the -CE line with -ADL for the entire bus cycle.

The address ranges which the EPB2001 decodes for the -CE input to the SCC consist of blocks of 4 locations. The EPB2001 allows the designer to pre-specify up to 8 such ranges. The PS/2 POST (Power-On Self-Test) routines can then relocate the Multi- Function card's resources to eliminate address conflicts with other adapters. Any I/O base address can be selected for the block which resides on a 4-byte boundary.

The EPB2001 asserts the -DEN line for the data transceivers within 20 nS of the DT/-R line falling (write cycle to board). This signal falls within 20 nS of -ADL going active. The MC Bus spec has a minimum of 40 nS from -ADL active to -CMD active. The -CMD signal triggers -IOWR, and -IOWR has a delay of up to 20 nS, which tracks parametrically with the -DEN delay. As a result, there will be a minimum of 20 nS between -DEN falling and -IOWR falling. The 74AS245's have a 9 nS delay from enable input to outputs valid. Data is therefore present at the SCC

inputs 11 nS before the -IOWR (-WR strobe) input and supports data set-up time requirements of the Z8530.

The MC Bus requires drivers to tristate within 30 nS of -CMD going inactive. The 74AS245's 9 nS tristate delay, coupled with the 20 nS -CMD to -DEN delay on the trailing edge, is a good match with the bus spec.

#### INTERRUPT INTERFACE

The SCC may be programmed to run in either an interrupt-driven or DMA transfer mode. On this particular board, hardware has been provided to support either mode, allowing the board software driver to select the data transfer mechanism. The Z8530 can be programmed to issue an interrupt request each time a byte of data is received, when the transmit buffer is empty, or on a variety of error conditions. The reader is referred to the Z8030/Z8530 Data Sheet for further details.

To support interrupt-driven operation, an open-collector 24 mA driver is used to connect the SCC's -INT output to the MC Bus interrupt -IRQ3. While the SCC has an open-drain output, it's drive is

insufficient to handle the MC Bus lol requirements and must be re-buffered. Several prioritized -IRQx lines are available on the MC Bus, and in this case selection of the -IRQ3 line fixes the SCC's priority at a relatively low level, fourth lowest in the hierarchy. This is the alternate serial port level defined for the PS/2. The Z8530 specification requires that the dedicated interrupt acknowledge -INTACK become valid 250 nS before -RD becomes active. This is not feasible in a single bus cycle and complicates logic design. However, the Z8530 also supports interrupt servicing by providing a register (Read Register #2) which contains an interrupt vector, and interrupt reset bits in

Write Register #0. Interrupt acknowledge can therefore be treated as standard I/O read and write operations without special timing.

This Multi-Function card design does not use the channel check non-maskable interrupt protocol defined for the MC Bus. The -CHCK line, like the other interrupt lines on the MC Bus, is a level-sensitive, shared open-collector arrangement. A channel check request by any add-on card is wire ORed onto this line. Adapter logic can activate this line by an active-low pulse on the -SETCHK input to the EPB2001. This also resets POS register 0105H, bit 7 (when inactive, a logic one). By interrogating this location on each adapter, the PS/2 channel check handler can determine which card has issued the channel check request.

#### DMA INTERFACE

In this application, the Z8530 will handshake with the EPB2002 when DMA transfers are enabled. Due to constraints in the basic DMA structure of the Micro Channel / PS/2, only one DMA channel per adapter is allowed. As a result, only one SCC channel can issue DMA requests at a time. To make this feature software configurable, a DMA request source selector has been built into the BUSTER support device. It has the two -W/REQx outputs of the SCC as inputs, and generates either a -BRSTREQ or -BUSREQ line for the EPB2002. The DMA request mode is controlled by a POS register bit as outlined earlier. A POS register bit selects which channel is the DMA requestor. DMA requests can also be permanently disabled by another POS bit for interrupt-driven mode on both channels. Interrupt-driven operation may be used on one channel while DMA operation is employed on the other.

The Z8530 may be programmed to assert -W/REQx on a character receive or transmit buffer empty condition. This signal is routed to either the EPB2002 -BRSTREQ or -BUSREQ input, and results in the EPB2002 asserting -PREEMPT. Timing for the assertion is not critical.

Timing for the removal of the request is important, however. The Z8530 deasserts -W/REQx line 240 nS after the corresponding strobe goes active. This signal experiences a 35 nS delay in going through the DMA request selector in the EPB1400. In the burst transfer mode, the EPB2002 will deassert -BURST approximately 50 nS after this signal is deasserted, and at the same time BUSGNT will be deasserted. To properly terminate the cycle, -BURST must be inactive 35 nS before -CMD rises. Therefore, in order to guarantee correct burst operation, it is necessary that the strobe width (and therefore -CMD active width) be To guarantee the absence of DMA overrun (erroneous extra transfers), the DMA transfer cycle must be extended via wait states so this requirement is satisfied.

Since -BURST is not used in single transfer mode, this timing constraint need not be considered. However, for simplicity, in this design single transfer and burst wait-states will be the same.

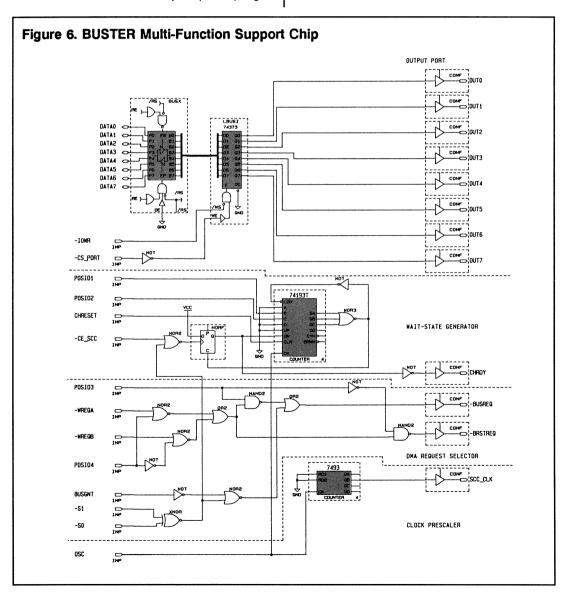

In of single transfer mode, it is necessary to deassert the -BUSREQ line on the occurrence of BUSGNT active and the -S0, -S1 status lines going to the active state (indicating start of the DMA transfer). The logic in the lower left of the BUSTER schematic (Figure 6) performs this function.

For burst transfers, the BUSGNT signal is not used on the adapter. Since the PS/2's resident DMA channels on the motherboard are being used, BUSGNT is not needed to communicate bus ownership. As long as -BURST is active, the DMA channels will execute transfer cycles. DMA acknowledge for both cases consists of the DMA channel actually accessing (reading/writing) the SCC data buffer. No dedicated DMACK lines appear on the MC Bus. In other applications, BUSGNT might be used to reset a request transfer flip-flop or otherwise indicate to board logic the granting of the bus.

### SERIAL INTERFACE

Minimal serial interfaces for Channel A & B are shown in this design. Modem control signals (-RTS, -CTS, -DCD) are not used to control data transfer over the RS-232 links. This could easily be added by programming the SCC for such operation and adding the appropriate buffers. With the arrangement shown, only the RxD, TxD and Ground lines for each RS-232 line need be connected.

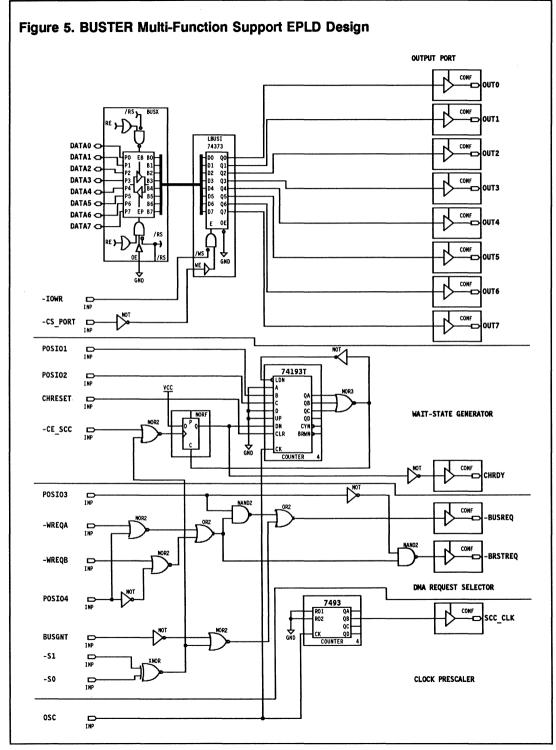

### BUSTER SUPPORT LOGIC

#### WAIT-STATE LOGIC

Overall strobe (-RD or -WR) width required by the SCC is 250 nS. Since the default MC Bus cycle provides only a 90 nS -CMD width, the cycle must be extended by use of a wait-state generator, in this case designed into a BUSTER component. The timing source for the wait-state generator, the OSC signal from the MC Bus, has a period of about 70 nS. The wait-state generator will pull CHRDY on the MC Bus inactive (low) for a number of OSC clock edges determined by a value written into a POS register bit field.

The number of wait-states is software programmable, and can be selected by parameters in

240 nS + 35 nS + 50 nS + 35 nS = 360 nS

the add-on card's Adapter Description File (ADF). The ADF, required for every add-on card, describes to the PS/2 the available address response ranges and configuration options for a given card. The system reads the board I.D. for each card in its backplane when the system is booted. The board I.D. is used to find the associated ADF file on the system's disk, and the information there is used to configure the adapter and/or to eliminate address range conflicts with other cards.

BUSTER's 28 MegaHertz operating frequency supports the wait- state generator and clock divider functions with considerable margin given the 14 MegaHertz clock inputs.

The number of wait-states can be varied from 0 to 6. A minimum number of clock edges to support the 250 nS width required by the 4 MegaHertz SCC is 4 x 70 nS = 280 nS. If DMA is used as described earlier, 6 x 70 nS = 420 nS must be used. The generator is triggered by an active -CE input to the SCC, indicating an Z8530 access to/from the MC Bus.

The actual wait-state generator consists of a loadable down-counter shown in Figure 6. The counter is automatically reloaded each time it reaches zero. While counting, CHRDY is held low.

### OUTPUT PORT

As an added feature, an output port is constructed in a portion of the BUSTER EPB1400 for general-purpose use. These 8 lines may be used to control whatever output functions are required. This block is shown at the top of Figure 6. It is entered using Altera's LogiCaps schematic capture package and TTL MacroFunction elements. The integral MPU data port on the EPB2001 simplifies the MC Bus interface.

This output port uses another of the EPB2001's -CSx outputs for selection during write operations. The -WS input to the EPB1400 is connected to the -IOWR output of the EPB2001. Since the output port is the only resource on the BUSTER device mapped into the I/O address space, no address inputs are needed.

BUSTER's write control interface timing is very simple: a minimum write strobe (-WS) low width of 20 nS will insure correct writing of the output port when accompanied by valid data and chip select. To be precise, data must be valid 7 nS prior to BUSTER's -WS input falling, and the chip select 10 nS prior to -WS falling. Since MC Bus data is valid at -CMD's leading edge (prior to -IOWR leading edge), and the EPB2001's -CSx lines are valid at least 55 nS prior to

-CMD falling, the minimum overlaps are easily satisfied. Minimum strobe width of 90 nS is also more than adequate.

STATIC RAM INTERFACE CONSIDERATIONS

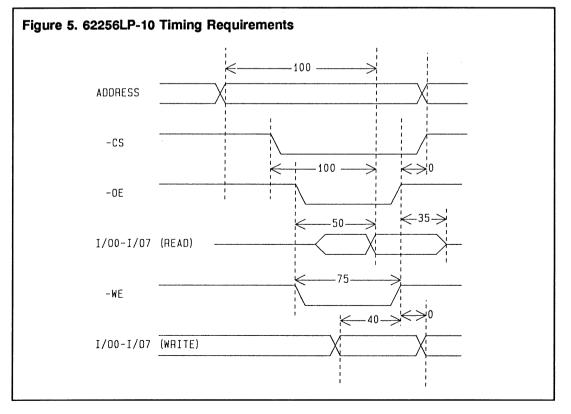

The 32K word static RAM on the Multi-Function card has been implemented using two 32K x 8 CMOS SRAM devices. These devices are 62256LP-10 RAMs, packaged in 28 lead, 600 mil DIP packages. The devices have 15 address inputs (A0-A14), eight bidirectional data lines (I/O0-I/O7), a chip select (-CS), output enable (-OE) and write enable (-WE).

For these chips, access time is 100 nS from address or chip select. Output enable delay from -OE to valid read data is 50 nS. Minimum write enable width (-WE) is 75 nS, with a 40 nS set-up time for of valid write data to -WE trailing edge.

As shown in the Multi-Function board schematic (Figure 1), addresses from the 74AS373's drive the SRAM address inputs. SRAM I/O's drive the upper and lower bytes of the board data bus. The -CE inputs

are driven by a -CSx output of the EPB2001, while -OE is connected to -MEMRD and -OE to -MEMWR.

As discussed earlier, the MC Bus guarantees 85 nS set-up of addresses to -CMD. 5 nS delay through the 74AS373's gives greater than 80 nS of address to -MEMRD or -MEMWR set-up at the SRAM devices. Even assuming minimum strobe width of 90 nS (minimum -CMD width on the MC Bus), this allows 170 nS of address access time at the SRAMs. Chip select access is reduced by the chip select decode delay on the EPB2001 (30 nS), but is still 140 nS.

Since the output enable delay on the SRAMs is 50 nS, even with a 9 nS delay through the 74AS245 transceivers, data is valid on the bus in time to meet the 60 nS MC Bus maximum delay for read data.

The SRAMs require 40 nS of valid write data / -WE overlap to guarantee correct writing of the selected locations. The MC Bus specifies 0 nS of write data set-up to the leading edge of -CMD, and a minimum 90 nS -CMD width. This results in 80 nS of overlap, more than adequate even with the 9 nS buffer delay.

# GENERAL EPB2001/2002 DESIGN TIPS

EPB2001 CHIP SELECT LOGIC USE IN 32-BIT SYSTEMS

The decoding inputs to the EPB2001 are labelled A0-A23. This allows full decoding of 24-bit MC Bus addresses down to the byte level. Even though 32 address inputs are not provided, the device is still applicable to 32-bit machines. This is true because the granularity required in chip select ranges is often quite coarse.

A typical adapter may be memory only, I/O only, or some mix of memory and I/O. A0-A2 on the EPB2001 must always be connected to the A0-A2 pins on the MC Bus to assure correct access of the POS registers and board I.D. If the A3-A23 inputs to the EPB2001 are connected to the A11-A31 lines on the MC Bus, the chip select logic can decode addresses down to block sizes of 2K bytes over the full 32-bit address range. Since most RAM chips in use today are much greater than 2K byte density, this is usually sufficient for memory addressing and memory-only applications.

Mixed memory/I/O adapters can also use this scheme. However, it implies that I/O peripherals also be placed on 2K byte boundaries, and is somewhat wasteful of the address space. Only 32 such blocks are available. Further decoding of A3-A10 external to the EPB2001 can reduce or eliminate this waste.

Pure I/O applications require only A0-A15. In such cases, more than enough address inputs are available on the EPB2001 for 16- or 32-bit applications.

#### ALTERNATIVE ADDRESS INPUT USE

If an I/O-only adapter is being designed, or one for 16-bit applications specifically, all 24 address inputs, as well as MADE24 may not be needed. In such cases, these inputs may be used to provide additional board-specific functions.

For example, it may be desireable to generate read or write strobes for specific board I.C.'s. These strobes may be generated as an address decode logically ANDed with a transfer strobe. The -- CMD signal on the MC Bus typically functions as such a strobe. By connecting an unused Ax pin to -CMD, it can be factored into appropriate read or write strobes.

ALTERNATIVE USES FOR THE EPB2001 CHIP SELECT LOGIC BLOCK

The chip select programmable logic block on the EPB2001 is primarily used to generate adapter chip select signals. Some other uses for this logic includes:

Latched Addresses

-CSx outputs of the EPB2001 may be used as latched address outputs for general use on the add-on card. In this case, the programmable chip select block is programmed to drive the corresponding output low whenever the desired address input is low. The output is latched by -ADL. When used for this purpose, the corresponding -CSx output is not factored into the -CDSFDBK line to the Micro Channel (an EPB2001 programmable feature).

Additional POS Register Bit Access

-CSx outputs of the EPB2001 may be used to access POS register bits (output only). These may be used to increase POS register output pins to 24 from the 16 POSI/O lines dedicated for this purpose.

Data Size Feedback

-CSx outputs have sufficient drive to directly drive the -CDDS32 and -CDDS16 lines on the Micro Channel. These signals indicate a devices's data bus width as 32 or 16 bits, respectively. They are derived as unlatched decodes of appropriate address ranges.

As described in the EPB2001/2002 Data Sheet, chip select address ranges may be enabled by any combination of POS register bits. Typically, a bit field is designated within a POS register to act as an Address Relocation control field. It may be desireable to factor into certain chip select enabling functions special bits such as POS 0102 bit 0 (card enable) or POS 0105 bit 7 (channel check). In this way, chip selects may be selectively disabled when the card is

# ADERA

disabled or during error recovery (channel check) routines.

# MC MAP SOFTWARE SUPPORT

The MC Map Micro Channel Interface Assembler, available from Altera, provides an easy table-driven entry mechanism for specifying EPB2001 designs. All programmable options mentioned above are easily specified using this PC-based package. Once design entry is finished, the design is compiled in less than a minute and the resulting JEDEC file may be used to program the EPB2001. Programming of the component may be accomplished using Altera's PC-based hardware: an LP4 or LP5 programming card, PLE3-12 Master Programming Unit and PLEJ2001 programming pinout adapter. The actual device is programmed in seconds and ready for use on the board.

Further information on the MC Map software and programming hardware may be obtained from Altera's Marketinggroup.

### SUMMARY

The EPB2001 and EPB2002 Micro Channel interface devices provide all required interface functions between an IBM PS/2 add-on board and the system bus. The programmable nature of the EPB2001 provides many possibilities for implementing adapter-specific functions. Coupled with other EPLDs such as BUSTER for unique applicationfeatures, extremely efficient interfaces for PS/2 adapters can be rapidly designed and implemented.

WHERE TO GET MORE INFORMATION

Information on IBM's Independent Developer Assistance Program may be obtained from IBM through

IBM Independent Developer Assistance Program - (800)426-7736

Registration in this program is a prerequisite for obtaining technical assistance and board I.D. assignments from IBM.

Specifications and technical reference manuals may be obtained from IBM through

IBM Technical Directory - (800)426-7282

### REFERENCES

1. EPB2001/2002 Data Sheet, Rev. 1.0, February, 1988

2. Z8030/Z8530 Data Sheet, Rev. E, August, 1987

3. IBM Personal System/2 Model 50/60 Technical Reference (IBM# 68X-2224)

4. IBM Personal System/2 Model 80 Technical Reference (IBM# 68X-2256)

5. IBM Personal System/2 Model 50,60,80 Micro Channel Architecture (IBM# G360-2637) Rev. 5.3, May,1987

6. Altera Data Book, January, 1988

### CONTENTS

- Programmable Option Select (POS)

- Micro Channel Adapter Installation

- Adapter Description Files (ADF)

- Installation Procedure

- Power-On Self-Test (POST)

- Utility to read back Adapter I.D. and POS Register contents

- Altera Multi-Function Adapter Description File

- Software Driver Source Code

## INTRODUCTION

This Application Note provides the software design aspects for an adapter card for the IBM Micro Channel bus architecture, described in Application Note 14. Configuration and installation information for Micro Channel-based adapter cards is also discussed. Included is a utility to interrogate each adapter slot and read back the adapter I.D and POS register contents.The Altera Multi-Function adapter card developed for the IBM PS/2 Models 50/60/80 is described. The Adapter Description File( ADF) and a software driver written for this adapter illustrate the software design issues involved. This note, together with Application Note #14, provide tested hardware and software design examples to speed and simplify IBM PS/2 add-on card design using Altera's user-configurable solutions.

The card is designed utilizing Altera's Micro Channel interface and DMA arbitration chips, the EPB2001 and EPB2002. The Altera EPB2001 and EPB2002 Micro Channel Bus interface chips handle interface requirements for a PS/2 adapter, ranging from POS register implementation and address range definition for chip selects to bus arbitration for single cycle or "burst" DMA transfers. For a detailed description and timing information related to the Altera Multi-Function add-on card, the reader is referred to Altera Application Note 14 entitled "PS/2 Add-on Card Interfacing With The EPB2001 and EPB2002".

# PROGRAMMABLE OPTION SELECT (POS)

The Programmable Option Select (POS) feature specified in the Micro Channel Bus Architecture for IBM PS/2 Models 50/60/80 eliminates configuration switches on add-on cards or adapters. Programmable

# IBM PS/2 ADD-ON CARD SOFTWARE DESIGN

Option Select registers are implemented through programmable registers residing at I/O addresses 0100 Hex through 0107 Hex on each add-on card. Other objectives of POS are to permit installation of multiple identical feature cards, positive identification of any card by slot and resolution of resource assignment conflicts. Each add-on card type needs to be identifiable by a unique 16-bit I.D. number. The adapter I.D. is implemented by providing two read-only registers at addresses 0100H (for the low order byte) and 0101H (for the high order byte) on every card.

IBM has published the following guidelines for adapter I.D numbers:

| 0000       | Device not ready               |

|------------|--------------------------------|

| 0001-0FFF  | Bus Master                     |

| 5000 -5FFF | DMA devices                    |

| 6000-6FFF  | Direct program control or      |

|            | memory-mapped I/O              |

| 7000-7FFF  | Storage or multifunction cards |

| 8000-8FFF  | Video                          |

A card developer must register with the IBM Independent Developer Assistance Program (IDAP). Call (800) 426-3333 for information. An IBM IDAP number is assigned to the developer which must be used for further inquiries and technical assistance including obtaining adapter I.D. numbers.

The Micro Channel specification is quite complex. The reader is encouraged to review the IBM Technical Reference Manual for the applicable PS/2 Model (50/60/80). The EPB2001 and EPB2002 greatly simplify the Micro Channel interface portion of an add-on card design and insure compatibility with the Micro Channel specification.

# ADAPTER INSTALLATION

ADAPTER DESCRIPTION FILES

After the add-on card hardware design is complete, based on the POS register bit assignment, an Adapter Description File (ADF) must be created on a 3 1/2" diskette. The ADF should be an ASCII file and may be created using any text editor. Each add-on card or adapter must have a separate ADF with file name @CARDID and an extension of "ADF" prior to installation. For example, an adapter that uses an I.D. of ABCD Hex (POS Reg. at address 0100H contains the byte CD and POS Reg. at address at 0101H contains the byte AB), must be accompanied by an ADF named @ABCD.ADF on a 3 1/2" diskette called an option diskette. The ADF provides information regarding POS settings and usage of resources for

Automatic Configuration. The ADF also provides input for the System Configuration Utilities (these are packaged with every system on a 3 1/2" Reference diskette), help screens and prompts. The ADF provides to the PS/2 configuration utilities information regarding the available address response ranges and configuration options for a given card. The system reads the board I.D. for each card in its backplane when the system is booted and compares it to the information stored in its CMOS RAM. When a new adapter is installed the board I.D. is used to find the associated ADF file on the configuration/option diskette, and the information there is used to configure the adapter and/or to eliminate address range conflicts with other cards. The ADF syntax is available in the IBM Technical Reference Manual for any of the Micro Channel-based Models.

The System Configuration Utilities automatically create configuration data using the ADF files supplied for each add-on card (adapter) by matching the unique adapter I.D. with an ADF file. The configuration data is subsequently stored on battery-backed CMOS RAM along with the adapter I.D. numbers.

#### CREATING AN ADF

Syntax for creating an ADF is available in the relevant IBM PS/2 Model Technical Reference Manual. Syntax rules must be followed strictly since the error messages generated by the system during configuration are terse and do not point specifically to syntax rule violations. For example, if the "Help" field in a NamedItem structure is omitted, a seemingly unrelated divide overflow exception error is flagged. The ADF syntax is not case sensitive.

The following notation is used to refer to the POS registers in the ADF:

pos[0] - POS register at I/O address 0102H pos[1] - POS register at I/O address 0103H pos[2] - POS register at I/O address 0104H pos[3] - POS register at I/O address 0105H

CAUTION: Bit 0 in pos[0] and bit 7 in pos[3] are reserved for Card Enable and -CHCK (Channel Check) functions and must not be written to. The letter "X" must be specified in the respective bit positions in the ADF when specifying configuration data for POS registers 0 and 3 to avoid writing to those two bits.

The NamedItem structure is used to specify a field providing a choice of resource or configuration options. The text within quotes following the keyword "Prompt" is what appears in the View/Change Configuration Screen when Set Configuration under the System Configuration Utilities is invoked. This text field must contain a brief description of the resource or option being controlled so that the user can choose a particular option.

The text within quotes following the "choice" keyword associates the bit pattern in the POS register to one of the configuration choices that the resource may have. This text is displayed in a field in the configuration screen. The user steps through this field using [Next] and [Previous] function keys while the various "choices" to which the resource may be configured are displayed. The actual POS bits are therefore transparent to the user. The last portion of the choice structure is an optional resource qualifier e.g. arb for arbitration level, mem for memory address space, i/o for i/o address space. If the resource does not fall into one of the categories specified in the syntax rules, this field may be omitted.

For customizing the configuration, the user invokes Change Configuration in the Set Configuration menu under the System Configuration Utilities. If a particular choice conflicts with a previously assigned configuration for the same resource while stepping through the various "choices" for a resource a "\* Conflicts" flag appears at the top right hand corner of the screen and an \* appears next to the field that caused the conflict. The conflict can be resolved by stepping through and choosing a different resource choice either for the new adapter or for the existing adapter. In each field the user may invoke help by pressing the F1 function key whereby the text within quotes following the Help keyword appears.

#### INSTALLATION PROCEDURE

Make a back-up copy of the Reference diskette (the original diskette is read-only) to allow update of the system configuration after installation of a new adapter. The ADF file for the adapter being installed may either be on a separate option diskette or it may also be on the back-up diskette.

Power-up the system with the Reference diskette (the original one) in drive A. The System Configuration Utilities Screen comes up (blue screen with the IBM logo).

Press ENTER to continue and invoke "Set Configuration". In the Set Configuration menu invoke the "Copy an Option Diskette" utility.

When prompted for the new option diskette, insert the back-up diskette (or the option diskette as the case may be) in drive A. At this point the new ADF or option file is read and the new adapter configuration information is merged with the previous information.

Use "Back-up Configuration" to write the up-to-date configuration data on the back-up diskette. This diskette should subsequently be used whenever System Configuration Utilities need to be run. Re-start the computer without the back-up diskette in drive A. This time the system boots up with the updated configuration stored in the battery-backed CMOS RAM.

If the system boots up, the adapter has been installed successfully. In order to view the updated configuration, insert the back-up diskette in drive A. Make A: the default drive and invoke "sc". This invokes the Set Configuration utility under the System Configuration Utilities. While in the Set Configuration menu, the user may simply view the current configuration, or invoke another utility within this menu to "Change the Configuration".

# POWER-ON SELF-TEST (POST)

Power-On Self-Test (POST) The process automatically configures the system. POST verifies whether the configuration has changed by reading each adapter I.D. number and comparing it to the values stored in CMOS RAM for that slot. If the configuration has changed, System Configuration Utilities on the Reference diskette need to be run again. A configuration error is flagged by the number "165" on the screen at system power-up. A change in configuration occurs if a new card is installed or if a card that was part of the existing configuration has been removed. In either case configuration error number 165 is flagged.

If an adapter is turned off (e.g. an external drive or the terminal) or is not working properly, error number "162" occurs. When this error occurs, make sure the adapters and devices attached to the adapter cards have power. Boot the system with the back-up diskette in drive A and follow the prompts in the System Configuration Utilities. If cards are moved to different slots, POST flags error number 165. In this case, follow the prompts for running "Automatic Configuration". POST automatically reconfigures the system and updates the CMOS RAM accordingly.

Figure 1 contains a listing of the source code in "C" for a utility that interrogates each slot in the system. It runs setup cycles to each adapter in order to read back the contents of I/O addresses 0100H to 0105H. This routine was utilized on a PS/2 Model 80 to read back POS register contents of adapters in all the 8 slots. It may be further tailored to suit the system under consideration. e.g. Registers pos[4] and pos[5] at addresses 0106H and 0107H respectively may be read back to obtain the low and high bytes of the subaddress extension, if applicable. The number of slots being interrogated may also vary depending on the model.

The utility confirms the POS bit settings slotwise, for the various NamedItem(s) in the ADF file.

The source file is available under the file name "rdpos.c" on the Altera Bulletin Board Service.

Figure 2 contains the output listing as obtained by running the utility on a PS/2 Model 80 with a disk controller adapter card (CARDID = DFFDH) in slot #8 and the Altera Multi-Function card (CARDID = 6789H) in slot #6. The configuration is:

| Slot #1-5 | Empty                     |

|-----------|---------------------------|

| Slot #6   | Altera MultiFunction Card |

| Slot #7   | Empty                     |

| Slot #3   | HardDisk                  |

The empty slots read back as FF Hex at the POS I/O addresses.

# ADAPTER HARDWARE DESCRIPTION

The block diagram in Figure 3 shows the overall structure of the Multi-Function card design. The board has 32Kx16 memory, a serial communications chip (AmZ8530) and the Altera Micro Channel Bus Interface and DMA arbitration chips, EPB2001 and EPB2002. The common Micro Channel Bus lines are shown on the right. The EPB2001 provides the POS register functions mandated by the IBM specification for any add-on card interface. In addition, board control logic, board I.D. storage and address decoding are integrated onto the chip. The EPB2002 provides DMA arbitration and fully supports the IBM bus exchange protocols.

The Altera Multi-Function adapter card is designed so that it appears to the PS/2 as either an 8-bit I/O peripheral (for accesses to the 8530 Serial Communications Controller), or as a 16-bit memory extension (32K words). The two 74AS245 transceivers buffer data during transfers between the Micro Channel and I/O or memory. Two 74AS373 flow-through latches are used to latch addresses during bus transfers. The -ADL line from the MC Bus controls the latching. Only the 16 low-order address bits need to be latched since memory capacity is 64K (2\*\*16). The EPB2001's chip select logic handles upper-order address decoding for the various I/O and memory chips on the board. A separate write-only output port designed using an EPB1400 EPLD is also available. The 8530 Serial Communications Controller (SCC) chip provides two serial channels in a single 40-pin device. The chip supports a variety of synchronous and asynchronous communication modes, on-chip data buffering, and an integral baud-rate generator. The 8530 includes handshake lines for DMA Request/Acknowledge which interface to the EPB2002. The EPB2002 requests use of the MC Bus via the -PREEMPT line in response to requests from the SCC. The clock for the SCC is provided by a divide-by-four clock derived from the OSC line on the MC Bus. The clock divider is implemented in a portion of an EPB1400 EPLD (BUSTER). The OSC line provides a precise 14.31818

#

```

Figure 1. Utility to Read Adapter I.D. and POS Register Contents

/* *********

(c) 1988 Altera Corp.

*/

*'/

/*

*'/

/* File Name "rdpos.c", available on the Altera Bulletin

/* Board Service.

*/

/*

*/

/* This program runs 'setup' cycles for each slot in order

*/

/* to obtain setup information such as the CARD I.D. and

*/

/* contents of the POS Registers. This involves I/O oper-

*/

/* ations to the Channel Position Select Register residing

/* at port 0096H. Details available in the IBM Technical

*/

/* Reference Manual. Microsoft "C" Ver. 5.0 utilized

*/

/*

/*

*/

#include <stdio.h>

#include <conio.h>

/* Low byte of cardid read at 0100H

*/

#define cardidl 0x0100

#define cardidh 0x0101 /* Upper byte of cardid read at 0101H

*/

/* I/O address for POS Register 0 = 0102H */

#define posio0 0x0102

/* I/O address for POS Register 1 = 0103H */

#define posio1 0x0103

/* I/O address for POS Register 2 = 0104H */

#define posio2 0x0104

/* I/O address for POS Register 3 = 0105H */

#define posio3 0x0105

main()

{

int data, i;

int port96, reset;

int val[10];

struct adapt

int crdidl;

int crdidh;

int pos0;

int pos1;

int pos2;

int pos3;

} adapter[8];

/* for the eight slots in a Model 80 PS/2 */

port96 = 0x0096;/* Channel Position Select Register at 0096H */

/* val[] contains bit patterns to select the channel position */

/* where the subsequent setup cycle (low active pulse on

/* -CD SETUP(n) ) may be run.

/* Bit pattern 00001111B for Slot position 8 */

val[7] = 0x0F;

val[6] = 0x0E;

val[5] = 0x0D;

val[4] = 0x0C;

val[3] = 0x0B;

val[2] = 0x0A;

val[1] = 0x09;

val[0] = 0x08;

reset = 0x00;

```

### Figure 1. (Continued)

```

for (i=0 ; i<= 7; i++){

outp(port96,val[i]); /* Select Channel Position */

adapter[i].crdidl = inp(cardidl);

adapter[i].crdidh = inp(cardidh); /* Read info. */

adapter[i].pos0 = inp(posio0); /* at I/O

adapter[i].pos1 = inp(posio1); /* addresses

*/

*/

adapter[i].pos2 = inp(posio2); /* 0100H to

*/

adapter[i].pos3 = inp(posio3); /*

0105H */

printf ("\n\n The CARD ID at Slot # ");

printf ("%d", i+1);

printf (" is %X%X \n", adapter[i].crdidh, adapter[i].crdidl);

printf ("\n POS Register Contents for this Adapter are:");

printf ("\n POS Req. ");

printf ("%02X

%02X", posio0, adapter[i].pos0);

printf ("\n POS Reg. ");

printf ("%02X

%02X", posio1, adapter[i].pos1);

printf ("\n POS Reg. ");

printf ("%02X

%02X", posio2, adapter[i].pos2);

printf ("\n POS Reg. ");

%02X", posio3, adapter[i].pos3);

printf ("%02X

} /* end for loop */

/* Reset Channel Position Select Register */

outp(port96,reset); /* No op. value = 00000XXXB */

} /* end main*/

```

# Figure 2. Output Listing of Utility

Output Listing (c) 1988 Altera Corp. The CARD ID at Slot # 1 is FFFF POS Register Contents for this Adapter are: POS Reg. 102 FF POS Reg. 103 FF POS Reg. 104 FF POS Reg. 105 FF The CARD ID at Slot # 2 is FFFF POS Register Contents for this Adapter are: POS Reg. 102 FF POS Reg. 103 FF POS Reg. 104 FF POS Reg. 105 FF The CARD ID at Slot # 3 is FFFF POS Register Contents for this Adapter are: POS Reg. 102 FF POS Req. 103 FF POS Reg. 104 FF POS Reg. 105 FF The CARD ID at Slot # 4 is FFFF POS Register Contents for this Adapter are: POS Reg. 102 FF POS Reg. 103 FF POS Reg. 104 FF POS Reg. 105 FF The CARD ID at Slot # 5 is FFFF POS Register Contents for this Adapter are: POS Reg. 102 FF POS Reg. 103 FF POS Reg. 104 FF POS Reg. 105 FF The CARD ID at Slot # 6 is 6789 POS Register Contents for this Adapter are: POS Reg. 102 75 POS Reg. 103 FF POS Reg. 104 FF POS Reg. 105 **A**3 The CARD ID at Slot # 7 is FFFF POS Register Contents for this Adapter are: POS Reg. 102 FF POS Reg. 103 FF POS Reg. 104 FF POS Reg. 105 FF The CARD ID at Slot # 8 is DFFD POS Register Contents for this Adapter are: POS Reg. 102 09 POS Reg. 103 F3 POS Reg. 104 FF POS Reg. 105 FF

# ANDIERA

MHz clock. The clock divider generates a 3.58 MHz output for the SCC.

Wait-state logic associated with the 8530 is also designed into the same EPB1400 device. In a Micro Channel default bus cycle, the width of the -CMD bus transfer strobe may be as narrow as 90 ns. The 4 MHz 8530 used in this design requires a 250 ns minimum width on -RD and -WR to the device. As a result, the bus cycle must be "stretched" at least 160ns. This is done by inserting wait-states to extend the cycle. This logic is described in detail in Application Note 14. The two CMOS SRAM chips used in this design have 100 ns address access times. As such, access to these chips requires no wait-states.

The two pairs of serial data lines (RxD and TxD, Channels A and B) from the SCC are connected to 1488/1489 line driver/receivers which form RS-232-compatible interfaces. In this application, the full DCD/CTS/RTS handshake has not been shown. This could be implemented by the addition of buffers between the RS-232 links and the SCC modem control pins. The + 12V/-12V supply required by these drivers is obtained from the Micro Channel edge connector.

#### MULTI-FUNCTION CARD POS FUNCTIONS

In this Multi-Function application, the EPB2001 provides the primary control interface. As required for any MC Bus add-on card, the EPB2001 provides two CMOS EPROM bytes at locations 0100-0101H for the board I.D. These are read-only locations accessible from the MC Bus. These I.D.'s are unique to a given board design and are allocated by IBM to registered Independent Developers. The developer must contact IBM directly for such I.D.'s. Four read/write POS registers located at addresses 0102-0105H are used in this application to control I/O remapping, memory remapping, number of I/O wait-states, DMA request source selection, Bus(single cycle) or Burst request and DMA arbitration level and Fairness. The DMA arbitration level and the Fairness bit are also mapped into the satellite POS register bits on the EPB2002. The bit-mapping of these functions is illustrated in Figure 4. POS bits which are required outside the EPB2001 are brought-out via the POS I/O pins.

Each of the chip selects has 8 pre-programmed ranges controlled by the address remapping fields specified in the POS registers. The programmable POS chip select enable decoder provides a unique mechanism for linking the POS registers to the chip select decode block. In this way the PS/2 can control address response ranges for the card and associated memory / I/O resources as it configures the system. This is used to eliminate address conflicts between cards without mechanical setting of DIP switches or jumpers, an error-prone process. The EPB2002 implements the bus arbitration protocol defined for the Micro Channel in an asynchronous state machine. POS register bits are included which are readable and writeable from the MC Bus. These bits control the four-bit Arbitration Level for the board (arbitration priority) and enable Fairness (Fairness is a mechanism specified by IBM to eliminate bus "hogging" by bursting DMA devices).

The bit positions and POS register location where these bits will be mapped is up to the board designer. The MC Bus specification does not define required POS locations for them. Any of POS registers 0102-0105H may be used for this purpose (except bit 0 in POS register at 0102H and bit 7 in POS register at 0105H.) The EPB2002 allows the remapping of these bits by appropriate connections to the SELx inputs to the chip. This is described in detail in the EPB2001/2002 Data Sheet. By connecting the SELx inputs as shown in Figure 3, these bits have been mapped into POS register 0104H for this application, bit locations D3-D7 on the data bus.

#### 8530 INTERFACE CONSIDERATIONS

Basic signals involved in interfacing the 8530 to an MPU bus(the MC Bus in this case) are -CE (Chip Enable), A/-B (Channel A/B designator), D/-C (Data/Control Select), -RD (Read Strobe), -WR (Write Strobe) and the 8-bit data bus, D0-D7. A leading hyphen indicates an active low signal name. The 8530 includes 9 Read-able and 15 Write-able registers to set device configuration, report status and access data. To reduce address input pin requirements, the 8530 uses the concept of an address pointer register: any command register access (read or write) must be preceded by a write to the SCC with D/-C low and the address of the register to be accessed on the next cycle as the associated data. After the subsequent access, the pointer register is automatically reset to the address pointer register. Every command register access is thus a two bus cycle process: write address pointer, write or read selected register. The receive and transmit data registers only require a single bus cycle with the D/-C input held high.

#### DMA INTERFACE

In this application, the 8530 will handshake with the EPB2002 when DMA transfers are enabled. Due to constraints in the basic DMA structure of the Micro Channel / PS/2, only one DMA channel per adapter is allowed. As a result, only one SCC channel can issue DMA requests at a time. To make this feature software configurable, a DMA request source selector has been built into the BUSTER support device. It has

#

the two -W/REQx outputs of the SCC as inputs, and generates either a -BRSTREQ or -BUSREQ line for the EPB2002. The DMA request mode is controlled by a POS register bit as outlined earlier. A POS register bit selects which channel is the DMA requestor. DMA requests can also be permanently disabled by another POS bit for interrupt-driven mode on both channels. Interrupt-driven operation may be used on one channel while DMA operation is employed on the other.

The 8530 may be programmed to assert -W/REQx on a character receive or transmit buffer empty condition. This signal is routed to either the -BRSTREQ or -BUSREQ input on the EPB2002, and results in the EPB2002 asserting -PREEMPT. Minimal serial interfaces for Channel A & B are shown in this design. Modem control signals (-RTS, CTS, -DCD) are not used to control data transfer over the RS-232 links. This could easily be added by programming the SCC for such operation and adding the appropriate buffers. With the arrangement shown, only the RxD, TxD and Ground lines for each RS-232 line need to be connected.

#### OUTPUT PORT (EPB1400 EPLD)

As an added feature, an output port is constructed in a portion of the BUSTER EPB1400 for general-purpose use. These port output lines may be used to control output functions in software. This block is shown at the top of Figure 5. It is entered using Altera's LogiCaps schematic capture package and TTL MacroFunction elements. The integral MPU data port on the EPB2001 simplifies the MC Bus interface. This output port uses another of the EPB2001's -CSx outputs for selection during write operations. The -WS (write strobe) input to the EPB1400 is connected to the -IOWR output of the EPB2001. Since the output port is the only resource on the BUSTER device mapped into the I/O address space, no address inputs are needed.

### ALTERA ADD-ON CARD ADF

The Adapter Description File (ADF) for the Altera adapter is presented in Figure 6. Note how the bit assignment indicated in Figure 4 is specified through the NamedItem structure in the ADF. POS registers 0,1,2 and 3 are implemented in this Multi-Function interface; hence NumBytes = 4 (in the ADF).

Syntax for generating an ADF is described in the IBM Technical Reference Manual for Micro Channel-based PS/2 models. The following listing of the ADF file @6789.ADF for the Altera Multi-Function adapter card illustrates how the ADF file is constructed once the POS register bits are assigned to implement specific control functions. The CARDID

implemented in the read-only POS registers at addresses 0101H and 0100H is 6789H.

Features on the multi-function card such as the number of wait-states, the SCC channel select (A or B), the mode of DMA request (Bus or Burst) and the arbitration level are software programmable, and can be selected in the System Configuration Utilities' "Change Configuration" screen. The Change Configuration screen for the ADF described herein will appear as shown in Figure 7.

NOTE: Each time the configuration is changed, the System Configuration Utilities need to be run off the back-up diskette, the changes backed-up and the computer re-booted without the configuration diskette in drive A in order to effect the changes.

### A SAMPLE SOFTWARE DRIVER

The driver for the Altera Serial Port adapter has been developed using Microsoft "C" Ver. 5.0. The source code is documented to indicate how the 8530 Serial Communications Controller (SCC) and the DMA controller are configured for the application. For detailed technical information regarding the SCC, the user is referred to the 8530 Technical manual or the Data Book. Information regarding programming the DMA controller (8237) can be obtained from the IBM Technical Reference Manual for the PS/2 model under consideration.

File name: dmalpb.c (DMA transfer, SCC Local Loopback). Source code listing is included herein and is also available on Altera's Bulletin Board Service.

Function: To provide a software loopback test for the SCC using a PS/2 DMA channel on the motherboard.

Hardware Setup

On the adapter board the Tx Data pin for SCC Channel A is connected directly to the Rx Data pin for Channel B.

#### Software Setup

SCC Channel A - configured for Transmission at 1200 baud, 8 data bits, 1 stop bit and no parity. Tx clock is sourced by the on-chip baud rate generator.

SCC Channel B - configured for Receiving at 1200 baud, 8 data bits, 1 stop bit and no parity. Rx clock is also sourced by the baud rate generator.

In the driver, a wait loop has been inserted between successsive read/write operations to the SCC control registers due to timing constraints (Refer to Section 3.2 of the AmZ8530 Technical Manual).

Using a system call in "C" (segread), the data segment register contents are read and the actual run-time address assigned to an array is calculated. This address in memory is used by the DMA controller for data writes.

11

#

# Figure 6. Multi-Function Card Adapter Description File (ADF)

AdapterID 06789h AdapterName "Altera Multi-Function Card" NumBytes 4 NamedItem Prompt "I/O Remapping" Choice "I/O Range 1" pos[0]=000XXXXXb io 6000h-600Fh Choice "I/O Range 2" pos[0]=001XXXXb io 6400h-640Fh Choice "I/O Range 3" pos[0]=010XXXXb io 6800h-680Fh Choice "I/O Range 4" pos[0]=011XXXXb io 6COOh-6COFh Choice "I/O Range 5" pos[0]=100XXXXXb

pos[0]=100XXXXD io 7000h-700Fh Choice "I/O Range 6" pos[0]=101XXXXD io 7400h-740Fh Choice "I/O Range 7" pos[0]=110XXXXD io 7800h-780Fh Choice "I/O Range 8" pos[0]=111XXXXD io 7C00h-7C0Fh

Help

"This field assigns an address range in which the SCC registers may be accessed."

```

Figure 6. (Continued)

NamedItem

Prompt "Memory Remapping"

Choice "Memory Range 1"

pos[0]=XXX000XXb

mem 200000h-20ffffh

Choice "Memory Range 2"

pos[0]=XXX001XXb

mem 210000h-21ffffh

Choice "Memory Range 3"

pos[0]=XXX010XXb

mem 220000h-22ffffh

Choice "Memory Range 4"

pos[0]=XXX011XXb

mem 230000h-23ffffh

Choice "Memory Range 5"

pos[0]=XXX100XXb

mem 240000h-24ffffh

Choice "Memory Range 6"

pos[0]=XXX101XXb

mem 250000h-25ffffh

Choice "Memory Range 7"

pos[0]=XXX110XXb

mem 260000h-26ffffh

Choice "Memory Range 8"

pos[0]=XXX111XXb

mem 270000h-27ffffh

Help

"To configure this adapter you must choose

the base address for the memory that the

adapter will use for buffering data. There are

Eight memory ranges that can be selected.

Under normal circumstances, select <Segment

200000>."

NamedItem

Prompt "DMA Request Mask"

Choice " Disable DMA "

pos[1]=XX0XXXXb

Choice " Enable DMA "

pos[1]=XX1XXXXb

Help

"This field lets you enable or disable

DMA requests."

```

# Figure 6. (Continued)

NamedItem Prompt "Interrupt Mask" Choice " Disable Interrupt " pos[1]=XXX0XXXXb

Choice " Enable Interrupt " pos[1]=XXX1XXXXb Help "This bit field lets you enable or disable Interrupts." NamedItem Prompt "Number of Wait States" Choice " 0 Wait States" pos[1]=XXXXXX00b Choice " 2 Wait States" pos[1]=XXXXXX01b Choice " 4 Wait States" pos[1]=XXXXX10b Choice " 6 Wait States" pos[1]=XXXXX11b Help " This determines the number of wait states introduced. Under normal circumstances, select <6 Wait States>." NamedItem Prompt "Fairness Option" Choice "Fair" pos[2]=1XXXXXXb Choice "Linear Priority" pos[2]=0XXXXXXb Help "This bit-fields selects the way in which the device competes during arbitration." Under normal circumstances, select <Fair>."

# Figure 6. (Continued)

NamedItem Prompt "DMA Arbitration Level" Choice "Level 0" pos[2]=X0000XXXb arb 0 Choice "Level 1" pos[2]=X0001XXXb arb 1 Choice "Level 2" pos[2]=X0010XXXb arb 2 Choice "Level 3" pos[2]=X0011XXXb arb 3 Choice "Level 4" pos[2]=X0100XXXb arb 4 Choice "Level 5" pos[2]=X0101XXXb arb 5 Choice "Level 6" pos[2]=X0110XXXb arb 6 Choice "Level 7" pos[2]=X0111XXXb arb 7 Choice "Level 8" pos[2]=X1000XXXb arb 8 Choice "Level 9" pos[2]=X1001XXXb arb 9 Choice "Level 10" pos[2]=X1010XXXb arb 10 Choice "Level 11" pos[2]=X1011XXXb arb 11 Choice "Level 12" pos[2]=X1100XXXb arb 12 Choice "Level 13" pos[2]=X1101XXXb arb 13 Choice "Level 14" pos[2]=X1110XXXb arb 14 Help "This selects the adapter arbitration level."

# Figure 6. (Continued)

NamedItem Prompt "DMA Mode" Choice "Single Transfer" pos[3]=XX1XXXXXb Choice "Burst Transfer" pos[3]=XX0XXXXb Help "This field simulates the adapter's mode of request for the bus."

NamedItem Prompt "SCC Channel Select for DMA" Choice "CHANNEL A " pos[3]=XXX0XXXb Choice "CHANNEL B " pos[3]=XXX1XXXb Help "Determines which SCC channel requests will be honored."

```

Figure 7. A Sample Change Configuration Screen

_____

* Conflicts

Change Configuration

_____

Total System Memory

Built In Features

Slot1 - Empty

Slot2 - Empty

Slot3 - Empty

Slot4 - Empty

Slot5 - Empty

Slot6 - Altera Multi-Function Card

I/O Remapping ..... [I/O Range 1]

Memory Remapping ..... [Memory Range 2]

DMA Request Mask ..... [Disable DMA]

Interrupt Mask ..... [Enable Interupt ]

Fairness Option ..... [Fair

1

DMA Arbitration Level ..... [Level 10 ]

DMA Mode ..... [Single Transfer]

SCC Channel Select for DMA ..... [Channel B]

Slot7 - Empty

Slot8 - IBM Fixed Disk Adapter

Type of first drive ..... [ --]

Type of second drive ..... [ --]

Arbitration Level ..... [Level_10] *

THIS WINDOW DISPLAYS FUNCTION KEYS FOR CHANGE CONFIGURATION

_____

```

Figure 8.

Software Driver Listing

/\*----(c) 1988 Altera Corporation------(c) Ch. A on the SCC is configured to Tx & Channel B to Rx /\* This program is set up to receive Data on Ch. B from an /\* external source and the block of data stored in an array \*/ The DNA controller is then set up to perform memory write\*/ transfers, to transfer the received block of data into \*) memory. #include <stdio.h> #include <conio.h> #include <dos.h> #define wait\_count 2 #define array size 64 idefine xfer\_count 15 main() int scc\_addr\_chbc = 0x6000L; /\* SCC address for Ch. B control \*/ int scc\_addr\_chbd = 0x6001L; /\* SCC address for Ch. B data int scc\_addr\_chac = 0x6002L; /\* SCC address for Ch. A control \*/ int scc\_addr\_chad = 0x6003L; /\* SCC address for Ch. A data int port\_addr = 0x8000L; /\* Output Port address \*/ int i, data, ndata, dummy\_cntr, count, flag ; struct SREGS segregs; int array[array\_size]; /\* This array contains the block of data \*/ /\* to be transferred by DMA int rx\_array[array\_size]; /\* This array holds data rxed by the SCC \*/ unsigned long rx mem addr; int \*rxarrav; int rx\_mem\_addr\_0, rx\_mem\_addr\_1, rx\_mem\_addr\_2; unsigned int ds; int function\_reg = 0x0018; int exec\_fcn\_reg = 0x001A;

`/\* \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ i= inp(scc addr chac); /\* Reset pointer bits to 0 Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 9); /\* Point to WR9\*/ Wait 2 us. \*/ for (i=0; i<=45; i++); \*. outp(scc\_addr\_chac, 0xC0); 7\* Reset both Channels \*/ for (i=0; i<=45; i++); ait 2 us. \*/ i=inp(scc\_addr\_chac); /\* WRITE AND READ REGISTER 4 \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 4); \*/ Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 0x46); /\* Set up Register 4. \*/ /\* x16 Clock Mode \*/ /\* 1 Stop bit/char /\* Even Parity, Disabled \*/ /\* WRITE TO REGISTER 3 \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); ·/\* \*/ outp(scc\_addr\_chac, 3); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 0xC0); /\* Set up Write Register 3.\*/ /\* WRITE TO REGISTER 5 - Tx Control \*/ \*/ Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 5); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 0xE4); /\* Set up Write Register 5.\*/

õ

/\*

/\*

′/\*

/\*

Figure 8. (Continued)

\*/

| /* WRITE TO REGISTER 9 - Interrupt Control*/                                 |

|------------------------------------------------------------------------------|

| /* */<br>/* Wait 2 us. */ for (i=0; i<=45; i++);                             |

| /* */ outp(scc_addr_chac, 9);                                                |

| /* /* Wait 2 us. */ for (i=0; i<=45; i++);                                   |

| /* */                                                                        |

| outp(scc_addr_chac, 0x17);<br>/* Set up Write Register 9.*/                  |

| /* WRITE TO REGISTER 11 - Clock Control */                                   |

| /* */ /* Wait 2 us. */ for (i=0; i<=45; i++);                                |

| /* */                                                                        |

| <pre>outp(scc_addr_chac, 11); /* /*</pre>                                    |

| /* Wait 2 us. */ for (i=0; i<=45; i++); /* */                                |

| /*                                                                           |

| /* WRITE AND READ REGISTER 12 -<br>Baud Rate Genr. Time Constant low byte */ |

| <pre>i = inp(scc_addr_chac);</pre>                                           |

| /*                                                                           |

| /* */ outp(scc addr chac, 0x0C);                                             |

| /* */                                                                        |

| /* Wait 2 us. */ for (i=0; i<=45; i++); /* */                                |

| outp(scc_addr_chac, 0x5B);<br>/*Write low byte of time const.*/              |

/\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ i = inp(scc\_addr\_chac); /\* Reset pointer bits \*/ /\* WRITE REGISTER 13 -Baud Genr. Time Constant high byte \*/ \*/ Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 0x0D); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac, 0x00); /\*Write upper byte of time const.\*/ i = inp(scc addr chac); /\* Reset pointer bits \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chac,0x0D); \*/ /\* Wait \*/ for (i=0; i<=5; i++);</pre> \*/ i = inp(scc\_addr\_chac); /\* Read back Register 13 \*/ printf("\n Contents of RR13 = %X\n", i); Read Reg. 12 \*/ /\* /\* Wait 2 us. \*/ for (i=0; i<=45; i++); /\* \*/ outp(scc\_addr\_chac, 0x0C); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ i = inp(scc\_addr\_chac); /\* Read back Register 12 \*/ printf("\n Contents of RR12 = %X\n", i); /\* WRITE TO REGISTER 14 - Misc.Control, enable Baud Rate Generator \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); /\* \*/ outp(scc\_addr\_chac, 14); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); `/\* \*/ outp(scc\_addr\_chac, 03); /\* Set up Write Register 14.\*/ \*/

10

#

5

ALTERA APPLICATION NOTE

Figure 8. (Continued)

\*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ i= inp(scc\_addr\_chbc); /\* Reset pointer bits to 0 \*/ Wait 2 us. \*/ for (i=0; i<=45; i++); outp(scc\_addr\_chbc, 9); /\* Point to WR9\*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); outp(scc\_addr\_chbc, 0x40); 7\* Reset Channel B only \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++);</pre> \*/ i=inp(scc\_addr\_chbc); /\* WRITE REGISTER 4 \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 4); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 0x46); /\* Set up Register 4. \*/ /\* x16 Clock Mode \*/ /\* 1 Stop bit/char \*, /\* Even Parity, Disabled \*/ /\* WRITE TO REGISTER 3 \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 3); \*/ Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc addr chbc, 0xC0); /\* Set up Write Reg.3 \*. /\* Rx 8 bits/char. \*/ /\* WRITE TO REGISTER 1 \*/ \*/ 7. Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 1); \*, Wait 2 us. \*/ for (i=0; i<=45; i++); \*, outp(scc\_addr\_chbc, 0x60); 7\* Set up Write Register 1. ×, /\* Wait/Req. not enabled \*/

/\* WRITE TO REGISTER 9 - Interrupt Control\*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 9); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 0x17); /\* Set up Write Register 9.\*/ /\* WRITE TO REGISTER 11 - Clock Control \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); /\* \*/ outp(scc\_addr chbc, 11); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc addr chbc, 0x56); /\* Tx clock = Rx clock = BRG clk \*/ /\* WRITE TO REGISTER 12 - Low Byte of BRG Time Const\*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ i = inp(scc\_addr\_chbc); /\* Reset pointer bits \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 0x0C); \*/ Wait 2 us. \*/ for (i=0; i<=45; i++); outp(scc\_addr chbc, 0x5B); /\*Write low byte of time const.\*/ i = inp(scc\_addr\_chbc); /\* Reset pointer bits \*/ /\* WRITE TO REGISTER 13 - High Byte BRG Time Const. \*/ `/\* Wait 2 us. \*/ for (i=0; i<=45; i++); outp(scc\_addr\_chbc, 0x0D); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 0x00); /\*Write upper byte of time const.\*/ Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr chbc, 12); \*/ Wait 2 us. \*/ for (i=0; i<=45; i++); i = inp(scc\_addr\_chbc); /\* Read back Register 12 \*/ printf("\n Contents of RR12 Ch. B = %X\n", i);

8

Figure 8. (Continued)

/\* Read Reg. 13 \*/ ·/\* /\* Wait 2 us. \*/ for (i=0; i<=45; i++); ·/\* \*/ outp(scc addr chbc, 13); \*/ /\* Wait \*/ for (i=0; i<=5; i++); \*/ i = inp(scc addr chbc); /\* Read back Register 13 \*/ printf("\n Contents of RR13 Ch. B = %X\n", i); WRITE TO REGISTER 14 - Misc.Control \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 14); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc\_addr\_chbc, 0x02); /\* Set up Write Register 14.\*/ /\* WRITE TO REGISTER 14 - Misc. Control. enable Baud Rate Generator \*/ \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++); \*/ outp(scc addr chbc, 14); \*/ /\* Wait 2 us. \*/ for (i=0; i<=45; i++);</pre> \*/ outp(scc\_addr\_chbc, 0x03); /\* Baud Rate Genr. Enabled \*/ ..... \*/

/\* ----- \*/

/\* Initialize the tx array with data to be xmitted \*/

| array | [0]  | - | 0xCB;  |

|-------|------|---|--------|

| array | [1]  | - | 0xDD;  |

| array | [2]  | = | 0xCB;  |

| array | [3]  | = | 0xED;  |

| array | [4]  | = | 0xAB;  |

| array | [5]  | - | OXDE;  |

| array | [6]  | - | 0xEB;  |

| array | 71   | = | 0xAD;  |

| array | 8]   | - | OxFE;  |

| array | 9]   | - | 0xCD;  |

| array | [10] | - | 0xAC;  |

| array | [11] | = | 0xBD;  |

| array | 121  | - | 0xDA;  |

| array |      |   | OxA1;  |

| array | 141  | - | OxBO ; |

| array |      | - | OxBB;  |

|       |      |   |        |

/\* -/\* \*\*\*\*\*\*\*\*\*\*\* Reserve Memory for DMA Write Xfer \*\*\*\*\*\*\*\*\* \*/ /\* ----- \*/ rxarray = &rx\_array[0]; /\* Allocate space for array\_size integers \*/ segread(&segregs); /\* Read segment register values \*/ ds = segregs.ds; /\* Extract Data Seg. Reg. Contents \*/

printf("\n DATA SEGMENT Register contents = %X", ds); print: (", DrAn Strong and a state of the state of t rx\_mem\_addr\_2 = ((rx\_mem\_addr>>16) & 0x0FF) ; printf ("\n Memory Address for DMA High byte = %X", rx\_mem\_addr\_2); rx\_mem\_addr\_1 = ((rx\_mem\_addr>>8) & 0x0FF) ; printf ("\n Memory Address for DMA Middle byte = %X", rx\_mem\_addr\_1); rx\_mem\_addr\_0 = rx\_mem\_addr & 0x0FF; printf ("\n Memory Address for DMA Low byte = %X", rx\_mem\_addr\_0); /\* Initialize the rx array locations to 0 \*/ for (i=0; i<= (xfer\_count); i++) rx array[i] = 0; . \_\_\_\_\_\_\_\_\_\_\_ /\* \*\*\*\*\*\*\*\*\*\* Configure the DMA Channel for Mem. Write Xfer \*\*\*\*\*\*\*\* \*/ outp (function reg, 0xD4); /\* Master Clear \*/ outp (function\_reg, 0x94); /\* Set Mask bit, DMA channel 4 \*/ outp (function\_reg, 0x84); /\* Set up channel #4 \*/ outp (exec\_fcn\_reg, 0xFA); /\* Assign Arb Level 10 \*/ outp (function\_reg, 0x04); Write SCC data port addr. to I/O addr. reg.\*/ outp (exec\_fcn\_reg, 0x01); outp (exec\_fcn\_reg, 0x60); /\* 6001H is the SCC Ch. B data reg. addr. \*/ outp (function\_reg, 0x24) :/\* Mem. Address write \*/ outp (exec\_fcn\_reg, rx\_mem\_addr\_0); /\* Lower Byte of address \*/ outp (exec\_fcn\_reg, rx\_mem\_addr\_1); /\* Middle Byte of address \*/ outp (exec\_fcn\_reg, rx\_mem\_addr\_2); /\* Upper Byte of address \*/

N

#15

ALTERA APPLICATION NOTE

R

```

outp (function_reg, 0x44);/* Write the xfer count */

outp (exec_fcn_reg, xfer_count); /* Low Byte */

outp (exec_fcn_reg, 0x00);

/* High Byte */

outp (function_reg, 0x54); /* Read xfer Count Reg.*/

i = inp (exec_fcn_reg);

printf("\n Low byte of the xfer count = %X", i);

i = inp (exec fcn reg);

printf("\n High byte of the xfer count = %X", i);

outp (function_reg, 0x74); /* Extended Mode Reg. */

outp (exec fcn reg, 0x0D);

/*Write, 8-bit Xfer, Programmed I/O addr */

/* Write to Channel A Register 5 to enable Tx

*/