June 14, 1999

# Voodoo3®

# **HIGH-PERFORMANCE**

# **GRAPHICS ENGINE**

# FOR

# **3D GAME ACCELERATION**

Programming Guide: Revision 1.4 June 14, 1999 Copyright 1998 3Dfx Interactive, Inc. All Rights Reserved

## 3Dfx Interactive, Inc.

4435 Fortran Drive San Jose CA 95134 Phone: (408) 935-4400 Fax: (408) 935-4424

Copyright 1998 © 3Dfx Interactive, Inc. Proprietary and Preliminary

1 **Confidential**  Revision 1.4 June 14, 1999

### Voodoo3 High-Performance Graphics Engine for 3D Game Acceleration

### Notice:

3Dfx Interactive, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. The information is subject to change without notice. No responsibility is assumed by 3Dfx Interactive, Inc. for the use of this information, nor for infringements of patents or the rights of third parties. This document is the property of 3Dfx Interactive, Inc. and implies no license under patents, copyrights, or trade secrets.

### Trademarks:

All trademarks are the property of their respective owners.

### **Copyright Notice:**

No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photographic, or otherwise, or used as the basis for manufacture or sale of any items without the prior written consent of 3Dfx Interactive, Inc. If this document is downloaded from the 3Dfx Interactive, Inc. world wide web site, the user may view or print it, but may not transmit copies to any other party and may not post it on any other site or location.

### **Programming Examples:**

Sample programs in this book may be adapted, in part or in whole, for use in any equipment incorporating Voodoo3. Use in any equipment not incorporating Voodoo3 is expressly prohibited.

### **Proprietary Information:**

This document contains proprietary information of 3Dfx Interactive, Inc., and its receipt or possession does not convey any rights to reproduce, disclose its contents, or to manufacture, use or sell anything it may describe. Reproduction, disclosure or use without specific written authorization of 3Dfx Interactive, Inc., is strictly forbidden.

# **Table of Contents**

| Table          | of Contents                                                              | . 3  |

|----------------|--------------------------------------------------------------------------|------|

| List o         | f Tables                                                                 | 12   |

| List o         | f Figures                                                                | 14   |

| 1              | Introduction                                                             |      |

| 1.1            | Scope of Document                                                        |      |

| 1.2            | Document History                                                         |      |

| 1.2            | Devices Covered                                                          |      |

|                |                                                                          |      |

| 1.4            | Audience                                                                 |      |

| 1.5            | Conventions                                                              |      |

| 1.5.1          | Acronyms                                                                 |      |

| 1.5.2          | Number Base                                                              |      |

| 1.5.3          | Number/Color Formats                                                     |      |

| 1.5.4          | Object Grouping                                                          |      |

| 1.5.5          | Abbreviations Product Overview                                           |      |

| 2              |                                                                          |      |

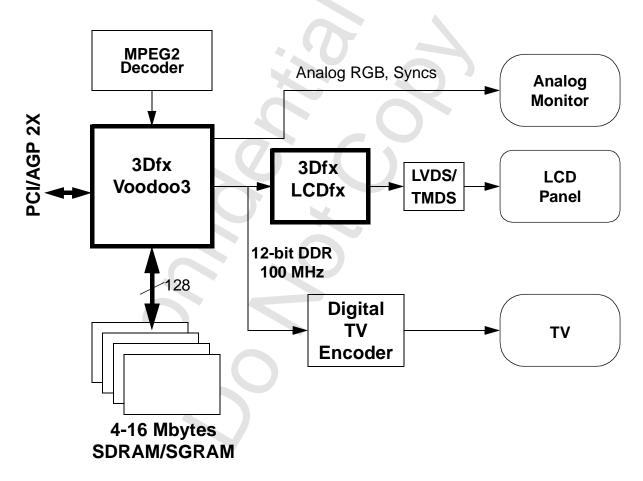

| 2.1            | Introduction                                                             |      |

| 2.1.1          | Voodoo Graphics Compatibility                                            | 18   |

| 2.1.2          | 3D Performance and Quality                                               |      |

| 2.1.3          | Optimized for Pentium, II and AGP-2X Platform                            | . 18 |

| 2.1.4          | Windows, GUI/Video Acceleration                                          |      |

| 2.1.5          | DVD Acceleration                                                         |      |

| 2.2            | Feature List                                                             |      |

| 2.2.1          | General Features                                                         |      |

| 2.2.2          | 2D Acceleration                                                          |      |

| 2.2.3          | 3D Acceleration                                                          |      |

| 2.2.4<br>2.2.5 | Video Acceleration                                                       |      |

| 2.2.5          | Host Interface                                                           |      |

| 2.2.0          | Process and Package Technology                                           | 20   |

| 2.2.7          | Software                                                                 |      |

| 3              | VGA Core Registers                                                       |      |

|                | Overview                                                                 |      |

| 3.1            |                                                                          |      |

| 3.2            | General Registers                                                        |      |

| 3.2.1          | Miscellaneous Output                                                     |      |

| 3.2.2          | FC: Feature Control                                                      |      |

| 3.2.3          | FEAT: Input Status Register 0                                            |      |

| 3.2.4          | STAT: Input Status Register 1                                            |      |

| 3.2.5<br>3.2.6 | Motherboard Enable (0x03C3)                                              |      |

| 3.2.0<br>3.2.7 | Adapter Enable (0x46E8)<br>Subsystem Enable (0x0102)                     |      |

| 3.2.7          |                                                                          |      |

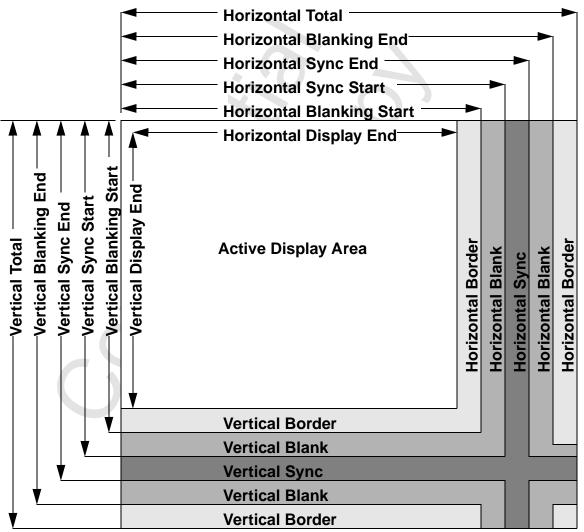

|                | CRT Controller Registers                                                 |      |

| 3.3.1          | CRX: CRTC Index                                                          |      |

| 3.3.2<br>3.3.3 | CR0: CRTC Horizontal Total<br>CR1: CRTC Horizontal Display Enable End    |      |

| 3.3.3<br>3.3.4 | CR1: CRTC Horizontal Display Enable End                                  |      |

| 3.3.4<br>3.3.5 | CR2. CRTC Horizontal Blanking Start<br>CR3: CRTC Horizontal Blanking End |      |

| 3.3.5          | CR3. CRTC Horizontal Blanking End                                        |      |

| 3.3.7          | CR5: CRTC Horizontal Sync End                                            |      |

| 3.3.8          | CR6: CRTC Vertical Total                                                 |      |

|                |                                                                          |      |

| 3.3.9                                                                                                                                                                                                    | CR7: CRTC Overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3.10                                                                                                                                                                                                   | CR8: CRTC Preset Row Scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                                                                                                        |

| 3.3.11                                                                                                                                                                                                   | CR9:CRTC Maximum Scan Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 32                                                                                                                                                      |

| 3.3.12                                                                                                                                                                                                   | CRA: CRTC Cursor Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                           |

| 3.3.13                                                                                                                                                                                                   | CRB: CRTC Cursor End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33                                                                                                                                                        |

| 3.3.14                                                                                                                                                                                                   | CRC: CRTC Screen Start Address High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |

| 3.3.15                                                                                                                                                                                                   | CRD: CRTC Screen Start Address Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                           |

| 3.3.16                                                                                                                                                                                                   | CRE: CRTC Cursor Location High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                           |

| 3.3.17                                                                                                                                                                                                   | CRF: CRTC Cursor Location Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                           |

| 3.3.18                                                                                                                                                                                                   | CR10: CRTC Vertical Sync Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                           |

| 3.3.19                                                                                                                                                                                                   | CR11: CRTC Vertical Sync End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                           |

| 3.3.20                                                                                                                                                                                                   | CR12: CRTC Vertical Display Enable End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                           |

| 3.3.21                                                                                                                                                                                                   | CR13: CRTC Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                           |

| 3.3.22                                                                                                                                                                                                   | CR14: CRTC UnderlineLocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                           |

| 3.3.23                                                                                                                                                                                                   | CR15: CRTC Vertical Blanking Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                           |

| 3.3.24                                                                                                                                                                                                   | CR16: CRTC Vertical Blanking End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |

| 3.3.25                                                                                                                                                                                                   | CR17: CRTC Mode Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |

| 3.3.26                                                                                                                                                                                                   | CR18: CRTC Line Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                                                        |

| 3.3.27                                                                                                                                                                                                   | CR1A: CRTC Horizontal Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |

| 3.3.28                                                                                                                                                                                                   | CR1B: CRTC Vertical Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38                                                                                                                                                        |

| 3.3.29                                                                                                                                                                                                   | CR1C: PCI Configuration Readback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |

| 3.3.30                                                                                                                                                                                                   | CR1D, CR1E, CR1F: Scratch Pad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                           |

| 3.3.31                                                                                                                                                                                                   | CR20: CRTC Vertical Counter Preload Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |

| 3.3.32                                                                                                                                                                                                   | CR21: CRTC Vertical Counter Preload High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39                                                                                                                                                        |

| 3.3.33                                                                                                                                                                                                   | CR22: Latches ReadBack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                                                                                                        |

| 3.3.34                                                                                                                                                                                                   | CR24: Attribute Controller Toggle Readback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39                                                                                                                                                        |

| 0 0 05                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20                                                                                                                                                        |

| 3.3.35                                                                                                                                                                                                   | CR26: Attribute Controller Index Readback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39                                                                                                                                                        |

| 3.3.35<br><b>3.4</b>                                                                                                                                                                                     | Graphics Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                           |

|                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                                                        |

| 3.4                                                                                                                                                                                                      | Graphics Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>40                                                                                                                                                  |

| 3.4<br>3.4.1                                                                                                                                                                                             | Graphics Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>40<br>40                                                                                                                                            |

| <b>3.4</b><br>3.4.1<br>3.4.2                                                                                                                                                                             | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40<br>40<br>40<br>40                                                                                                                                      |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3                                                                                                                                                                           | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40<br>40<br>40<br>40<br>40                                                                                                                          |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                                                                                                                  | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40<br>40<br>40<br>40<br>40<br>40                                                                                                                          |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                                                                                                                                                         | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40<br>40<br>40<br>40<br>41<br>41                                                                                                                    |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6                                                                                                                                                | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Read Plane Select<br>GR5: Graphics Controller Mode<br>GR6: Graphics Controller Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>40<br>40<br>40<br>41<br>41<br>42<br>43                                                                                                              |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9                                                                                                                     | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Data Rotate<br>GR5: Graphics Controller Read Plane Select<br>GR5: Graphics Controller Mode<br>GR6: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Color Dont Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43                                                                                                        |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10                                                                                                           | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Read Plane Select<br>GR5: Graphics Controller Mode<br>GR6: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Color Dont Care<br>GR8: Graphics Controller Bit Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>43                                                                                                  |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9                                                                                                                     | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Read Plane Select<br>GR5: Graphics Controller Mode<br>GR6: Graphics Controller Mode<br>GR7: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Bit Mask<br>Attribute Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>43<br>43                                                                                            |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1                                                                                           | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Data Rotate<br>GR5: Graphics Controller Read Plane Select<br>GR6: Graphics Controller Mode<br>GR7: Graphics Controller Mode<br>GR7: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Color Dont Care<br>GR8: Graphics Controller Bit Mask<br>Attribute Controller Registers<br>ARX: Attribute Controller Index                                                                                                                                                                                                                                                                                                                                                                                                        | 40<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>43<br>43<br>44<br>44                                                                                |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.1<br>3.5.2                                                                         | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Read Plane Select<br>GR5: Graphics Controller Mode<br>GR6: Graphics Controller Mode<br>GR7: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Bit Mask<br>Attribute Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>43<br>43<br>44<br>44                                                                                |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1                                                                                           | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Data Rotate<br>GR5: Graphics Controller Read Plane Select<br>GR6: Graphics Controller Mode<br>GR6: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Bit Mask<br>Attribute Controller Registers<br>ARX: Attribute Controller Index<br>ARX: Attribute Controller Index<br>AR10: Attribute Controller Mode                                                                                                                                                                                                                                                                                                                                                                     | 40<br>40<br>40<br>41<br>41<br>41<br>42<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>44                                                                    |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4                                                                | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Data Rotate<br>GR5: Graphics Controller Read Plane Select<br>GR6: Graphics Controller Mode<br>GR6: Graphics Controller Mode<br>GR7: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Bit Mask<br>Attribute Controller Registers<br>ARX: Attribute Controller Index<br>ARX: Attribute Controller Index<br>ARO-ARF: Attribute Controller Palette                                                                                                                                                                                                                                                                                                                              | 40<br>40<br>40<br>41<br>41<br>41<br>42<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>44                                                                    |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5                                              | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Read Plane Select<br>GR5: Graphics Controller Mode<br>GR6: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Bit Mask<br>Attribute Controller Registers<br>ARX: Attribute Controller Index<br>AR0-ARF: Attribute Controller Palette<br>AR10: Attribute Controller Mode<br>AR11: OverScan Color<br>AR12: Color Plane Enable                                                                                                                                                                                                                                                                                                         | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 45 \\ 45$                                                 |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6                            | Graphics Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 44$                                                       |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7                                     | Graphics Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 44$                                                       |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6                            | Graphics Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 44$                                                       |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7                                     | Graphics Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 45 \\ 45 \\ 45$                                                       |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.6                              | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset Enable<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate<br>GR4: Graphics Controller Read Plane Select<br>GR5: Graphics Controller Mode<br>GR6: Graphics Controller Mode<br>GR6: Graphics Controller Miscellaneous<br>GR7: Graphics Controller Miscellaneous<br>GR8: Graphics Controller Registers<br>ARX: Attribute Controller Index<br>AR0-ARF: Attribute Controller Palette<br>AR1: OverScan Color<br>AR1: OverScan Color<br>AR12: Color Plane Enable<br>AR13: Pixel Panning<br>AR14: Attribute Color Select                                                                                                                                                                                                                                                                                                  | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 45 \\ 45$                                                       |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3   | Graphics Controller Registers<br>GRX: Graphics Controller Index<br>GR0: Graphics Controller Set/Reset Enable<br>GR1: Graphics Controller Set/Reset Enable<br>GR2: Graphics Controller Color Compare<br>GR3: Graphics Controller Data Rotate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 45 \\ 45$                                                 |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4 | Graphics Controller Registers         GRX: Graphics Controller Index         GR0: Graphics Controller Set/Reset         GR1: Graphics Controller Set/Reset Enable         GR2: Graphics Controller Color Compare         GR3: Graphics Controller Data Rotate         GR4: Graphics Controller Read Plane Select         GR5: Graphics Controller Mode         GR6: Graphics Controller Mode         GR7: Graphics Controller Miscellaneous         GR7: Graphics Controller Color Dont Care         GR8: Graphics Controller Bit Mask         Attribute Controller Index         ARX: Attribute Controller Index         AR0-ARF: Attribute Controller Palette         AR10: Attribute Controller Mode         AR11: OverScan Color         AR12: Color Plane Enable         AR13: Pixel Panning         AR14: Attribute Color Select         Sequencer Registers         SRX: Sequencer Index         SR0: Sequencer Reset         SR1: Sequencer Clocking Mode         SR2: Sequencer Plane Mask | $\begin{array}{c} 40\\ 40\\ 40\\ 40\\ 41\\ 42\\ 43\\ 43\\ 43\\ 43\\ 43\\ 44\\ 44\\ 45\\ 46\\ 46\\ 47\\ 47\\ 47\\ 47\\ 48\end{array}$                      |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3   | Graphics Controller Registers         GRX: Graphics Controller Index         GR0: Graphics Controller Set/Reset         GR1: Graphics Controller Set/Reset Enable         GR2: Graphics Controller Color Compare         GR3: Graphics Controller Data Rotate         GR4: Graphics Controller Read Plane Select         GR5: Graphics Controller Mode         GR6: Graphics Controller Miscellaneous         GR7: Graphics Controller Miscellaneous         GR7: Graphics Controller Bit Mask         Attribute Controller Registers         ARX: Attribute Controller Index         ARC-ARF: Attribute Controller Palette         AR10: Attribute Controller Mode         AR11: OverScan Color         AR12: Color Plane Enable         AR13: Pixel Panning         AR14: Attribute Color Select         Sequencer Registers         SRX: Sequencer Index         SR0: Sequencer Reset         SR1: Sequencer Clocking Mode                                                                       | $\begin{array}{c} 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\ 45 \\ 46 \\ 46 \\ 47 \\ 47 \\ 47 \\ 47 \\ 48 \\ 49 \end{array}$ |

| 3.7             | RAMDAC Registers                                                 | 50   |

|-----------------|------------------------------------------------------------------|------|

| 3.7.1           | RAMDAC Pixel Mask                                                |      |